# E·XFL

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                         |

|--------------------------------|-------------------------------------------------------------------------|

| Product Status                 | Active                                                                  |

| Number of LABs/CLBs            | -                                                                       |

| Number of Logic Elements/Cells | 512                                                                     |

| Total RAM Bits                 | -                                                                       |

| Number of I/O                  | 81                                                                      |

| Number of Gates                | 12000                                                                   |

| Voltage - Supply               | 2.3V ~ 2.7V                                                             |

| Mounting Type                  | Surface Mount                                                           |

| Operating Temperature          | -40°C ~ 125°C (TA)                                                      |

| Package / Case                 | 100-LQFP                                                                |

| Supplier Device Package        | 100-TQFP (14x14)                                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/ex256-tqg100a |

|                                |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

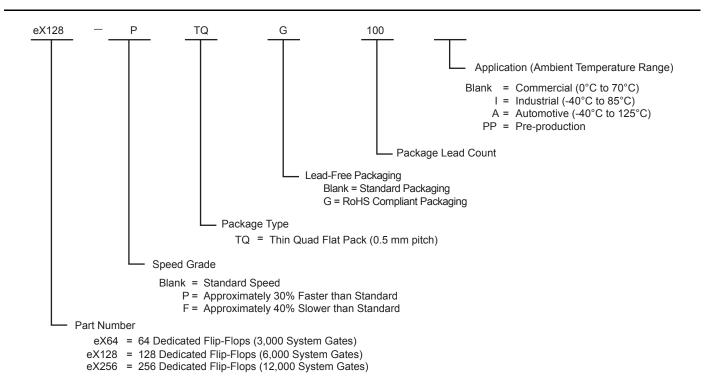

## **Ordering Information**

## **eX Device Status**

| eX Devices | Status     |  |

|------------|------------|--|

| eX64       | Production |  |

| eX128      | Production |  |

| eX256      | Production |  |

## **Plastic Device Resources**

|        | User I/Os (Including Clock Buffers) |       |  |

|--------|-------------------------------------|-------|--|

| Device | TQ64                                | TQ100 |  |

| eX64   | 41                                  | 56    |  |

| eX128  | 46                                  | 70    |  |

| eX256  | —                                   | 81    |  |

Note: TQ = Thin Quad Flat Pack

## **Temperature Grade Offerings**

| Device\ Package | TQ64    | TQ100   |

|-----------------|---------|---------|

| eX64            | C, I, A | C, I, A |

| eX128           | C, I, A | C, I, A |

| eX256           | C, I, A | C, I, A |

Note: C = Commercial

l = Industrial

A = Automotive

## **Speed Grade and Temperature Grade Matrix**

|   | –F           | Std          | –P           |

|---|--------------|--------------|--------------|

| С | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| 1 |              | $\checkmark$ | $\checkmark$ |

| A |              | $\checkmark$ |              |

*Note: P* = Approximately 30% faster than Standard

*–F* = Approximately 40% slower than Standard

Refer to the eX Automotive Family FPGAs datasheet for details on automotive temperature offerings.

Contact your local Microsemi representative for device availability.

# 1 – eX FPGA Architecture and Characteristics

## **General Description**

The eX family of FPGAs is a low-cost solution for low-power, high-performance designs. The inherent low power attributes of the antifuse technology, coupled with an additional low static power mode, make these devices ideal for power-sensitive applications. Fabricated with an advanced 0.22 mm CMOS antifuse technology, these devices achieve high performance with no power penalty.

## **eX Family Architecture**

Microsemi eX family is implemented on a high-voltage twin-well CMOS process using 0.22  $\mu$ m design rules. The eX family architecture uses a "sea-of-modules" structure where the entire floor of the device is covered with a grid of logic modules with virtually no chip area lost to interconnect elements or routing. Interconnection among these logic modules is achieved using Microsemi patented metal-to-metal programmable antifuse interconnect elements. The antifuse interconnect is made up of a combination of amorphous silicon and dielectric material with barrier metals and has an "on" state resistance of 25 $\Omega$  with a capacitance of 1.0fF for low-signal impedance. The antifuses are normally open circuit and, when programmed, form a permanent low-impedance connection. The eX family provides two types of logic modules, the register cell (R-cell) and the combinatorial cell (C-cell).

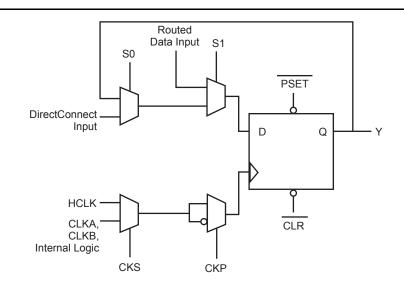

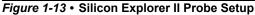

The R-cell contains a flip-flop featuring asynchronous clear, asynchronous preset, and clock enable (using the S0 and S1 lines) control signals (Figure 1-1). The R-cell registers feature programmable clock polarity selectable on a register-by-register basis. This provides additional flexibility while allowing mapping of synthesized functions into the eX FPGA. The clock source for the R-cell can be chosen from either the hard-wired clock or the routed clock.

The C-cell implements a range of combinatorial functions up to five inputs (Figure 1-2 on page 1-2). Inclusion of the DB input and its associated inverter function enables the implementation of more than 4,000 combinatorial functions in the eX architecture in a single module.

Two C-cells can be combined together to create a flip-flop to imitate an R-cell via the use of the CC macro. This is particularly useful when implementing non-timing-critical paths and when the design engineer is running out of R-cells. More information about the CC macro can be found in the *Maximizing Logic Utilization in eX, SX and SX-A FPGA Devices Using CC Macros* application note.

Figure 1-1 • R-Cell

## **Routing Resources**

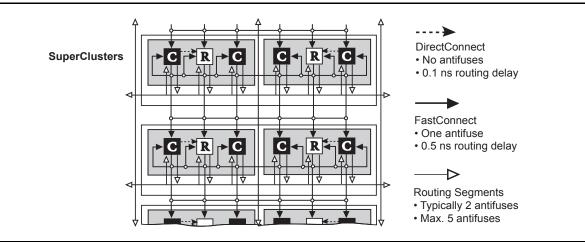

Clusters and SuperClusters can be connected through the use of two innovative local routing resources called FastConnect and DirectConnect, which enable extremely fast and predictable interconnection of modules within Clusters and SuperClusters (Figure 1-4). This routing architecture also dramatically reduces the number of antifuses required to complete a circuit, ensuring the highest possible performance.

DirectConnect is a horizontal routing resource that provides connections from a C-cell to its neighboring R-cell in a given SuperCluster. DirectConnect uses a hard-wired signal path requiring no programmable interconnection to achieve its fast signal propagation time of less than 0.1 ns (–P speed grade).

FastConnect enables horizontal routing between any two logic modules within a given SuperCluster and vertical routing with the SuperCluster immediately below it. Only one programmable connection is used in a FastConnect path, delivering maximum pin-to-pin propagation of 0.3 ns (–P speed grade).

In addition to DirectConnect and FastConnect, the architecture makes use of two globally oriented routing resources known as segmented routing and high-drive routing. The segmented routing structure of Microsemi provides a variety of track lengths for extremely fast routing between SuperClusters. The exact combination of track lengths and antifuses within each path is chosen by the fully automatic place-and-route software to minimize signal propagation delays.

Figure 1-4 • DirectConnect and FastConnect for SuperClusters

### **Clock Resources**

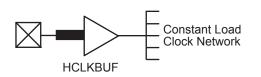

eX's high-drive routing structure provides three clock networks. The first clock, called HCLK, is hardwired from the HCLK buffer to the clock select MUX in each R-Cell. HCLK cannot be connected to combinational logic. This provides a fast propagation path for the clock signal, enabling the 3.9 ns clock-to-out (pad-to-pad) performance of the eX devices. The hard-wired clock is tuned to provide a clock skew of less than 0.1 ns worst case. If not used, the HCLK pin must be tied LOW or HIGH and must not be left floating. Figure 1-5 describes the clock circuit used for the constant load HCLK.

HCLK does not function until the fourth clock cycle each time the device is powered up to prevent false output levels due to any possible slow power-on-reset signal and fast start-up clock circuit. To activate HCLK from the first cycle, the TRST pin must be reserved in the Design software and the pin must be tied to GND on the board. (See the "TRST, I/O Boundary Scan Reset Pin" on page 1-32).

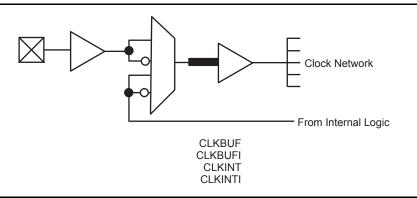

The remaining two clocks (CLKA, CLKB) are global routed clock networks that can be sourced from external pins or from internal logic signals (via the CLKINT routed clock buffer) within the eX device. CLKA and CLKB may be connected to sequential cells or to combinational logic. If CLKA or CLKB is sourced from internal logic signals, the external clock pin cannot be used for any other input and must be tied LOW or HIGH and must not float. Figure 1-6 describes the CLKA and CLKB circuit used in eX devices.

eX FPGA Architecture and Characteristics

Table 1-1 describes the possible connections of the routed clock networks, CLKA and CLKB. Unused clock pins must not be left floating and must be tied to HIGH or LOW.

#### Figure 1-5 • eX HCLK Clock Pad

Figure 1-6 • eX Routed Clock Buffer

#### Table 1-1 • Connections of Routed Clock Networks, CLKA and CLKB

| Module   | Pins                              |  |  |

|----------|-----------------------------------|--|--|

| C-Cell   | A0, A1, B0 and B1                 |  |  |

| R-Cell   | CLKA, CLKB, S0, S1, PSET, and CLR |  |  |

| I/O-Cell | EN                                |  |  |

## **Other Architectural Features**

#### Performance

The combination of architectural features described above enables eX devices to operate with internal clock frequencies exceeding 350 MHz for very fast execution of complex logic functions. The eX family is an optimal platform upon which the functionality previously contained in CPLDs can be integrated. eX devices meet the performance goals of gate arrays, and at the same time, present significant improvements in cost and time to market. Using timing-driven place-and-route tools, designers can achieve highly deterministic device performance.

### **User Security**

Microsemi FuseLock advantage provides the highest level of protection in the FPGA industry against unauthorized modifications. In addition to the inherent strengths of the architecture, special security fuses that are intended to prevent internal probing and overwriting are hidden throughout the fabric of the device. They are located such that they cannot be accessed or bypassed without destroying the rest of the device, making Microsemi antifuse FPGAs highly resistant to both invasive and more subtle noninvasive attacks.

Look for this symbol to ensure your valuable IP is secure. The FuseLock Symbol on the FPGA ensures that the device is safeguarded to cryptographic attacks.

#### Figure 1-7 • Fuselock

For more information, refer to Implementation of Security in Microsemi Antifuse FPGAs application note.

### **I/O Modules**

Each I/O on an eX device can be configured as an input, an output, a tristate output, or a bidirectional pin. Even without the inclusion of dedicated I/O registers, these I/Os, in combination with array registers, can achieve clock-to-out (pad-to-pad) timing as fast as 3.9 ns. I/O cells in eX devices do not contain embedded latches or flip-flops and can be inferred directly from HDL code. The device can easily interface with any other device in the system, which in turn enables parallel design of system components and reduces overall design time.

All unused I/Os are configured as tristate outputs by Microsemi's Designer software, for maximum flexibility when designing new boards or migrating existing designs. Each I/O module has an available pull-up or pull-down resistor of approximately 50 k $\Omega$  that can configure the I/O in a known state during power-up. Just shortly before V<sub>CCA</sub> reaches 2.5 V, the resistors are disabled and the I/Os will be controlled by user logic.

To exit the LP mode, the LP pin must be driven LOW for over 200  $\mu s$  to allow for the charge pumps to power-up and device initialization can begin.

Table 1-3 illustrates the standby current of eX devices in LP mode.

| Table 1-3 | <ul> <li>Standby Power of eX Devices in LP Mode Typical Conditions, V<sub>CCA</sub>, V<sub>CCI</sub> = 2.5 V,</li> </ul> |

|-----------|--------------------------------------------------------------------------------------------------------------------------|

|           | $T_{J} = 25^{\circ} C$                                                                                                   |

| Product | Low Power Standby Current | Units |

|---------|---------------------------|-------|

| eX64    | 100                       | μA    |

| eX128   | 111                       | μA    |

| eX256   | 134                       | μΑ    |

eX FPGA Architecture and Characteristics

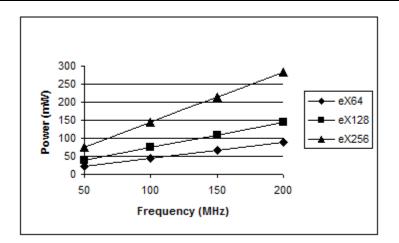

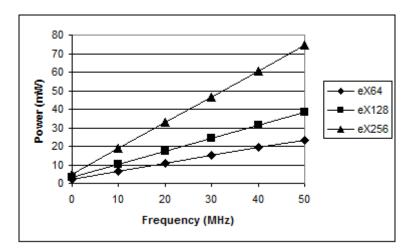

Figure 1-8 to Figure 1-11 on page 1-9 show some sample power characteristics of eX devices.

#### Notes:

- 1. Device filled with 16-bit counters.

- 2. VCCA, VCCI = 2.7 V, device tested at room temperature.

Figure 1-8 • eX Dynamic Power Consumption – High Frequency

#### Notes:

- 1. Device filled with 16-bit counters.

- 2. VCCA, VCCI = 2.7 V, device tested at room temperature.

Figure 1-9 • eX Dynamic Power Consumption – Low Frequency

Table 1-5 describes the different configuration requirements of BST pins and their functionality in different modes.

| Mode                | Designer "Reserve JTAG" Selection | TAP Controller State        |

|---------------------|-----------------------------------|-----------------------------|

| Dedicated (JTAG)    | Checked                           | Any                         |

| Flexible (User I/O) | Unchecked                         | Test-Logic-Reset            |

| Flexible (JTAG)     | Unchecked                         | Any EXCEPT Test-Logic-Reset |

Table 1-5 • Boundary-Scan Pin Configurations and Functions

## **TRST Pin**

The TRST pin functions as a dedicated Boundary-Scan Reset pin when the **Reserve JTAG Test Reset** option is selected, as shown in Figure 1-12. An internal pull-up resistor is permanently enabled on the TRST pin in this mode. It is recommended to connect this pin to GND in normal operation to keep the JTAG state controller in the Test-Logic-Reset state. When JTAG is being used, it can be left floating or be driven HIGH.

When the **Reserve JTAG Test Reset** option is not selected, this pin will function as a regular I/O. If unused as an I/O in the design, it will be configured as a tristated output.

## **JTAG Instructions**

Table 1-6 lists the supported instructions with the corresponding IR codes for eX devices.

| Instructions (IR4: IR0) | Binary Code |

|-------------------------|-------------|

| EXTEST                  | 00000       |

| SAMPLE / PRELOAD        | 00001       |

| INTEST                  | 00010       |

| USERCODE                | 00011       |

| IDCODE                  | 00100       |

| HIGHZ                   | 01110       |

| CLAMP                   | 01111       |

| Diagnostic              | 10000       |

| BYPASS                  | 11111       |

| Reserved                | All others  |

Table 1-7 lists the codes returned after executing the IDCODE instruction for eX devices. Note that bit 0 is always "1." Bits 11-1 are always "02F", which is Microsemi SoC Products Group's manufacturer code.

| Device | Revision | Bits 31-28 | Bits 27-12 |

|--------|----------|------------|------------|

| eX64   | 0        | 8          | 40B2, 42B2 |

| eX128  | 0        | 9          | 40B0, 42B0 |

| eX256  | 0        | 9          | 40B5, 42B5 |

| eX64   | 1        | A          | 40B2, 42B2 |

| eX128  | 1        | В          | 40B0, 42B0 |

| eX256  | 1        | В          | 40B5, 42B5 |

Table 1-7 • IDCODE for eX Devices

## **Design Considerations**

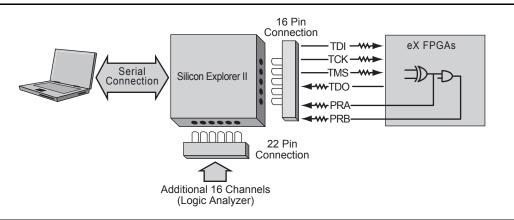

The TDI, TCK, TDO, PRA, and PRB pins should not be used as input or bidirectional ports. Since these pins are active during probing, critical signals input through these pins are not available while probing. In addition, the Security Fuse should not be programmed because doing so disables the probe circuitry. It is recommended to use a series  $70\Omega$  termination resistor on every probe connector (TDI, TCK, TMS, TDO, PRA, PRB). The  $70\Omega$  series termination is used to prevent data transmission corruption during probing and reading back the checksum.

| JTAG Mode | TRST <sup>1</sup> | Security Fuse<br>Programmed | PRA, PRB <sup>2</sup> | TDI, TCK, TDO <sup>2</sup> |

|-----------|-------------------|-----------------------------|-----------------------|----------------------------|

| Dedicated | LOW               | No                          | User I/O <sup>3</sup> | Probing Unavailable        |

| Flexible  | LOW               | No                          | User I/O <sup>3</sup> | User I/O <sup>3</sup>      |

| Dedicated | HIGH              | No                          | Probe Circuit Outputs | Probe Circuit Inputs       |

| Flexible  | HIGH              | No                          | Probe Circuit Outputs | Probe Circuit Inputs       |

| -         | _                 | Yes                         | Probe Circuit Secured | Probe Circuit Secured      |

Notes:

1. If TRST pin is not reserved, the device behaves according to TRST = HIGH in the table.

- 2. Avoid using the TDI, TCK, TDO, PRA, and PRB pins as input or bidirectional ports. Since these pins are active during probing, input signals will not pass through these pins and may cause contention.

- 3. If no user signal is assigned to these pins, they will behave as unused I/Os in this mode. Unused pins are automatically tristated by Microsemi Designer software.

### **Development Tool Support**

The eX family of FPGAs is fully supported by both Libero® Integrated Design Environment and Designer FPGA Development software. Libero IDE is a design management environment that streamlines the design flow. Libero IDE provides an integrated design manager that seamlessly integrates design tools while guiding the user through the design flow, managing all design and log files, and passing necessary design data among tools. Additionally, Libero IDE allows users to integrate both schematic and HDL synthesis into a single flow and verify the entire design in a single environment. Libero IDE includes Synplify<sup>®</sup> for Microsemi from Synplicity<sup>®</sup>, ViewDraw for Microsemi from Mentor Graphics, ModelSim<sup>®</sup> HDL Simulator from Mentor Graphics<sup>®</sup>, WaveFormer Lite<sup>™</sup> from SynaptiCAD<sup>™</sup>, and Designer software from Microsemi. Refer to the *Libero IDE flow* (located on Microsemi SoC Product Group's website) diagram for more information.

## **3.3 V LVTTL Electrical Specifications**

|                                    |                                                       |                 | Commercial |              | Ind       |           |       |

|------------------------------------|-------------------------------------------------------|-----------------|------------|--------------|-----------|-----------|-------|

| Symbol                             | Parameter                                             |                 | Min.       | Max.         | Min.      | Max.      | Units |

| VOH                                | VCCI = MIN, VI = VIH or VIL                           | (IOH =8 mA)     | 2.4        |              | 2.4       | •         | V     |

| VOL                                | VCCI = MIN, VI = VIH or VIL                           | (IOL = 12 mA)   |            | 0.4          |           | 0.4       | V     |

| VIL                                | Input Low Voltage                                     |                 |            | 0.8          |           | 0.8       | V     |

| VIH                                | Input High Voltage                                    |                 | 2.0        | VCCI +0.5    | 2.0       | VCCI +0.5 | V     |

| IIL/ IIH                           | Input Leakage Current, VIN = VCCI or<br>GND           |                 | -10        | 10           | -10       | 10        | μA    |

| IOZ                                | 3-State Output Leakage Current,<br>VOUT = VCCI or GND |                 | -10        | 10           | –10       | 10        | μA    |

| t <sub>R</sub> , t <sub>F1,2</sub> | Input Transition Time                                 |                 |            | 10           |           | 10        | ns    |

| C <sub>IO</sub>                    | I/O Capacitance                                       |                 |            | 10           |           | 10        | pF    |

| ICC <sup>3,4</sup>                 | Standby Current                                       |                 |            | 1.5          |           | 10        | mA    |

| IV Curve                           | Can be derived from the IBIS model at ww              | w.microsemi.com | m/soc/cu   | stsup/models | /ibis.htm | I         | -     |

Notes:

1.  $t_R$  is the transition time from 0.8 V to 2.0 V.

2.  $t_F$  is the transition time from 2.0 V to 0.8 V.

3. ICC max Commercial -F = 5.0 mA

*4. ICC* = *ICCI* + *ICCA*

5. JTAG pins comply with LVTTL/TTL I/O specification regardless of whether they are used as a user I/O or a JTAG I/O.

## **5.0 V TTL Electrical Specifications**

|                                    |                                                                                             |               | Commercial |           | Ind  |           |       |

|------------------------------------|---------------------------------------------------------------------------------------------|---------------|------------|-----------|------|-----------|-------|

| Symbol                             | Parameter                                                                                   |               | Min.       | Max.      | Min. | Max.      | Units |

| VOH                                | VCCI = MIN, VI = VIH or VIL                                                                 | (IOH = -8 mA) | 2.4        | •         | 2.4  | •         | V     |

| VOL                                | VCCI = MIN, VI = VIH or VIL                                                                 | (IOL= 12 mA)  |            | 0.4       |      | 0.4       | V     |

| VIL                                | Input Low Voltage                                                                           |               |            | 0.8       |      | 0.8       | V     |

| VIH                                | Input High Voltage                                                                          |               | 2.0        | VCCI +0.5 | 2.0  | VCCI +0.5 | V     |

| IIL/ IIH                           | Input Leakage Current, VIN = VCCI or GND                                                    |               | -10        | 10        | -10  | 10        | μA    |

| IOZ                                | 3-State Output Leakage Current,<br>VOUT = VCCI or GND                                       |               | -10        | 10        | -10  | 10        | μA    |

| t <sub>R</sub> , t <sub>F1,2</sub> | Input Transition Time                                                                       |               |            | 10        |      | 10        | ns    |

| C <sub>IO</sub>                    | I/O Capacitance                                                                             |               |            | 10        |      | 10        | pF    |

| ICC <sup>3,4</sup>                 | Standby Current                                                                             |               |            | 15        |      | 20        | mA    |

| IV Curve                           | Curve Can be derived from the IBIS model at www.microsemi.com/soc/custsup/models/ibis.html. |               |            |           |      |           |       |

| Noto:                              | •                                                                                           |               |            |           |      |           |       |

Note:

1.  $t_R$  is the transition time from 0.8 V to 2.0 V.

2.  $t_F$  is the transition time from 2.0 V to 0.8 V.

3. ICC max Commercial -F=20mA

*4. ICC* = *ICCI* + *ICCA*

5. JTAG pins comply with LVTTL/TTL I/O specification regardless of whether they are used as a user I/O or a JTAG I/O.

## **Power Dissipation**

Power consumption for eX devices can be divided into two components: static and dynamic.

## Static Power Component

The power due to standby current is typically a small component of the overall power. Typical standby current for eX devices is listed in the Table 1-11 on page 1-16. For example, the typical static power for eX128 at 3.3 V V<sub>CCI</sub> is:

ICC \* VCCA = 795 µA x 2.5 V = 1.99 mW

### **Dynamic Power Component**

Power dissipation in CMOS devices is usually dominated by the dynamic power dissipation. This component is frequency-dependent and a function of the logic and the external I/O. Dynamic power dissipation results from charging internal chip capacitance due to PC board traces and load device inputs. An additional component of the dynamic power dissipation is the totem pole current in the CMOS transistor pairs. The net effect can be associated with an equivalent capacitance that can be combined with frequency and voltage to represent dynamic power dissipation.

Dynamic power dissipation = CEQ \* VCCA<sup>2</sup> x F

where:

CEQ = Equivalent capacitance

F = switching frequency

Equivalent capacitance is calculated by measuring ICCA at a specified frequency and voltage for each circuit component of interest. Measurements have been made over a range of frequencies at a fixed value of VCC. Equivalent capacitance is frequency-independent, so the results can be used over a wide range of operating conditions. Equivalent capacitance values are shown below.

#### **CEQ Values for eX Devices**

| 1.70 pF |

|---------|

| 1.70 pF |

| 1.30 pF |

| 7.40 pF |

| 1.05 pF |

|         |

The variable and fixed capacitance of other device components must also be taken into account when estimating the dynamic power dissipation.

Table 1-12 shows the capacitance of the clock components of eX devices.

#### Table 1-12 • Capacitance of Clock Components of eX Devices

|                                          | eX64     | eX128    | eX256    |

|------------------------------------------|----------|----------|----------|

| Dedicated array clock – variable (Ceqhv) | 0.85 pF  | 0.85 pF  | 0.85 pF  |

| Dedicated array clock – fixed (Ceqhf)    | 18.00 pF | 20.00 pF | 25.00 pF |

| Routed array clock A (r1)                | 23.00 pF | 28.00 pF | 35.00 pF |

| Routed array clock B (r2)                | 23.00 pF | 28.00 pF | 35.00 pF |

# **Cell Timing Characteristics**

Figure 1-16 • Flip-Flops

## **eX Family Timing Characteristics**

Table 1-17 • eX Family Timing Characteristics

(Worst-Case Commercial Conditions, VCCA = 2.3 V, T<sub>J</sub> = 70°C)

|                      |                                          | –P S | peed | Std S | Speed | –F S | peed |       |

|----------------------|------------------------------------------|------|------|-------|-------|------|------|-------|

| Parameter            | Description                              | Min. | Max. | Min.  | Max.  | Min. | Max. | Units |

| C-Cell Prop          | agation Delays <sup>1</sup>              |      |      |       |       |      |      |       |

| t <sub>PD</sub>      | Internal Array Module                    |      | 0.7  |       | 1.0   |      | 1.4  | ns    |

| Predicted R          | outing Delays <sup>2</sup>               |      |      |       |       |      |      |       |

| t <sub>DC</sub>      | FO=1 Routing Delay, DirectConnect        |      | 0.1  |       | 0.1   |      | 0.2  | ns    |

| t <sub>FC</sub>      | FO=1 Routing Delay, FastConnect          |      | 0.3  |       | 0.5   |      | 0.7  | ns    |

| t <sub>RD1</sub>     | FO=1 Routing Delay                       |      | 0.3  |       | 0.5   |      | 0.7  | ns    |

| t <sub>RD2</sub>     | FO=2 Routing Delay                       |      | 0.4  |       | 0.6   |      | 0.8  | ns    |

| t <sub>RD3</sub>     | FO=3 Routing Delay                       |      | 0.5  |       | 0.8   |      | 1.1  | ns    |

| t <sub>RD4</sub>     | FO=4 Routing Delay                       |      | 0.7  |       | 1.0   |      | 1.3  | ns    |

| t <sub>RD8</sub>     | FO=8 Routing Delay                       |      | 1.2  |       | 1.7   |      | 2.4  | ns    |

| t <sub>RD12</sub>    | FO=12 Routing Delay                      |      | 1.7  |       | 2.5   |      | 3.5  | ns    |

| R-Cell Timir         | ng                                       |      |      |       |       |      |      |       |

| t <sub>RCO</sub>     | Sequential Clock-to-Q                    |      | 0.6  |       | 0.9   |      | 1.3  | ns    |

| t <sub>CLR</sub>     | Asynchronous Clear-to-Q                  |      | 0.6  |       | 0.8   |      | 1.2  | ns    |

| t <sub>PRESET</sub>  | Asynchronous Preset-to-Q                 |      | 0.7  |       | 0.9   |      | 1.3  | ns    |

| t <sub>SUD</sub>     | Flip-Flop Data Input Set-Up              | 0.5  |      | 0.7   |       | 1.0  |      | ns    |

| t <sub>HD</sub>      | Flip-Flop Data Input Hold                | 0.0  |      | 0.0   |       | 0.0  |      | ns    |

| t <sub>WASYN</sub>   | Asynchronous Pulse Width                 | 1.3  |      | 1.9   |       | 2.6  |      | ns    |

| t <sub>RECASYN</sub> | Asynchronous Recovery Time               | 0.3  |      | 0.5   |       | 0.7  |      | ns    |

| t <sub>HASYN</sub>   | Asynchronous Hold Time                   | 0.3  |      | 0.5   |       | 0.7  |      | ns    |

| 2.5 V Input          | Module Propagation Delays                |      |      |       |       |      |      |       |

| t <sub>INYH</sub>    | Input Data Pad-to-Y HIGH                 |      | 0.6  |       | 0.9   |      | 1.3  | ns    |

| t <sub>INYL</sub>    | Input Data Pad-to-Y LOW                  |      | 0.8  |       | 1.1   |      | 1.5  | ns    |

| 3.3 V Input          | Module Propagation Delays                |      |      |       |       |      |      |       |

| t <sub>INYH</sub>    | Input Data Pad-to-Y HIGH                 |      | 0.7  |       | 1.0   |      | 1.4  | ns    |

| t <sub>INYL</sub>    | Input Data Pad-to-Y LOW                  |      | 0.9  |       | 1.3   |      | 1.8  | ns    |

| 5.0 V Input          | Module Propagation Delays                |      |      |       |       |      |      |       |

| t <sub>INYH</sub>    | Input Data Pad-to-Y HIGH                 |      | 0.7  |       | 1.0   |      | 1.4  | ns    |

| t <sub>INYL</sub>    | Input Data Pad-to-Y LOW                  |      | 0.9  |       | 1.3   |      | 1.8  | ns    |

| Input Modu           | le Predicted Routing Delays <sup>2</sup> |      |      |       |       |      |      | 1     |

| t <sub>IRD1</sub>    | FO=1 Routing Delay                       |      | 0.3  |       | 0.4   |      | 0.5  | ns    |

| t <sub>IRD2</sub>    | FO=2 Routing Delay                       |      | 0.4  |       | 0.6   |      | 0.8  | ns    |

| t <sub>IRD3</sub>    | FO=3 Routing Delay                       |      | 0.5  |       | 0.8   |      | 1.1  | ns    |

| t <sub>IRD4</sub>    | FO=4 Routing Delay                       |      | 0.7  |       | 1.0   |      | 1.3  | ns    |

| t <sub>IRD8</sub>    | FO=8 Routing Delay                       |      | 1.2  |       | 1.7   |      | 2.4  | ns    |

| t <sub>IRD12</sub>   | FO=12 Routing Delay                      |      | 1.7  |       | 2.5   |      | 3.5  | ns    |

| Notes:               |                                          |      |      | -     |       |      |      | -     |

Notes:

1. For dual-module macros, use  $t_{PD} + t_{RD1} + t_{PDn}$ ,  $t_{RCO} + t_{RD1} + t_{PDn}$  or  $t_{PD1} + t_{RD1} + t_{SUD}$ , whichever is appropriate. 2. Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for

Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Post-route timing analysis or simulation is required to determine actual worst-case performance.

## 🔨 Microsemi

eX FPGA Architecture and Characteristics

# Table 1-18 • eX Family Timing Characteristics (Worst-Case Commercial Conditions VCCA = 2.3 V, VCCI = 4.75 V, T<sub>J</sub> = 70°C)

|                      |                                                              | –P S | peed | Std S | Speed | ed –F S |      |       |

|----------------------|--------------------------------------------------------------|------|------|-------|-------|---------|------|-------|

| Parameter            | Description                                                  | Min. | Max. | Min.  | Max.  | Min.    | Max. | Units |

| Dedicated (H         | lard-Wired) Array Clock Networks                             |      |      |       |       |         |      |       |

| t <sub>нскн</sub>    | Input LOW to HIGH<br>(Pad to R-Cell Input)                   |      | 1.1  |       | 1.6   |         | 2.3  | ns    |

| t <sub>HCKL</sub>    | Input HIGH to LOW<br>(Pad to R-Cell Input)                   |      | 1.1  |       | 1.6   |         | 2.3  | ns    |

| t <sub>HPWH</sub>    | Minimum Pulse Width HIGH                                     | 1.4  |      | 2.0   |       | 2.8     |      | ns    |

| t <sub>HPWL</sub>    | Minimum Pulse Width LOW                                      | 1.4  |      | 2.0   |       | 2.8     |      | ns    |

| t <sub>HCKSW</sub>   | Maximum Skew                                                 |      | <0.1 |       | <0.1  |         | <0.1 | ns    |

| t <sub>HP</sub>      | Minimum Period                                               | 2.8  |      | 4.0   |       | 5.6     |      | ns    |

| f <sub>HMAX</sub>    | Maximum Frequency                                            |      | 357  |       | 250   |         | 178  | MHz   |

| Routed Arra          | y Clock Networks                                             |      |      |       |       |         |      |       |

| t <sub>RCKH</sub>    | Input LOW to HIGH (Light Load)<br>(Pad to R-Cell Input) MAX. |      | 1.1  |       | 1.6   |         | 2.2  | ns    |

| t <sub>RCKL</sub>    | Input HIGH to LOW (Light Load)<br>(Pad to R-Cell Input) MAX. |      | 1.0  |       | 1.4   |         | 2.0  | ns    |

| t <sub>RCKH</sub>    | Input LOW to HIGH (50% Load)<br>(Pad to R-Cell Input) MAX.   |      | 1.2  |       | 1.7   |         | 2.4  | ns    |

| t <sub>RCKL</sub>    | Input HIGH to LOW (50% Load)<br>(Pad to R-Cell Input) MAX.   |      | 1.2  |       | 1.7   |         | 2.4  | ns    |

| t <sub>RCKH</sub>    | Input LOW to HIGH (100% Load)<br>(Pad to R-Cell Input) MAX.  |      | 1.3  |       | 1.9   |         | 2.6  | ns    |

| t <sub>RCKL</sub>    | Input HIGH to LOW (100% Load)<br>(Pad to R-Cell Input) MAX.  |      | 1.3  |       | 1.9   |         | 2.6  | ns    |

| t <sub>RPWH</sub>    | Min. Pulse Width HIGH                                        | 1.5  |      | 2.1   |       | 3.0     |      | ns    |

| t <sub>RPWL</sub>    | Min. Pulse Width LOW                                         | 1.5  |      | 2.1   |       | 3.0     |      | ns    |

| t <sub>RCKSW</sub> * | Maximum Skew (Light Load)                                    |      | 0.2  |       | 0.3   |         | 0.4  | ns    |

| t <sub>RCKSW</sub> * | Maximum Skew (50% Load)                                      |      | 0.1  |       | 0.2   |         | 0.3  | ns    |

| t <sub>RCKSW</sub> * | Maximum Skew (100% Load)                                     |      | 0.1  |       | 0.1   |         | 0.2  | ns    |

Note: \*Clock skew improves as the clock network becomes more heavily loaded.

## **Microsemi**.

eX FPGA Architecture and Characteristics

Table 1-20 • eX Family Timing Characteristics (Worst-Case Commercial Conditions VCCA = 2.3 V, T<sub>J</sub> = 70°C)

|                    |                                                    | -P S | peed  | Std S | Speed | –F Speed |       |       |  |

|--------------------|----------------------------------------------------|------|-------|-------|-------|----------|-------|-------|--|

| Parameter          | Description                                        | Min. | Max.  | Min.  | Max.  | Min.     | Max.  | Units |  |

| 2.5 V LVCMO        | S Output Module Timing <sup>1</sup> (VCCI = 2.3 V) |      |       |       |       |          |       |       |  |

| t <sub>DLH</sub>   | Data-to-Pad LOW to HIGH                            |      | 3.3   |       | 4.7   |          | 6.6   | ns    |  |

| t <sub>DHL</sub>   | Data-to-Pad HIGH to LOW                            |      | 3.5   |       | 5.0   |          | 7.0   | ns    |  |

| t <sub>DHLS</sub>  | Data-to-Pad HIGH to LOW—Low Slew                   |      | 11.6  |       | 16.6  |          | 23.2  | ns    |  |

| t <sub>ENZL</sub>  | Enable-to-Pad, Z to L                              |      | 2.5   |       | 3.6   |          | 5.1   | ns    |  |

| t <sub>ENZLS</sub> | Enable-to-Pad Z to L—Low Slew                      |      | 11.8  |       | 16.9  |          | 23.7  | ns    |  |

| t <sub>ENZH</sub>  | Enable-to-Pad, Z to H                              |      | 3.4   |       | 4.9   |          | 6.9   | ns    |  |

| t <sub>ENLZ</sub>  | Enable-to-Pad, L to Z                              |      | 2.1   |       | 3.0   |          | 4.2   | ns    |  |

| t <sub>ENHZ</sub>  | Enable-to-Pad, H to Z                              |      | 2.4   |       | 5.67  |          | 7.94  | ns    |  |

| d <sub>TLH</sub>   | Delta Delay vs. Load LOW to HIGH                   |      | 0.034 |       | 0.046 |          | 0.066 | ns/pF |  |

| d <sub>THL</sub>   | Delta Delay vs. Load HIGH to LOW                   |      | 0.016 |       | 0.022 |          | 0.05  | ns/pF |  |

| d <sub>THLS</sub>  | Delta Delay vs. Load HIGH to LOW—<br>Low Slew      |      | 0.05  |       | 0.072 |          | 0.1   | ns/pF |  |

| 3.3 V LVTTL (      | Output Module Timing <sup>1</sup> (VCCI = 3.0 V)   |      |       |       |       |          |       |       |  |

| t <sub>DLH</sub>   | Data-to-Pad LOW to HIGH                            |      | 2.8   |       | 4.0   |          | 5.6   | ns    |  |

| t <sub>DHL</sub>   | Data-to-Pad HIGH to LOW                            |      | 2.7   |       | 3.9   |          | 5.4   | ns    |  |

| t <sub>DHLS</sub>  | Data-to-Pad HIGH to LOW—Low Slew                   |      | 9.7   |       | 13.9  |          | 19.5  | ns    |  |

| t <sub>ENZL</sub>  | Enable-to-Pad, Z to L                              |      | 2.2   |       | 3.2   |          | 4.4   | ns    |  |

| t <sub>ENZLS</sub> | Enable-to-Pad Z to L—Low Slew                      |      | 9.7   |       | 13.9  |          | 19.6  | ns    |  |

| t <sub>ENZH</sub>  | Enable-to-Pad, Z to H                              |      | 2.8   |       | 4.0   |          | 5.6   | ns    |  |

| t <sub>ENLZ</sub>  | Enable-to-Pad, L to Z                              |      | 2.8   |       | 4.0   |          | 5.6   | ns    |  |

| t <sub>ENHZ</sub>  | Enable-to-Pad, H to Z                              |      | 2.6   |       | 3.8   |          | 5.3   | ns    |  |

| d <sub>TLH</sub>   | Delta Delay vs. Load LOW to HIGH                   |      | 0.02  |       | 0.03  |          | 0.046 | ns/pF |  |

| d <sub>THL</sub>   | Delta Delay vs. Load HIGH to LOW                   |      | 0.016 |       | 0.022 |          | 0.05  | ns/pF |  |

| d <sub>THLS</sub>  | Delta Delay vs. Load HIGH to LOW—<br>Low Slew      |      | 0.05  |       | 0.072 |          | 0.1   | ns/pF |  |

| 5.0 V TTL Ou       | tput Module Timing* (VCCI = 4.75 V)                |      |       |       |       |          |       |       |  |

| t <sub>DLH</sub>   | Data-to-Pad LOW to HIGH                            |      | 2.0   |       | 2.9   |          | 4.0   | ns    |  |

| t <sub>DHL</sub>   | Data-to-Pad HIGH to LOW                            |      | 2.6   |       | 3.7   |          | 5.2   | ns    |  |

| t <sub>DHLS</sub>  | Data-to-Pad HIGH to LOW—Low Slew                   |      | 6.8   |       | 9.7   |          | 13.6  | ns    |  |

| t <sub>ENZL</sub>  | Enable-to-Pad, Z to L                              |      | 1.9   |       | 2.7   |          | 3.8   | ns    |  |

| t <sub>ENZLS</sub> | Enable-to-Pad Z to L—Low Slew                      |      | 6.8   |       | 9.8   |          | 13.7  | ns    |  |

| t <sub>ENZH</sub>  | Enable-to-Pad, Z to H                              |      | 2.1   |       | 3.0   |          | 4.1   | ns    |  |

| t <sub>ENLZ</sub>  | Enable-to-Pad, L to Z                              |      | 3.3   |       | 4.8   |          | 6.6   | ns    |  |

Note: \*Delays based on 35 pF loading.

## **Pin Description**

#### CLKA/B Routed Clock A and B

These pins are clock inputs for clock distribution networks. Input levels are compatible with standard TTL or LVTTL specifications. The clock input is buffered prior to clocking the R-cells. If not used, this pin must be set LOW or HIGH on the board. It must not be left floating.

#### GND Ground

LOW supply voltage.

#### HCLK Dedicated (Hardwired) Array Clock

This pin is the clock input for sequential modules. Input levels are compatible with standard TTL or LVTTL specifications. This input is directly wired to each R-cell and offers clock speeds independent of the number of R-cells being driven. If not used, this pin must be set LOW or HIGH on the board. It must not be left floating.

#### I/O Input/Output

The I/O pin functions as an input, output, tristate, or bidirectional buffer. Based on certain configurations, input and output levels are compatible with standard TTL or LVTTL specifications. Unused I/O pins are automatically tristated by the Designer software.

#### LP Low Power Pin

Controls the low power mode of the eX devices. The device is placed in the low power mode by connecting the LP pin to logic HIGH. In low power mode, all I/Os are tristated, all input buffers are turned OFF, and the core of the device is turned OFF. To exit the low power mode, the LP pin must be set LOW. The device enters the low power mode 800 ns after the LP pin is driven to a logic HIGH. It will resume normal operation 200  $\mu$ s after the LP pin is driven to a logic LOW. LP pin should not be left floating. Under normal operating condition it should be tied to GND via 10 k $\Omega$  resistor.

#### NC No Connection

This pin is not connected to circuitry within the device. These pins can be driven to any voltage or can be left floating with no effect on the operation of the device.

#### PRA/PRB, I/O Probe A/B

The Probe pin is used to output data from any user-defined design node within the device. This diagnostic pin can be used independently or in conjunction with the other probe pin to allow real-time diagnostic output of any signal path within the device. The Probe pin can be used as a user-defined I/O when verification has been completed. The pin's probe capabilities can be permanently disabled to protect programmed design confidentiality.

#### TCK, I/O Test Clock

Test clock input for diagnostic probe and device programming. In flexible mode, TCK becomes active when the TMS pin is set LOW (refer to Table 1-4 on page 1-10). This pin functions as an I/O when the boundary scan state machine reaches the "logic reset" state.

#### TDI, I/O Test Data Input

Serial input for boundary scan testing and diagnostic probe. In flexible mode, TDI is active when the TMS pin is set LOW (refer to Table 1-4 on page 1-10). This pin functions as an I/O when the boundary scan state machine reaches the "logic reset" state.

#### TDO, I/O Test Data Output

Serial output for boundary scan testing. In flexible mode, TDO is active when the TMS pin is set LOW (refer to Table 1-4 on page 1-10). This pin functions as an I/O when the boundary scan state machine reaches the "logic reset" state. When Silicon Explorer is being used, TDO will act as an output when the "checksum" command is run. It will return to user I/O when "checksum" is complete.

# 2 – Package Pin Assignments

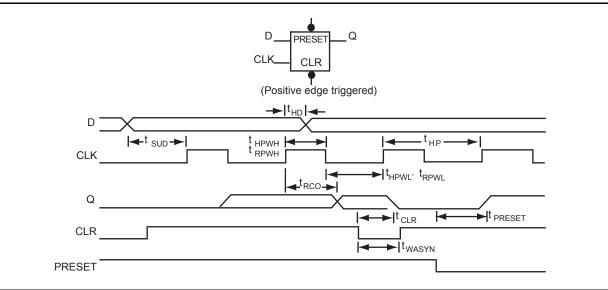

## **TQ64**

Note: For Package Manufacturing and Environmental information, visit Resource center at www.microsemi.com/soc/products/rescenter/package/index.html.

Datasheet Information

| Revision            | Changes                                                                                                                                                         | Page                   |  |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--|--|

| v4.0<br>(continued) | The "Flexible Mode" section was updated.                                                                                                                        | 1-10                   |  |  |

|                     | Table 1-5 •Boundary-Scan Pin Configurations and Functions is new.                                                                                               | 1-11                   |  |  |

|                     | The "TRST Pin" section was updated.                                                                                                                             | 1-11                   |  |  |

|                     | The "Probing Capabilities" section is new.                                                                                                                      | 1-12                   |  |  |

|                     | The "Programming" section was updated.                                                                                                                          | 1-12                   |  |  |

|                     | The "Probing Capabilities" section was updated.                                                                                                                 | 1-12                   |  |  |

|                     | The "Silicon Explorer II Probe" section was updated.                                                                                                            | 1-12                   |  |  |

|                     | The "Design Considerations" section was updated.                                                                                                                |                        |  |  |

|                     | The "Development Tool Support" section was updated.                                                                                                             | 1-13                   |  |  |

|                     | The "Absolute Maximum Ratings*" section was updated.                                                                                                            |                        |  |  |

|                     | The "Temperature and Voltage Derating Factors" section was updated.                                                                                             | 1-26                   |  |  |

|                     | The "TDI, I/O Test Data Input" section was updated.                                                                                                             | 1-31                   |  |  |

|                     | The "TDO, I/O Test Data Output" section was updated.                                                                                                            | 1-31                   |  |  |

|                     | The "TMS Test Mode Select" section was updated.                                                                                                                 | 1-32                   |  |  |

|                     | The "TRST, I/O Boundary Scan Reset Pin" section was updated.                                                                                                    | 1-32                   |  |  |

|                     | All VSV pins were changed to VCCA. The change affected the following pins:                                                                                      |                        |  |  |

|                     | 64-Pin TQFP – Pin 36                                                                                                                                            |                        |  |  |

|                     | 100-Pin TQFP – Pin 57                                                                                                                                           |                        |  |  |

|                     | 49-Pin CSP – Pin D5                                                                                                                                             |                        |  |  |

|                     | 128-Pin CSP-Pin H11 and Pin J1 for eX256                                                                                                                        |                        |  |  |

|                     | 180-Pin CSP – Pins J12 and K2                                                                                                                                   |                        |  |  |

| v3.0                | The "Recommended Operating Conditions" section has been changed.                                                                                                | 1-16                   |  |  |

|                     | The "3.3 V LVTTL Electrical Specifications" section has been updated.                                                                                           | 1-18                   |  |  |

|                     | The "5.0 V TTL Electrical Specifications" section has been updated.                                                                                             | 1-18                   |  |  |

|                     | The "Total Dynamic Power (mW)" section is new.                                                                                                                  | 1-9                    |  |  |

|                     | The "System Power at 5%, 10%, and 15% Duty Cycle" section is new.                                                                                               | 1-9                    |  |  |

|                     | The "eX Timing Model" section has been updated.                                                                                                                 | 1-22                   |  |  |

| v2.0.1              | The I/O Features table, Table 1-2 on page 1-6, was updated.                                                                                                     | 1-6                    |  |  |

|                     | The table, "Standby Power of eX Devices in LP Mode Typical Conditions, VCCA, VCCI = $2.5 \text{ V}$ , TJ = $25^{\circ} \text{ C}$ " section, was updated.       | 1-7                    |  |  |

|                     | "Typical eX Standby Current at 25°C" section is a new table.                                                                                                    | 1-16                   |  |  |

|                     | The table in the section, "Package Thermal Characteristics" section has been updated for the 49-Pin CSP.                                                        | 1-21                   |  |  |

|                     | The "eX Timing Model" section has been updated.                                                                                                                 | 1-22                   |  |  |

|                     | The timing numbers found in, "eX Family Timing Characteristics" section have been updated.                                                                      | 1-27                   |  |  |

|                     | The V <sub>SV</sub> pin has been added to the "Pin Description" section.                                                                                        | 1-31                   |  |  |

|                     | Please see the following pin tables for the V <sub>SV</sub> pin and an important footnote including the pin: "TQ64", "TQ100", "128-Pin CSP", and "180-Pin CSP". | 2-1, 2-3,<br>2-6, 2-11 |  |  |

|                     | The figure, "TQ64" section has been updated.                                                                                                                    | 2-1                    |  |  |

| Revision     | Changes                                                                                                                                                                                                                     | Page            |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Advance v0.4 | In the Product Profile, the Maximum User I/Os for eX64 was changed to 84.                                                                                                                                                   | 1-I             |

|              | In the Product Profile table, the Maximum User I/Os for eX128 was changed to 100.                                                                                                                                           | 1-I             |

| Advance v0.3 | The Mechanical Drawings section has been removed from the data sheet. The mechanical drawings are now contained in a separate document, "Package Characteristics and Mechanical Drawings," available on the Actel web site. |                 |

|              | A new section describing "Clock Resources"has been added.                                                                                                                                                                   |                 |

|              | A new table describing "I/O Features"has been added.                                                                                                                                                                        | 1-6             |

|              | The "Pin Description" section has been updated and clarified.                                                                                                                                                               | 1-31            |

|              | The original Electrical Specifications table was separated into two tables (2.5V and 3.3/5.0V). In both tables, several different currents are specified for $V_{OH}$ and $V_{OL}$ .                                        | Page 8<br>and 9 |

|              | A new table listing 2.5V low power specifications and associated power graphs were added.                                                                                                                                   | page 9          |

|              | Pin functions for eX256 TQ100 have been added to the "TQ100"table.                                                                                                                                                          | 2-3             |

|              | A CS49 pin drawing and pin assignment table including eX64 and eX128 pin functions have been added.                                                                                                                         | page 26         |

|              | A CS128 pin drawing and pin assignment table including eX64, eX128, and eX256 pin functions have been added.                                                                                                                | pages<br>26-27  |

|              | A CS180 pin drawing and pin assignment table for eX256 pin functions have been added.                                                                                                                                       | pages 27<br>31  |

| Advance v0.2 | The following table note was added to the eX Timing Characteristics table for<br>clarification: Clock skew improves as the clock network becomes more heavily loaded.                                                       | pages<br>14-15  |