Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                  |

|----------------------------|------------------------------------------------------------------|

| Product Status             | Active                                                           |

| Core Processor             | XCore                                                            |

| Core Size                  | 32-Bit 16-Core                                                   |

| Speed                      | 1000MIPS                                                         |

| Connectivity               | Configurable                                                     |

| Peripherals                |                                                                  |

| Number of I/O              | 73                                                               |

| Program Memory Size        | 128KB (32K x 32)                                                 |

| Program Memory Type        | SRAM                                                             |

| EEPROM Size                | -                                                                |

| RAM Size                   | -                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                        |

| Data Converters            | A/D 8x12b                                                        |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                  |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 217-LFBGA                                                        |

| Supplier Device Package    | 217-FBGA (16x16)                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/xmos/xs1-u16a-128-fb217-c10 |

#### TO OUR VALUED CUSTOMERS

It is our intention to provide you with accurate and comprehensive documentation for the hardware and software components used in this product. To subscribe to receive updates, visit <a href="http://www.xmos.com/">http://www.xmos.com/</a>.

XMOS Ltd. is the owner or licensee of the information in this document and is providing it to you "AS IS" with no warranty of any kind, express or implied and shall have no liability in relation to its use. XMOS Ltd. makes no representation that the information, or any particular implementation thereof, is or will be free from any claims of infringement and again, shall have no liability in relation to any such claims.

XMOS and the XMOS logo are registered trademarks of XMOS Ltd in the United Kingdom and other countries, and may not be used without written permission. Company and product names mentioned in this document are the trademarks or registered trademarks of their respective owners.

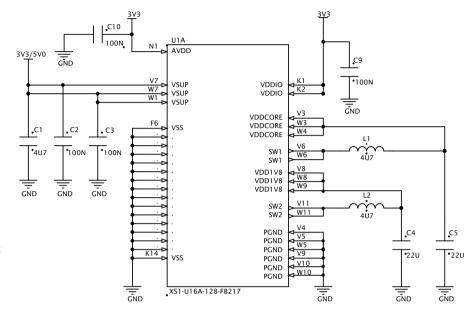

# 5 Example Application Diagram

Figure 2: Simplified Reference Schematic

have the appropriate frequency and accuracy. If desired, an external oscillator can be used on the XI/CLK input pin, this must be a 1.8 V oscillator.

- ▶ A 20 MHz silicon oscillator. This enables the device to boot and execute code without requiring an external crystal. The silicon oscillator is not as accurate as an external crystal.

- ▶ A 31,250 Hz oscillator. This enables the real-time counter to operate whilst the device is in low-power mode. This oscillator is not as accurate as an external crystal.

The oscillator can be controlled through package pins, a set of peripheral registers, and a digital node control register.

A package pin OSC\_EXT\_N is used to select the oscillator to use on boot. It must be grounded to select an external resonator or connected to VDDIO to select the on-chip 20 MHz oscillator. If an external resonator is used, then it must be in the range 5-100 MHz. If the USB PHY is used, then an external crystal (12 or 24 MHz) or an external oscillator (12, 24, 48, or 96 MHz) is required in order to provide a stable USB clock. Two more package pins, MODE0 and MODE1 are used to inform the node of the frequency.

The analog node runs at the frequency provided by the oscillator. Hence, increasing the clock frequency will speed up operation of the analog node, and will speed up communicating data with the digital node. The digital node has a PLL.

The PLL creates a high-speed clock that is used for the switch, tile, and reference clock.

The PLL multiplication value is selected through the two MODE pins, and can be changed by software to speed up the tile or use less power. The MODE pins are set as shown in Figure 8:

Figure 8: PLL multiplier values and MODE pins

| Oscillator | or MODE |   | Tile           | PLL Ratio | PLL | setting | gs |

|------------|---------|---|----------------|-----------|-----|---------|----|

| Frequency  | 1       | 0 | Frequency      |           | OD  | F       | R  |

| 5-13 MHz   | 0       | 0 | 130-399.75 MHz | 30.75     | 1   | 122     | 0  |

| 13-20 MHz  | 1       | 1 | 260-400.00 MHz | 20        | 2   | 119     | 0  |

| 20-48 MHz  | 1       | 0 | 167-400.00 MHz | 8.33      | 2   | 49      | 0  |

| 48-100 MHz | 0       | 1 | 196-400.00 MHz | 4         | 2   | 23      | 0  |

Figure 8 also lists the values of OD, F and R, which are the registers that define the ratio of the tile frequency to the oscillator frequency:

$$F_{core} = F_{osc} \times \frac{F+1}{2} \times \frac{1}{R+1} \times \frac{1}{OD+1}$$

OD, F and R must be chosen so that  $0 \le R \le 63$ ,  $0 \le F \le 4095$ ,  $0 \le OD \le 7$ , and  $260MHz \le F_{osc} \times \frac{F+1}{2} \times \frac{1}{R+1} \le 1.3 GHz$ . The OD, F, and R values can be modified by writing to the digital node PLL configuration register.

The MODE pins must be held at a static value during and after deassertion of the system reset.

#### 11 USB PHY

The USB PHY provides High-Speed and Full-Speed, device, host, and on-the-go functionality. The PHY is configured through a set of peripheral registers (Appendix F), and data is communicated through ports on the digital node. A library, libxud\_s.a, is provided to implement USB device functionality.

### 11.1 Logical Core Requirements

The XMOS XUD software component runs in a single logical core with endpoint and application cores communicating with it via a combination of channel communication and shared memory variables.

Each IN (host requests data from device) or OUT (data transferred from host to device) endpoint requires one logical core.

To guarantee correct operation the USB logical core must run at at least 80 MIPS, and the logical cores that communicate with the USB core must also run at 80 MIPS. This means that no more than six logical cores execute at any one time on a 500MHz device.

## 12 Analog-to-Digital Converter

The device has a 12-bit 1MSample/second Successive Approximation Register (SAR) Analogue to Digital Converter (ADC). It has 8 input pins which are multiplexed into the ADC. The sampling of the ADC is controlled using GPIO pin X0D24 that is triggered either by writing to port 1I, or by driving the pin externally. On each rising edge of the sample pin the ADC samples, holds and converts the data value from one of the analog input pins. Each of the 8 inputs can be enabled individually. Each of the enabled analog inputs is sampled in turn, on successive rising edges of the sample pin. The data is transmitted to the channel-end that the user configures during initialization of the ADC. Data is transmitted over the channel in individual packets, or in packets that contain multiple consecutive samples. The ADC uses an external reference voltage, nominally 3V3, which represents the full range of the ADC. The ADC configuration registers are documented in Appendix G.

The minimum latency for reading a value from the ADC into the xCORE register is shown in Figure 13:

Figure 13:

Minimum latency to read sample from ADC to xCORE

| Sample | Tile clock frequency | Start of packet | Subsequent samples |

|--------|----------------------|-----------------|--------------------|

| 32-bit | 500 MHz              | 840 ns          | 710 ns             |

| 32-bit | 400 MHz              | 870 ns          | 740 ns             |

| 16-bit | 500 MHz              | 770 ns          | 640 ns             |

| 16-bit | 400 MHz              | 800 ns          | 670 ns             |

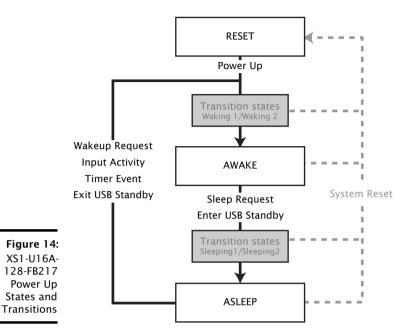

A transition from the ASLEEP state into the AWAKE state is instigated by a wakeup request triggered by a request from the USB block to exit standby mode an input, or a timer. The device only responds to a wakeup stimulus in the ASLEEP state. If wakeup stimulus occurs whilst transitioning from AWAKE to ASLEEP, the appropriate response occurs when the ASLEEP state is reached.

Configuration is through a set of registers documented in Appendix K.

### 14.3 Deep Sleep Modes and Real-Time Counter

The normal mode in which the XS1-U16A-128-FB217 operates is the AWAKE mode. In this mode, all cores, memory, and peripherals operate as normal. To save power, the XS1-U16A-128-FB217 can be put into a deep sleep mode, called ASLEEP, where the digital node is powered down, and most peripherals are powered down. The XS1-U16A-128-FB217 will stay in the ASLEEP mode until one of three conditions:

- 1. An external pin is asserted or deasserted (set by the program);

- 2. The 64-bit real-time counter reaches a value set by the program; or

- 3. The USB host (if USB is enabled) performs a wakeup.

When the chip is awake, the real-time counter counts the number of clock ticks on the oscillator. As such, the real-time counter will run at a fixed ratio, but synchronously with the 100 MHz timers on the xCORE Tile. When asleep, the real-time counter can be automatically switched to the 31,250 Hz silicon oscillator

0x11: Debug SPC

| Bits | Perm | Init | Description |

|------|------|------|-------------|

| 31:0 | DRW  |      | Value.      |

### B.13 Debug SSP: 0x12

This register contains the value of the SSP register when the debugger was called.

0x12: Debug SSP

| Bits | Perm | Init | Description |

|------|------|------|-------------|

| 31:0 | DRW  |      | Value.      |

### B.14 DGETREG operand 1: 0x13

The resource ID of the logical core whose state is to be read.

0x13: DGETREG operand 1

| Bits | Perm | Init | Description              |

|------|------|------|--------------------------|

| 31:8 | RO   | -    | Reserved                 |

| 7:0  | DRW  |      | Thread number to be read |

#### B.15 DGETREG operand 2: 0x14

Register number to be read by DGETREG

**0x14:** DGETREG operand 2

| Bits | Perm | Init | Description                |

|------|------|------|----------------------------|

| 31:5 | RO   | -    | Reserved                   |

| 4:0  | DRW  |      | Register number to be read |

### B.16 Debug interrupt type: 0x15

Register that specifies what activated the debug interrupt.

| Bits  | Perm | Init | Description                                                                                                                                                                                                                            |

|-------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:18 | RO   | -    | Reserved                                                                                                                                                                                                                               |

| 17:16 | DRW  |      | If the debug interrupt was caused by a hardware breakpoint or hardware watchpoint, this field contains the number of the breakpoint or watchpoint. If multiple breakpoints or watchpoints trigger at once, the lowest number is taken. |

| 15:8  | DRW  |      | If the debug interrupt was caused by a logical core, this field contains the number of that core. Otherwise this field is 0.                                                                                                           |

| 7:3   | RO   | -    | Reserved                                                                                                                                                                                                                               |

| 2:0   | DRW  | 0    | Indicates the cause of the debug interrupt  1: Host initiated a debug interrupt through JTAG  2: Program executed a DCALL instruction  3: Instruction breakpoint  4: Data watch point  5: Resource watch point                         |

0x15: Debug interrupt type

### B.17 Debug interrupt data: 0x16

On a data watchpoint, this register contains the effective address of the memory operation that triggered the debugger. On a resource watchpoint, it countains the resource identifier.

**0x16:** Debug interrupt data

| Bits | Perm | Init | Description |

|------|------|------|-------------|

| 31:0 | DRW  |      | Value.      |

## B.18 Debug core control: 0x18

This register enables the debugger to temporarily disable logical cores. When returning from the debug interrupts, the cores set in this register will not execute. This enables single stepping to be implemented.

0x18: Debug core control

| Bits | Perm | Init | Description                                                                                                                                                   |

|------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:8 | RO   | -    | Reserved                                                                                                                                                      |

| 7:0  | DRW  |      | 1-hot vector defining which logical cores are stopped when not<br>in debug mode. Every bit which is set prevents the respective<br>logical core from running. |

# C xCORE Tile Configuration

The xCORE Tile control registers can be accessed using configuration reads and writes (use write\_tile\_config\_reg(tileref, ...) and read\_tile\_config\_reg(tileref, ...) for reads and writes).

| Number    | Perm | Description                                    |

|-----------|------|------------------------------------------------|

| 0x00      | RO   | Device identification                          |

| 0x01      | RO   | xCORE Tile description 1                       |

| 0x02      | RO   | xCORE Tile description 2                       |

| 0x04      | CRW  | Control PSwitch permissions to debug registers |

| 0x05      | CRW  | Cause debug interrupts                         |

| 0x06      | RW   | xCORE Tile clock divider                       |

| 0x07      | RO   | Security configuration                         |

| 0x10 0x13 | RO   | PLink status                                   |

| 0x20 0x27 | CRW  | Debug scratch                                  |

| 0x40      | RO   | PC of logical core 0                           |

| 0x41      | RO   | PC of logical core 1                           |

| 0x42      | RO   | PC of logical core 2                           |

| 0x43      | RO   | PC of logical core 3                           |

| 0x44      | RO   | PC of logical core 4                           |

| 0x45      | RO   | PC of logical core 5                           |

| 0x46      | RO   | PC of logical core 6                           |

| 0x47      | RO   | PC of logical core 7                           |

| 0x60      | RO   | SR of logical core 0                           |

| 0x61      | RO   | SR of logical core 1                           |

| 0x62      | RO   | SR of logical core 2                           |

| 0x63      | RO   | SR of logical core 3                           |

| 0x64      | RO   | SR of logical core 4                           |

| 0x65      | RO   | SR of logical core 5                           |

| 0x66      | RO   | SR of logical core 6                           |

| 0x67      | RO   | SR of logical core 7                           |

| 0x80 0x9F | RO   | Chanend status                                 |

Figure 45: Summary

#### C.1 Device identification: 0x00

| Bits  | Perm | Init | Description                                             |

|-------|------|------|---------------------------------------------------------|

| 31:24 | RO   |      | Processor ID of this xCORE tile.                        |

| 23:16 | RO   |      | Number of the node in which this xCORE tile is located. |

| 15:8  | RO   |      | xCORE tile revision.                                    |

| 7:0   | RO   |      | xCORE tile version.                                     |

**0x00:**Device identification

### C.2 xCORE Tile description 1: 0x01

This register describes the number of logical cores, synchronisers, locks and channel ends available on this xCORE tile.

|   | Bits  | Perm | Init | Description              |

|---|-------|------|------|--------------------------|

| 3 | 31:24 | RO   |      | Number of channel ends.  |

| 2 | 23:16 | RO   |      | Number of locks.         |

|   | 15:8  | RO   |      | Number of synchronisers. |

|   | 7:0   | RO   | -    | Reserved                 |

0x01: xCORE Tile description 1

### C.3 xCORE Tile description 2: 0x02

This register describes the number of timers and clock blocks available on this  $xCORE\ tile.$

0x02: xCORE Tile description 2

| Bits  | Perm | Init | Description             |

|-------|------|------|-------------------------|

| 31:16 | RO   | -    | Reserved                |

| 15:8  | RO   |      | Number of clock blocks. |

| 7:0   | RO   |      | Number of timers.       |

## C.4 Control PSwitch permissions to debug registers: 0x04

This register can be used to control whether the debug registers (marked with permission CRW) are accessible through the tile configuration registers. When this bit is set, write -access to those registers is disabled, preventing debugging of the xCORE tile over the interconnect.

| Bits  | Perm | Init | Description                                                                                                    |

|-------|------|------|----------------------------------------------------------------------------------------------------------------|

| 31:26 | RO   | -    | Reserved                                                                                                       |

| 25:24 | RO   |      | 00 - ChannelEnd, 01 - ERROR, 10 - PSCTL, 11 - Idle.                                                            |

| 23:16 | RO   |      | Based on SRC_TARGET_TYPE value, it represents channelEnd ID or Idle status.                                    |

| 15:6  | RO   | -    | Reserved                                                                                                       |

| 5:4   | RO   |      | Two-bit network identifier                                                                                     |

| 3     | RO   | -    | Reserved                                                                                                       |

| 2     | RO   |      | 1 when the current packet is considered junk and will be thrown away.                                          |

| 1     | RO   | 0    | Set to 1 if the switch is routing data into the link, and if a route exists from another link.                 |

| 0     | RO   | 0    | Set to 1 if the link is routing data into the switch, and if a route is created to another link on the switch. |

0x10 .. 0x13: PLink status

## C.9 Debug scratch: 0x20 .. 0x27

A set of registers used by the debug ROM to communicate with an external debugger, for example over the switch. This is the same set of registers as the Debug Scratch registers in the processor status.

0x20 .. 0x27: Debug scratch

| Bits | Perm | Init | Description |

|------|------|------|-------------|

| 31:0 | CRW  |      | Value.      |

## C.10 PC of logical core 0: 0x40

Value of the PC of logical core 0.

0x40: PC of logical core 0

| Bits | Perm | Init | Description |

|------|------|------|-------------|

| 31:0 | RO   |      | Value.      |

| Bits  | Perm | Init | Description                                                 |

|-------|------|------|-------------------------------------------------------------|

| 31:28 | RW   | 0    | The direction for packets whose first mismatching bit is 7. |

| 27:24 | RW   | 0    | The direction for packets whose first mismatching bit is 6. |

| 23:20 | RW   | 0    | The direction for packets whose first mismatching bit is 5. |

| 19:16 | RW   | 0    | The direction for packets whose first mismatching bit is 4. |

| 15:12 | RW   | 0    | The direction for packets whose first mismatching bit is 3. |

| 11:8  | RW   | 0    | The direction for packets whose first mismatching bit is 2. |

| 7:4   | RW   | 0    | The direction for packets whose first mismatching bit is 1. |

| 3:0   | RW   | 0    | The direction for packets whose first mismatching bit is 0. |

**0x0C:** Directions 0-7

#### D.9 Directions 8-15: 0x0D

This register contains eight directions, for packets with a mismatch in bits 15..8 of the node-identifier. The direction in which a packet will be routed is goverened by the most significant mismatching bit.

| Bits  | Perm | Init | Description                                                  |

|-------|------|------|--------------------------------------------------------------|

| 31:28 | RW   | 0    | The direction for packets whose first mismatching bit is 15. |

| 27:24 | RW   | 0    | The direction for packets whose first mismatching bit is 14. |

| 23:20 | RW   | 0    | The direction for packets whose first mismatching bit is 13. |

| 19:16 | RW   | 0    | The direction for packets whose first mismatching bit is 12. |

| 15:12 | RW   | 0    | The direction for packets whose first mismatching bit is 11. |

| 11:8  | RW   | 0    | The direction for packets whose first mismatching bit is 10. |

| 7:4   | RW   | 0    | The direction for packets whose first mismatching bit is 9.  |

| 3:0   | RW   | 0    | The direction for packets whose first mismatching bit is 8.  |

0x0D: Directions 8-15

### D.10 DEBUG\_N configuration: 0x10

Configures the behavior of the DEBUG\_N pin.

| Bits | Perm | Init | Description                                                                          |

|------|------|------|--------------------------------------------------------------------------------------|

| 31:2 | RO   | -    | Reserved                                                                             |

| 1    | RW   | 0    | Set to 1 to enable signals on DEBUG_N to generate DCALL on the core.                 |

| 0    | RW   | 0    | When set to 1, the DEBUG_N wire will be pulled down when the node enters debug mode. |

0x10: DEBUG\_N configuration

#### D.11 Debug source: 0x1F

Contains the source of the most recent debug event.

| Bits | Perm | Init | Description                                                                        |

|------|------|------|------------------------------------------------------------------------------------|

| 31:5 | RO   | -    | Reserved                                                                           |

| 4    | RW   |      | If set, the external DEBUG_N pin is the source of the most recent debug interrupt. |

| 3:1  | RO   | -    | Reserved                                                                           |

| 0    | RW   |      | If set, the xCORE Tile is the source of the most recent debug interrupt.           |

**0x1F:** Debug source

### D.12 Link status, direction, and network: 0x20 .. 0x27

These registers contain status information for low level debugging (read-only), the network number that each link belongs to, and the direction that each link is part of. The registers control links C, D, A, B, G, H, E, and F in that order.

| Bits  | Perm | Init | Description                                                                                                                                                                  |

|-------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:26 | RO   | -    | Reserved                                                                                                                                                                     |

| 25:24 | RO   |      | If this link is currently routing data into the switch, this field specifies the type of link that the data is routed to: 0: plink 1: external link 2: internal control link |

| 23:16 | RO   | 0    | If the link is routing data into the switch, this field specifies the destination link number to which all tokens are sent.                                                  |

| 15:12 | RO   | -    | Reserved                                                                                                                                                                     |

| 11:8  | RW   | 0    | The direction that this this link is associated with; set for routing.                                                                                                       |

| 7:6   | RO   | -    | Reserved                                                                                                                                                                     |

| 5:4   | RW   | 0    | Determines the network to which this link belongs, set for quality of service.                                                                                               |

| 3     | RO   | -    | Reserved                                                                                                                                                                     |

| 2     | RO   | 0    | Set to 1 if the current packet is junk and being thrown away. A packet is considered junk if, for example, it is not routable.                                               |

| 1     | RO   | 0    | Set to 1 if the switch is routing data into the link, and if a route exists from another link.                                                                               |

| 0     | RO   | 0    | Set to 1 if the link is routing data into the switch, and if a route is created to another link on the switch.                                                               |

0x20 .. 0x27: Link status, direction, and network

#### D.13 PLink status and network: 0x40 ... 0x43

These registers contain status information and the network number that each processor-link belongs to.

| Bits  | Perm | Init | Description                                                                                                                                                                  |

|-------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:26 | RO   | -    | Reserved                                                                                                                                                                     |

| 25:24 | RO   |      | If this link is currently routing data into the switch, this field specifies the type of link that the data is routed to: 0: plink 1: external link 2: internal control link |

| 23:16 | RO   | 0    | If the link is routing data into the switch, this field specifies the destination link number to which all tokens are sent.                                                  |

| 15:6  | RO   | -    | Reserved                                                                                                                                                                     |

| 5:4   | RW   | 0    | Determines the network to which this link belongs, set for quality of service.                                                                                               |

| 3     | RO   | -    | Reserved                                                                                                                                                                     |

| 2     | RO   | 0    | Set to 1 if the current packet is junk and being thrown away. A packet is considered junk if, for example, it is not routable.                                               |

| 1     | RO   | 0    | Set to 1 if the switch is routing data into the link, and if a route exists from another link.                                                                               |

| 0     | RO   | 0    | Set to 1 if the link is routing data into the switch, and if a route is created to another link on the switch.                                                               |

0x40 .. 0x43: PLink status and network

## D.14 Link configuration and initialization: 0x80 .. 0x87

These registers contain configuration and debugging information specific to external links. The link speed and width can be set, the link can be initialized, and the link status can be monitored. The registers control links C, D, A, B, G, H, E, and F in that order.

0x04: Node configuration register

| Bits | Perm | Init | Description                                                                                          |

|------|------|------|------------------------------------------------------------------------------------------------------|

| 31   | RW   | 0    | Set to 1 to disable further updates to the node configuration and link control and status registers. |

| 30:1 | RO   | -    | Reserved                                                                                             |

| 0    | RW   | 0    | Header mode. 0: 3-byte headers; 1: 1-byte headers.                                                   |

#### E.3 Node identifier: 0x05

| 0x05:      |  |

|------------|--|

| Node       |  |

| identifier |  |

| Bits  | Perm | Init | Description                                                                                               |

|-------|------|------|-----------------------------------------------------------------------------------------------------------|

| 31:16 | RO   | -    | Reserved                                                                                                  |

| 15:0  | RW   | 0    | 16-bit node identifier. This does not need to be set, and is present for compatibility with XS1-switches. |

#### E.4 Reset and Mode Control: 0x50

The XS1-S has two main reset signals: a system-reset and an xCORE Tile-reset. System-reset resets the whole system including external devices, whilst xCORE Tile-reset resets the xCORE Tile(s) only. The resets are induced either by software (by a write to the register below) or by one of the following:

- \* External reset on RST\_N (System reset)

- \* Brown out on one of the power supplies (System reset)

- \* Watchdog timer (System reset)

- \* Sleep sequence (xCORE Tile reset)

- \* Clock source change (xCORE Tile reset)

The minimum system reset duration is achieved when the fastest permissible clock is used. The reset durations will be proportionately longer when a slower clock is used. Note that the minimum system reset duration allows for all power rails except the VOUT2 to turn off, and decay.

The length of the system reset comes from an internal counter, counting 524,288 oscillator clock cycles which gives the maximum time allowable for the supply rails to discharge. The system reset duration is a balance between leaving a long time for the supply rails to discharge, and a short time for the system to boot. Example reset times are 44 ms with a 12 MHz oscillator or 5.5 ms with a 96 MHz oscillator.

#### F.16 UIFM PHY control: 0x3C

| Bits  | Perm | Init | Description                                                                                                                                          |

|-------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:19 | RO   | -    | Reserved                                                                                                                                             |

| 18    | RW   | 0    | Set to 1 to disable pulldowns on ports 8A and 8B.                                                                                                    |

| 17:14 | RO   | -    | Reserved                                                                                                                                             |

| 13    | RW   | 0    | After an auto-resume, this bit is set to indicate that the resume signalling was for reset (se0). Set to 0 to clear.                                 |

| 12    | RW   | 0    | After an auto-resume, this bit is set to indicate that the resume signalling was for resume (K). Set to 0 to clear.                                  |

| 11:8  | RW   | 0    | Log-2 number of clocks before any linestate change is propagated.                                                                                    |

| 7     | RW   | 0    | Set to 1 to use the suspend controller handle to resume from suspend. Otherwise, the program has to poll the linestate_filt field in phy_teststatus. |

| 6:4   | RW   | 0    | Control the the conf1,2,3 input pins of the PHY.                                                                                                     |

| 3:0   | RO   | -    | Reserved                                                                                                                                             |

0x3C: UIFM PHY control

## **G** ADC Configuration

The device has a 12-bit Analogue to Digital Converter (ADC). It has multiple input pins, and on each positive clock edge on port 11, it samples and converts a value on the next input pin. The data is transmitted to a channel-end that must be set on enabling the ADC input pin.

The ADC is peripheral 2. The control registers are accessed using 32-bit reads and writes (use write\_periph\_32(device, 2, ...) and read\_periph\_32(device, 2, ...) for reads and writes).

| Number | Perm | Description             |

|--------|------|-------------------------|

| 0x00   | RW   | ADC Control input pin 0 |

| 0x04   | RW   | ADC Control input pin 1 |

| 0x08   | RW   | ADC Control input pin 2 |

| 0x0C   | RW   | ADC Control input pin 3 |

| 0x10   | RW   | ADC Control input pin 4 |

| 0x14   | RW   | ADC Control input pin 5 |

| 0x18   | RW   | ADC Control input pin 6 |

| 0x1C   | RW   | ADC Control input pin 7 |

| 0x20   | RW   | ADC General Control     |

Figure 49: Summary

#### G.1 ADC Control input pin 0: 0x00

Controls specific to ADC input pin 0.

| Bits | Perm | Init | Description                                                                                                                                                                      |

|------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:8 | RW   | 0    | The node and channel-end identifier to which data for this ADC input pin should be send to. This is the top 24 bits of the channel-end identifier as allocated on an xCORE Tile. |

| 7:1  | RO   | -    | Reserved                                                                                                                                                                         |

| 0    | RW   | 0    | Set to 1 to enable this input pin on the ADC.                                                                                                                                    |

0x00: ADC Control input pin 0

### G.2 ADC Control input pin 1: 0x04

Controls specific to ADC input pin 1.

| Bits | Perm | Init | Description                                                                                                                                                                      |

|------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:8 | RW   | 0    | The node and channel-end identifier to which data for this ADC input pin should be send to. This is the top 24 bits of the channel-end identifier as allocated on an xCORE Tile. |

| 7:1  | RO   | -    | Reserved                                                                                                                                                                         |

| 0    | RW   | 0    | Set to 1 to enable this input pin on the ADC.                                                                                                                                    |

0x04: ADC Control input pin 1

### G.3 ADC Control input pin 2: 0x08

Controls specific to ADC input pin 2.

| Bits | Perm | Init | Description                                                                                                                                                                      |

|------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:8 | RW   | 0    | The node and channel-end identifier to which data for this ADC input pin should be send to. This is the top 24 bits of the channel-end identifier as allocated on an xCORE Tile. |

| 7:1  | RO   | -    | Reserved                                                                                                                                                                         |

| 0    | RW   | 0    | Set to 1 to enable this input pin on the ADC.                                                                                                                                    |

0x08: ADC Control input pin 2

### G.4 ADC Control input pin 3: 0x0C

Controls specific to ADC input pin 3.

#### I.1 General oscillator control: 0x00

| Bits | Perm | Init | Description                                                                                                   |

|------|------|------|---------------------------------------------------------------------------------------------------------------|

| 7:2  | RO   | -    | Reserved                                                                                                      |

| 1    | RW   | 0    | Set to 1 to reset the xCORE Tile when the value of the oscillator select control register (bit 0) is changed. |

| 0    | RW   | pin  | Selects the oscillator to use: 0: Crystal oscillator 1: On-silicon oscillator                                 |

0x00: General oscillator control

#### I.2 On-silicon-oscillator control: 0x01

This register controls the on-chip logic that implements an on-chip oscillator. The on-chip oscillator does not require an external crystal, but does not provide an accurate timing source. The nominal frequency of the on-silicon-oscillator is given below, but the actual frequency are temperature, voltage, and chip dependent.

0x01: On-siliconoscillator control

| Bits | Perm | Init | Description                                                                                                                           |

|------|------|------|---------------------------------------------------------------------------------------------------------------------------------------|

| 7:2  | RO   | -    | Reserved                                                                                                                              |

| 1    | RW   | 0    | Selects the clock speed of the on-chip oscillator:<br>0: approximately 20 Mhz (fast clock)<br>1: approximately 31,250 Hz (slow clock) |

| 0    | RW   | 1    | Set to 0 to disable the on-chip oscillator. Do not do this unless the xCORE Tile is running off the crystal oscillator.               |

### I.3 Crystal-oscillator control: 0x02

This register controls the on-chip logic that implements the crystal oscillator; the crystal-oscillator requires an external crystal.

**0x02:** Crystaloscillator control

| Bits | Perm | Init | Description                                                                                                                          |

|------|------|------|--------------------------------------------------------------------------------------------------------------------------------------|

| 7:2  | RO   | -    | Reserved                                                                                                                             |

| 1    | RW   | 1    | Set to 0 to disable the crystal bias circuit. Only switch the bias off if an external oscillator rather than a crystal is connected. |

| 0    | RW   | 1    | Set to 0 to disable the crystal oscillator. Do not do this unless the xCORE Tile is running off the on-silicon oscillator.           |

## J Real time clock Configuration

The Real time clock is peripheral 5. The control registers are accessed using 32-bit reads and writes (use write\_periph\_32(device, 5, ...) and read\_periph\_32(device, 5, ...) for reads and writes).

Figure 52: Summary

| Number | Perm | Description                                 |

|--------|------|---------------------------------------------|

| 0x00   | RW   | Real time counter least significant 32 bits |

| 0x04   | RW   | Real time counter most significant 32 bits  |

### J.1 Real time counter least significant 32 bits: 0x00

This registers contains the lower 32-bits of the real-time counter.

0x00: Real time counter least significant 32 bits

| Bits | Perm | Init | Description                                     |

|------|------|------|-------------------------------------------------|

| 31:0 | RO   | 0    | Least significant 32 bits of real-time counter. |

## J.2 Real time counter most significant 32 bits: 0x04

This registers contains the upper 32-bits of the real-time counter.

0x04: Real time counter most significant 32 bits

| Bits | Perm | Init | Description                                    |

|------|------|------|------------------------------------------------|

| 31:0 | RO   | 0    | Most significant 32 bits of real-time counter. |

# K Power control block Configuration

The *Power control block* is peripheral 6. The control registers are accessed using 32-bit reads and writes (use write\_periph\_32(device, 6, ...) and read\_periph\_32(

→ device, 6, ...) for reads and writes).

| Bits  | Perm | Init | Description                                                                                                                    |

|-------|------|------|--------------------------------------------------------------------------------------------------------------------------------|

| 31:21 | RO   | -    | Reserved                                                                                                                       |

| 20:16 | RW   | 16   | Log2 number of cycles to stay in this state: 0: 1 clock cycles 1: 2 clock cycles 2: 4 clock cycles 31: 2147483648 clock cycles |

| 15    | RO   | -    | Reserved                                                                                                                       |

| 14    | RW   | 0    | Set to 1 to disable clock to the xCORE Tile.                                                                                   |

| 13:10 | RO   | -    | Reserved                                                                                                                       |

| 9     | RW   | 0    | Sets modulation used by DCDC2:<br>0: PWM modulation (max 475 mA)<br>1: PFM modulation (max 50 mA)                              |

| 8     | RW   | 0    | Sets modulation used by DCDC1: 0: PWM modulation (max 700 mA) 1: PFM modulation (max 50 mA)                                    |

| 7:6   | RO   | -    | Reserved                                                                                                                       |

| 5     | RW   | 1    | Set to 1 to enable VOUT6 (IO supply).                                                                                          |

| 4     | RW   | 1    | Set to 1 to enable LDO5 (core PLL supply).                                                                                     |

| 3:2   | RO   | -    | Reserved                                                                                                                       |

| 1     | RO   | 1    | Set to 1 to enable DCDC2 (analogue supply).                                                                                    |

| 0     | RW   | 1    | Set to 1 to enable DCDC1 (core supply).                                                                                        |

0x14: Power supply states whilst WAKING2

## K.7 Power supply states whilst AWAKE: 0x18

This register controls what state the power control block should be in when in the AWAKE state.

| Bits  | Perm | Init | Description                                                                                                                    |

|-------|------|------|--------------------------------------------------------------------------------------------------------------------------------|

| 31:21 | RO   | -    | Reserved                                                                                                                       |

| 20:16 | RW   | 16   | Log2 number of cycles to stay in this state: 0: 1 clock cycles 1: 2 clock cycles 2: 4 clock cycles 31: 2147483648 clock cycles |

| 15    | RO   | -    | Reserved                                                                                                                       |

| 14    | RW   | 0    | Set to 1 to disable clock to the xCORE Tile.                                                                                   |

| 13:10 | RO   | -    | Reserved                                                                                                                       |

| 9     | RW   | 0    | Sets modulation used by DCDC2:<br>0: PWM modulation (max 475 mA)<br>1: PFM modulation (max 50 mA)                              |

| 8     | RW   | 0    | Sets modulation used by DCDC1:<br>0: PWM modulation (max 700 mA)<br>1: PFM modulation (max 50 mA)                              |

| 7:6   | RO   | -    | Reserved                                                                                                                       |

| 5     | RW   | 0    | Set to 1 to enable VOUT6 (IO supply).                                                                                          |

| 4     | RW   | 0    | Set to 1 to enable LDO5 (core PLL supply).                                                                                     |

| 3:2   | RO   | -    | Reserved                                                                                                                       |

| 1     | RO   | 1    | Set to 1 to enable DCDC2 (analogue supply).                                                                                    |

| 0     | RW   | 0    | Set to 1 to enable DCDC1 (core supply).                                                                                        |

0x20: Power supply states whilst SLEEPING2

## K.10 Power sequence status: 0x24

This register defines the current status of the power supply controller.