# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                  |

|----------------------------|------------------------------------------------------------------|

| Product Status             | Active                                                           |

| Core Processor             | XCore                                                            |

| Core Size                  | 32-Bit 16-Core                                                   |

| Speed                      | 1000MIPS                                                         |

| Connectivity               | Configurable                                                     |

| Peripherals                | -                                                                |

| Number of I/O              | 73                                                               |

| Program Memory Size        | 128KB (32K x 32)                                                 |

| Program Memory Type        | SRAM                                                             |

| EEPROM Size                | -                                                                |

| RAM Size                   | -                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                        |

| Data Converters            | A/D 8x12b                                                        |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 217-LFBGA                                                        |

| Supplier Device Package    | 217-FBGA (16x16)                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/xmos/xs1-u16a-128-fb217-i10 |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3 Pin Configuration

|   | 1                       | 2           | 3       | 4       | 5     | 6            | 7     | 8      | 9      | 10    | 11           | 12    | 13    | 14    | 15    | 16    | 17          | 18             | 19    |

|---|-------------------------|-------------|---------|---------|-------|--------------|-------|--------|--------|-------|--------------|-------|-------|-------|-------|-------|-------------|----------------|-------|

| A | X1D05                   | X1D06       | x1D07   | x1D08   | X1D09 | X1D10        | X1D11 | X1D12  | X1D13  | X1D14 | X1D15        | X1D16 | X1D17 | x1D18 | X1D19 | X1D20 | 40<br>X1D21 | X1D22          | x1D23 |

| в | x1D04                   | x1D53       | X1D54   | x1D55   | X1D56 | x1D57        | X1D58 | X1D61  | X1D62  | x1D63 | 22A<br>X1D64 | x1D65 | X1D66 | X1D67 | X1D68 | X1D69 | x1D70       | X1D24          | X1D25 |

| с | x1D03                   | x1D52       |         |         |       |              |       |        |        |       |              |       |       |       |       |       |             | X1D26          | X1D27 |

| D | X1D02                   | X1D51       |         |         |       |              |       |        |        |       |              |       |       |       |       |       |             | x1033          | X1D32 |

| E | X1D01                   | x1D50       |         |         |       |              |       |        |        |       |              |       |       |       |       |       |             | X1D35          | X1D34 |

| F | X1D00                   | X1D49       |         |         |       | GND          | GND   | GND    | GND    | GND   | GND          | GND   | GND   | GND   |       |       |             | VDDIO_<br>OUT- | X1D36 |

| G | USB_<br>DN <sup>_</sup> | USB<br>VBUS |         |         |       | GND          | GND   | GND    | GND    | GND   | GND          | GND   | GND   | GND   |       |       |             | MODE[4]        | X1D37 |

| н | USB_<br>DP              | USB_<br>ID  |         |         |       | GND          | GND   | GND    | GND    | GND   | GND          | GND   | GND   | GND   |       |       |             | MODE[3]        | X1D38 |

| J | X0D43/<br>WAKE          | RST_N       |         |         |       | GND          | GND   | GND    | GND    | GND   | GND          | GND   | GND   | GND   |       |       |             | MODE[2]        | X1D39 |

| к | VDDIO                   | VDDIO       |         |         |       | GND          | GND   | GND    | GND    | GND   | GND          | GND   | GND   | GND   |       |       |             | MODE[1]        | TDO   |

| L | ADC6                    | ADC7        |         |         |       | OSC<br>EXT_N | GND   | GND    | GND    | GND   | GND          | GND   | GND   | GND   |       |       |             | MODE[0]        | тск   |

| м | ADC4                    | ADC5        |         |         |       | NC           | NC    | GND    | GND    | GND   | GND          | GND   | GND   | GND   |       |       |             | DEBUG_<br>N    | TMS   |

| N | AVDD                    | AVSS        |         |         |       | NC           | NC    | GND    | GND    | GND   | GND          | GND   | GND   | GND   |       |       |             | NC             | TDI   |

| Р | ADC2                    | ADC3        |         |         |       | AVSS         | GND   | GND    | GND    | GND   | GND          | GND   | GND   | GND   |       |       |             | NC             | X0D35 |

| R | ADC0                    | ADC1        |         |         |       |              |       |        |        |       |              |       |       |       |       |       |             | NC             | X0D00 |

| т | NC                      | NC          |         |         |       |              |       |        |        |       |              |       |       |       |       |       |             | NC             | X0D01 |

| U | XV<br>CLK               | NC          |         |         |       |              |       |        |        |       |              |       |       |       |       |       |             | NC             | X0D10 |

| v | хо                      | NC          | VDDCORE | PGND    | PGND  | SW1          | VSUP  | VDD1V8 | PGND   | PGND  | SW2          | NC    | X0D24 | X0D21 | X0D19 | X0D17 | X0D15       | NC             | X0D11 |

| w | VSUP                    | NC          | VDDCORE | VDDCORE | PGND  | SW1          | VSUP  | VDD1V8 | VDD1V8 | PGND  | SW2          | NC    | X0D22 | X0D20 | X0D18 | X0D16 | X0D14       | X0D13          | X0D12 |

| Signal   | Function                       | Туре   | Properties |

|----------|--------------------------------|--------|------------|

| USB_DP   | USB Serial Data                | I/O    |            |

| USB_ID   | USB Device ID (OTG) - Reserved | Output |            |

| USB_VBUS | USB Power Detect Pin           | Input  |            |

|           | Clocks pins (4)                |        |            |  |  |  |  |  |  |  |

|-----------|--------------------------------|--------|------------|--|--|--|--|--|--|--|

| Signal    | Function                       | Туре   | Properties |  |  |  |  |  |  |  |

| MODE[4:0] | Boot mode select               | Input  | PU, ST     |  |  |  |  |  |  |  |

| OSC_EXT_N | Use Silicon Oscillator         | Input  | ST         |  |  |  |  |  |  |  |

| XI/CLK    | Crystal Oscillator/Clock Input | Input  |            |  |  |  |  |  |  |  |

| хо        | Crystal Oscillator Output      | Output |            |  |  |  |  |  |  |  |

|         | JTAG pins (5)    |        |            |  |  |  |  |  |  |

|---------|------------------|--------|------------|--|--|--|--|--|--|

| Signal  | Function         | Туре   | Properties |  |  |  |  |  |  |

| DEBUG_N | Multi-chip debug | I/O    | PU         |  |  |  |  |  |  |

| ТСК     | Test clock       | Input  | PU, ST     |  |  |  |  |  |  |

| TDI     | Test data input  | Input  | PU, ST     |  |  |  |  |  |  |

| TDO     | Test data output | Output | PD, OT     |  |  |  |  |  |  |

| TMS     | Test mode select | Input  | PU, ST     |  |  |  |  |  |  |

|        | Misc pins (1)      |       |            |  |  |  |  |

|--------|--------------------|-------|------------|--|--|--|--|

| Signal | Function           | Туре  | Properties |  |  |  |  |

| RST_N  | Global reset input | Input | PU, ST     |  |  |  |  |

|        | I/O pins (74)                                                                                      |      |                                  |

|--------|----------------------------------------------------------------------------------------------------|------|----------------------------------|

| Signal | Function                                                                                           | Туре | Properties                       |

| X0D00  | 1A <sup>0</sup>                                                                                    | I/O  | PD <sub>S</sub> , R <sub>S</sub> |

| X0D01  | 1 B <sup>0</sup>                                                                                   | I/O  | PD <sub>S</sub> , R <sub>S</sub> |

| X0D10  | 1C <sup>0</sup>                                                                                    | I/O  | PD <sub>S</sub> , R <sub>S</sub> |

| X0D11  | 1D <sup>0</sup>                                                                                    | I/0  | PD <sub>S</sub> , R <sub>S</sub> |

| X0D12  | 1 E <sup>0</sup>                                                                                   | I/0  | PDs                              |

| X0D13  | XLB <sup>4</sup> <sub>out</sub> 1F <sup>0</sup>                                                    | I/O  | PDs                              |

| X0D14  | XLB <sup>3</sup> <sub>out</sub> 4C <sup>0</sup> 8B <sup>0</sup> 16A <sup>8</sup> 32A <sup>28</sup> | I/O  | PDs                              |

| X0D15  | XLB <sup>2</sup> <sub>out</sub> 4C <sup>1</sup> 8B <sup>1</sup> 16A <sup>9</sup> 32A <sup>29</sup> | I/O  | PDs                              |

| X0D16  | $XLB_{out}^{1}$ $4D^{0}$ $8B^{2}$ 16A <sup>10</sup>                                                | I/0  | PDs                              |

| X0D17  | XLB <sup>0</sup> <sub>out</sub> 4D <sup>1</sup> 8B <sup>3</sup> 16A <sup>11</sup>                  | I/O  | PDs                              |

| X0D18  | XLB <sup>0</sup> <sub>in</sub> 4D <sup>2</sup> 8B <sup>4</sup> 16A <sup>12</sup>                   | I/O  | PDs                              |

| X0D19  | XLB <sup>1</sup> <sub>in</sub> 4D <sup>3</sup> 8B <sup>5</sup> 16A <sup>13</sup>                   | I/O  | PDs                              |

| X0D20  | XLB <sup>2</sup> <sub>in</sub> 4C <sup>2</sup> 8B <sup>6</sup> 16A <sup>14</sup> 32A <sup>30</sup> | I/0  | PDs                              |

(continued)

| Feature              | Bit  | Description                                                                                                                                                                                                                                |

|----------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Disable JTAG         | 0    | The JTAG interface is disabled, making it impossible<br>for the tile state or memory content to be accessed<br>via the JTAG interface.                                                                                                     |

| Disable Link access  | 1    | Other tiles are forbidden access to the processor state<br>via the system switch. Disabling both JTAG and Link<br>access transforms an xCORE Tile into a "secure island"<br>with other tiles free for non-secure user application<br>code. |

| Secure Boot          | 5    | The processor is forced to boot from address 0 of the OTP, allowing the processor boot ROM to be bypassed (see §9).                                                                                                                        |

| Redundant rows       | 7    | Enables redundant rows in OTP.                                                                                                                                                                                                             |

| Sector Lock 0        | 8    | Disable programming of OTP sector 0.                                                                                                                                                                                                       |

| Sector Lock 1        | 9    | Disable programming of OTP sector 1.                                                                                                                                                                                                       |

| Sector Lock 2        | 10   | Disable programming of OTP sector 2.                                                                                                                                                                                                       |

| Sector Lock 3        | 11   | Disable programming of OTP sector 3.                                                                                                                                                                                                       |

| OTP Master Lock      | 12   | Disable OTP programming completely: disables up<br>dates to all sectors and security register.                                                                                                                                             |

| Disable JTAG-OTP     | 13   | Disable all (read & write) access from the JTAG inter face to this OTP.                                                                                                                                                                    |

| Disable Global Debug | 14   | Disables access to the DEBUG_N pin.                                                                                                                                                                                                        |

|                      | 2115 | General purpose software accessable security register available to end-users.                                                                                                                                                              |

|                      | 3122 | General purpose user programmable JTAG UserID code extension.                                                                                                                                                                              |

Figure 12: Security register features

port with resource ID 0x200100, and the OTP control is on a 16-bit port with ID 0x100300. Programming is performed through libotp and xburn.

### 10.2 SRAM

Each xCORE Tile integrates a single 64KBSRAM bank for both instructions and data. All internal memory is 32 bits wide, and instructions are either 16-bit or 32-bit. Byte (8-bit), half-word (16-bit) or word (32-bit) accesses are supported and are executed within one tile clock cycle. There is no dedicated external memory interface, although data memory can be expanded through appropriate use of the ports.

### 10.3 Deep Sleep Memory

The XS1-U16A-128-FB217 device includes 128 bytes of deep sleep memory for state storage during sleep mode. Deep sleep memory is volatile and if device input power is remove, the data will be lost.

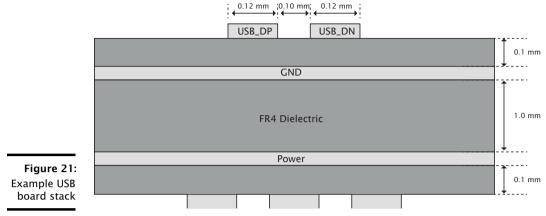

For best results, most of the routing should be done on the top layer (assuming the USB connector and XS1-U16A-128-FB217 are on the top layer) closest to GND. Reference planes should be below the transmission lines in order to maintain control of the trace impedance.

We recommend that the high-speed clock and high-speed USB differential pairs are routed first before any other routing. When routing high speed USB signals, the following guidelines should be followed:

- ▶ High speed differential pairs should be routed together.

- ▶ High-speed USB signal pair traces should be trace-length matched. Maximum trace-length mismatch should be no greater than 4mm.

- Ensure that high speed signals (clocks, USB differential pairs) are routed as far away from off-board connectors as possible.

- ▶ High-speed clock and periodic signal traces that run parallel should be at least 1.27mm away from USB\_DP/USB\_DN (see Figure 20).

- Low-speed and non-periodic signal traces that run parallel should be at least 0.5mm away from USB\_DP/USB\_DN (see Figure 20).

- ▶ Route high speed USB signals on the top of the PCB wherever possible.

- Route high speed USB traces over continuous power planes, with no breaks. If a trade-off must be made, changing signal layers is preferable to crossing plane splits.

- Follow the  $20 \times h$  rule; keep traces  $20 \times h$  (the height above the power plane) away from the edge of the power plane.

- ▶ Use a minimum of vias in high speed USB traces.

29

- Avoid corners in the trace. Where necessary, rather than turning through a 90 degree angle, use two 45 degree turns or an arc.

- DO NOT route USB traces near clock sources, clocked circuits or magnetic devices.

- Avoid stubs on high speed USB signals.

#### 16.3 Land patterns and solder stencils

The land pattern recommendations in this document are based on a RoHS compliant process and derived, where possible, from the nominal *Generic Requirements for Surface Mount Design and Land Pattern Standards* IPC-7351B specifications. This standard aims to achieve desired targets of heel, toe and side fillets for solder-joints.

Solder paste and ground via recommendations are based on our engineering and development kit board production. They have been found to work and optimized as appropriate to achieve a high yield. These factors should be taken into account during design and manufacturing of the PCB.

The following land patterns and solder paste contains recommendations. Final land pattern and solder paste decisions are the responsibility of the customer. These should be tuned during manufacture to suit the manufacturing process.

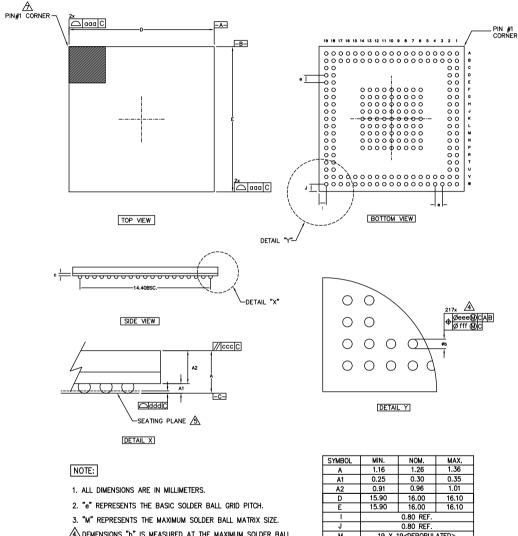

The package is a 217 pin Fine Ball Grid Array package on a 0.8mm pitch with 0.4mm balls.

An example land pattern is shown in Figure 22.

Pad widths and spacings are such that solder mask can still be applied between the pads using standard design rules. This is highly recommended to reduce solder shorts.

#### 16.4 Ground and Thermal Vias

Vias next to every other ground ball into the ground plane of the PCB are recommended for a low inductance ground connection and good thermal performance. Vias with with a 0.6mm diameter annular ring and a 0.3mm drill would be suitable.

#### 16.5 Moisture Sensitivity

XMOS devices are, like all semiconductor devices, susceptible to moisture absorption. When removed from the sealed packaging, the devices slowly absorb moisture from the surrounding environment. If the level of moisture present in the device is too high during reflow, damage can occur due to the increased internal vapour pressure of moisture. Example damage can include bond wire damage, die lifting, internal or external package cracks and/or delamination.

All XMOS devices are Moisture Sensitivity Level (MSL) 3 - devices have a shelf life of 168 hours between removal from the packaging and reflow, provided they

30

# 17 Example XS1-U16A-128-FB217 Board Designs

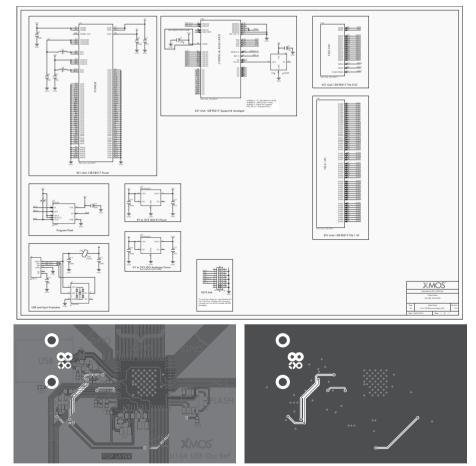

This section shows example schematics and layout for a 2-layer PCB.

- Figures 23 shows example schematics and layout. It uses a 24 MHz crystal for the clock, and an SPI flash for booting. The XS1-U16A-128-FB217 is powered directly from 5V. An optional ESD protection device is included to increase ESD protection from 2 to 15 kV.

- Figures 24 shows example schematics and layout for a design that uses an oscillator rather than a crystal. If required a 3V3 oscillator can be used (for example when sharing an oscillator with other parts of the design), but a resistor bridge must be included to reduce the XI/CLK input from 3V3 to 1V8.

- ▶ Figure 25 shows example schematics and layout for a design that does not use USB and that runs off the internal 20 MHz oscillator. The XS1-U16A-128-FB217 is powered directly from 3V3.

Flash, AVDD, RST, and JTAG connectivity are all optional. Flash can be removed if the processor boots from OTP. The AVDD decoupler and wiring can be removed if the ADC is not used. RST\_N and all JTAG wiring can be removed if debugging is not required (see Appendix M)

-XMOS<sup>®</sup>

Figure 24: Example Oscillator schematic, with top and bottom layout of a 2-layer PCB

### 18.10 External Oscillator Characteristics

Figure 35: External oscillator characteristics

| Symbol | Parameter          | MIN  | ТҮР | MAX  | UNITS | Notes |

|--------|--------------------|------|-----|------|-------|-------|

| F(EXT) | External Frequency |      |     | 100  | MHz   | А     |

| V(IH)  | Input high voltage | 1.62 |     | 1.98 | V     |       |

| V(IL)  | Input low voltage  |      |     | 0.4  | V     |       |

A For use with USB, the design should use a 12 or 24 MHz +/- 150 ppm crystal.

#### 18.11 Power Consumption

| Figure 36: | Symbol   | Parameter                     | MIN | TYP | MAX | UNITS | Notes |

|------------|----------|-------------------------------|-----|-----|-----|-------|-------|

| xCORE Tile | P(AWAKE) | Active Power for awake states | TBC | 600 | ТВС | mW    |       |

| currents   | P(SLEEP) | Power when asleep             | TBC | 500 | ТВС | μW    |       |

#### 18.12 Clock

#### Figure 37: Clock

L

| Symbol | Parameter                 | MIN | TYP | MAX | UNITS | Notes |

|--------|---------------------------|-----|-----|-----|-------|-------|

| f(MAX) | Processor clock frequency |     |     | 500 | MHz   | А     |

A Assumes typical tile and I/O voltages with nominal activity.

### 18.13 Processor I/O AC Characteristics

|                             | Symbol       | Parameter                                                           | MIN | TYP | MAX | UNITS | Notes |

|-----------------------------|--------------|---------------------------------------------------------------------|-----|-----|-----|-------|-------|

| <b></b>                     | T(XOVALID)   | Input data valid window                                             | 8   |     |     | ns    |       |

| Figure 38:                  | T(XOINVALID) | Output data invalid window                                          | 9   |     |     | ns    |       |

| I/O AC char-<br>acteristics | T(XIFMAX)    | Rate at which data can be sampled with respect to an external clock |     |     | 60  | MHz   |       |

The input valid window parameter relates to the capability of the device to capture data input to the chip with respect to an external clock source. It is calculated as the sum of the input setup time and input hold time with respect to the external clock as measured at the pins. The output invalid window specifies the time for which an output is invalid with respect to the external clock. Note that these parameters are specified as a window rather than absolute numbers since the device provides functionality to delay the incoming clock with respect to the incoming data.

Information on interfacing to high-speed synchronous interfaces can be found in the XS1 Port I/O Timing document, X5821.

# 19 Package Information

- A DEMENSIONS "b" IS MEASURED AT THE MAXIMUM SOLDER BALL DIAMETER PARALLEL TO PRIMARY DATUM C.

- THE SPHERICAL CROWNS OF THE SOLDER BALLS.

- 6. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994

- $\Delta$  a1 corner must be identified by ink or laser mark.

- 8. PACKAGE DIMENSIONS CONFORM TO JEDEC REGISTRATION MO-275.

| A   | 1.16              | 1.26       | 1.36  |

|-----|-------------------|------------|-------|

| A1  | 0.25              | 0.30       | 0.35  |

| A2  | 0.91              | 0.96       | 1.01  |

| D   | 15.90             | 16.00      | 16.10 |

| E   | 15.90             | 16.00      | 16.10 |

|     |                   | 0.80 REF.  |       |

| J   | 0.80 REF.         |            |       |

| М   | 19 X <sup>-</sup> | I9⊲DEPOPUL | ATED> |

| aaa |                   |            | 0.15  |

| ccc |                   |            | 0.20  |

| ddd |                   |            | 0.10  |

| eee |                   |            | 0.15  |

| fff |                   |            | 0.08  |

| b   | 0.35              | 0.40       | 0.45  |

| e   | 0.80 BSC.         |            |       |

| c   | 0.26 RFF          |            |       |

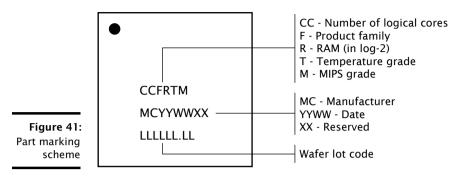

## 19.1 Part Marking

# 20 Ordering Information

| Figure 42:   | Product Code           | Marking | Qualification | Speed Grade |

|--------------|------------------------|---------|---------------|-------------|

| Orderable    | XS1-U16A-128-FB217-C10 | 16U7C10 | Commercial    | 1000 MIPS   |

| part numbers | XS1-U16A-128-FB217-I10 | 16U7I10 | Industrial    | 1000 MIPS   |

42

# **B** Processor Status Configuration

The processor status control registers can be accessed directly by the processor using processor status reads and writes (use getps(reg) and setps(reg,value) for reads and writes).

| Number    | Perm | Description                           |

|-----------|------|---------------------------------------|

| 0x00      | RW   | RAM base address                      |

| 0x01      | RW   | Vector base address                   |

| 0x02      | RW   | xCORE Tile control                    |

| 0x03      | RO   | xCORE Tile boot status                |

| 0x05      | RO   | Security configuration                |

| 0x06      | RW   | Ring Oscillator Control               |

| 0x07      | RO   | Ring Oscillator Value                 |

| 0x08      | RO   | Ring Oscillator Value                 |

| 0x09      | RO   | Ring Oscillator Value                 |

| 0x0A      | RO   | Ring Oscillator Value                 |

| 0x10      | DRW  | Debug SSR                             |

| 0x11      | DRW  | Debug SPC                             |

| 0x12      | DRW  | Debug SSP                             |

| 0x13      | DRW  | DGETREG operand 1                     |

| 0x14      | DRW  | DGETREG operand 2                     |

| 0x15      | DRW  | Debug interrupt type                  |

| 0x16      | DRW  | Debug interrupt data                  |

| 0x18      | DRW  | Debug core control                    |

| 0x20 0x27 | DRW  | Debug scratch                         |

| 0x30 0x33 | DRW  | Instruction breakpoint address        |

| 0x40 0x43 | DRW  | Instruction breakpoint control        |

| 0x50 0x53 | DRW  | Data watchpoint address 1             |

| 0x60 0x63 | DRW  | Data watchpoint address 2             |

| 0x70 0x73 | DRW  | Data breakpoint control register      |

| 0x80 0x83 | DRW  | Resources breakpoint mask             |

| 0x90 0x93 | DRW  | Resources breakpoint value            |

| 0x9C 0x9F | DRW  | Resources breakpoint control register |

-XMOS<sup>®</sup>

Figure 44: Summary

#### D.13 PLink status and network: 0x40 .. 0x43

These registers contain status information and the network number that each processor-link belongs to.

| Bits  | Perm | Init | Description                                                                                                                                                                              |

|-------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:26 | RO   | -    | Reserved                                                                                                                                                                                 |

| 25:24 | RO   |      | If this link is currently routing data into the switch, this field<br>specifies the type of link that the data is routed to:<br>0: plink<br>1: external link<br>2: internal control link |

| 23:16 | RO   | 0    | If the link is routing data into the switch, this field specifies the destination link number to which all tokens are sent.                                                              |

| 15:6  | RO   | -    | Reserved                                                                                                                                                                                 |

| 5:4   | RW   | 0    | Determines the network to which this link belongs, set for quality of service.                                                                                                           |

| 3     | RO   | -    | Reserved                                                                                                                                                                                 |

| 2     | RO   | 0    | Set to 1 if the current packet is junk and being thrown away. A packet is considered junk if, for example, it is not routable.                                                           |

| 1     | RO   | 0    | Set to 1 if the switch is routing data into the link, and if a route exists from another link.                                                                                           |

| 0     | RO   | 0    | Set to 1 if the link is routing data into the switch, and if a route is created to another link on the switch.                                                                           |

0x40 .. 0x43: PLink status and network

### D.14 Link configuration and initialization: 0x80 .. 0x87

-XMOS<sup>®</sup>

These registers contain configuration and debugging information specific to external links. The link speed and width can be set, the link can be initialized, and the link status can be monitored. The registers control links C, D, A, B, G, H, E, and F in that order.

# E Analogue Node Configuration

The analogue node control registers can be accessed using configuration reads and writes (use write\_node\_config\_reg(device, ...) and read\_node\_config\_reg(device, ...) for reads and writes).

| Number | Perm                              | Description                 |  |

|--------|-----------------------------------|-----------------------------|--|

| 0x00   | RO Device identification register |                             |  |

| 0x04   | RW                                | Node configuration register |  |

| 0x05   | RW Node identifier                |                             |  |

| 0x50   | RW Reset and Mode Control         |                             |  |

| 0x51   | RW                                | RW System clock frequency   |  |

| 0x80   | 0x80 RW Link Control and Status   |                             |  |

| 0xD6   | RW                                | 1 KHz Watchdog Control      |  |

| 0xD7   | RW                                | Watchdog Disable            |  |

Figure 47: Summary

### E.1 Device identification register: 0x00

This register contains version information, and information on power-on behavior.

| Bits  | Perm | Init | Description                                                                                                                              |

|-------|------|------|------------------------------------------------------------------------------------------------------------------------------------------|

| 31:24 | RO   | 0x0F | Chip identifier                                                                                                                          |

| 23:17 | RO   | -    | Reserved                                                                                                                                 |

| 16    | RO   | pin  | Oscillator used on power-up. This is set by the OSC_EXT_N<br>pin:<br>0: boot from crystal;<br>1: boot from on-silicon 20 MHz oscillator. |

| 15:8  | RO   | 0x02 | Revision number of the analogue block                                                                                                    |

| 7:0   | RO   | 0x00 | Version number of the analogue block                                                                                                     |

0x00: Device identification register

### E.2 Node configuration register: 0x04

This register is used to set the communication model to use (1 or 3 byte headers), and to prevent any further updates.

**0x20:** UIFM Sticky flags

| Bits | Perm | Init | Description               |

|------|------|------|---------------------------|

| 31:7 | RO   | -    | Reserved                  |

| 6:0  | RW   | 0    | Stickyness for each flag. |

#### F.10 UIFM port masks: 0x24

Set of masks that identify how port 1N, port 1O and port 1P are affected by changes to the flags in  $\ensuremath{\mathsf{FLAGS}}$

| Bits  | Perm | Init | Description                                                                                                                                         |

|-------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:23 | RO   | -    | Reserved                                                                                                                                            |

| 22:16 | RW   | 0    | Bit mask that determines which flags in UIFM_IFM_FLAG[6:0] contribute to port 1P. If any flag listed in this bitmask is high, port 1P will be high. |

| 15    | RO   | -    | Reserved                                                                                                                                            |

| 14:8  | RW   | 0    | Bit mask that determines which flags in UIFM_IFM_FLAG[6:0] contribute to port 10. If any flag listed in this bitmask is high, port 10 will be high. |

| 7     | RO   | -    | Reserved                                                                                                                                            |

| 6:0   | RW   | 0    | Bit mask that determines which flags in UIFM_IFM_FLAG[6:0] contribute to port 1N. If any flag listed in this bitmask is high, port 1N will be high. |

**0x24:** UIFM port masks

### F.11 UIFM SOF value: 0x28

USB Start-Of-Frame counter

**0x28:** UIFM SOF value

| Bits  | Perm | Init | Description                             |

|-------|------|------|-----------------------------------------|

| 31:11 | RO   | -    | Reserved                                |

| 10:8  | RW   | 0    | Most significant 3 bits of SOF counter  |

| 7:0   | RW   | 0    | Least significant 8 bits of SOF counter |

-XMOS

# F.12 UIFM PID: 0x2C

The last USB packet identifier received

79

|          | Bits |

|----------|------|

| 0x2C:    | 31:4 |

| UIFM PID | 3:0  |

| Bits | Perm | Init | Description                     |

|------|------|------|---------------------------------|

| 1:4  | RO   | -    | Reserved                        |

| 3:0  | RO   | 0    | Value of the last received PID. |

#### F.13 UIFM Endpoint: 0x30

The last endpoint seen

0x30 UIFM Endpoint

|               | Bits | Perm | Init | Description                           |

|---------------|------|------|------|---------------------------------------|

| 0:            | 31:5 | RO   | -    | Reserved                              |

| V.<br>M<br>It | 4    | RO   | 0    | 1 if endpoint contains a valid value. |

|               | 3:0  | RO   | 0    | A copy of the last received endpoint. |

### F.14 UIFM Endpoint match: 0x34

This register can be used to mark UIFM endpoints as special.

0x34: UIFM Endpoint match

| Bits  | Perm | Init | Description                                                                                                                          |

|-------|------|------|--------------------------------------------------------------------------------------------------------------------------------------|

| 31:16 | RO   | -    | Reserved                                                                                                                             |

| 15:0  | RW   | 0    | This register contains a bit for each endpoint. If its bit is set, the endpoint will be supplied on the RX port when ORed with 0x10. |

## F.15 UIFM power signalling: 0x38

Bits Perm Init Description 31:9 RO Reserved -0x38: 8 RW 0 Valid 7:0 RW 0 Data

-XMOS

0x0C: ADC Control input pin 3

| Bits | Perm | Init | Description                                                                                                                                                                      |

|------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:8 | RW   | 0    | The node and channel-end identifier to which data for this ADC input pin should be send to. This is the top 24 bits of the channel-end identifier as allocated on an xCORE Tile. |

| 7:1  | RO   | -    | Reserved                                                                                                                                                                         |

| 0    | RW   | 0    | Set to 1 to enable this input pin on the ADC.                                                                                                                                    |

# G.5 ADC Control input pin 4: 0x10

Controls specific to ADC input pin 4.

0x10: ADC Control input pin 4

0x14: ADC Control input pin 5

| Bits | Perm | Init | Description                                                                                                                                                                      |

|------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:8 | RW   | 0    | The node and channel-end identifier to which data for this ADC input pin should be send to. This is the top 24 bits of the channel-end identifier as allocated on an xCORE Tile. |

| 7:1  | RO   | -    | Reserved                                                                                                                                                                         |

| 0    | RW   | 0    | Set to 1 to enable this input pin on the ADC.                                                                                                                                    |

#### G.6 ADC Control input pin 5: 0x14

Controls specific to ADC input pin 5.

| В | Bits | Perm | Init | Description                                                                                                                                                                      |

|---|------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3 | 1:8  | RW   | 0    | The node and channel-end identifier to which data for this ADC input pin should be send to. This is the top 24 bits of the channel-end identifier as allocated on an xCORE Tile. |

|   | 7:1  | RO   | -    | Reserved                                                                                                                                                                         |

|   | 0    | RW   | 0    | Set to 1 to enable this input pin on the ADC.                                                                                                                                    |

# G.7 ADC Control input pin 6: 0x18

Controls specific to ADC input pin 6.

| Number | Perm | Description                                |  |

|--------|------|--------------------------------------------|--|

| 0x00   | RW   | General control                            |  |

| 0x04   | RW   | Time to wake-up, least significant 32 bits |  |

| 0x08   | RW   | Time to wake-up, most significant 32 bits  |  |

| 0x0C   | RW   | Power supply states whilst ASLEEP          |  |

| 0x10   | RW   | Power supply states whilst WAKING1         |  |

| 0x14   | RW   | Power supply states whilst WAKING2         |  |

| 0x18   | RW   | Power supply states whilst AWAKE           |  |

| 0x1C   | RW   | Power supply states whilst SLEEPING1       |  |

| 0x20   | RW   | Power supply states whilst SLEEPING2       |  |

| 0x24   | RW   | Power sequence status                      |  |

| 0x2C   | RW   | DCDC control                               |  |

| 0x30   | RW   | Power supply status                        |  |

| 0x34   | RW   | VDDCORE level control                      |  |

| 0x40   | RW   | LDO5 level control                         |  |

Figure 53: Summary

# K.1 General control: 0x00

This register controls the basic settings for power modes.

| Bits  | Perm | Init | Description                                                                                                                                    |

|-------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:21 | RO   | -    | Reserved                                                                                                                                       |

| 20:16 | RW   | 16   | Log2 number of cycles to stay in this state:<br>0: 1 clock cycles<br>1: 2 clock cycles<br>2: 4 clock cycles<br><br>31: 2147483648 clock cycles |

| 15    | RO   | -    | Reserved                                                                                                                                       |

| 14    | RW   | 0    | Set to 1 to disable clock to the xCORE Tile.                                                                                                   |

| 13:10 | RO   | -    | Reserved                                                                                                                                       |

| 9     | RW   | 0    | Sets modulation used by DCDC2:<br>0: PWM modulation (max 475 mA)<br>1: PFM modulation (max 50 mA)                                              |

| 8     | RW   | 0    | Sets modulation used by DCDC1:<br>0: PWM modulation (max 700 mA)<br>1: PFM modulation (max 50 mA)                                              |

| 7:6   | RO   | -    | Reserved                                                                                                                                       |

| 5     | RW   | 1    | Set to 1 to enable VOUT6 (IO supply).                                                                                                          |

| 4     | RW   | 1    | Set to 1 to enable LDO5 (core PLL supply).                                                                                                     |

| 3:2   | RO   | -    | Reserved                                                                                                                                       |

| 1     | RO   | 1    | Set to 1 to enable DCDC2 (analogue supply).                                                                                                    |

| 0     | RW   | 1    | Set to 1 to enable DCDC1 (core supply).                                                                                                        |

0x14: Power supply states whilst WAKING2

# K.7 Power supply states whilst AWAKE: 0x18

This register controls what state the power control block should be in when in the AWAKE state.

-XMOS"

| Bits  | Perm | Init | Description                                                                                                                                    |

|-------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:21 | RO   | -    | Reserved                                                                                                                                       |

| 20:16 | RW   | 16   | Log2 number of cycles to stay in this state:<br>0: 1 clock cycles<br>1: 2 clock cycles<br>2: 4 clock cycles<br><br>31: 2147483648 clock cycles |

| 15    | RO   | -    | Reserved                                                                                                                                       |

| 14    | RW   | 0    | Set to 1 to disable clock to the xCORE Tile.                                                                                                   |

| 13:10 | RO   | -    | Reserved                                                                                                                                       |

| 9     | RW   | 0    | Sets modulation used by DCDC2:<br>0: PWM modulation (max 475 mA)<br>1: PFM modulation (max 50 mA)                                              |

| 8     | RW   | 0    | Sets modulation used by DCDC1:<br>0: PWM modulation (max 700 mA)<br>1: PFM modulation (max 50 mA)                                              |

| 7:6   | RO   | -    | Reserved                                                                                                                                       |

| 5     | RW   | 0    | Set to 1 to enable VOUT6 (IO supply).                                                                                                          |

| 4     | RW   | 0    | Set to 1 to enable LDO5 (core PLL supply).                                                                                                     |

| 3:2   | RO   | -    | Reserved                                                                                                                                       |

| 1     | RO   | 1    | Set to 1 to enable DCDC2 (analogue supply).                                                                                                    |

| 0     | RW   | 0    | Set to 1 to enable DCDC1 (core supply).                                                                                                        |

0x20: Power supply states whilst SLEEPING2

## K.10 Power sequence status: 0x24

This register defines the current status of the power supply controller.

Copyright © 2015, All Rights Reserved.

XM002326,

Xmos Ltd. is the owner or licensee of this design, code, or Information (collectively, the "Information") and is providing it to you "AS IS" with no warranty of any kind, express or implied and shall have no liability in relation to its use. Xmos Ltd. makes no representation that the Information, or any particular implementation thereof, is or will be free from any claims of infringement and again, shall have no liability in relation to any such claims.