Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 60                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 45x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f65k40-e-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.4 Register and Bit naming conventions

### 1.4.1 REGISTER NAMES

When there are multiple instances of the same peripheral in a device, the peripheral control registers will be depicted as the concatenation of a peripheral identifier, peripheral instance, and control identifier. The control registers section will show just one instance of all the register names with an 'x' in the place of the peripheral instance number. This naming convention may also be applied to peripherals when there is only one instance of that peripheral in the device to maintain compatibility with other devices in the family that contain more than one.

#### 1.4.2 BIT NAMES

There are two variants for bit names:

- · Short name: Bit function abbreviation

- · Long name: Peripheral abbreviation + short name

#### 1.4.2.1 Short Bit Names

Short bit names are an abbreviation for the bit function. For example, some peripherals are enabled with the EN bit. The bit names shown in the registers are the short name variant.

Short bit names are useful when accessing bits in C programs. The general format for accessing bits by the short name is RegisterNamebits. ShortName. For example, the enable bit, EN, in the COG1CON0 register can be set in C programs with the instruction COG1CON0bits.EN = 1.

Short names are generally not useful in assembly programs because the same name may be used by different peripherals in different bit positions. When this occurs, during the include file generation, all instances of that short bit name are appended with an underscore plus the name of the register in which the bit resides to avoid naming contentions.

### 1.4.2.2 Long Bit Names

Long bit names are constructed by adding a peripheral abbreviation prefix to the short name. The prefix is unique to the peripheral thereby making every long bit name unique. The long bit name for the COG1 enable bit is the COG1 prefix, G1, appended with the enable bit short name, EN, resulting in the unique bit name G1EN

Long bit names are useful in both C and assembly programs. For example, in C the COG1CON0 enable bit can be set with the G1EN = 1 instruction. In assembly, this bit can be set with the BSF COG1CON0, G1EN instruction.

#### 1.4.2.3 Bit Fields

Bit fields are two or more adjacent bits in the same register. Bit fields adhere only to the short bit naming convention. For example, the three Least Significant bits of the COG1CON0 register contain the mode control bits. The short name for this field is MD. There is no long bit name variant. Bit field access is only possible in C programs. The following example demonstrates a C program instruction for setting the COG1 to the Push-Pull mode:

```

COG1CON0bits.MD = 0x5;

```

Individual bits in a bit field can also be accessed with long and short bit names. Each bit is the field name appended with the number of the bit position within the field. For example, the Most Significant mode bit has the short bit name MD2 and the long bit name is G1MD2. The following two examples demonstrate assembly program sequences for setting the COG1 to Push-Pull mode:

#### Example 1:

```

MOVLW ~(1<<G1MD1)

ANDWF COG1CON0,F

MOVLW 1<<G1MD2 | 1<<G1MD0

IORWF COG1CON0,F

```

#### Example 2:

BSF COG1CON0,G1MD2

BCF COG1CON0,G1MD1

BSF COG1CON0,G1MD0

# 1.4.3 REGISTER AND BIT NAMING EXCEPTIONS

### 1.4.3.1 Status, Interrupt, and Mirror Bits

Status, interrupt enables, interrupt flags, and mirror bits are contained in registers that span more than one peripheral. In these cases, the bit name shown is unique so there is no prefix or short name variant.

### 1.4.3.2 Legacy Peripherals

There are some peripherals that do not strictly adhere to these naming conventions. Peripherals that have existed for many years and are present in almost every device are the exceptions. These exceptions were necessary to limit the adverse impact of the new conventions on legacy code. Peripherals that do adhere to the new convention will include a table in the registers section indicating the long name prefix for each peripheral instance. Peripherals that fall into the exception category will not have this table. These peripherals include, but are not limited to, the following:

- EUSART

- MSSP

# 4.0 OSCILLATOR MODULE (WITH FAIL-SAFE CLOCK MONITOR)

### 4.1 Overview

The oscillator module has multiple clock sources and selection features that allow it to be used in a wide range of applications while maximizing performance and minimizing power consumption. Figure 4-1 illustrates a block diagram of the oscillator module.

Clock sources can be supplied from external oscillators, quartz-crystal resonators and ceramic resonators. In addition, the system clock source can be supplied from one of two internal oscillators and PLL circuits, with a choice of speeds selectable via software. Additional clock features include:

- Selectable system clock source between external or internal sources via software.

- Fail-Safe Clock Monitor (FSCM) designed to detect a failure of the external clock source (LP, XT, HS, ECH, ECM, ECL) and switch automatically to the internal oscillator.

- Oscillator Start-up Timer (OST) ensures stability of crystal oscillator sources.

The RSTOSC bits of Configuration Word 1 (Register 3-1) determine the type of oscillator that will be used when the device runs after Reset, including when it is first powered up.

If an external clock source is selected, the FEXTOSC bits of Configuration Word 1 must be used in conjunction with the RSTOSC bits to select the External Clock mode.

The external oscillator module can be configured in one of the following clock modes, by setting the FEXTOSC<2:0> bits of Configuration Word 1:

- ECL External Clock Low-Power mode (below 100 kHz)

- ECM External Clock Medium Power mode (100 kHz to 8 MHz)

- 3. ECH External Clock High-Power mode (above 8 MHz)

- 4. LP 32 kHz Low-Power Crystal mode.

- XT Medium Gain Crystal or Ceramic Resonator Oscillator mode (between 100 kHz and 8 MHz)

- HS High Gain Crystal or Ceramic Resonator mode (above 4 MHz)

The ECH, ECM, and ECL Clock modes rely on an external logic level signal as the device clock source. The LP, XT, and HS Clock modes require an external crystal or resonator to be connected to the device. Each mode is optimized for a different frequency range. The internal oscillator block produces low and high-frequency clock sources, designated LFINTOSC and HFINTOSC. (see Internal Oscillator Block, Figure 4-1). Multiple device clock frequencies may be derived from these clock sources.

### REGISTER 4-7: OSCEN: OSCILLATOR MANUAL ENABLE REGISTER

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 |

|---------|---------|---------|---------|---------|---------|-----|-----|

| EXTOEN  | HFOEN   | MFOEN   | LFOEN   | SOSCEN  | ADOEN   | _   | _   |

|         |         |         |         |         |         |     |     |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | EXTOEN: External Oscillator Manual Request Enable bit  1 = EXTOSC is explicitly enabled, operating as specified by FEXTOSC  0 = EXTOSC could be enabled by requesting peripheral                              |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | <b>HFOEN:</b> HFINTOSC Oscillator Manual Request Enable bit  1 = HFINTOSC is explicitly enabled, operating as specified by OSCFRQ (Register 4-5)  0 = HFINTOSC could be enabled by requesting peripheral      |

| bit 5   | MFOEN: MFINTOSC (500 kHz/31.25 kHz) Oscillator Manual Request Enable bit (Derived from HFINTOSC)  1 = MFINTOSC is explicitly enabled  0 = MFINTOSC could be enabled by requesting peripheral                  |

| bit 4   | LFOEN: LFINTOSC (31 kHz) Oscillator Manual Request Enable bit  1 = LFINTOSC is explicitly enabled  0 = LFINTOSC could be enabled by requesting peripheral                                                     |

| bit 3   | SOSCEN: Secondary Oscillator Manual Request Enable bit  1 = Secondary Oscillator is explicitly enabled, operating as specified by SOSCPWR  0 = Secondary Oscillator could be enabled by requesting peripheral |

| bit 2   | ADOEN: ADC Oscillator Manual Request Enable bit  1 = ADC oscillator is explicitly enabled  0 = ADC oscillator could be enabled by requesting peripheral                                                       |

| bit 1-0 | Unimplemented: Read as '0'                                                                                                                                                                                    |

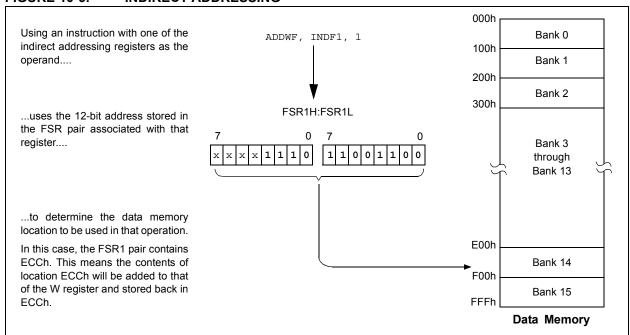

# 10.6.3.1 FSR Registers and the INDF Operand

At the core of indirect addressing are three sets of registers: FSR0, FSR1 and FSR2. Each represents a pair of 8-bit registers, FSRnH and FSRnL. Each FSR pair holds a 12-bit value, therefore, the four upper bits of the FSRnH register are not used. The 12-bit FSR value can address the entire range of the data memory in a linear fashion. The FSR register pairs, then, serve as pointers to data memory locations.

Indirect addressing is accomplished with a set of Indirect File Operands, INDF0 through INDF2. These can be thought of as "virtual" registers; they are mapped in the SFR space but are not physically implemented. Reading or writing to a particular INDF register actually accesses its corresponding FSR register pair. A read from INDF1, for example, reads the data at the address indicated by FSR1H:FSR1L. Instructions that use the INDF registers as operands actually use the contents of their corresponding FSR as a pointer to the instruction's target. The INDF operand is just a convenient way of using the pointer.

Because indirect addressing uses a full 12-bit address, data RAM banking is not necessary. Thus, the current contents of the BSR and the Access RAM bit have no effect on determining the target address.

# 10.6.3.2 FSR Registers and POSTINC, POSTDEC, PREINC and PLUSW

In addition to the INDF operand, each FSR register pair also has four additional indirect operands. Like INDF, these are "virtual" registers which cannot be directly read or written. Accessing these registers actually accesses the location to which the associated FSR register pair points, and also performs a specific action on the FSR value. They are:

- POSTDEC: accesses the location to which the FSR points, then automatically decrements the FSR by 1 afterwards

- POSTINC: accesses the location to which the FSR points, then automatically increments the FSR by 1 afterwards

- PREINC: automatically increments the FSR by one, then uses the location to which the FSR points in the operation

- PLUSW: adds the signed value of the W register (range of -127 to 128) to that of the FSR and uses the location to which the result points in the operation.

In this context, accessing an INDF register uses the value in the associated FSR register without changing it. Similarly, accessing a PLUSW register gives the FSR value an offset by that in the W register; however, neither W nor the FSR is actually changed in the operation. Accessing the other virtual registers changes the value of the FSR register.

### FIGURE 10-6: INDIRECT ADDRESSING

# 11.0 NONVOLATILE MEMORY (NVM) CONTROL

Nonvolatile Memory (NVM) is separated into two types: Program Flash Memory (PFM) and Data EEPROM Memory.

PFM, Data EEPROM, User IDs and Configuration bits can all be accessed using the NVMREG<1:0> bits of the NVMCON1 register.

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump rated to operate over the operating voltage range of the device.

NVM can be protected in two ways, by either code protection or write protection. Code protection ( $\overline{CP}$  and  $\overline{CPD}$  bits in Configuration Word 5L) disables access, reading and writing to both PFM and Data EEPROM Memory via external device programmers. Code protection does not affect the self-write and erase functionality. Code protection can only be reset by a device programmer performing a Bulk Erase to the device, clearing all nonvolatile memory, Configuration bits and User IDs.

Write protection prohibits self-write and erase to a portion or all of the PFM, as defined by the WRT bits of Configuration Word 4H. Write protection does not affect a device programmer's ability to read, write or erase the device.

TABLE 11-1: NVM ORGANIZATION AND ACCESS INFORMATION

|                                   | PC<20:0><br>ICSP™ Addr<21:0> | Execution    | User Access  |                               |                |  |

|-----------------------------------|------------------------------|--------------|--------------|-------------------------------|----------------|--|

| Memory                            | TRUBTR 404.05 CPII           |              | NVMREG       | TABLAT                        | NVMDAT         |  |

| User Flash Memory<br>(PFM)        | 00 0000h<br>•••<br>01 FFFFh  | Read         | 10           | Read/<br>Write <sup>(1)</sup> | (3)            |  |

| User IDs <sup>(2)</sup>           | 20 0000h<br>•••<br>20 000Fh  | No Access    | x1           | Read/<br>Write                | (3)            |  |

| Reserved                          | 20 0010h<br>2F FFFFh         | No Access(3) |              | (3)                           |                |  |

| Configuration                     | 30 0000h<br>•••<br>30 000Bh  | No Access    | x1           | Read/<br>Write                | (3)            |  |

| Reserved                          | 30 000Ch<br>30 FFFFh         | No Access    | (3)          |                               |                |  |

| User Data Memory<br>(Data EEPROM) | 31 0000h<br>•••<br>31 03FFh  | No Access    | No Access 00 |                               | Read/<br>Write |  |

| Reserved                          | 32 0000h<br>3F FFFBh         | No Access(3) |              |                               |                |  |

| Revision ID/<br>Device ID         | 3F FFFCh  ••• 3F FFFFh       | No Access    | x1           | Read                          | (3)            |  |

Note 1: Subject to Memory Write Protection settings.

- 2: User IDs are eight words ONLY. There is no code protection, table read protection or write protection implemented for this region.

- 3: Reads as '0', writes clear the WR bit and WRERR bit is set.

### REGISTER 11-5: NVMDAT: DATA EEPROM MEMORY DATA

| R/W-0/0 | R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |  |

|---------|-------------|---------|---------|---------|---------|---------|---------|--|--|--|

|         | NVMDAT<7:0> |         |         |         |         |         |         |  |  |  |

| bit 7   | bit 7 bit 0 |         |         |         |         |         |         |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

x = Bit is unknown '0' = Bit is cleared '1' = Bit is set

-n = Value at POR

bit 7-0 **NVMDAT<7:0>:** The value of the data memory word returned from NVMADR after a Read command, or the data written by a Write command.

TABLE 11-5: SUMMARY OF REGISTERS ASSOCIATED WITH DATA EEPROM MEMORY

| Name    | Bit 7       | Bit 6          | Bit 5     | Bit 4        | Bit 3         | Bit 2        | Bit 1       | Bit 0   | Register on Page |  |

|---------|-------------|----------------|-----------|--------------|---------------|--------------|-------------|---------|------------------|--|

| NVMCON1 | NVMRE       | G<1:0>         | _         | FREE         | WRERR         | WREN         | WR          | WR RD   |                  |  |

| NVMCON2 |             | Unlock Pattern |           |              |               |              |             |         |                  |  |

| NVMADRL |             | NVMADR<7:0>    |           |              |               |              |             |         |                  |  |

| NVMADRH | _           | _              | _         | _            | _             | _            | NVMAI       | 149     |                  |  |

| NVMDAT  | NVMDAT<7:0> |                |           |              |               |              |             |         |                  |  |

| TBLPTRU | _           | _              |           | Program M    | lemory Table  | Pointer (TBL | PTR<21:16>) |         | 130*             |  |

| TBLPTRH |             |                | Program M | lemory Table | Pointer (TBI  | LPTR<15:8>)  |             |         | 130*             |  |

| TBLPTRL |             |                | Program I | Memory Table | e Pointer (TB | LPTR<7:0>)   |             |         | 130*             |  |

| TABLAT  |             |                |           | TA           | BLAT          |              |             |         | 129*             |  |

| INTCON  | GIE/GIEH    | PEIE/GIEL      | IPEN      | _            | _             | INT2EDG      | INT1EDG     | INT0EDG | 173              |  |

| PIE8    | SCANIE      | CRCIE          | NVMIE     | -            | _             | _            | _           | CWG1IE  | 193              |  |

| PIR8    | SCANIF      | CRCIF          | NVMIF     | _            | _             | _            | _           | CWG1IF  | 183              |  |

| IPR8    | SCANIP      | CRCIP          | NVMIP     | _            | _             | _            | _           | CWG1IP  | 203              |  |

**Legend:** — = unimplemented, read as '0'. Shaded bits are not used during EEPROM access.

<sup>\*</sup>Page provides register information.

# 13.9 Program Memory Scan Configuration

If desired, the program memory scan module may be used in conjunction with the CRC module to perform a CRC calculation over a range of program memory addresses. In order to set up the scanner to work with the CRC you need to perform the following steps:

- Set the Enable bit in both the CRCCON0 and SCANCON0 registers. If they get disabled, all internal states of the scanner and the CRC are reset (registers are unaffected).

- Choose which memory access mode is to be used (see Section 13.11 "Scanning Modes") and set the MODE bits of the SCANCONO register appropriately.

- Based on the memory access mode, set the INTM bits of the SCANCON0 register to the appropriate interrupt mode (see Section 13.11.5 "Interrupt Interaction")

- Set the SCANLADRL/H/U and SCANHADRL/H/ U registers with the beginning and ending locations in memory that are to be scanned.

- 5. The CRCGO bit must be set before setting the SCANGO bit. Setting the SCANGO bit starts the scan. Both CRCEN and CRCGO bits must be enabled to use the scanner. When either of these bits are disabled, the scan aborts and the INVALID bit SCANCON0 is set. The scanner will wait for the signal from the CRC that it is ready for the first Flash memory location, then begin loading data into the CRC. It will continue to do so until it either hits the configured end address or an address that is unimplemented on the device, at which point the SCANGO bit will clear, Scanner functions will cease, and the SCANIF interrupt will be triggered. Alternately, the SCANGO bit can be cleared in software if desired.

### 13.10 Scanner Interrupt

The scanner will trigger an interrupt when the SCANGO bit transitions from '1' to '0'. The SCANIF interrupt flag of PIR7 is set when the last memory location is reached and the data is entered into the CRCDATA registers. The SCANIF bit can only be cleared in software. The SCAN interrupt enable is the SCANIE bit of the PIE7 register.

### 13.11 Scanning Modes

The memory scanner can scan in four modes: Burst, Peek, Concurrent, and Triggered. These modes are controlled by the MODE bits of the SCANCON0 register. The four modes are summarized in Table 13-2.

#### 13.11.1 BURST MODE

When MODE = 01, the scanner is in Burst mode. In Burst mode, CPU operation is stalled beginning with the operation after the one that sets the SCANGO bit, and the scan begins, using the instruction clock to execute. The CPU is held in its current state until the scan stops. Note that because the CPU is not executing instructions, the SCANGO bit cannot be cleared in software, so the CPU will remain stalled until one of the hardware end-conditions occurs. Burst mode has the highest throughput for the scanner, but has the cost of stalling other execution while it occurs.

#### 13.11.2 CONCURRENT MODE

When MODE = 00, the scanner is in Concurrent mode. Concurrent mode, like Burst mode, stalls the CPU while performing accesses of memory. However, while Burst mode stalls until all accesses are complete, Concurrent mode allows the CPU to execute in between access cycles.

### 13.11.3 TRIGGERED MODE

When MODE = 11, the scanner is in Triggered mode. Triggered mode behaves identically to Concurrent mode, except instead of beginning the scan immediately upon the SCANGO bit being set, it waits for a rising edge from a separate trigger clock, the source of which is determined by the SCANTRIG register.

#### 13.11.4 PEEK MODE

When MODE = 10, the scanner is in Peek mode. Peek mode waits for an instruction cycle in which the CPU does not need to access the NVM (such as a branch instruction) and uses that cycle to do its own NVM access. This results in the lowest throughput for the NVM access (and can take a much longer time to complete a scan than the other modes), but does so without any impact on execution times, unlike the other modes.

### REGISTER 17-2: RxyPPS: PIN Rxy OUTPUT SOURCE SELECTION REGISTER

bit 5-0 **RxyPPS<5:0>:** Pin Rxy Output Source Selection bits

| RxyPPS<5:0> | Pin Rxy Output Source |   | Outp | ut can | be red | irected | to PC | RTx |   |

|-------------|-----------------------|---|------|--------|--------|---------|-------|-----|---|

| 0x21        | ADGRDB                |   | _    | С      |        |         | _     |     | Н |

| 0x20        | ADGRDA                | _ | _    | С      | _      | _       | _     | _   | Н |

| 0x1F        | DSM1                  | _ | _    | С      | _      | _       | _     | _   | Н |

| 0x1E        | CLKR                  | _ | _    | С      | _      | _       | _     | _   | Н |

| 0x1D        | TMR0                  | _ | В    | С      | _      | _       | _     | _   | _ |

| 0x1C        | MSSP2 (SDO/SDA)       |   | В    | _      | D      | _       | _     | _   | _ |

| 0x1B        | MSSP2 (SCK/SCL)       | _ | В    | _      | D      | _       | _     | _   | _ |

| 0x1A        | MSSP1 (SDO/SDA)       | _ | В    | С      | _      | _       | _     | _   | _ |

| 0x19        | MSSP1 (SCK/SCL)       |   | В    | С      | _      |         | _     | _   | _ |

| 0x18        | CMP3                  | _ | _    | _      | _      | _       | F     | G   | _ |

| 0x17        | CMP2                  | _ | _    | _      | _      | _       | F     | G   | _ |

| 0x16        | CMP1                  |   | _    | _      | _      | _       | F     | G   | _ |

| 0x15        | EUSART5 (DT)          | _ | _    | _      | _      | Е       | _     | G   | _ |

| 0x14        | EUSART5 (TX/CK)       |   | _    | _      | _      | Е       | _     | G   | _ |

| 0x13        | EUSART4 (DT)          |   | В    | С      | _      | _       | _     | _   | _ |

| 0x12        | EUSART4 (TX/CK)       | _ | В    | С      | _      | _       | _     | _   | _ |

| 0x11        | EUSART3 (DT)          | _ | В    | _      | _      | Е       | _     | _   | _ |

| 0x10        | EUSART3 (TX/CK)       | _ | В    | _      | _      | Е       | _     | _   | _ |

| 0xF         | EUSART2 (DT)          | _ | _    | _      | D      | _       | _     | G   | _ |

| 0xE         | EUSART2 (TX/CK)       | _ | _    | _      | D      | _       | _     | G   | _ |

| 0xD         | EUSART1 (DT)          |   | _    | С      | D      | _       | _     | _   | _ |

| 0xC         | EUSART1 (TX/CK)       | _ | _    | С      | D      | _       | _     | _   | _ |

| 0xB         | PWM7                  |   | _    | С      | _      | Е       | _     | _   | _ |

| 0xA         | PWM6                  | _ | _    | С      | _      | Е       | _     | _   | _ |

| 0x9         | CCP5                  | _ | _    | _      | _      | Е       | _     | G   | _ |

| 0x8         | CCP4                  | _ | _    | _      |        | Е       | _     | G   | _ |

| 0x7         | CCP3                  | _ | _    | С      |        | Е       | _     | _   | _ |

| 0x6         | CCP2                  | _ | _    | С      |        | Е       | _     |     | _ |

| 0x5         | CCP1                  | _ | _    | С      |        | Е       | _     | _   | _ |

| 0x4         | CWG1D                 |   |      | _      | _      | E       | _     | G   | _ |

| 0x3         | CWG1C                 | _ | _    | С      | _      | Е       | _     | _   | _ |

| 0x2         | CWG1B                 | _ | _    | _      |        | Е       | _     | G   | _ |

| 0x1         | CWG1A                 |   | _    | С      |        | Е       |       |     |   |

| 0x0         | LATxy                 | Α | В    | С      | D      | Е       | F     | G   | Н |

### REGISTER 18-2: T0CON1: TIMER0 CONTROL REGISTER 1

| R/W-0/0 | R/W-0/0   | R/W-0/0 | R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|-----------|---------|-------------|---------|---------|---------|---------|

|         | T0CS<2:0> | T0ASYNC | T0CKPS<3:0> |         |         |         |         |

| bit 7   |           |         |             |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-5 T0CS<2:0>:Timer0 Clock Source Select bits

111 = Reserved

110 = Reserved

101 = SOSC

100 = LFINTOSC

011 = HFINTOSC

010 = Fosc/4

001 = Pin selected by T0CKIPPS (Inverted)

000 = Pin selected by T0CKIPPS (Non-inverted)

bit 4 **T0ASYNC:** TMR0 Input Asynchronization Enable bit

1 = The input to the TMR0 counter is not synchronized to system clocks

0 = The input to the TMR0 counter is synchronized to Fosc/4

bit 3-0 **TOCKPS<3:0>:** Prescaler Rate Select bit

1111 = 1:32768

1110 = 1:16384

1101 = 1:8192

1100 = 1:4096

1011 = 1:2048

1010 = 1:1024

1001 = 1:512

1000 = 1:256

0111 = 1:128

0110 = 1:64

0101 = 1:32

0100 = 1:16

0011 = 1:8

0010 = 1:4

0001 = 1:2

0000 = 1:1

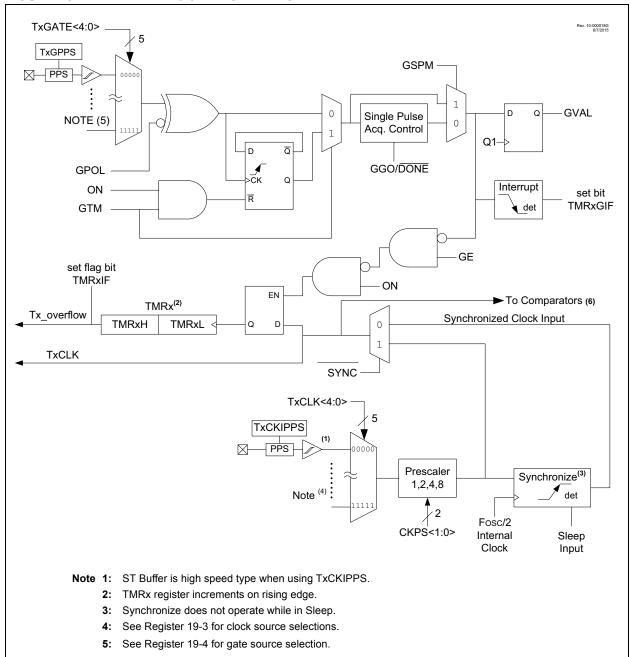

FIGURE 19-1: TIMER1/3/5/7 BLOCK DIAGRAM

**6:** Synchronized comparator output should not be used in conjunction with synchronized input clock.

### REGISTER 19-3: TMRxCLK: TIMERx CLOCK REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W-0/u | R/W-0/u | R/W-0/u | R/W-0/u |

|-------|-----|-----|-----|---------|---------|---------|---------|

| -     | _   | _   | _   |         | CS<     | 3:0>    |         |

| bit 7 |     |     |     |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared u = unchanged

bit 7-4 Unimplemented: Read as '0'

bit 3-0 CS<3:0>: Timerx Clock Source Selection bits

| 66        | Timer1             | Timer3             | Timer5             | Timer7             |  |

|-----------|--------------------|--------------------|--------------------|--------------------|--|

| CS        | Clock Source       | Clock Source       | Clock Source       | Clock Source       |  |

| 1111-1101 | Reserved           | Reserved           | Reserved           | Reserved           |  |

| 1100      | TMR7 overflow      | TMR7 overflow      | TMR7 overflow      | Reserved           |  |

| 1011      | TMR5 overflow      | TMR5 overflow      | Reserved           | TMR5 overflow      |  |

| 1010      | TMR3 overflow      | Reserved           | TMR3 overflow      | TMR3 overflow      |  |

| 1001      | Reserved           | TMR1 overflow      | TMR1 overflow      | TMR1 overflow      |  |

| 1000      | TMR0 overflow      | TMR0 overflow      | TMR0 overflow      | TMR0 overflow      |  |

| 0111      | CLKREF             | REF CLKREF         |                    | CLKREF             |  |

| 0110      | SOSC               | SOSC               | SOSC               | SOSC               |  |

| 0101      | MFINTOSC (500 kHz) | MFINTOSC (500 kHz) | MFINTOSC (500 kHz) | MFINTOSC (500 kHz) |  |

| 0100      | LFINTOSC           | LFINTOSC           | LFINTOSC           | LFINTOSC           |  |

| 0011      | HFINTOSC           | HFINTOSC           | HFINTOSC           | HFINTOSC           |  |

| 0010      | Fosc               | Fosc               | Fosc               | Fosc               |  |

| 0001      | Fosc/4             | Fosc/4             | Fosc/4             | Fosc/4             |  |

| 0000      | T1CKIPPS           | T3CKIPPS           | T5CKIPPS           | T7CKIPPS           |  |

PIC18(L)F65/66K40

### 25.7.5 WINDOWED MEASURE MODE

This mode measures the window duration of the SMTWINx input of the SMT. It begins incrementing the timer on a rising edge of the SMTWINx input and updates the SMTxCPR register with the value of the timer and resets the timer on a second rising edge. See Figure 25-10 and Figure 25-11.

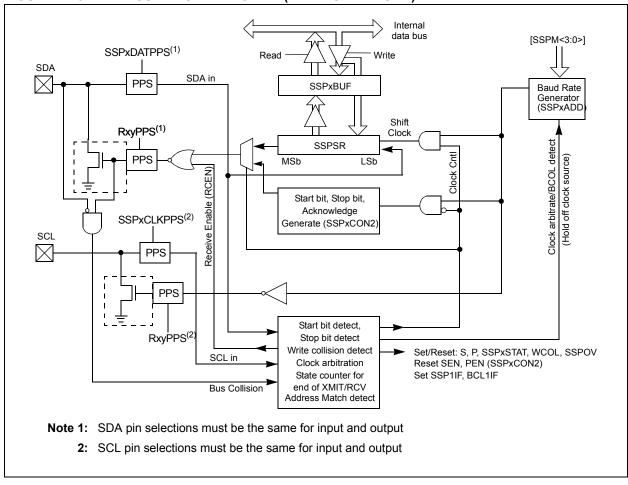

### 27.6 I<sup>2</sup>C Mode Overview

The Inter-Integrated Circuit (I<sup>2</sup>C) bus is a multi-master serial data communication bus. Devices communicate in a master/slave environment where the master devices initiate the communication. A slave device is

controlled through addressing. Figure 27-9 is a block diagram of the I<sup>2</sup>C interface module in Master mode. Figure 27-10 is a diagram of the I<sup>2</sup>C interface module in Slave mode.

FIGURE 27-9: MSSP BLOCK DIAGRAM (I<sup>2</sup>C MASTER MODE)

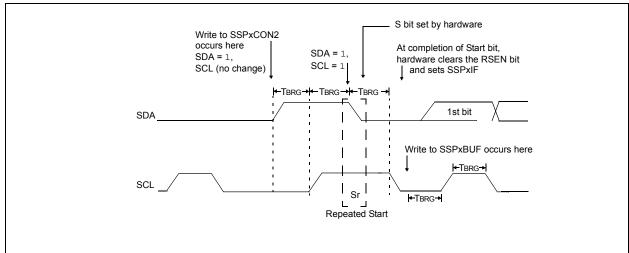

# 27.10.5 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition (Figure 27-27) occurs when the RSEN bit of the SSPxCON2 register is programmed high and the master state machine is no longer active. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the Baud Rate Generator is loaded and begins counting. The SDA pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDA is sampled high, the SCL pin will be deasserted (brought high). When SCL is sampled high, the Baud Rate Generator is reloaded and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA = 0) for one TBRG while SCL is high. SCL is asserted low. Following this, the RSEN bit of the SSPxCON2 register will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDA pin held low. As soon as a Start condition is detected on the SDA and SCL pins. the S bit of the SSPxSTAT register will be set. The SSPxIF bit will not be set until the Baud Rate Generator has timed out.

- **Note 1:** If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDA is sampled low when SCL goes from low-to-high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data '1'.

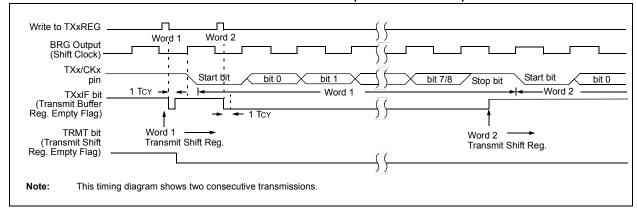

# 27.10.6 | C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSPxBUF register. This action will set the Buffer Full flag bit, BF, and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted. SCL is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCL is released high. When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA. This allows the slave device being addressed to respond with an ACK bit during the ninth bit time if an address match occurred, or if data was received properly. The status of ACK is written into the ACKSTAT bit on the rising edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared. If not, the bit is set. After the ninth clock, the SSPxIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPxBUF, leaving SCL low and SDA unchanged (Figure 27-28).

### FIGURE 27-27: REPEATED START CONDITION WAVEFORM

FIGURE 28-4: ASYNCHRONOUS TRANSMISSION (BACK-TO-BACK)

TABLE 28-1: SUMMARY OF REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Name     | Bit 7    | Bit 6     | Bit 5   | Bit 4      | Bit 3        | Bit 2     | Bit 1   | Bit 0   | Register on Page |

|----------|----------|-----------|---------|------------|--------------|-----------|---------|---------|------------------|

| BAUDxCON | ABDOVF   | RCIDL     | _       | SCKP       | BRG16        | _         | WUE     | ABDEN   | 451              |

| INTCON   | GIE/GIEH | PEIE/GIEL | IPEN    | _          | INT3EDG      | INT2EDG   | INT1EDG | INT0EDG | 173              |

| PIE3     | RC2IE    | TX2IE     | RC1IE   | TX1IE      | BCL2IE       | SSP2IE    | BCL1IE  | SSP1IE  | 177              |

| PIR3     | RC2IF    | TX2IF     | RC1IF   | TX1IF      | BCL2IF       | SSP2IF    | BCL1IF  | SSP1IF  | 177              |

| IPR3     | RC2IP    | TX2IP     | RC1IP   | TX1IP      | BCL2IP       | SSP2IP    | BCL1IP  | SSP1IP  | 198              |

| PIE4     | _        | _         | RC5IE   | TX5IE      | RC4IE        | TX4IE     | RC3IE   | TX3IE   | 189              |

| PIR4     | _        | _         | RC5IF   | TX5IF      | RC4IF        | TX4IF     | RC3IF   | TX3IF   | 178              |

| IPR4     | _        | _         | RC5IP   | TX5IP      | RC4IP        | TX4IP     | RC3IP   | TX3IP   | 199              |

| RCxSTA   | SPEN     | RX9       | SREN    | CREN       | ADDEN        | FERR      | OERR    | RX9D    | 450              |

| RxyPPS   | _        | _         |         |            | RxyP         | PS<5:0>   |         |         | 228              |

| TXxPPS   | _        | _         |         |            | TXPI         | PS<5:0>   |         |         | 225              |

| SPxBRGH  |          |           | EUSARTx | Baud Rate  | Generator, F | ligh Byte |         |         | 460*             |

| SPxBRGL  |          |           | EUSARTx | Baud Rate  | Generator, L | ow Byte   |         |         | 460*             |

| TXxREG   |          |           | EU:     | SARTx Trar | smit Registe | er        |         |         | 452*             |

| TXxSTA   | CSRC     | TX9       | TXEN    | SYNC       | SENDB        | BRGH      | TRMT    | TX9D    | 449              |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used for asynchronous transmission.

Page provides register information.

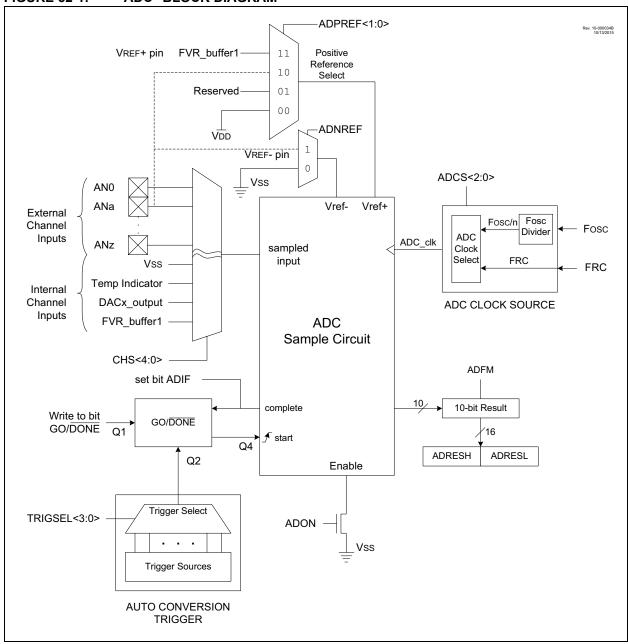

FIGURE 32-1: ADC<sup>2</sup> BLOCK DIAGRAM

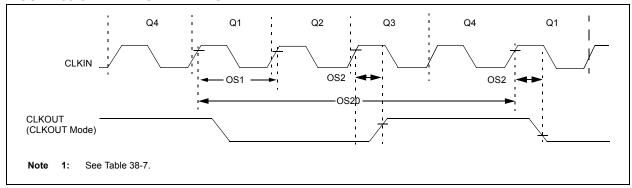

### FIGURE 38-5: CLOCK TIMING

TABLE 38-7: EXTERNAL CLOCK/OSCILLATOR TIMING REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated) |                     |                        |      |        |      |       |                  |  |  |  |  |

|---------------------------------------------------------|---------------------|------------------------|------|--------|------|-------|------------------|--|--|--|--|

| Param<br>No.                                            | Sym.                | Characteristic         | Min. | Тур†   | Max. | Units | Conditions       |  |  |  |  |

| ECL Osc                                                 | ECL Oscillator      |                        |      |        |      |       |                  |  |  |  |  |

| OS1                                                     | F <sub>ECL</sub>    | Clock Frequency        | _    | _      | 500  | kHz   |                  |  |  |  |  |

| OS2                                                     | T <sub>ECL_DC</sub> | Clock Duty Cycle       | 40   | _      | 60   | %     |                  |  |  |  |  |

| ECM Oscillator                                          |                     |                        |      |        |      |       |                  |  |  |  |  |

| OS3                                                     | F <sub>ECM</sub>    | Clock Frequency        | _    | _      | 8    | MHz   |                  |  |  |  |  |

| OS4                                                     | T <sub>ECM_DC</sub> | Clock Duty Cycle       | 40   | _      | 60   | %     |                  |  |  |  |  |

| ECH Oscillator                                          |                     |                        |      |        |      |       |                  |  |  |  |  |

| OS5                                                     | F <sub>ECH</sub>    | Clock Frequency        | _    | _      | 32   | MHz   |                  |  |  |  |  |

| OS6                                                     | T <sub>ECH_DC</sub> | Clock Duty Cycle       | 40   | _      | 60   | %     |                  |  |  |  |  |

| LP Oscillator                                           |                     |                        |      |        |      |       |                  |  |  |  |  |

| OS7                                                     | F <sub>LP</sub>     | Clock Frequency        | _    | _      | 100  | kHz   | Note 4           |  |  |  |  |

| XT Oscillator                                           |                     |                        |      |        |      |       |                  |  |  |  |  |

| OS8                                                     | F <sub>XT</sub>     | Clock Frequency        | _    | _      | 4    | MHz   | Note 4           |  |  |  |  |

| HS Oscillator                                           |                     |                        |      |        |      |       |                  |  |  |  |  |

| OS9                                                     | F <sub>HS</sub>     | Clock Frequency        | _    | _      | 20   | MHz   | Note 4           |  |  |  |  |

| Secondary Oscillator                                    |                     |                        |      |        |      |       |                  |  |  |  |  |

| OS10                                                    | F <sub>SEC</sub>    | Clock Frequency        | 32.4 | 32.768 | 33.1 | kHz   |                  |  |  |  |  |

| System Oscillator                                       |                     |                        |      |        |      |       |                  |  |  |  |  |

| OS20                                                    | F <sub>OSC</sub>    | System Clock Frequency | _    | _      | 64   | MHz   | (Note 2, Note 3) |  |  |  |  |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to OSC1 pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

- 2: The system clock frequency (Fosc) is selected by the "main clock switch controls" as described in **Section 6.0 "Power-Saving Operation Modes"**.

- 3: The system clock frequency (Fosc) must meet the voltage requirements defined in the Section 38.2 "Standard Operating Conditions".

- **4:** LP, XT and HS oscillator modes require an appropriate crystal or resonator to be connected to the device. For clocking the device with the external square wave, one of the EC mode selections must be used.

## TABLE 38-13: ANALOG-TO-DIGITAL CONVERTER (ADC) ACCURACY SPECIFICATIONS<sup>(1,2)</sup>:

Operating Conditions (unless otherwise stated) VDD = 3.0V, TA = 25°C, TAD =  $1\mu s$

| Param<br>No. | Sym.   | Characteristic                                    | Min.   | Typ† | Max.   | Units | Conditions                  |  |  |

|--------------|--------|---------------------------------------------------|--------|------|--------|-------|-----------------------------|--|--|

| AD01         | NR     | Resolution                                        | _      | _    | 10     | bit   |                             |  |  |

| AD02         | EIL    | Integral Error                                    | _      | ±0.1 | ±1.0   | LSb   | ADCREF+ = 3.0V, ADCREF-= 0V |  |  |

| AD03         | Edl    | Differential Error                                | _      | ±0.1 | ±1.0   | LSb   | ADCREF+ = 3.0V, ADCREF-= 0V |  |  |

| AD04         | Eoff   | Offset Error                                      | _      | 0.5  | ±2.0   | LSb   | ADCREF+ = 3.0V, ADCREF-= 0V |  |  |

| AD05         | Egn    | Gain Error                                        | _      | ±0.2 | ±1.0   | LSb   | ADCREF+ = 3.0V, ADCREF-= 0V |  |  |

| AD06         | VADREF | ADC Reference Voltage<br>(ADREF+ - ADREF-)        | 1.8    | _    | VDD    | ٧     |                             |  |  |

| AD07         | VAIN   | Full-Scale Range                                  | ADREF- | _    | ADREF+ | V     |                             |  |  |

| AD08         | ZAIN   | Recommended Impedance of<br>Analog Voltage Source | _      | 10   | _      | kΩ    |                             |  |  |

| AD09         | RVREF  | ADC Voltage Reference Ladder Impedance            | _      | 50   | _      | kΩ    | Note 3                      |  |  |

These parameters are characterized but not tested.

- Note 1: Total Absolute Error is the sum of the offset, gain and integral non-linearity (INL) errors.

- 2: The ADC conversion result never decreases with an increase in the input and has no missing codes.

- 3: This is the impedance seen by the VREF pads when the external reference pads are selected.

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not