Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detans                     |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 60                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 45x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-VFQFN Exposed Pad                                                        |

| Supplier Device Package    | 64-VQFN (9x9)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f65k40t-i-mr |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

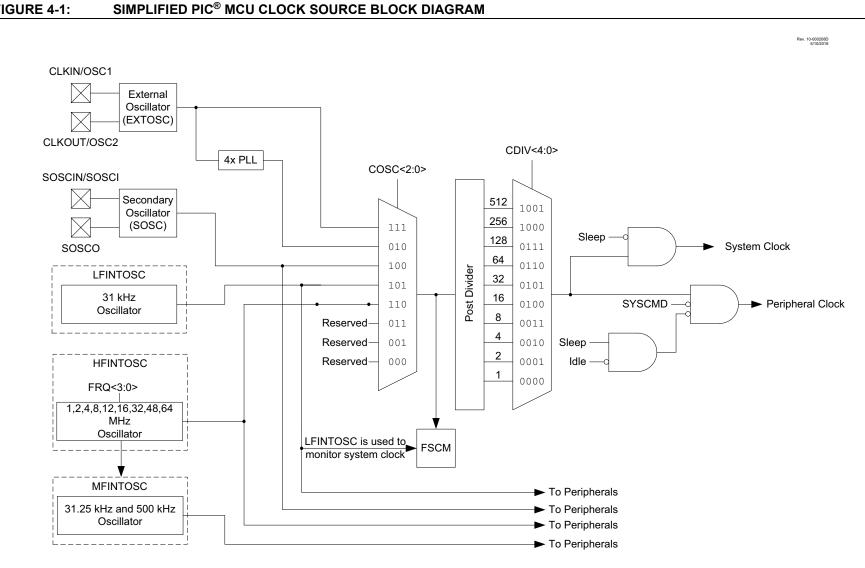

# FIGURE 4-1:

#### EXAMPLE 11-3: ERASING A PROGRAM FLASH MEMORY BLOCK

; This sample row erase routine assumes the following:

; 1. A valid address within the erase row is loaded in variables TBLPTR register

; 2. ADDRH and ADDRL are located in common RAM (locations  $0 \mathrm{x} 70$  -  $0 \mathrm{x} 7 \mathrm{F})$

|            | MOVLW | CODE_ADDR_UPPER  | ; load TBLPTR with the base     |

|------------|-------|------------------|---------------------------------|

|            | MOVWF | TBLPTRU          | ; address of the memory block   |

|            | MOVLW | CODE_ADDR_HIGH   |                                 |

|            | MOVWF | TBLPTRH          |                                 |

|            | MOVLW | CODE_ADDR_LOW    |                                 |

|            | MOVWF | TBLPTRL          |                                 |

| ERASE_BLOC | CK    |                  |                                 |

|            | BCF   | NVMCON1, NVMREG0 | ; point to Program Flash Memory |

|            | BSF   | NVMCON1, NVMREG1 | ; access Program Flash Memory   |

|            | BSF   | NVMCON1, WREN    | ; enable write to memory        |

|            | BSF   | NVMCON1, FREE    | ; enable block Erase operation  |

|            | BCF   | INTCON, GIE      | ; disable interrupts            |

| Required   | MOVLW | 55h              |                                 |

| Sequence   | MOVWF | NVMCON2          | ; write 55h                     |

|            | MOVLW | AAh              |                                 |

|            | MOVWF | NVMCON2          | ; write AAh                     |

|            | BSF   | NVMCON1, WR      | ; start erase (CPU stalls)      |

|            | BSF   | INTCON, GIE      | ; re-enable interrupts          |

|            |       |                  |                                 |

|            |       |                  |                                 |

# 12.0 8x8 HARDWARE MULTIPLIER

# 12.1 Introduction

All PIC18 devices include an 8x8 hardware multiplier as part of the ALU. The multiplier performs an unsigned operation and yields a 16-bit result that is stored in the product register pair, PRODH:PRODL. The multiplier's operation does not affect any flags in the STATUS register.

Making multiplication a hardware operation allows it to be completed in a single instruction cycle. This has the advantages of higher computational throughput and reduced code size for multiplication algorithms and allows the PIC18 devices to be used in many applications previously reserved for digital signal processors. A comparison of various hardware and software multiply operations, along with the savings in memory and execution time, is shown in Table 12-1.

# 12.2 Operation

Example 12-1 shows the instruction sequence for an 8x8 unsigned multiplication. Only one instruction is required when one of the arguments is already loaded in the WREG register.

Example 12-2 shows the sequence to do an 8x8 signed multiplication. To account for the sign bits of the arguments, each argument's Most Significant bit (MSb) is tested and the appropriate subtractions are done.

#### EXAMPLE 12-1: 8x8 UNSIGNED MULTIPLY ROUTINE

| MOVF  | ARG1, | W | ; |       |     |       |    |

|-------|-------|---|---|-------|-----|-------|----|

| MULWF | ARG2  |   | ; | ARG1  | *   | ARG2  | -> |

|       |       |   | ; | PRODE | 1:1 | PRODL |    |

|       |       |   |   |       |     |       |    |

# EXAMPLE 12-2: 8x8 SIGNED MULTIPLY

|       |          | n | JUTINE         |

|-------|----------|---|----------------|

| MOVF  | ARG1, W  |   |                |

| MULWF | ARG2     | ; | ARG1 * ARG2 -> |

|       |          | ; | PRODH:PRODL    |

| BTFSC | ARG2, SB | ; | Test Sign Bit  |

| SUBWF | PRODH, F | ; | PRODH = PRODH  |

|       |          | ; | - ARG1         |

| MOVF  | ARG2, W  |   |                |

| BTFSC | ARG1, SB | ; | Test Sign Bit  |

| SUBWF | PRODH, F | ; | PRODH = PRODH  |

|       |          | ; | - ARG2         |

|       |          |   |                |

|                |                           | Program           | Cycles | Time     |          |                 |         |  |

|----------------|---------------------------|-------------------|--------|----------|----------|-----------------|---------|--|

| Routine        | Multiply Method           | Memory<br>(Words) | (Max)  | @ 64 MHz | @ 40 MHz | @ 10 MHz        | @ 4 MHz |  |

| 9v9 uppigpod   | Without hardware multiply | 13                | 69     | 4.3 μs   | 6.9 μs   | 27.6 μs         | 69 μs   |  |

| 8x8 unsigned   | Hardware multiply         | 1                 | 1      | 62.5 ns  | 100 ns   | 400 ns          | 1 μs    |  |

| 9v9 signed     | Without hardware multiply | 33                | 91     | 5.7 μs   | 9.1 μs   | 36.4 μs         | 91 μs   |  |

| 8x8 signed     | Hardware multiply         | 6                 | 6      | 375 ns   | 600 ns   | 2.4 μs          | 6 μs    |  |

| 10v10 unsigned | Without hardware multiply | 21                | 242    | 15.1 μs  | 24.2 μs  | 96.8 μ <b>s</b> | 242 μs  |  |

| 16x16 unsigned | Hardware multiply         | 28                | 28     | 1.8 μs   | 2.8 μs   | 11.2 μs         | 28 μs   |  |

| 16x16 signed   | Without hardware multiply | 52                | 254    | 15.9 μs  | 25.4 μs  | 102.6 μs        | 254 μs  |  |

|                | Hardware multiply         | 35                | 40     | 2.5 μs   | 4.0 μs   | 16.0 μs         | 40 μs   |  |

### TABLE 12-1: PERFORMANCE COMPARISON FOR VARIOUS MULTIPLY OPERATIONS

| R/W-0/0                                               | R/W-0/0                              | R/W-0/0      | R/W-0/0         | R/W-0/0                            | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |

|-------------------------------------------------------|--------------------------------------|--------------|-----------------|------------------------------------|---------|---------|---------|--|--|

| ODCx7                                                 | ODCx6                                | ODCx5        | ODCx4           | ODCx3                              | ODCx2   | ODCx1   | ODCx0   |  |  |

| bit 7                                                 |                                      |              |                 |                                    |         |         | bit 0   |  |  |

|                                                       |                                      |              |                 |                                    |         |         |         |  |  |

| Legend:                                               |                                      |              |                 |                                    |         |         |         |  |  |

| R = Readable                                          | bit                                  | W = Writable | bit             | U = Unimplemented bit, read as '0' |         |         |         |  |  |

| '1' = Bit is set                                      | 1' = Bit is set '0' = Bit is cleared |              | x = Bit is unkr | nown                               |         |         |         |  |  |

| -n/n = Value at POR and BOR/Value at all other Resets |                                      |              |                 |                                    |         |         |         |  |  |

#### REGISTER 15-6: ODCONx: OPEN-DRAIN CONTROL REGISTER

bit 7-0

ODCx<7:0>: Open-Drain Configuration on Pins Rx<7:0>

1 = Output drives only low-going signals (sink current only)

0 = Output drives both high-going and low-going signals (source and sink current)

TABLE 15-6: OPEN-DRAIN CONTROL REGISTERS

| Name   | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|--------|---------|---------|---------|---------|---------|---------|---------|---------|

| ODCONA | ODCONA7 | ODCONA6 | ODCONA5 | ODCONA4 | ODCONA3 | ODCONA2 | ODCONA1 | ODCONA0 |

| ODCONB | ODCONB7 | ODCONB6 | ODCONB5 | ODCONB4 | ODCONB3 | ODCONB2 | ODCONB1 | ODCONB0 |

| ODCONC | ODCONC7 | ODCONC6 | ODCONC5 | ODCONC4 | ODCONC3 | ODCONC2 | ODCONC1 | ODCONC0 |

| ODCOND | ODCOND7 | ODCOND6 | ODCOND5 | ODCOND4 | ODCOND3 | ODCOND2 | ODCOND1 | ODCOND0 |

| ODCONE | ODCONE7 | ODCONE6 | ODCONE5 | ODCONE4 | ODCONE3 | ODCONE2 | ODCONE1 | ODCONE0 |

| ODCONF | ODCONF7 | ODCONF6 | ODCONF5 | ODCONF4 | ODCONF3 | ODCONF2 | ODCONF1 | ODCONF0 |

| ODCONG | ODCONG7 | ODCONG6 | _       | ODCONG4 | ODCONG3 | ODCONG2 | ODCONG1 | ODCONG0 |

| ODCONH | _       | _       | _       | _       | ODCONH3 | ODCONH2 | ODCONH1 | ODCONH0 |

| Name       | Bit 7 | Bit 6 | Bit 5 | Bit 4       | Bit 3 | Bit 2      | Bit 1 | Bit 0 | Register<br>on page |

|------------|-------|-------|-------|-------------|-------|------------|-------|-------|---------------------|

| MDCARLPPS  | —     | —     |       |             | MDCA  | RLPPS<5:0> | >     |       | 225                 |

| MDCARHPPS  | _     | _     |       |             | MDCA  | RHPPS<5:0  | >     |       | 225                 |

| MDSRCPPS   | —     | _     |       |             | MDSF  | RCPPS<5:0> |       |       | 225                 |

| ADACTPPS   | —     | _     |       |             | ADAC  | TPPS<5:0>  |       |       | 225                 |

| SSP1CLKPPS | _     | _     |       |             | SSP1C | LKPPS<5:0  | >     |       | 225                 |

| SSP1DATPPS | —     | _     |       |             | SSP1D | ATPPS<5:0  | >     |       | 225                 |

| SSP1SSPPS  | —     | —     |       |             | SSP1  | SSPPS<5:0> |       |       | 225                 |

| SSP2CLKPPS | —     | _     |       |             | SSP2C | LKPPS<5:0  | >     |       | 225                 |

| SSP2DATPPS | —     | _     |       |             | SSP2D | ATPPS<5:0  | >     |       | 225                 |

| SSP2SSPPS  | —     | _     |       |             | SSP2  | SSPPS<5:0> |       |       | 225                 |

| RX1PPS     | —     | _     |       |             | RX1   | PPS<5:0>   |       |       | 225                 |

| TX1PPS     | —     | _     |       |             | TX1   | PPS<5:0>   |       |       | 225                 |

| RX2PPS     | _     | _     |       |             | RX2   | PPS<5:0>   |       |       | 225                 |

| TX2PPS     | —     | _     |       |             | TX2   | PPS<5:0>   |       |       | 225                 |

| RX3PPS     | —     | _     |       |             | RX3   | PPS<5:0>   |       |       | 225                 |

| TX3PPS     | —     | —     |       |             | TX3   | PPS<5:0>   |       |       | 225                 |

| RX4PPS     | —     | _     |       |             | RX4   | PPS<5:0>   |       |       | 225                 |

| TX4PPS     | —     | _     |       | TX4PPS<5:0> |       |            |       |       | 225                 |

| RX5PPS     | —     | _     |       | RX5PPS<5:0> |       |            |       |       | 225                 |

| TX5PPS     | _     | _     |       | TX5PPS<5:0> |       |            |       |       |                     |

| RxyPPS     | _     | _     |       | RxyPPS<5:0> |       |            |       |       |                     |

#### TABLE 17-2: SUMMARY OF REGISTERS ASSOCIATED WITH THE PPS MODULE (CONTINUED)

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the PPS module.

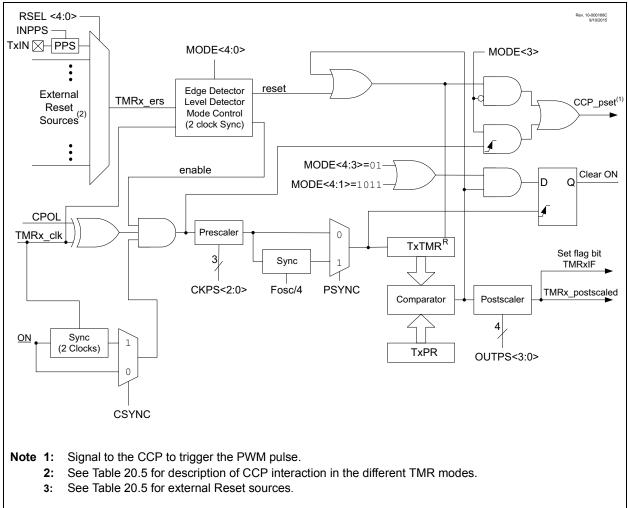

# 20.0 TIMER2/4/6/8 MODULE

The Timer2/4/6/8 modules are 8-bit timers that can operate as free-running period counters or in conjunction with external signals that control start, run, freeze, and reset operation in One-Shot and Monostable modes of operation. Sophisticated waveform control such as pulse density modulation are possible by combining the operation of these timers with other internal peripherals such as the comparators and CCP modules. Features of the timer include:

- 8-bit timer register

- 8-bit period register

- · Selectable external hardware timer Resets

- Programmable prescaler (1:1 to 1:128)

- Programmable postscaler (1:1 to 1:16)

- · Selectable synchronous/asynchronous operation

- · Alternate clock sources

- · Interrupt-on-period

- Three modes of operation:

- Free Running Period

- One-shot

- Monostable

See Figure 20-1 for a block diagram of Timer2. See Figure 20-2 for the clock source block diagram.

Note: Four identical Timer2 modules are implemented on this device. The timers are named Timer2, Timer4, Timer6 and Timer8. All references to Timer2 apply as well to Timer4, Timer6 and Timer8. All references to PR2 apply equally to other timers as well.

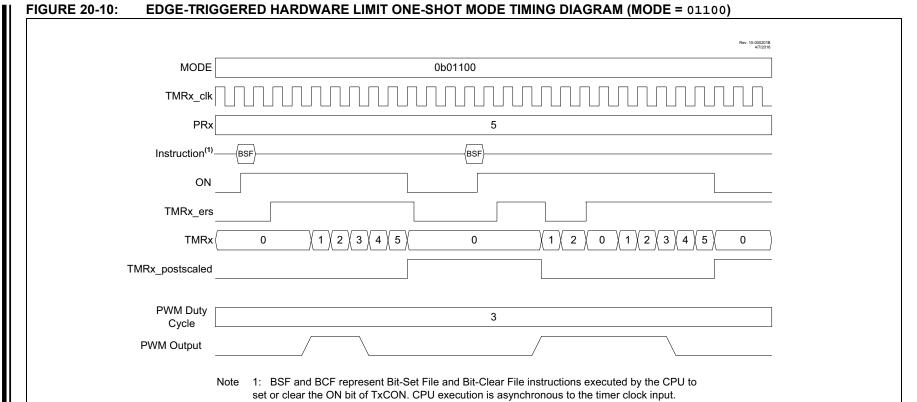

# FIGURE 20-1: TIMER2 BLOCK DIAGRAM

© -2017 Microchip Technology Inc.

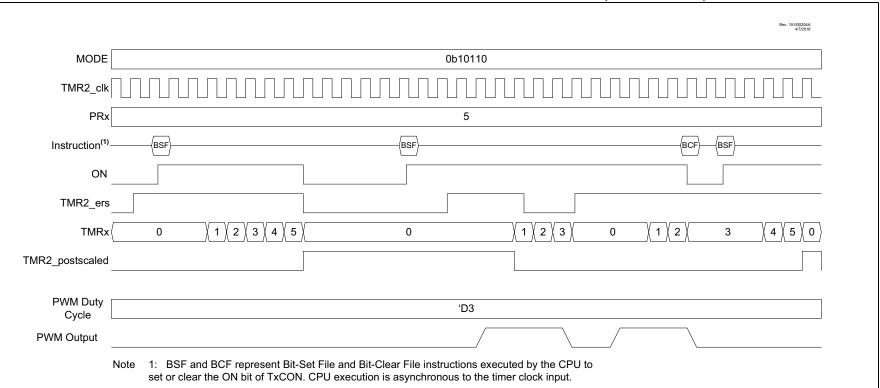

#### FIGURE 20-13: LEVEL-TRIGGERED HARDWARE LIMIT ONE-SHOT MODE TIMING DIAGRAM (MODE = 10110)

| U-0   | U-0 | U-0 | U-0 | R/W-0/0   | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|-------|-----|-----|-----|-----------|---------|---------|---------|--|

| _     | —   | —   | —   | RSEL<3:0> |         |         |         |  |

| bit 7 |     |     |     |           |         |         | bit 0   |  |

|       |     |     |     |           |         |         |         |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-4 Unimplemented: Read as '0'

bit 3-0 RSEL<3:0>: Timer2 External Reset Signal Source Selection bits

|           | TMR2                       | TMR4                       | TMR6                       | TMR8                       |

|-----------|----------------------------|----------------------------|----------------------------|----------------------------|

| RSEL<3:0> | Reset Source               | Reset Source               | Reset Source               | Reset Source               |

| 1111      | ZCD_OUT                    | ZCD_OUT                    | ZCD_OUT                    | ZCD_OUT                    |

| 1110      | CMP3OUT                    | CMP3OUT                    | CMP3OUT                    | CMP3OUT                    |

| 1101      | CMP2OUT                    | CMP2OUT                    | CMP2OUT                    | CMP2OUT                    |

| 1100      | CMP1OUT                    | CMP1OUT                    | CMP1OUT                    | CMP10UT                    |

| 1011      | PWM7OUT                    | PWM7OUT                    | PWM7OUT                    | PWM7OUT                    |

| 1010      | PWM6OUT                    | PWM6OUT                    | PWM6OUT                    | PWM6OUT                    |

| 1001      | CCP5OUT                    | CCP5OUT                    | CCP5OUT                    | CCP5OUT                    |

| 1000      | CCP4OUT                    | CCP4OUT                    | CCP4OUT                    | CCP4OUT                    |

| 0111      | CCP3OUT                    | CCP3OUT                    | CCP3OUT                    | CCP3OUT                    |

| 0110      | CCP2OUT                    | CCP2OUT                    | CCP2OUT                    | CCP2OUT                    |

| 0101      | CCP1OUT                    | CCP1OUT                    | CCP1OUT                    | CCP10UT                    |

| 0100      | TMR8 post-scaled           | TMR8 post-scaled           | TMR8 post-scaled           | Reserved                   |

| 0011      | TMR6 post-scaled           | TMR6 post-scaled           | Reserved                   | TMR6 post-scaled           |

| 0010      | TMR4 post-scaled           | Reserved                   | TMR4 post-scaled           | TMR4 post-scaled           |

| 0001      | Reserved                   | TMR2 post-scaled           | TMR2 post-scaled           | TMR2 post-scaled           |

| 0000      | Pin selected by<br>T2INPPS | Pin selected by<br>T4INPPS | Pin selected by<br>T6INPPS | Pin selected by<br>T8INPPS |

# 23.6 Handling VPEAK Variations

If the peak amplitude of the external voltage is expected to vary, the series resistor must be selected to keep the ZCD current source and sink below the design maximum range of  $\pm 600 \ \mu$ A and above a reasonable minimum range. A general rule of thumb is that the maximum peak voltage can be no more than six times the minimum peak voltage. To ensure that the maximum current does not exceed  $\pm 600 \ \mu$ A and the minimum is at least  $\pm 100 \ \mu$ A, compute the series resistance as shown in Equation 23-5. The compensating pull-up for this series resistance can be determined with Equation 23-4 because the pull-up value is independent from the peak voltage.

# EQUATION 23-5: SERIES R FOR V RANGE

$$R_{SERIES} = \frac{V_{MAXPEAK} + V_{MINPEAK}}{7 \times 10^{-4}}$$

# 23.7 Operation During Sleep

The ZCD current sources and interrupts are unaffected by Sleep.

# 23.8 Effects of a Reset

The ZCD circuit can be configured to default to the active or inactive state on Power-on-Reset (POR). When the  $\overline{ZCD}$  Configuration bit is cleared, the ZCD circuit will be active at POR. When the  $\overline{ZCD}$  Configuration bit is set, the ZCDSEN bit of the ZCDCON register must be set to enable the ZCD module.

# 23.9 Disabling the ZCD Module

The ZCD module can be disabled in two ways:

- Configuration Word 2H has the ZCD bit which disables the ZCD module when set, but it can be enabled using the ZCDSEN bit of the ZCDCON register (Register 23-1). If the ZCD bit is clear, the ZCD is always enabled.

- 2. The ZCD can also be disabled using the ZCDMD bit of the PMD3 register (Register 7-4). This is subject to the status of the ZCD bit.

| U-0                               | U-0                                                                                                      | R-x                                    | U-0                | R/W-0/0                        | R/W-0/0                                               | R/W-0/0 | R/W-0/0 |  |  |

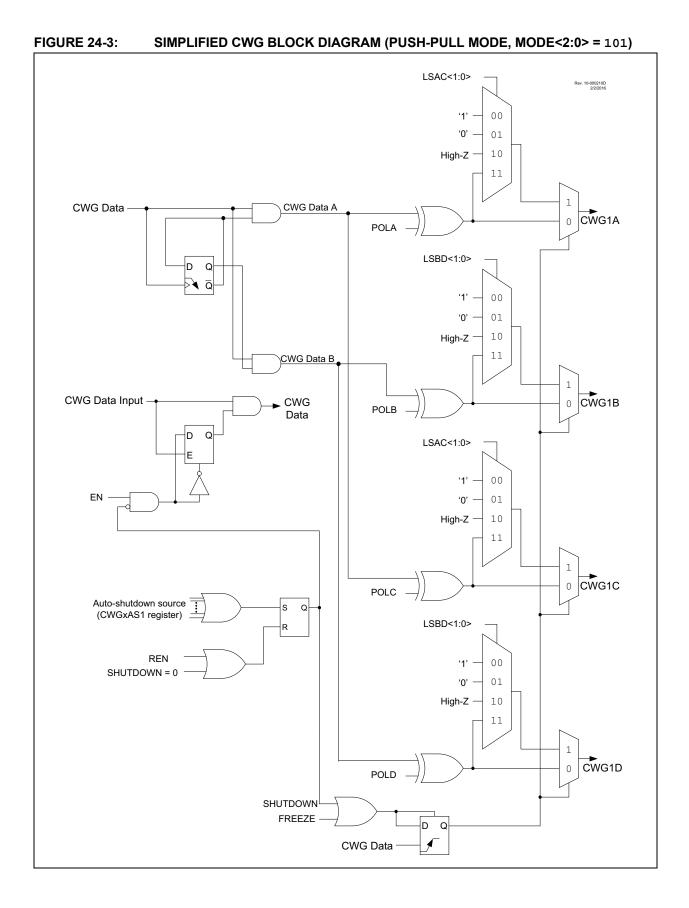

|-----------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------|--------------------|--------------------------------|-------------------------------------------------------|---------|---------|--|--|

| 0-0                               | 0-0                                                                                                      | IN                                     | 0-0                | POLD                           | POLC                                                  | POLB    | POLA    |  |  |

|                                   |                                                                                                          | IN                                     | _                  | POLD                           | POLC                                                  | POLB    |         |  |  |

| bit 7                             |                                                                                                          |                                        |                    |                                |                                                       |         | bit 0   |  |  |

|                                   |                                                                                                          |                                        |                    |                                |                                                       |         |         |  |  |

| Legend:                           |                                                                                                          |                                        |                    |                                |                                                       |         |         |  |  |

| R = Readable bit W = Writable bit |                                                                                                          | U = Unimplemented bit, read as '0'     |                    |                                |                                                       |         |         |  |  |

| u = Bit is unchanged x = E        |                                                                                                          | x = Bit is unkr                        | c = Bit is unknown |                                | -n/n = Value at POR and BOR/Value at all other Resets |         |         |  |  |

| '1' = Bit is set                  | '1' = Bit is set '0' = Bit is cleared                                                                    |                                        | ared               | q = Value depends on condition |                                                       |         |         |  |  |

|                                   |                                                                                                          |                                        |                    |                                |                                                       |         |         |  |  |

| bit 7-6                           | Unimplemen                                                                                               | ted: Read as '                         | 0'                 |                                |                                                       |         |         |  |  |

| bit 5                             | IN: CWG Inpu                                                                                             | ut Value bit (rea                      | ad-only)           |                                |                                                       |         |         |  |  |

| bit 4                             | Unimplemented: Read as '0'                                                                               |                                        |                    |                                |                                                       |         |         |  |  |

| bit 3                             | POLD: CWG                                                                                                | 1D Output Pola                         | arity bit          |                                |                                                       |         |         |  |  |

|                                   | 1 = Signal ou                                                                                            | 1 = Signal output is inverted polarity |                    |                                |                                                       |         |         |  |  |

|                                   | 0 = Signal ou                                                                                            | tput is normal p                       | olarity            |                                |                                                       |         |         |  |  |

| bit 2                             | POLC: CWG1C Output Polarity bit                                                                          |                                        |                    |                                |                                                       |         |         |  |  |

|                                   | 1 = Signal output is inverted polarity                                                                   |                                        |                    |                                |                                                       |         |         |  |  |

|                                   | 0 = Signal ou                                                                                            | tput is normal p                       | olarity            |                                |                                                       |         |         |  |  |

| bit 1                             | POLB: CWG1B Output Polarity bit                                                                          |                                        |                    |                                |                                                       |         |         |  |  |

|                                   | -                                                                                                        | tput is inverted                       |                    |                                |                                                       |         |         |  |  |

|                                   | -                                                                                                        | tput is normal p                       | -                  |                                |                                                       |         |         |  |  |

| bit 0                             |                                                                                                          | 1A Output Pola                         | 5                  |                                |                                                       |         |         |  |  |

|                                   | <ul> <li>1 = Signal output is inverted polarity</li> <li>0 = Signal output is normal polarity</li> </ul> |                                        |                    |                                |                                                       |         |         |  |  |

|                                   | 0 = Signal ou                                                                                            | tput is normal p                       | polarity           |                                |                                                       |         |         |  |  |

# REGISTER 24-2: CWG1CON1: CWG CONTROL REGISTER 1

### 25.7.3 PERIOD AND DUTY-CYCLE MODE

In Duty-Cycle mode, either the duty cycle or period (depending on polarity) of the SMTx\_signal can be acquired relative to the SMT clock. The CPW register is updated on a falling edge of the signal, and the CPR register is updated on a rising edge of the signal, along with the SMTxTMR resetting to 0x0001. In addition, the SMTxGO bit is reset on a rising edge when the SMT is in Single Acquisition mode. See Figure 25-6 and Figure 25-7.

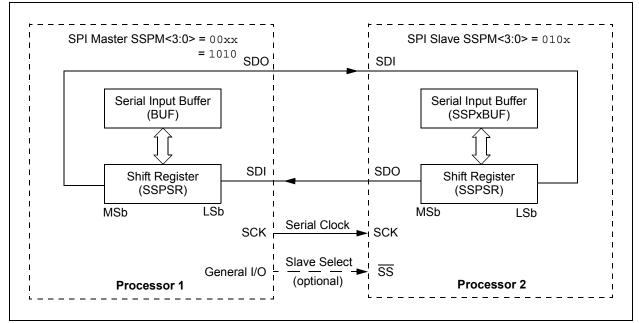

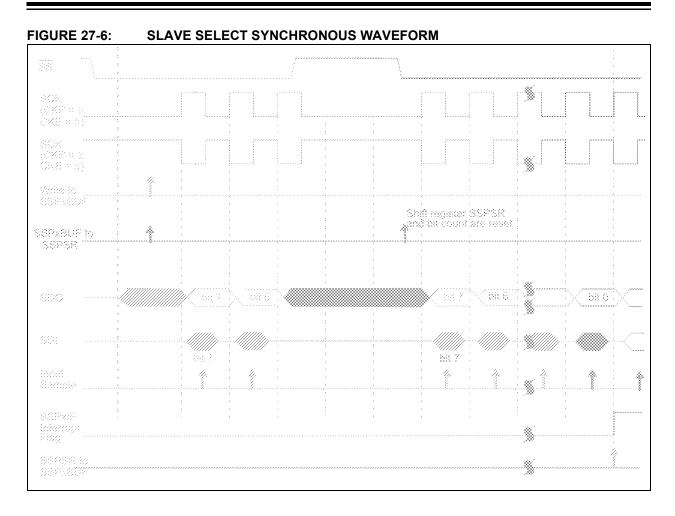

When the application software is expecting to receive valid data, the SSPxBUF should be read before the next byte of data to transfer is written to the SSPxBUF. The Buffer Full bit, BF of the SSPxSTAT register, indicates when SSPxBUF has been loaded with the received data (transmission is complete). When the SSPxBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSP interrupt is used to determine when the transmission/reception has completed. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur.

The SSPSR is not directly readable or writable and can only be accessed by addressing the SSPxBUF register. Additionally, the SSPxSTAT register indicates the various Status conditions.

#### FIGURE 27-3: SPI MASTER/SLAVE CONNECTION

# PIC18(L)F65/66K40

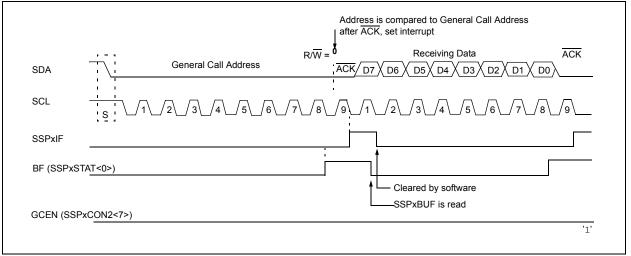

#### 27.9.8 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the  $I^2C$  bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master device. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an acknowledge.

The general call address is a reserved address in the I<sup>2</sup>C protocol, defined as address 0x00. When the GCEN bit of the SSPxCON2 register is set, the slave module will automatically ACK the reception of this address regardless of the value stored in SSPxADD. After the slave clocks in an address of all zeros with the R/W bit clear, an interrupt is generated and slave SSPxBUF software can read and respond. Figure 27-24 shows reception а general call sequence.

In 10-bit Address mode, the UA bit will not be set on the reception of the general call address. The slave will prepare to receive the second byte as data, just as it would in 7-bit mode. If the AHEN bit of the SSPxCON3 register is set, just as with any other address reception, the slave hardware will stretch the clock after the eighth falling edge of SCL. The slave must then set its ACKDT value and release the clock with communication progressing as it would normally.

#### 27.9.9 SSP MASK REGISTER

An SSP Mask (SSPxMSK) register (Register 27-12) is available in I<sup>2</sup>C Slave mode as a mask for the value held in the SSPSR register during an address comparison operation. A zero ('0') bit in the SSPxMSK register has the effect of making the corresponding bit of the received address a "don't care".

This register is reset to all '1's upon any Reset condition and, therefore, has no effect on standard SSP operation until written with a mask value.

The SSP Mask register is active during:

• 7-bit Address mode: address compare of A<7:1>.

10-bit Address mode: address compare of A<7:0> only. The SSP mask has no effect during the reception of the first (high) byte of the address.

# 28.6 EUSART Operation During Sleep

The EUSART will remain active during Sleep only in the Synchronous Slave mode. All other modes require the system clock and therefore cannot generate the necessary signals to run the Transmit or Receive Shift registers during Sleep.

Synchronous Slave mode uses an externally generated clock to run the Transmit and Receive Shift registers.

#### 28.6.1 SYNCHRONOUS RECEIVE DURING SLEEP

To receive during Sleep, all the following conditions must be met before entering Sleep mode:

- RCxSTA and TXxSTA Control registers must be configured for Synchronous Slave Reception (see Section 28.5.2.4 "Synchronous Slave Reception Setup:").

- If interrupts are desired, set the RCxIE bit of the PIE3/4 registers and the GIE and PEIE bits of the INTCON register.

- The RCxIF interrupt flag must be cleared by reading RCxREG to unload any pending characters in the receive buffer.

Upon entering Sleep mode, the device will be ready to accept data and clocks on the RXx/DTx and TXx/CKx pins, respectively. When the data word has been completely clocked in by the external device, the RCxIF interrupt flag bit of the PIR3/4 registers will be set. Thereby, waking the processor from Sleep.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the Global Interrupt Enable (GIE) bit of the INTCON register is also set, then the Interrupt Service Routine at address 004h will be called.

#### 28.6.2 SYNCHRONOUS TRANSMIT DURING SLEEP

To transmit during Sleep, all the following conditions must be met before entering Sleep mode:

- The RCxSTA and TXxSTA Control registers must be configured for synchronous slave transmission (see Section 28.5.2.2 "Synchronous Slave Transmission Setup").

- The TXxIF interrupt flag must be cleared by writing the output data to the TXxREG, thereby filling the TSR and transmit buffer.

- If interrupts are desired, set the TXxIE bit of the PIE3/4 registers and the PEIE bit of the INTCON register.

- Interrupt enable bits TXxIE of the PIE3 register and PEIE of the INTCON register must set.

Upon entering Sleep mode, the device will be ready to accept clocks on TXx/CKx pin and transmit data on the RXx/DTx pin. When the data word in the TSR has been completely clocked out by the external device, the pending byte in the TXxREG will transfer to the TSR and the TXxIF flag will be set. Thereby, waking the processor from Sleep. At this point, the TXxREG is available to accept another character for transmission, which will clear the TXxIF flag.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the Global Interrupt Enable (GIE) bit is also set then the Interrupt Service Routine at address 0004h will be called.

| R/W-x/x          | R/W-x/x | R/W-x/x           | R/W-x/x | R/W-x/x        | R/W-x/x          | R/W-x/x          | R/W-x/x      |

|------------------|---------|-------------------|---------|----------------|------------------|------------------|--------------|

|                  |         |                   | ADUTI   | H<15:8>        |                  |                  |              |

| bit 7            |         |                   |         |                |                  |                  | bit 0        |

|                  |         |                   |         |                |                  |                  |              |

| Legend:          |         |                   |         |                |                  |                  |              |

| R = Readable     | bit     | W = Writable b    | oit     | U = Unimpler   | nented bit, read | d as '0'         |              |

| u = Bit is unch  | anged   | x = Bit is unkn   | own     | -n/n = Value a | at POR and BC    | R/Value at all o | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                  |              |

### REGISTER 32-30: ADUTHH: ADC UPPER THRESHOLD HIGH BYTE REGISTER

bit 7-0 **ADUTH<15:8>**: ADC Upper Threshold MSB. ADLTH and ADUTH are compared with ADERR to set the ADUTHR and ADLTHR bits of ADSTAT. Depending on the setting of ADTMD, an interrupt may be triggered by the results of this comparison.

#### REGISTER 32-31: ADUTHL: ADC UPPER THRESHOLD LOW BYTE REGISTER

| R/W-x/x |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | ADUTH   | 1<7:0>  |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **ADUTH<7:0>**: ADC Upper Threshold LSB. ADLTH and ADUTH are compared with ADERR to set the ADUTHR and ADLTHR bits of ADSTAT. Depending on the setting of ADTMD, an interrupt may be triggered by the results of this comparison.

# 33.9 Comparator Response Time

The comparator output is indeterminate for a period of time after the change of an input source or the selection of a new reference voltage. This period is referred to as the response time. The response time of the comparator differs from the settling time of the voltage reference. Therefore, both of these times must be considered when determining the total response time to a comparator input change. See the Comparator and Voltage Reference Specifications in Table 37-15 and Table 37-17 for more details.

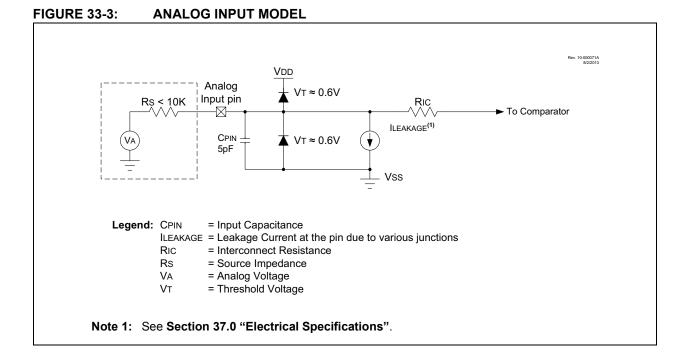

# 33.10 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 33-3. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and VSS. The analog input, therefore, must be between VSS and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

# 38.2 Standard Operating Conditions

| Operating Voltage: $VDDMIN \le VDD \le VDDMAX$                            |

|---------------------------------------------------------------------------|

| Operating Temperature: $TA\_MIN \le TA \le TA\_MAX$                       |

| VDD — Operating Supply Voltage <sup>(1)</sup>                             |

| PIC18LF65/66K40                                                           |

| VDDMIN (Fosc $\leq$ 16 MHz) +1.8V                                         |

| VDDMIN (Fosc $\leq$ 32 MHz) +2.5V                                         |

| VDDMIN (Fosc $\leq$ 64 MHz)                                               |

| VDDMAX                                                                    |

| PIC18F65/66K40                                                            |

| VDDMIN (Fosc $\leq$ 16 MHz)                                               |

| VDDMIN (Fosc $\leq$ 32 MHz)                                               |

| VDDMIN (Fosc $\leq$ 64 MHz)                                               |

| VDDMAX                                                                    |

| TA — Operating Ambient Temperature Range                                  |

| Industrial Temperature                                                    |

| TA_MIN40°C                                                                |

| TA_MAX                                                                    |

| Extended Temperature                                                      |

| TA_MIN40°C                                                                |

| <br>Ta_max                                                                |

| Note 1: See Parameter Supply Voltage, DS Characteristics: Supply Voltage. |