Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betalls                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 60                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.5K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 45x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 64-VQFN (9x9)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f66k40-e-mr |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC18(L)F65/66K40

#### PIC18(L)F6xK40 Family Types

| Device         | Data Sheet Index | Program Memory Flash<br>(words) | Data SRAM<br>(bytes) | Data EEPROM<br>(bytes) | I/O Pins | 16-bit Timers | Comparators | 10-bit ADC <sup>2</sup> with<br>Computation (ch) | 5-bit DAC | Zero-Cross Detect | CCP/10-bit PWM | DWD | Signal Measurement<br>Timer (SMT) | 8-bit TMR with HLT | Windowed Watchdog<br>Timer | <b>CRC</b> with Memory Scan | EUSART | I <sup>2</sup> C/SPI | Sdd | Peripheral Module Disable | Temperature Indicator | Debug <sup>(1)</sup> |

|----------------|------------------|---------------------------------|----------------------|------------------------|----------|---------------|-------------|--------------------------------------------------|-----------|-------------------|----------------|-----|-----------------------------------|--------------------|----------------------------|-----------------------------|--------|----------------------|-----|---------------------------|-----------------------|----------------------|

| PIC18(L)F65K40 | (1)              | 32k                             | 2048                 | 1024                   | 60       | 5             | 3           | 45                                               | 1         | 1                 | 5/2            | 1   | 2                                 | 4                  | Y                          | Υ                           | 5      | 2                    | Y   | Υ                         | Y                     | I                    |

| PIC18(L)F66K40 | (1)              | 64k                             | 3562                 | 1024                   | 60       | 5             | 3           | 45                                               | 1         | 1                 | 5/2            | 1   | 2                                 | 4                  | Y                          | Υ                           | 5      | 2                    | Υ   | Υ                         | Υ                     | Ι                    |

| PIC18(L)F67K40 | (2)              | 128k                            | 3562                 | 1024                   | 60       | 5             | 3           | 47                                               | 1         | 1                 | 5/2            | 1   | 2                                 | 4                  | Y                          | Υ                           | 5      | 2                    | Υ   | Υ                         | Υ                     | Ι                    |

**Note 1:** Debugging Methods: (I) – Integrated on Chip.

2.

Data Sheet Index: (Unshaded devices are described in this document.)

1. DS40001842 PIC18(L)F65/66K40 Data Sheet, 64-Pin, 8-bit Flash Microcontrollers

DS40001841 PIC18(L)F67K40 Data Sheet, 64-Pin, 8-bit Flash Microcontrollers

**Note:** For other small form-factor package availability and marking information, please visit http://www.microchip.com/packaging or contact your local sales office.

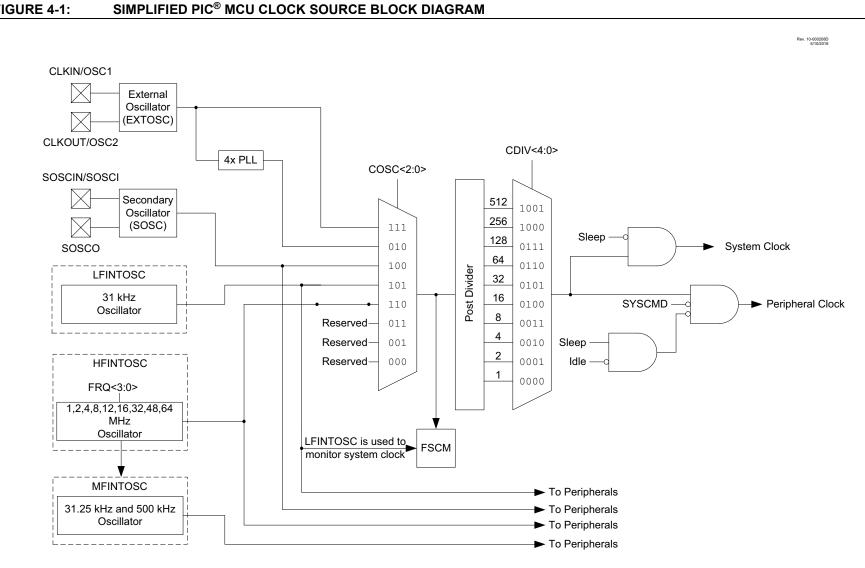

## FIGURE 4-1:

#### 4.3.2.1 HFINTOSC

The High-Frequency Internal Oscillator (HFINTOSC) is a precision digitally-controlled internal clock source that produces a stable clock up to 64 MHz. The HFINTOSC can be enabled through one of the following methods:

- Programming the RSTOSC<2:0> bits in Configuration Word 1 to '110' (Fosc = 1 MHz) or '000' (Fosc = 64 MHz) to set the oscillator upon device Power-up or Reset.

- Write to the NOSC<2:0> bits of the OSCCON1 register during run-time. See Section 4.4 "Clock Switching" for more information.

The HFINTOSC frequency can be selected by setting the HFFRQ<3:0> bits of the OSCFRQ register.

The NDIV<3:0> bits of the OSCCON1 register allow for division of the HFINTOSC output from a range between 1:1 and 1:512.

#### 4.3.2.2 MFINTOSC

The module provides two (500 kHz and 31.25 kHz) constant clock outputs. These clocks are digital divisors of the HFINTOSC clock. Dynamic divider logic is used to provide constant MFINTOSC clock rates for all settings of HFINTOSC.

The MFINTOSC cannot be used to drive the system but it is used to clock certain modules such as the Timers and WWDT.

#### 4.3.2.3 Internal Oscillator Frequency Adjustment

The internal oscillator is factory-calibrated. This internal oscillator can be adjusted in software by writing to the OSCTUNE register (Register 4-3).

The default value of the OSCTUNE register is 00h. The value is a 6-bit two's complement number. A value of 1Fh will provide an adjustment to the maximum frequency. A value of 20h will provide an adjustment to the minimum frequency.

When the OSCTUNE register is modified, the oscillator frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred.

OSCTUNE **does not affect** the LFINTOSC frequency. Operation of features that depend on the LFINTOSC clock source frequency, such as the Power-up Timer (PWRT), WWDT, Fail-Safe Clock Monitor (FSCM) and peripherals, are *not* affected by the change in frequency.

#### 4.3.2.4 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is a factory-calibrated 31 kHz internal clock source.

The LFINTOSC is the frequency for the Power-up Timer (PWRT), Windowed Watchdog Timer (WWDT) and Fail-Safe Clock Monitor (FSCM).

The LFINTOSC is enabled through one of the following methods:

- Programming the RSTOSC<2:0> bits of Configuration Word 1 to enable LFINTOSC.

- Write to the NOSC<2:0> bits of the OSCCON1 register during run-time. See Section 4.4, Clock Switching for more information.

#### 4.3.2.5 ADCRC

The ADCRC is an oscillator dedicated to the  $ADC^2$  module. The ADCRC oscillator can be manually enabled using the ADOEN bit of the OSCEN register. The ADCRC runs at a fixed frequency of 600 kHz. ADCRC is automatically enabled if it is selected as the clock source for the  $ADC^2$  module.

| Address | Name       | Bit 7           | Bit 6             | Bit 5        | Bit 4  | Bit 3   | Bit 2     | Bit 1        | Bit 0  | <u>Value on</u><br>POR, BOR |  |

|---------|------------|-----------------|-------------------|--------------|--------|---------|-----------|--------------|--------|-----------------------------|--|

| F42h    | CRCACCH    | ACC<15:8>       |                   |              |        |         |           |              |        |                             |  |

| F41h    | CRCACCL    |                 | ACC<7:0>          |              |        |         |           |              |        |                             |  |

| F40h    | CRCDATH    |                 | DATA<15:8>        |              |        |         |           |              |        |                             |  |

| F3Fh    | CRCDATL    |                 |                   |              | DAT    | A<7:0>  |           |              |        | xxxxxxxx                    |  |

| F3Eh    | CWG1STR    | OVRD            | OVRC              | OVRB         | OVRA   | STRD    | STRC      | STRB         | STRA   | 00000000                    |  |

| F3Dh    | CWG1AS1    | AS7E            | AS6E              | AS5E         | AS4E   | AS3E    | AS2E      | AS1E         | AS0E   | 00000000                    |  |

| F3Ch    | CWG1AS0    | SHUTDOWN        | REN               | LSBD         | 0<1:0> | LSAC    | C<1:0>    | —            | _      | 000101                      |  |

| F3Bh    | CWG1CON1   | —               | _                 | IN           | _      | POLD    | POLC      | POLB         | POLA   | x-0000                      |  |

| F3Ah    | CWG1CON0   | EN              | LD                | —            | _      | —       |           | MODE<2:0>    | 1      | 00000                       |  |

| F39h    | CWG1DBF    | —               | _                 |              |        | DBF     | <5:0>     |              |        | 000000                      |  |

| F38h    | CWG1DBR    | _               | _                 |              |        | DBF     | <5:0>     |              |        | 000000                      |  |

| F37h    | CWG1ISM    | _               | _                 | —            | _      |         | ISM       | <3:0>        |        | 0000                        |  |

| F36h    | CWG1CLKCON | _               | _                 | _            | _      | _       | _         | _            | CS     | 0                           |  |

| F35h    | CLKRCLK    | _               | _                 | _            | _      | _       |           | CLKRxCLK<2:0 | )>     | 000                         |  |

| F34h    | CLKRCON    | EN              | _                 | _            | CLKRE  | )C<1:0> |           | CLKRDIV<2:0  | >      | 010000                      |  |

| F33h    | T7CLK      | _               | _                 | _            | _      |         | CS<3:0>   |              |        |                             |  |

| F32h    | T7GATE     | _               | _                 | _            | _      |         | GSS<3:0>  |              |        | 0000                        |  |

| F31h    | T7GCON     | GE              | GPOL              | GTM          | GSPM   | GO/DONE | GVAL      | _            | _      | 00000x                      |  |

| F30h    | T7CON      | _               | _                 | СКРЗ         | S<1:0> | _       | SYNC      | RD16         | ON     | 00-000                      |  |

| F2Fh    | TMR7H      |                 |                   |              | TMR    | 5H<7:0> |           |              |        | 00000000                    |  |

| F2Eh    | TMR7L      |                 |                   |              | TMR    | 5L<7:0> |           |              |        | 00000000                    |  |

| F2Dh    | T8RST      | _               | _                 | _            | _      |         | RSE       | L<3:0>       |        | 0000                        |  |

| F2Ch    | T8CLKCON   | _               | _                 | _            | _      |         | CS        | <3:0>        |        | 0000                        |  |

| F2Bh    | T8HLT      | PSYNC           | CPOL              | CSYNC        |        |         | MODE<4:0> |              |        | 00000000                    |  |

| F2Ah    | T8CON      | ON              |                   | CKPS<2:0>    |        |         | OUTF      | PS<3:0>      |        | 00000000                    |  |

| F29h    | T8PR       | TMR2 Period R   | egister           |              |        |         |           |              |        | 11111111                    |  |

| F28h    | T8TMR      | Holding Registe | r for the 8-bit 7 | MR2 Register |        |         |           |              |        | 00000000                    |  |

| F27h    | CCP3CAP    | _               | _                 | _            | _      | _       | _         | CTS          | S<1:0> | 00                          |  |

| F26h    | CCP3CON    | EN              | _                 | OUT          | FMT    |         | MOD       | E<3:0>       |        | 0-000000                    |  |

| F25h    | ССРЗН      | Capture/Compa   | are/PWM Regis     | ster 3 (MSB) |        |         |           |              |        | xxxxxxx                     |  |

| F24h    | CCP3L      | Capture/Compa   | are/PWM Regis     | ster 3 (LSB) |        |         |           |              |        | xxxxxxx                     |  |

| F23h    | CCP4CAP    | _               | _                 | _            | _      | _       | _         | CTS          | S<1:0> | 00                          |  |

| F22h    | CCP4CON    | EN              | _                 | OUT          | FMT    |         | MOD       | E<3:0>       |        | 0-000000                    |  |

| F21h    | CCPR4H     | Capture/Compa   | are/PWM Regis     | ster 4 (MSB) |        |         |           |              |        | xxxxxxxx                    |  |

| F20h    | CCPR4L     | Capture/Compa   | are/PWM Regis     | ster 4 (LSB) |        |         |           |              |        | xxxxxxxx                    |  |

| F1Fh    | CCP5CAP    | _               | —                 | _            | _      | —       | _         | CTS          | S<1:0> | 00                          |  |

| F1Eh    | CCP5CON    | EN              | _                 | OUT          | FMT    |         | MOD       | E<3:0>       |        | 0-000000                    |  |

| F1Dh    | CCPR5H     | Capture/Compa   | are/PWM Regi      | ster 5 (MSB) | 1      | 1       |           |              |        | xxxxxxxx                    |  |

| F1Ch    | CCPR5L     | Capture/Compa   | are/PWM Regi      | ster 5 (LSB) |        |         |           |              |        | xxxxxxxx                    |  |

| F1Bh    | SMT1WIN    | _               | _                 | _            |        |         | WSEL<4:0> |              |        | 00000                       |  |

| F1Ah    | SMT1SIG    | _               | _                 | _            |        |         | SSEL<4:0> |              |        | 00000                       |  |

#### TABLE 10-5: REGISTER FILE SUMMARY FOR PIC18(L)F6XK40 DEVICES (CONTINUED)

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition

Note 1: Not available on LF devices.

Example 12-3 shows the sequence to do a 16 x 16 unsigned multiplication. Equation 12-1 shows the algorithm that is used. The 32-bit result is stored in four registers (RES<3:0>).

#### EQUATION 12-1: 16 x 16 UNSIGNED MULTIPLICATION ALGORITHM

| RES3:RES0 | = | ARG1H:ARG1L • ARG2H:ARG2L                |

|-----------|---|------------------------------------------|

|           | = | $(ARG1H \bullet ARG2H \bullet 2^{16}) +$ |

|           |   | $(ARG1H \bullet ARG2L \bullet 2^8) +$    |

|           |   | $(ARG1L \bullet ARG2H \bullet 2^8) +$    |

|           |   | (ARG1L • ARG2L)                          |

|           |   |                                          |

#### EXAMPLE 12-3: 16 x 16 UNSIGNED MULTIPLY ROUTINE

|   | MOVF   | ARG1L, W    |                   |

|---|--------|-------------|-------------------|

|   | MULWF  | ARG2L       | ; ARG1L * ARG2L-> |

|   |        |             | ; PRODH:PRODL     |

|   | MOVFF  | PRODH, RES1 | i                 |

|   | MOVFF  | PRODL, RESO | ;                 |

| ; |        |             |                   |

|   |        | ARG1H, W    |                   |

|   | MULWF  | ARG2H       | ; ARG1H * ARG2H-> |

|   |        |             | ; PRODH:PRODL     |

|   |        | PRODH, RES3 | ;                 |

|   | MOVFF  | PRODL, RES2 | ;                 |

| ; |        |             |                   |

|   |        | ARG1L, W    |                   |

|   | MULWF  | ARG2H       | ; ARG1L * ARG2H-> |

|   |        |             | ; PRODH:PRODL     |

|   |        | PRODL, W    | ;                 |

|   |        | RES1, F     | ; Add cross       |

|   |        | PRODH, W    | ; products        |

|   |        | RES2, F     | i                 |

|   | CLRF   |             | i                 |

|   | ADDWFC | RES3, F     | ;                 |

| ; |        |             |                   |

|   |        | ARG1H, W    | ;                 |

|   | MOLWF. | ARG2L       | ; ARG1H * ARG2L-> |

|   | MOUTE  | DDODI W     | ; PRODH:PRODL     |

|   |        | PRODL, W    | <i>i</i>          |

|   |        | RES1, F     | ; Add cross       |

|   |        | PRODH, W    | ; products        |

|   |        | RES2, F     | ,                 |

|   | CLRF   |             | ,                 |

|   | ADDWFC | RES3, F     | ,                 |

Example 12-4 shows the sequence to do a 16 x 16 signed multiply. Equation 12-2 shows the algorithm used. The 32-bit result is stored in four registers (RES<3:0>). To account for the sign bits of the arguments, the MSb for each argument pair is tested and the appropriate subtractions are done.

#### EQUATION 12-2: 16 x 16 SIGNED MULTIPLICATION ALGORITHM

| RES3:RES0 = ARG1H:ARG1L • ARG2H:ARG2L                           |

|-----------------------------------------------------------------|

| $= (ARG1H \bullet ARG2H \bullet 2^{16}) +$                      |

| $(ARG1H \bullet ARG2L \bullet 2^8) +$                           |

| $(ARG1L \bullet ARG2H \bullet 2^8) +$                           |

| $(ARG1L \bullet ARG2L) +$                                       |

| $(-1 \bullet ARG2H < 7 > \bullet ARG1H:ARG1L \bullet 2^{16}) +$ |

| $(-1 \bullet ARG1H < 7 > \bullet ARG2H:ARG2L \bullet 2^{16})$   |

|                                                                 |

#### EXAMPLE 12-4: 16 x 16 SIGNED MULTIPLY ROUTINE

| MOVF      | ARG1L, W              |                                        |

|-----------|-----------------------|----------------------------------------|

| MULWF     | ARG2L                 | ; ARG1L * ARG2L ->                     |

|           |                       | ; PRODH:PRODL                          |

| MOVFF     | PRODH, RES1           | ;                                      |

| MOVFF     |                       |                                        |

| ;         |                       |                                        |

| MOVF      | ARG1H, W              |                                        |

|           | ARG2H                 | ; ARG1H * ARG2H ->                     |

|           |                       | ; PRODH:PRODL                          |

| MOVEE     | PRODH, RES3           |                                        |

| MOVFF     |                       |                                        |

| ;         |                       |                                        |

| MOVF      | ARG1L, W              |                                        |

|           | ARG2H                 | ; ARG1L * ARG2H ->                     |

|           |                       | ; PRODH:PRODL                          |

| MOVF      | PRODL, W              | i inodii inodd                         |

| ADDWF     |                       | ; Add cross                            |

| MOVE      | PRODH, W              | ; products                             |

| ADDWF     | C RES2, F             | ;                                      |

| CLRF      | WREG                  | ;                                      |

| ADDWF     | C RES3, F             | i                                      |

| ;         |                       |                                        |

| MOVE      | ARG1H, W              | i                                      |

| MULWF     |                       | ; ARG1H * ARG2L ->                     |

|           |                       | ; PRODH:PRODL                          |

| MOVF      | PRODL, W              | i                                      |

|           | RES1, F               | ; Add cross                            |

| MOVF      |                       | ; products                             |

| ADDWF     | C RES2, F             | ;                                      |

| CLRF      | WREG                  | i                                      |

| ADDWF     | C RES3, F             | ;                                      |

| ;         |                       |                                        |

| BTFSS     | ARG2H, 7<br>SIGN_ARG1 | ; ARG2H:ARG2L neg?                     |

| BRA       | SIGN_ARG1             | ; ARG2H:ARG2L neg?<br>; no, check ARG1 |

| MOVF      | ARG1L, W              | ;                                      |

| SUBWF     | RES2                  | ;                                      |

| MOVF      |                       | ;                                      |

| SUBWF     | 'B RES3               |                                        |

| ;         |                       |                                        |

| SIGN_ARG1 |                       |                                        |

| BTFSS     | ARG1H, 7              | ; ARG1H:ARG1L neg?                     |

| BRA       | CONT_CODE             | ; ARG1H:ARG1L neg?<br>; no, done       |

| MOVF      | ARG2L, W              | ;                                      |

| SUBWF     |                       | ;                                      |

| MOVF      | ARG2H, W              | ;                                      |

| SUBWF     | 'B RES3               |                                        |

| ;         |                       |                                        |

| CONT_CODE |                       |                                        |

| :         |                       |                                        |

| L         |                       |                                        |

#### 13.9 Program Memory Scan Configuration

If desired, the program memory scan module may be used in conjunction with the CRC module to perform a CRC calculation over a range of program memory addresses. In order to set up the scanner to work with the CRC you need to perform the following steps:

- Set the Enable bit in both the CRCCON0 and SCANCON0 registers. If they get disabled, all internal states of the scanner and the CRC are reset (registers are unaffected).

- Choose which memory access mode is to be used (see Section 13.11 "Scanning Modes") and set the MODE bits of the SCANCON0 register appropriately.

- 3. Based on the memory access mode, set the INTM bits of the SCANCON0 register to the appropriate interrupt mode (see Section 13.11.5 "Interrupt Interaction")

- 4. Set the SCANLADRL/H/U and SCANHADRL/H/ U registers with the beginning and ending locations in memory that are to be scanned.

- 5. The CRCGO bit must be set before setting the SCANGO bit. Setting the SCANGO bit starts the scan. Both CRCEN and CRCGO bits must be enabled to use the scanner. When either of these bits are disabled, the scan aborts and the INVALID bit SCANCON0 is set. The scanner will wait for the signal from the CRC that it is ready for the first Flash memory location, then begin loading data into the CRC. It will continue to do so until it either hits the configured end address or an address that is unimplemented on the device, at which point the SCANGO bit will clear, Scanner functions will cease, and the SCANIF interrupt will be triggered. Alternately, the SCANGO bit can be cleared in software if desired.

### 13.10 Scanner Interrupt

The scanner will trigger an interrupt when the SCANGO bit transitions from '1' to '0'. The SCANIF interrupt flag of PIR7 is set when the last memory location is reached and the data is entered into the CRCDATA registers. The SCANIF bit can only be cleared in software. The SCAN interrupt enable is the SCANIE bit of the PIE7 register.

## 13.11 Scanning Modes

The memory scanner can scan in four modes: Burst, Peek, Concurrent, and Triggered. These modes are controlled by the MODE bits of the SCANCON0 register. The four modes are summarized in Table 13-2.

#### 13.11.1 BURST MODE

When MODE = 01, the scanner is in Burst mode. In Burst mode, CPU operation is stalled beginning with the operation after the one that sets the SCANGO bit, and the scan begins, using the instruction clock to execute. The CPU is held in its current state until the scan stops. Note that because the CPU is not executing instructions, the SCANGO bit cannot be cleared in software, so the CPU will remain stalled until one of the hardware endconditions occurs. Burst mode has the highest throughput for the scanner, but has the cost of stalling other execution while it occurs.

#### 13.11.2 CONCURRENT MODE

When MODE = 00, the scanner is in Concurrent mode. Concurrent mode, like Burst mode, stalls the CPU while performing accesses of memory. However, while Burst mode stalls until all accesses are complete, Concurrent mode allows the CPU to execute in between access cycles.

#### 13.11.3 TRIGGERED MODE

When MODE = 11, the scanner is in Triggered mode. Triggered mode behaves identically to Concurrent mode, except instead of beginning the scan immediately upon the SCANGO bit being set, it waits for a rising edge from a separate trigger clock, the source of which is determined by the SCANTRIG register.

#### 13.11.4 PEEK MODE

When MODE = 10, the scanner is in Peek mode. Peek mode waits for an instruction cycle in which the CPU does not need to access the NVM (such as a branch instruction) and uses that cycle to do its own NVM access. This results in the lowest throughput for the NVM access (and can take a much longer time to complete a scan than the other modes), but does so without any impact on execution times, unlike the other modes.

#### 14.9 **INTn Pin Interrupts**

PIC18(L)F6xK40 devices have four external interrupt sources which can be assigned to any pin on PORTA and PORTB using PPS. The external interrupt sources are edge-triggered. If the corresponding INTxEDG bit in the INTCON0 register is set (= 1), the interrupt is triggered by a rising edge. It the bit is clear, the trigger is on the falling edge.

All external interrupts (INT0, INT1, INT2 and INT3) can wake-up the processor from Idle or Sleep modes if bit INTxE was set prior to going into those modes. If the Global Interrupt Enable bit, GIE/GIEH, is set, the processor will branch to the interrupt vector following wake-up.

Interrupt priority is determined by the value contained in the interrupt priority bits, INT0IP, INT1IP, INT2IP and INT3 of the IPR0 register.

#### 14.10 TMR0 Interrupt

In 8-bit mode (which is the default), an overflow in the TMR0 register (FFh  $\rightarrow$  00h) will set flag bit, TMR0IF. In 16-bit mode, an overflow in the TMR0H:TMR0L register pair (FFFFh  $\rightarrow$  0000h) will set TMR0IF. The interrupt can be enabled/disabled by setting/clearing enable bit, TMR0IE of the PIE0 register. Interrupt priority for Timer0 is determined by the value contained in the interrupt priority bit, TMR0IP of the IPR0 register. See Section 18.0 "Timer0 Module" for further details on the Timer0 module.

#### 14.11 Interrupt-on-Change

An input change on any port pins that support IOC sets Flag bit, IOCIF of the PIR0 register. The interrupt can be enabled/disabled by setting/clearing the enable bit, IOCIE of the PIE0 register. Pins must also be individually enabled in the IOCxP and IOCxN register. IOCIF is a read-only bit and the flag can be cleared by clearing the corresponding IOCxF registers. For more information refer to Section 16.0 "Interrupt-on-Change".

### 14.12 Context Saving During Interrupts

During interrupts, the return PC address is saved on the stack. Additionally, the WREG, STATUS and BSR registers are saved on the fast return stack. If a fast return from interrupt is not used (see Section 10.2.2 "Fast Register Stack"), the user may need to save the WREG, STATUS and BSR registers on entry to the Interrupt Service Routine. Depending on the user's application, other registers may also need to be saved. Example 14-1 saves and restores the WREG, STATUS and BSR registers during an Interrupt Service Routine.

| EXAMPL   | E 14-1: SAVING STATUS | , WREG AND BSR REGISTERS IN RAM |  |

|----------|-----------------------|---------------------------------|--|

| MOVWF    | W_TEMP                | ; W_TEMP is in virtual bank     |  |

| MOVFF    | STATUS, STATUS_TEMP   | ; STATUS_TEMP located anywhere  |  |

| MOVFF    | BSR, BSR_TEMP         | ; BSR_TEMP located anywhere     |  |

| ;        |                       |                                 |  |

| ; USER I | ISR CODE              |                                 |  |

| ;        |                       |                                 |  |

| MOVFF    | BSR_TEMP, BSR         | ; Restore BSR                   |  |

| MOVF     | W_TEMP, W             | ; Restore WREG                  |  |

| MOVFF    | STATUS_TEMP, STATUS   | ; Restore STATUS                |  |

|          |                       |                                 |  |

####

# 17.0 PERIPHERAL PIN SELECT (PPS) MODULE

The Peripheral Pin Select (PPS) module connects peripheral inputs and outputs to the device I/O pins. Only digital signals are included in the selections. All analog inputs and outputs remain fixed to their assigned pins. Input and output selections are independent as shown in the simplified block diagram Figure 17-1.

The peripheral input is selected with the peripheral xxxPPS register (Register 17-1), and the peripheral output is selected with the PORT RxyPPS register (Register 17-2). For example, to select PORTC<7> as the EUSART1 RX input, set RXxPPS to 6 ' b01 0111, and to select PORTC<6> as the EUSART1 TX output set RC6PPS to 6 ' b00 1100.

## 17.1 PPS Inputs

Each peripheral has a PPS register with which the inputs to the peripheral are selected. Inputs include the device pins.

Multiple peripherals can operate from the same source simultaneously. Port reads always return the pin level regardless of peripheral PPS selection. If a pin also has analog functions associated, the ANSEL bit for that pin must be cleared to enable the digital input buffer.

Although every peripheral has its own PPS input selection register, the selections are identical for every peripheral as shown in Register 17-1.

**Note:** The notation "xxx" in the register name is a place holder for the peripheral identifier. For example, INTOPPS.

### 17.2 PPS Outputs

Each I/O pin has a PPS register with which the pin output source is selected. With few exceptions, the port TRIS control associated with that pin retains control over the pin output driver. Peripherals that control the pin output driver as part of the peripheral operation will override the TRIS control as needed. These peripherals include:

- EUSART (synchronous operation)

- MSSP (I<sup>2</sup>C)

Although every pin has its own PPS peripheral selection register, the selections are identical for every pin as shown in Register 17-2.

**Note:** The notation "Rxy" is a place holder for the pin identifier. For example, RA0PPS.

| 7-2: RxyPP | S: PIN Rxy C                                                             | DUTPUT SO                                                  | URCE SELE                                     | CTION REGIS                                                                                                                                         | SIER                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                              |

|------------|--------------------------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| U-0        | R/W-0/u                                                                  | R/W-0/u                                                    | R/W-0/u                                       | R/W-0/u                                                                                                                                             | R/W-0/u                                                                                                                                                                                                                | R/W-0/u                                                                                                                                                                                                                                                      |

| —          |                                                                          |                                                            | RxyPF                                         | PS<5:0>                                                                                                                                             |                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                              |

|            |                                                                          |                                                            |                                               |                                                                                                                                                     |                                                                                                                                                                                                                        | bit 0                                                                                                                                                                                                                                                        |

|            |                                                                          |                                                            |                                               |                                                                                                                                                     |                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                              |

|            |                                                                          |                                                            |                                               |                                                                                                                                                     |                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                              |

| bit        | W = Writable                                                             | bit                                                        | U = Unimplem                                  | nented bit, read                                                                                                                                    | l as '0'                                                                                                                                                                                                               |                                                                                                                                                                                                                                                              |

| anged      | x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets |                                                            |                                               |                                                                                                                                                     |                                                                                                                                                                                                                        | ther Resets                                                                                                                                                                                                                                                  |

|            | '0' = Bit is clea                                                        | ared                                                       |                                               |                                                                                                                                                     |                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                              |

|            | U-0<br>—                                                                 | U-0 R/W-0/u<br>— Dit W = Writable<br>anged x = Bit is unkr | U-0 R/W-0/u R/W-0/u<br>— Dit W = Writable bit | U-0     R/W-0/u     R/W-0/u       —     RxyPF       Dit     W = Writable bit     U = Unimplen anged       x = Bit is unknown     -n/n = Value anged | U-0       R/W-0/u       R/W-0/u       R/W-0/u         —       RxyPPS<5:0>         Dit       W = Writable bit       U = Unimplemented bit, read         anged       x = Bit is unknown       -n/n = Value at POR and BO | U-0       R/W-0/u       R/W-0/u       R/W-0/u       R/W-0/u         —       RxyPPS<5:0>         Dit       W = Writable bit       U = Unimplemented bit, read as '0'         anged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all or |

#### CICTI

bit 7-6 Unimplemented: Read as '0'

# PIC18(L)F65/66K40

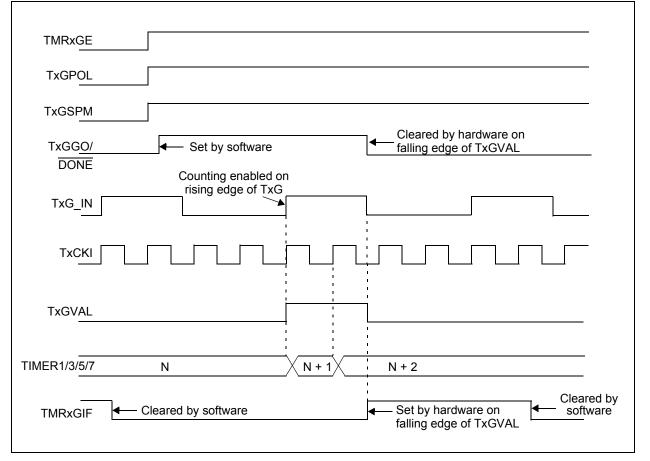

| FIGURE 19-5: | TIMER1/3/5/7 GATE TOGGLE MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TMRxGE       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TxGPOL       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TxGTM        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TxTxG_IN     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ТхСКІ        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TxGVAL       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TIMER1/3/5/7 | $N = \frac{1}{N+1} \times \frac{1}{N+2} \times \frac{1}{N+3} \times \frac{1}{N+4} = \frac{1}{N+5} \times \frac{1}{N+6} \times \frac{1}{N+7} \times \frac{1}{N+8} = \frac{1}{N+5} \times \frac{1}{N+6} \times $ |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

#### FIGURE 19-6: TIMER1/3/5/7 GATE SINGLE-PULSE MODE

#### 20.5.2 HARDWARE GATE MODE