Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 60                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 3.5K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 45x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-VFQFN Exposed Pad                                                        |

| Supplier Device Package    | 64-VQFN (9×9)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f66k40t-i-mr |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

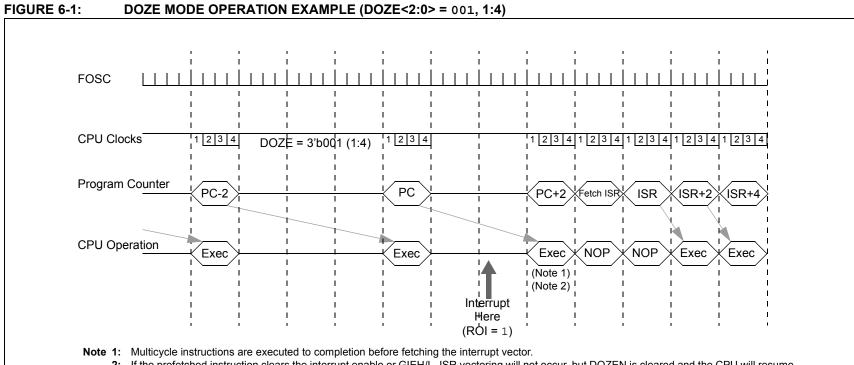

2: If the prefetched instruction clears the interrupt enable or GIEH/L, ISR vectoring will not occur, but DOZEN is cleared and the CPU will resume execution at full speed.

#### 8.5 Low-Power Brown-out Reset (LPBOR)

The Low-Power Brown-out Reset (LPBOR) provides an additional BOR circuit for low power operation. Refer to Figure 8-2 to see how the BOR interacts with other modules.

The LPBOR is used to monitor the external VDD pin. When too low of a voltage is detected, the device is held in Reset.

#### 8.5.1 ENABLING LPBOR

The LPBOR is controlled by the LPBOREN bit of Configuration Word 2L. When the device is erased, the LPBOR module defaults to disabled.

#### 8.5.1.1 LPBOR Module Output

The output of the LPBOR module is a signal indicating whether or not a Reset is to be asserted. This signal is OR'd together with the Reset signal of the BOR module to provide the generic BOR signal, which goes to the PCON0 register and to the power control block.

## 8.6 MCLR

The MCLR is an optional external input that can reset the device. The MCLR function is controlled by the MCLRE bit of Configuration Words and the LVP bit of Configuration Words (Table 8-2). The RMCLR bit in the PCON0 register will be set to '0' if a MCLR has occurred.

TABLE 8-2:

MCLR CONFIGURATION

| MCLRE | LVP | MCLR     |

|-------|-----|----------|

| х     | 1   | Enabled  |

| 1     | 0   | Enabled  |

| 0     | 0   | Disabled |

## 8.6.1 MCLR ENABLED

When MCLR is enabled and the pin is held low, the device is held in Reset. The MCLR pin is connected to VDD through an internal weak pull-up.

The device has a noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

| Note: | An internal Reset event (RESET, instr, |

|-------|----------------------------------------|

|       | BOR, WWDT, POR STK), does not drive    |

|       | the MCLR pin low.                      |

### 8.6.2 MCLR DISABLED

When MCLR is disabled, the MCLR becomes input-only and pin functions such as internal weak pull-ups are under software control. See Section 15.1 "I/O Priorities" for more information.

## 8.7 Windowed Watchdog Timer (WWDT) Reset

The Windowed Watchdog Timer generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period or window set. The TO and PD bits in the STATUS register and the RWDT bit in the PCON0 register are changed to indicate a WDT Reset. The WDTWV bit in the PCON0 register indicates if the WDT Reset has occurred due to a time out or a window violation. See Section 9.0 "Windowed Watchdog Timer (WWDT)" for more information.

#### 8.8 RESET Instruction

A RESET instruction will cause a device Reset. The  $\overline{RI}$  bit in the PCON0 register will be set to '0'. See Table 8-3 for default conditions after a RESET instruction has occurred.

### 8.9 Stack Overflow/Underflow Reset

The device can reset when the Stack Overflows or Underflows. The STKOVF or STKUNF bits of the PCON0 register indicate the Reset condition. These Resets are enabled by setting the STVREN bit in Configuration Words. See **Section 10.2.1 "Stack Overflow and Underflow Resets"** for more information.

## 8.10 Programming Mode Exit

Upon exit of Programming mode, the device will behave as if a POR had just occurred.

## 8.11 Power-up Timer (PWRT)

The Power-up Timer provides a nominal 66 ms (2048 cycles of LFINTOSC) time out on POR or Brown-out Reset.

The device is held in Reset as long as PWRT is active. The PWRT delay allows additional time for the VDD to rise to an acceptable level. The Power-up Timer is enabled by clearing the PWRTE bit in Configuration Words.

The Power-up Timer starts after the release of the POR and BOR.

For additional information, refer to Application Note AN607, *"Power-up Trouble Shooting"* (DS0000607).

### 8.13 Determining the Cause of a Reset

Upon any Reset, multiple bits in the STATUS and PCON0 registers are updated to indicate the cause of the Reset. Table 8-3 shows the Reset conditions of these registers.

| Condition                          | Program<br>Counter    | STATUS<br>Register <sup>(2,3)</sup> | PCON0<br>Register |

|------------------------------------|-----------------------|-------------------------------------|-------------------|

| Power-on Reset                     | 0                     | -110 0000                           | 0011 110x         |

| Brown-out Reset                    | 0                     | -110 0000                           | 0011 11u0         |

| MCLR Reset during normal operation | 0                     | -uuu uuuu                           | uuuu Ouuu         |

| MCLR Reset during Sleep            | 0                     | -10u uuuu                           | uuuu Ouuu         |

| WDT Time-out Reset                 | 0                     | -0uu uuuu                           | սսս0 սսսս         |

| WDT Wake-up from Sleep             | PC + 2                | -00u uuuu                           | uuuu uuuu         |

| WWDT Window Violation Reset        | 0                     | -uuu uuuu                           | uu0u uuuu         |

| Interrupt Wake-up from Sleep       | PC + 2 <sup>(1)</sup> | -10u 0uuu                           | uuuu uuuu         |

| RESET Instruction Executed         | 0                     | -uuu uuuu                           | uuuu u0uu         |

| Stack Overflow Reset (STVREN = 1)  | 0                     | -uuu uuuu                           | luuu uuuu         |

| Stack Underflow Reset (STVREN = 1) | 0                     | -uuu uuuu                           | uluu uuuu         |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and Global Interrupt Enable bit (GIE) is set the return address is pushed on the stack and PC is loaded with the corresponding interrupt vector (depending on source, high or low priority) after execution of PC + 2.

2: If a Status bit is not implemented, that bit will be read as '0'.

3: Status bits Z, C, DC are reset by POR/BOR (Register 10-2).

| U-0            | R/W <sup>(3)</sup> -q/q <sup>(1)</sup> | R/W <sup>(3)</sup> -q/q <sup>(1)</sup> | R/W <sup>(3)</sup> -q/q <sup>(1)</sup> | U-0                                                   | R/W <sup>(4)</sup> -q/q <sup>(2)</sup> | R/W <sup>(4)_</sup> q/q <sup>(2)</sup> | R/W <sup>(4)</sup> -q/q <sup>(2)</sup> |

|----------------|----------------------------------------|----------------------------------------|----------------------------------------|-------------------------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|

| —              |                                        | WDTCS<2:0>                             |                                        | - WINDOW<2:0>                                         |                                        |                                        |                                        |

| bit 7          |                                        |                                        |                                        |                                                       |                                        |                                        | bit 0                                  |

|                |                                        |                                        |                                        |                                                       |                                        |                                        |                                        |

| Legend:        |                                        |                                        |                                        |                                                       |                                        |                                        |                                        |

| R = Readable   | e bit                                  | W = Writable                           | e bit                                  | U = Unimplemented bit, read as '0'                    |                                        |                                        |                                        |

| u = Bit is und | hanged                                 | x = Bit is unk                         | nown                                   | -n/n = Value at POR and BOR/Value at all other Resets |                                        |                                        | er Resets                              |

q = Value depends on condition

### REGISTER 9-2: WDTCON1: WATCHDOG TIMER CONTROL REGISTER 1

| bit 7 | Unimplemented: Read as '0' |

|-------|----------------------------|

|       | Unimplemented. Read as 0   |

bit 6-4 WDTCS<2:0>: Watchdog Timer Clock Select bits

'0' = Bit is cleared

- 111 = Reserved

- •

'1' = Bit is set

- •

- 010 = Reserved

- 001 = MFINTOSC 31.25 kHz

- 000 = LFINTOSC 31 kHz

- bit 3 Unimplemented: Read as '0'

- bit 2-0 WINDOW<2:0>: Watchdog Timer Window Select bits

| window<2:0> | Window delay<br>Percent of time | Window opening<br>Percent of time |  |

|-------------|---------------------------------|-----------------------------------|--|

| 111         | N/A                             | 100                               |  |

| 110         | 12.5                            | 87.5                              |  |

| 101         | 25                              | 75                                |  |

| 100         | 37.5                            | 62.5                              |  |

| 011         | 50                              | 50                                |  |

| 010         | 62.5                            | 37.5                              |  |

| 001         | 75                              | 25                                |  |

| 000         | 87.5                            | 12.5                              |  |

- Note 1: If WDTCCS <2:0> in CONFIG3H = 111, the Reset value of WDTCS<2:0> is 000.

- 2: The Reset value of WINDOW<2:0> is determined by the value of WDTCWS<2:0> in the CONFIG3H register.

- **3:** If WDTCCS<2:0> in CONFIG3H  $\neq$  111, these bits are read-only.

- 4: If WDTCWS<2:0> in CONFIG3H  $\neq$  111, these bits are read-only.

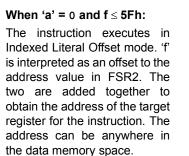

#### FIGURE 10-7: COMPARING ADDRESSING OPTIONS FOR BIT-ORIENTED AND BYTE-ORIENTED INSTRUCTIONS (EXTENDED INSTRUCTION SET ENABLED)

**EXAMPLE INSTRUCTION:** ADDWF, f, d, a (Opcode: 0010 01da ffff ffff)

#### When 'a' = 0 and $f \ge 60h$ :

The instruction executes in Direct Forced mode. 'f' is interpreted as a location in the Access RAM between 060h and 0FFh. This is the same as locations F60h to FFFh (Bank 15) of data memory.

Locations below 60h are not available in this addressing mode.

Note that in this mode, the correct syntax is now: ADDWF [k], d where 'k' is the same as 'f'.

#### When 'a' = 1 (all values of f):

The instruction executes in Direct mode (also known as Direct Long mode). 'f' is interpreted as a location in one of the 16 banks of the data memory space. The bank is designated by the Bank Select Register (BSR). The address can be in any implemented bank in the data memory space.

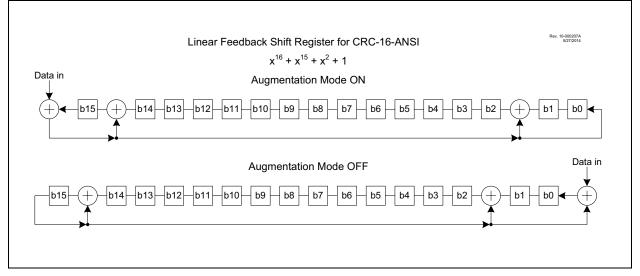

corresponding CRCXOR<15:0> bits with the value of

0x8004. The actual value is 0x8005 because the

hardware sets the LSb to 1. However, the LSb of the

CRCXORL register is unimplemented and always

reads as '0'. Refer to Example 13-1.

### 13.4 CRC Polynomial Implementation

Any polynomial can be used. The polynomial and accumulator sizes are determined by the PLEN<3:0> bits. For an n-bit accumulator, PLEN = n-1 and the corresponding polynomial is n+1 bits. Therefore, the accumulator can be any size up to 16 bits with a corresponding polynomial up to 17 bits. The MSb and LSb of the polynomial are always '1' which is forced by hardware. All polynomial bits between the MSb and LSb are specified by the CRCXOR registers. For example, when using CRC16-ANSI, the polynomial is defined as  $X^{16}+X^{15}+X^2+1$ . The  $X^{16}$  and  $X^0 = 1$  terms are the MSb and LSb controlled by hardware. The  $X^{15}$  and  $X^2$  terms are specified by setting the

### 13.5 CRC Data Sources

Data can be input to the CRC module in two ways:

- User data using the CRCDATA registers (CRCDATH and CRCDATL)

- Flash using the Program Memory Scanner

To set the number of bits of data, up to 16 bits, the DLEN bits of CRCCON1 must be set accordingly. Only data bits in CRCDATA registers up to DLEN will be used, other data bits in CRCDATA registers will be ignored.

Data is moved into the CRCSHIFT as an intermediate to calculate the check value located in the CRCACC registers.

The SHIFTM bit is used to determine the bit order of the data being shifted into the accumulator. If SHIFTM is not set, the data will be shifted in MSb first (Big Endian). The value of DLEN will determine the MSb. If SHIFTM bit is set, the data will be shifted into the accumulator in reversed order, LSb first (Little Endian).

The CRC module can be seeded with an initial value by setting the CRCACC<15:0> registers to the appropriate value before beginning the CRC.

#### 13.5.1 CRC FROM USER DATA

To use the CRC module on data input from the user, the user must write the data to the CRCDAT registers. The data from the CRCDAT registers will be latched into the shift registers on any write to the CRCDATL register.

#### 13.5.2 CRC FROM FLASH

To use the CRC module on data located in Flash memory, the user can initialize the Program Memory Scanner as defined in **Section 13.9, Program Memory Scan Configuration**.

© 2016-2017 Microchip Technology Inc.

#### 13.11.7 IN-CIRCUIT DEBUG (ICD) INTERACTION

The scanner freezes when an ICD halt occurs, and remains frozen until user-mode operation resumes. The debugger may inspect the SCANCON0 and SCANLADR registers to determine the state of the scan.

The ICD interaction with each operating mode is summarized in Table 13-4.

|                     |                                                                                                  | Scanner Operating Mode                                                                                                                                                                   |                                                                                                                                                                                                                                                           |

|---------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ICD Halt            | Peek                                                                                             | Concurrent<br>Triggered                                                                                                                                                                  | Burst                                                                                                                                                                                                                                                     |

| External<br>Halt    |                                                                                                  | If external halt is asserted during<br>a scan cycle, the instruction<br>(delayed by scan) may or may<br>not execute before ICD entry,<br>depending on external halt<br>timing.           | If external halt is asserted during<br>the BSF (SCANCON.GO), ICD<br>entry occurs, and the burst is<br>delayed until ICD exit.<br>Otherwise, the current NVM-<br>access cycle will complete, and<br>then the scanner will be<br>interrupted for ICD entry. |

|                     |                                                                                                  | If external halt is asserted during<br>the cycle immediately prior to the<br>scan cycle, both scan and<br>instruction execution happen<br>after the ICD exits.                           | If external halt is asserted during<br>the burst, the burst is suspended<br>and will resume with ICD exit.                                                                                                                                                |

| PC<br>Breakpoint    | If scanner would peek an<br>instruction that is not executed<br>(because of ICD entry), the peek | Scan cycle occurs before ICD<br>entry and instruction execution<br>happens after the ICD exits.                                                                                          | If PCPB (or single step) is on                                                                                                                                                                                                                            |

| Data<br>Breakpoint  | will occur after ICD exit, when the instruction executes.                                        | The instruction with the dataBP<br>executes and ICD entry occurs<br>immediately after. If scan is<br>requested during that cycle, the<br>scan cycle is postponed until the<br>ICD exits. | BSF (SCANCON, GO), the ICD is<br>entered before execution;<br>execution of the burst will occur<br>at ICD exit, and the burst will run<br>to completion.                                                                                                  |

| Single Step         |                                                                                                  | If a scan cycle is ready after the debug instruction is executed, the scan will read PFM and then the ICD is re-entered.                                                                 | Note that the burst can be interrupted by an external halt.                                                                                                                                                                                               |

| SWBP and<br>ICDINST |                                                                                                  | If scan would stall a SWBP, the scan cycle occurs and the ICD is entered.                                                                                                                | If SWBP replaces<br>BSF(SCANCON.GO), the ICD will<br>be entered; instruction execution<br>will occur at ICD exit (from<br>ICDINSTR register), and the<br>burst will run to completion.                                                                    |

| <b>TABLE 13-4</b> : | ICD AND SCANNER INTERACTIONS |

|---------------------|------------------------------|

| IADLL IJ-4.         |                              |

### 13.11.8 PERIPHERAL MODULE DISABLE

Both the CRC and scanner module can be disabled individually by setting the CRCMD and SCANMD bits of the PMD0 register (Register 7-1). The SCANMD can be used to enable or disable to the scanner module only if the SCANE bit of Configuration Word 4 is set. If the SCANE bit is cleared, then the scanner module is not available for use and the SCANMD bit is ignored.

| R/W-0/u       | R/W-0/u                                                | R/W-0/u                                                                                                                                                                                                                                                                 | R/W-0/u                       | R/W-0/u             | R-x              | U-0             | U-0   |

|---------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|---------------------|------------------|-----------------|-------|

| GE            | GPOL                                                   | GTM                                                                                                                                                                                                                                                                     | GSPM                          | GGO/DONE            | GVAL             | _               | _     |

| bit 7         |                                                        |                                                                                                                                                                                                                                                                         |                               | 1                   |                  |                 | bit 0 |

| Legend:       |                                                        |                                                                                                                                                                                                                                                                         |                               |                     |                  |                 |       |

| R = Readable  | e bit                                                  | W = Writable                                                                                                                                                                                                                                                            | bit                           | U = Unimplemer      | nted bit, read a | as '0'          |       |

| -n = Value at | POR                                                    | '1' = Bit is se                                                                                                                                                                                                                                                         | t                             | '0' = Bit is cleare | ed               | x = Bit is unkr | nown  |

| bit 7         | If TMRxON =<br>1 = Timerx<br>0 = Timerx<br>If TMRxON = | counting is co<br>is always cou                                                                                                                                                                                                                                         | ontrolled by th               | e Timerx gate fun   | ction            |                 |       |

| bit 6         | <b>GPOL:</b> Time                                      | <b>GPOL:</b> Timerx Gate Polarity bit<br>1 = Timerx gate is active-high (Timerx counts when gate is high)                                                                                                                                                               |                               |                     |                  |                 |       |

| bit 5         | 1 = Timerx<br>0 = Timerx                               | <ul> <li>TM: Timerx Gate Toggle Mode bit</li> <li>Timerx Gate Toggle mode is enabled</li> <li>Timerx Gate Toggle mode is disabled and Toggle flip-flop is cleared merx Gate Flip Flop Toggles on every rising edge</li> </ul>                                           |                               |                     |                  |                 |       |

| bit 4         | 1 = Timerx                                             | <ul> <li>SPM: Timerx Gate Single Pulse Mode bit</li> <li>Timerx Gate Single Pulse mode is enabled and is controlling Timerx gate)</li> <li>Timerx Gate Single Pulse mode is disabled</li> </ul>                                                                         |                               |                     |                  |                 |       |

| bit 3         | GGO/DONE<br>1 = Timerx<br>0 = Timerx                   | <b>DONE:</b> Timerx Gate Single Pulse Acquisition Status bit<br>Timerx Gate Single Pulse Acquisition is ready, waiting for an edge<br>Timerx Gate Single Pulse Acquisition has completed or has not been started.<br>t is automatically cleared when TxGSPM is cleared. |                               |                     |                  |                 |       |

| bit 2         | GVAL: Time<br>Indicates the                            | rx Gate Currer                                                                                                                                                                                                                                                          | nt State bit<br>of the Timerx | gate that could be  |                  | MRxH:TMRxL      |       |

| bit 1-0       | Unimpleme                                              | nted: Read as                                                                                                                                                                                                                                                           | '0'                           |                     |                  |                 |       |

#### REGISTER 19-2: TxGCON: TIMERx GATE CONTROL REGISTER

#### 20.5.6 EDGE-TRIGGERED ONE-SHOT MODE

The Edge-Triggered One-Shot modes start the timer on an edge from the external signal input, after the ON bit is set, and clear the ON bit when the timer matches the PRx period value. The following edges will start the timer:

- Rising edge (MODE<4:0> = 01001)

- Falling edge (MODE<4:0> = 01010)

- Rising or Falling edge (MODE<4:0> = 01011)

If the timer is halted by clearing the ON bit then another TMRx\_ers edge is required after the ON bit is set to resume counting. Figure 20-9 illustrates operation in the rising edge One-Shot mode.

When Edge-Triggered One-Shot mode is used in conjunction with the CCP then the edge-trigger will activate the PWM drive and the PWM drive will deactivate when the timer matches the CCPRx pulse width value and stay deactivated when the timer halts at the PRx period count match.

#### FIGURE 20-9: EDGE-TRIGGERED ONE-SHOT MODE TIMING DIAGRAM (MODE = 01001)

| MODE                         | 0b01001                                                                                                                                                                                                                     |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TMRx_clk                     |                                                                                                                                                                                                                             |

| PRx                          | 5                                                                                                                                                                                                                           |

| Instruction <sup>(1)</sup> — | BSF BSF                                                                                                                                                                                                                     |

| ON                           |                                                                                                                                                                                                                             |

| TMRx_ers                     |                                                                                                                                                                                                                             |

| TMRx                         | $0 \qquad \left< 1 \right> \left< 2 \right> \left< 3 \right> \left< 4 \right> \left< 5 \right> \qquad 0 \qquad \left< 1 \right> \left< 2 \qquad 2 $ |

| CCP_pset                     |                                                                                                                                                                                                                             |

| TMRx_postscaled              |                                                                                                                                                                                                                             |

| PWM Duty<br>Cycle            | 3                                                                                                                                                                                                                           |

| PWM Output                   |                                                                                                                                                                                                                             |

#### 20.5.7 EDGE-TRIGGERED HARDWARE LIMIT ONE-SHOT MODE

In Edge-Triggered Hardware Limit One-Shot modes the timer starts on the first external signal edge after the ON bit is set and resets on all subsequent edges. Only the first edge after the ON bit is set is needed to start the timer. The counter will resume counting automatically two clocks after all subsequent external Reset edges. Edge triggers are as follows:

- Rising edge start and Reset (MODE<4:0> = 01100)

- Falling edge start and Reset (MODE<4:0> = 01101)

The timer resets and clears the ON bit when the timer value matches the PRx period value. External signal edges will have no effect until after software sets the ON bit. Figure 20-10 illustrates the rising edge hardware limit one-shot operation.

When this mode is used in conjunction with the CCP then the first starting edge trigger, and all subsequent Reset edges, will activate the PWM drive. The PWM drive will deactivate when the timer matches the CCPRx pulse-width value and stay deactivated until the timer halts at the PRx period match unless an external signal edge resets the timer before the match occurs.

#### 22.1.5 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is ten bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 22-4.

#### EQUATION 22-4: PWM RESOLUTION

Resolution =  $\frac{\log[4(PR2 + 1)]}{\log(2)}$  bits

**Note:** If the pulse-width value is greater than the period the assigned PWM pin(s) will remain unchanged.

| <b>TABLE 22-1</b> : | EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz) |

|---------------------|---------------------------------------------------------|

|---------------------|---------------------------------------------------------|

| PWM Frequency             | 0.31 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale            | 64       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

#### TABLE 22-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 0.31 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale            | 64       | 4        | 1         | 1         | 1          | 1         |

| PR2 Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

#### 22.1.6 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the PWMx pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

#### 22.1.7 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency (Fosc). Any changes in the system clock frequency will result in changes to the PWM frequency. Refer to Section 4.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for additional details.

#### 22.1.8 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the PWM registers to their Reset states.

#### 24.7 Rising Edge and Reverse Dead Band

In Half-Bridge mode, the rising edge dead band delays the turn-on of the CWG1A output after the rising edge of the CWG data input. In Full-Bridge mode, the reverse dead-band delay is only inserted when changing directions from Forward mode to Reverse mode, and only the modulated output CWG1B is affected.

The CWG1DBR register determines the duration of the dead-band interval on the rising edge of the input source signal. This duration is from 0 to 64 periods of the CWG clock.

Dead band is always initiated on the edge of the input source signal. A count of zero indicates that no dead band is present.

If the input source signal reverses polarity before the dead-band count is completed, then no signal will be seen on the respective output.

The CWG1DBR register value is double-buffered. When EN = 0 (Register 24-1), the buffer is loaded when CWG1DBR is written. If EN = 1, then the buffer will be loaded at the rising edge following the first falling edge of the data input, after the LD bit (Register 24-1) is set. Refer to Figure 24-12 for an example.

## 24.8 Falling Edge and Forward Dead Band

In Half-Bridge mode, the falling edge dead band delays the turn-on of the CWG1B output at the falling edge of the CWG data input. In Full-Bridge mode, the forward dead-band delay is only inserted when changing directions from Reverse mode to Forward mode, and only the modulated output CWG1D is affected.

The CWG1DBF register determines the duration of the dead-band interval on the falling edge of the input source signal. This duration is from zero to 64 periods of CWG clock.

Dead-band delay is always initiated on the edge of the input source signal. A count of zero indicates that no dead band is present.

If the input source signal reverses polarity before the dead-band count is completed, then no signal will be seen on the respective output.

The CWG1DBF register value is double-buffered. When EN = 0 (Register 24-1), the buffer is loaded when CWG1DBF is written. If EN = 1, then the buffer will be loaded at the rising edge following the first falling edge of the data input after the LD (Register 24-1) is set. Refer to Figure 24-13 for an example.

#### 25.7.9 COUNTER MODE

This mode increments the timer on each pulse of the SMTx\_signal input. This mode is asynchronous to the SMT clock and uses the SMTx\_signal as a time source. The SMTxCPW register will be updated with the current SMTxTMR value on the falling edge of the SMTxWIN input. See Figure 25-18.

#### 27.8.9 ACKNOWLEDGE SEQUENCE

The ninth SCL pulse for any transferred byte in  $I^2C$  is dedicated as an Acknowledge. It allows receiving devices to respond back to the transmitter by pulling the SDA line low. The transmitter must release control of the line during this time to shift in the response. The Acknowledge (ACK) is an active-low signal, pulling the SDA line low indicates to the transmitter that the device has received the transmitted data and is ready to receive more.

The result of an  $\overline{ACK}$  is placed in the ACKSTAT bit of the SSPxCON2 register.

Slave software, when the AHEN and DHEN bits are set, allow the user to set the ACK value sent back to the transmitter. The ACKDT bit of the SSPxCON2 register is set/cleared to determine the response.

Slave hardware will generate an ACK response if the AHEN and DHEN bits of the SSPxCON3 register are clear.

There are certain conditions where an ACK will not be sent by the slave. If the BF bit of the SSPxSTAT register or the SSPOV bit of the SSPxCON1 register are set when a byte is received.

When the module is addressed, after the eighth falling edge of SCL on the bus, the ACKTIM bit of the SSPxCON3 register is set. The ACKTIM bit indicates the acknowledge time of the active bus. The ACKTIM Status bit is only active when the AHEN bit or DHEN bit is enabled.

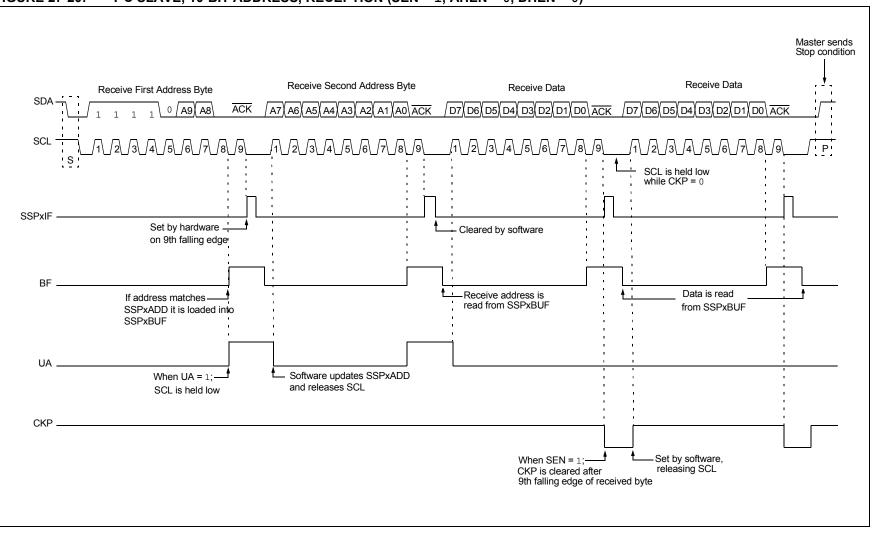

## 27.9 I<sup>2</sup>C Slave Mode Operation

The MSSP Slave mode operates in one of four modes selected by the SSPM bits of the SSPxCON1 register. The modes can be divided into 7-bit and 10-bit Addressing mode. 10-bit Addressing modes operate the same as 7-bit with some additional overhead for handling the larger addresses.

Modes with Start and Stop bit interrupts operate the same as the other modes with SSPxIF additionally getting set upon detection of a Start, Restart, or Stop condition.

#### 27.9.1 SLAVE MODE ADDRESSES

The SSPxADD register (Register 27-5) contains the Slave mode address. The first byte received after a Start or Restart condition is compared against the value stored in this register. If the byte matches, the value is loaded into the SSPxBUF register and an interrupt is generated. If the value does not match, the module goes idle and no indication is given to the software that anything happened.

The SSP Mask register affects the address matching process. See **Section 27.9.9** "**SSP Mask Register**" for more information.

#### 27.9.1.1 I<sup>2</sup>C Slave 7-bit Addressing Mode

In 7-bit Addressing mode, the LSb of the received data byte is ignored when determining if there is an address match.

#### 27.9.1.2 I<sup>2</sup>C Slave 10-bit Addressing Mode

In 10-bit Addressing mode, the first received byte is compared to the binary value of '1 1 1 1 0 A9 A8 0'. A9 and A8 are the two MSb's of the 10-bit address and stored in bits 2 and 1 of the SSPxADD register.

After the acknowledge of the high byte the UA bit is set and SCL is held low until the user updates SSPxADD with the low address. The low address byte is clocked in and all eight bits are compared to the low address value in SSPxADD. Even if there is not an address match; SSPxIF and UA are set, and SCL is held low until SSPxADD is updated to receive a high byte again. When SSPxADD is updated the UA bit is cleared. This ensures the module is ready to receive the high address byte on the next communication.

A high and low address match as a write request is required at the start of all 10-bit addressing communication. A transmission can be initiated by issuing a Restart once the slave is addressed, and clocking in the high address with the R/W bit set. The slave hardware will then acknowledge the read request and prepare to clock out data. This is only valid for a slave after it has received a complete high and low address byte match.

#### 27.9.2 SLAVE RECEPTION

When the R/W bit of a matching received address byte is clear, the R/W bit of the SSPxSTAT register is cleared. The received address is loaded into the SSPxBUF register and acknowledged.

When the overflow condition exists for a received address, then not Acknowledge is given. An overflow condition is defined as either bit BF of the SSPxSTAT register is set, or bit SSPOV of the SSPxCON1 register is set. The BOEN bit of the SSPxCON3 register modifies this operation. For more information see Register 27-3.

An MSSP interrupt is generated for each transferred data byte. Flag bit, SSPxIF, must be cleared by software.

When the SEN bit of the SSPxCON2 register is set, SCL will be held low (clock stretch) following each received byte. The clock must be released by setting the CKP bit of the SSPxCON1 register, except sometimes in 10-bit mode. See **Section 27.9.6.2 "10-bit Addressing Mode**" for more detail.

© 2016-2017 Microchip Technology Inc.

### FIGURE 27-20: I<sup>2</sup>C SLAVE, 10-BIT ADDRESS, RECEPTION (SEN = 1, AHEN = 0, DHEN = 0)

PIC18(L)F65/66K40

#### 27.10.7 I<sup>2</sup>C Master Mode Reception

Master mode reception (Figure 27-29) is enabled by programming the Receive Enable bit, RCEN bit of the SSP1CON2 register.

| Note: | The MSSP module must be in an Idle      |

|-------|-----------------------------------------|

|       | state before the RCEN bit is set or the |

|       | RCEN bit will be disregarded.           |

The Baud Rate Generator begins counting and on each rollover, the state of the SCL pin changes (high-to-low/low-to-high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPxBUF, the BF flag bit is set, the SSPxIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCL low. The MSSP is now in Idle state awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable, ACKEN bit of the SSPxCON2 register.

#### 27.10.7.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPxBUF from SSPSR. It is cleared when the SSPxBUF register is read.

#### 27.10.7.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when eight bits are received into the SSPSR and the BF flag bit is already set from a previous reception.

#### 27.10.7.3 WCOL Status Flag

If the user writes the SSPxBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

- 27.10.7.4 Typical Receive Sequence:

- 1. The user generates a Start condition by setting the SEN bit of the SSPxCON2 register.

- 2. SSPxIF is set by hardware on completion of the Start.

- 3. SSPxIF is cleared by software.

- 4. User writes SSPxBUF with the slave address to transmit and the R/W bit set.

- 5. Address is shifted out the SDA pin until all eight bits are transmitted. Transmission begins as soon as SSPxBUF is written to.

- 6. The MSSP module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- 7. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPxIF bit.

- 8. User sets the RCEN bit of the SSPxCON2 register and the master clocks in a byte from the slave.

- 9. After the eighth falling edge of SCL, SSPxIF and BF are set.

- 10. Master clears SSPxIF and reads the received byte from SSPUF, clears BF.

- 11. Master sets the ACK value sent to slave in the ACKDT bit of the SSPxCON2 register and initiates the ACK by setting the ACKEN bit.

- 12. Master's ACK is clocked out to the slave and SSPxIF is set.

- 13. User clears SSPxIF.

- 14. Steps 8-13 are repeated for each received byte from the slave.

- 15. Master sends a not ACK or Stop to end communication.

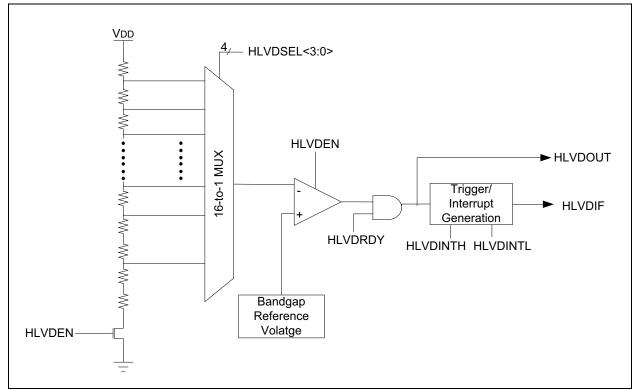

## 34.0 HIGH/LOW-VOLTAGE DETECT (HLVD)

The PIC18(L)F6xK40 of devices has a High/Low-Voltage Detect module (HLVD). This is a programmable circuit that sets both a device voltage trip point and the direction of change from that point (positive going, negative going or both). If the device experiences an excursion past the trip point in that direction, an interrupt flag is set. If the interrupt is enabled, the program execution branches to the interrupt vector address and the software responds to the interrupt.

Complete control of the HLVD module is provided through the HLVDCON0 and HLVDCON1 register. This allows the circuitry to be "turned off" by the user under software control, which minimizes the current consumption for the device.

The module's block diagram is shown in Figure 34-1.

Since the HLVD can be software enabled through the HLVDEN bit, setting and clearing the enable bit does not produce a false HLVD event glitch. Each time the HLVD module is enabled, the circuitry requires some time to stabilize. The RDY bit (HLVDCON0<4>) is a read-only bit used to indicate when the band gap reference voltages are stable.

The module can only generate an interrupt after the module is turned ON and the band gap reference voltages are ready.

The HLVDINTH and HLVDINTL bits determine the overall operation of the module. When HLVDINTH is set, the module monitors for rises in VDD above the trip point set by the HLVDCON1 register. When HLVDINTL is set, the module monitors for drops in VDD below the trip point set by the HLVDCON1 register. When both the HLVDINTH and HLVDINTL bits are set, any changes above or below the trip point set by the HLVDCON1 register can be monitored.

The OUT bit can be read to determine if the voltage is greater than or less than the voltage level selected by the HLVDCON1 register.

## 34.1 Operation

When the HLVD module is enabled, a comparator uses an internally generated voltage reference as the set point. The set point is compared with the trip point, where each node in the resistor divider represents a trip point voltage. The "trip point" voltage is the voltage level at which the device detects a high or low-voltage event, depending on the configuration of the module.

When the supply voltage is equal to the trip point, the voltage tapped off of the resistor array is equal to the internal reference voltage generated by the voltage reference module. The comparator then generates an interrupt signal by setting the HLVDIF bit.

The trip point voltage is software programmable to any of 16 values. The trip point is selected by programming the HLVDSEL<3:0> bits (HLVDCON1<3:0>).

FIGURE 34-1: HLVD MODULE BLOCK DIAGRAM

| TABLE 36-2: | INSTRUCTION SET ( | (CONTINUED) |

|-------------|-------------------|-------------|

|-------------|-------------------|-------------|

| Mnemonic, |         | Description                     | Quality | 16-Bit Instruction Word |      |      | Status   |                 |  |

|-----------|---------|---------------------------------|---------|-------------------------|------|------|----------|-----------------|--|

| Opera     | nds     | Description                     | Cycles  | MSb                     | LSb  |      | Affected | Notes           |  |

| LITERAL ( | OPERAT  | IONS                            |         |                         |      |      |          |                 |  |

| ADDLW     | k       | Add literal and WREG            | 1       | 0000                    | 1111 | kkkk | kkkk     | C, DC, Z, OV, N |  |

| ANDLW     | k       | AND literal with WREG           | 1       | 0000                    | 1011 | kkkk | kkkk     | Z, N            |  |

| IORLW     | k       | Inclusive OR literal with WREG  | 1       | 0000                    | 1001 | kkkk | kkkk     | Z, N            |  |

| LFSR      | f, k    | Move literal (12-bit) 2nd word  | 2       | 1110                    | 1110 | 00ff | kkkk     | None            |  |

|           |         | to FSR(f) 1st word              |         | 1111                    | 0000 | kkkk | kkkk     |                 |  |

| MOVLB     | k       | Move literal to BSR<3:0>        | 1       | 0000                    | 0001 | 0000 | kkkk     | None            |  |

| MOVLW     | k       | Move literal to WREG            | 1       | 0000                    | 1110 | kkkk | kkkk     | None            |  |

| MULLW     | k       | Multiply literal with WREG      | 1       | 0000                    | 1101 | kkkk | kkkk     | None            |  |

| RETLW     | k       | Return with literal in WREG     | 2       | 0000                    | 1100 | kkkk | kkkk     | None            |  |

| SUBLW     | k       | Subtract WREG from literal      | 1       | 0000                    | 1000 | kkkk | kkkk     | C, DC, Z, OV, N |  |

| XORLW     | k       | Exclusive OR literal with WREG  | 1       | 0000                    | 1010 | kkkk | kkkk     | Z, N            |  |

| DATA MEN  | /IORY ↔ | PROGRAM MEMORY OPERATION        | NS      |                         |      |      |          |                 |  |

| TBLRD*    |         | Table Read                      | 2       | 0000                    | 0000 | 0000 | 1000     | None            |  |

| TBLRD*+   |         | Table Read with post-increment  |         | 0000                    | 0000 | 0000 | 1001     | None            |  |

| TBLRD*-   |         | Table Read with post-decrement  |         | 0000                    | 0000 | 0000 | 1010     | None            |  |

| TBLRD+*   |         | Table Read with pre-increment   |         | 0000                    | 0000 | 0000 | 1011     | None            |  |

| TBLWT*    |         | Table Write                     | 2       | 0000                    | 0000 | 0000 | 1100     | None            |  |

| TBLWT*+   |         | Table Write with post-increment |         | 0000                    | 0000 | 0000 | 1101     | None            |  |

| TBLWT*-   |         | Table Write with post-decrement |         | 0000                    | 0000 | 0000 | 1110     | None            |  |

| TBLWT+*   |         | Table Write with pre-increment  |         | 0000                    | 0000 | 0000 | 1111     | None            |  |

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, 'd' = 1), the prescaler will be cleared if assigned.

**3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

# PIC18(L)F65/66K40

| BNC          | ;                                                                            | Branch if Not Carry                                                                                                                                                                                                                                                                   |                                            | BNN             |                     | Branch if                                                               | Branch if Not Negative                                                              |                                                          |                 |  |  |

|--------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-----------------|---------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------|-----------------|--|--|

| Synta        | ax:                                                                          | BNC n                                                                                                                                                                                                                                                                                 |                                            |                 | Syntax:             |                                                                         | BNN n                                                                               |                                                          |                 |  |  |

| Oper         | ands:                                                                        | -128 ≤ n ≤ 1                                                                                                                                                                                                                                                                          | 127                                        |                 | Operands            | S:                                                                      | $-128 \le n \le 127$                                                                |                                                          |                 |  |  |

| Oper         | ation:                                                                       | if CARRY b<br>(PC) + 2 + 2                                                                                                                                                                                                                                                            |                                            |                 | Operation           | Operation:                                                              |                                                                                     | if NEGATIVE bit is '0'<br>(PC) + 2 + 2n $\rightarrow$ PC |                 |  |  |

| Statu        | s Affected:                                                                  | None                                                                                                                                                                                                                                                                                  |                                            |                 | Status Af           | Status Affected:                                                        |                                                                                     |                                                          |                 |  |  |

| Enco         | ding:                                                                        | 1110                                                                                                                                                                                                                                                                                  | 0011 nni                                   | nn nnnn         | Encoding            | Encoding:                                                               |                                                                                     | 0111 nn                                                  | nn nnnn         |  |  |

| Desc         | ription:                                                                     | If the CARRY bit is '0', then the program<br>will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>2-cycle instruction. |                                            | Descriptio      | on:                 | program wi<br>The 2's con<br>added to the<br>incremente<br>instruction, | nplement nun<br>e PC. Since th<br>d to fetch the<br>the new addr<br>n. This instruc | nber '2n' is<br>ne PC will have<br>next                  |                 |  |  |

| Word         | s:                                                                           | 1                                                                                                                                                                                                                                                                                     |                                            |                 | Words:              |                                                                         | 1                                                                                   |                                                          |                 |  |  |

| Cycle        | es:                                                                          | 1(2)                                                                                                                                                                                                                                                                                  |                                            |                 | Cycles:             |                                                                         | 1(2)                                                                                |                                                          |                 |  |  |

| Q C<br>If Ju | ycle Activity:<br>mp:                                                        |                                                                                                                                                                                                                                                                                       |                                            |                 | Q Cycle<br>If Jump: | Activity:                                                               |                                                                                     |                                                          |                 |  |  |

|              | Q1                                                                           | Q2                                                                                                                                                                                                                                                                                    | Q3                                         | Q4              |                     | Q1                                                                      | Q2                                                                                  | Q3                                                       | Q4              |  |  |

|              | Decode                                                                       | Read literal<br>'n'                                                                                                                                                                                                                                                                   | Process<br>Data                            | Write to PC     | C                   | Decode                                                                  | Read literal<br>'n'                                                                 | Process<br>Data                                          | Write to PC     |  |  |

|              | No<br>operation                                                              | No<br>operation                                                                                                                                                                                                                                                                       | No<br>operation                            | No<br>operation | or                  | No<br>peration                                                          | No<br>operation                                                                     | No<br>operation                                          | No<br>operation |  |  |

| lf No        | Jump:                                                                        |                                                                                                                                                                                                                                                                                       |                                            |                 | If No Jur           | np:                                                                     |                                                                                     |                                                          |                 |  |  |

|              | Q1                                                                           | Q2                                                                                                                                                                                                                                                                                    | Q3                                         | Q4              |                     | Q1                                                                      | Q2                                                                                  | Q3                                                       | Q4              |  |  |

|              | Decode                                                                       | Read literal<br>'n'                                                                                                                                                                                                                                                                   | Process<br>Data                            | No<br>operation | C                   | Decode                                                                  | Read literal<br>'n'                                                                 | Process<br>Data                                          | No<br>operation |  |  |

| Exam         | <u>iple</u> :                                                                | HERE                                                                                                                                                                                                                                                                                  | BNC Jump                                   |                 | Example:            |                                                                         | HERE                                                                                | BNN Jum <u>r</u>                                         | 0               |  |  |

|              | Before Instruc<br>PC<br>After Instructio<br>If CARR'<br>PC<br>If CARR'<br>PC | = adv<br>on<br>Y = 0;<br>= adv<br>Y = 1;                                                                                                                                                                                                                                              | dress (HERE<br>dress (Jump)<br>dress (HERE |                 |                     | ore Instruct<br>PC<br>r Instruction<br>If NEGAT<br>PC<br>If NEGAT<br>PC | = ad<br>on<br>FIVE = 0;<br>= ad<br>FIVE = 1;                                        | dress (HERE<br>dress (Jump<br>dress (HERE                | )               |  |  |

# PIC18(L)F65/66K40

| TBLWT                                                  | Table Wi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | rite                                |           |                                                       |  |  |  |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----------|-------------------------------------------------------|--|--|--|

| Syntax:                                                | TBLWT (*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ; *+; *-; +*                        | ·)        |                                                       |  |  |  |

| Operands:                                              | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                     |           |                                                       |  |  |  |

| Operation:                                             | if TBLWT*,<br>(TABLAT) $\rightarrow$ Holding Register;<br>TBLPTR – No Change;<br>if TBLWT*+,<br>(TABLAT) $\rightarrow$ Holding Register;<br>(TBLPTR) + 1 $\rightarrow$ TBLPTR;<br>if TBLWT*-,<br>(TABLAT) $\rightarrow$ Holding Register;<br>(TBLPTR) – 1 $\rightarrow$ TBLPTR;<br>if TBLWT+*,<br>(TBLPTR) + 1 $\rightarrow$ TBLPTR;<br>(TABLAT) $\rightarrow$ Holding Register;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                     |           |                                                       |  |  |  |

| Status Affected:                                       | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ·                                   | 5 0       |                                                       |  |  |  |

| Encoding:                                              | 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0000                                | 0000      | 11nn<br>nn=0 *<br>=1 *+<br>=2 *-<br>=3 +*             |  |  |  |

| Description:<br>Words:<br>Cycles:<br>Q Cycle Activity: | =3 +*         This instruction uses the three LSBs of<br>TBLPTR to determine which of the eight<br>holding registers the TABLAT is written to.<br>The holding registers are used to program<br>the contents of Program Memory (P.M.).<br>(Refer to Section 11.1 "Program Flash<br>Memory" for additional details on pro-<br>gramming Flash memory.)<br>The TBLPTR (a 21-bit pointer) points to<br>each byte in the program memory.<br>TBLPTR has a 2-MByte address range.<br>The LSb of the TBLPTR selects which<br>byte of the program memory location to<br>access.         TBLPTR[0] = 0:       Least Significant<br>Byte of Program<br>Memory Word         TBLPTR[0] = 1:       Most Significant<br>Byte of Program<br>Memory Word         The TBLWT instruction can modify the<br>value of TBLPTR as follows:         • no change         • post-increment         • post-decrement         1 |                                     |           |                                                       |  |  |  |

| a cyole Autivity.                                      | Q1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Q2                                  | Q3        | Q4                                                    |  |  |  |