Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 64MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 60                                                                           |

| Program Memory Size        | 32KB (16K x 16)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 1K x 8                                                                       |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 45x10b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 64-VFQFN Exposed Pad                                                         |

| Supplier Device Package    | 64-VQFN (9x9)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf65k40t-i-mr |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| IADLE              | 1.               | 04-FIN F | ALLUCAT |            |                                            | 10(L)F0A    | R40) (CO              |     | (עבי |                           |           |                                          |                       |                                              |       |

|--------------------|------------------|----------|---------|------------|--------------------------------------------|-------------|-----------------------|-----|------|---------------------------|-----------|------------------------------------------|-----------------------|----------------------------------------------|-------|

| I/O <sup>(2)</sup> | 64-Pin TQFP, QFN | A/D      | DAC     | Comparator | Timers                                     | CCP and PWM | CWG                   | ZCD | SMT  | Clock Reference<br>(CLKR) | Interrupt | EUSART                                   | WSQ                   | MSSP                                         | Basic |

| RC1                | 29               | —        | -       | -          | T6IN <sup>(1)</sup>                        |             | -                     | -   |      | -                         | IOCC1     | RX4 <sup>(1)</sup><br>DT4 <sup>(1)</sup> | _                     |                                              | SOSCI |

| RC2                | 33               | _        | _       | _          | _                                          | _           | CWG1IN <sup>(1)</sup> | _   | _    | _                         | IOCC2     | —                                        | _                     | _                                            | _     |

| RC3                | 34               | _        | _       | _          | _                                          | —           | -                     | —   | —    | _                         | IOCC3     | _                                        | —                     | SCL1 <sup>(3,4)</sup><br>SCK1 <sup>(1)</sup> | _     |

| RC4                | 35               | _        | _       | _          | _                                          | —           | -                     | —   | —    | _                         | IOCC4     | _                                        | —                     | SDA1 <sup>(3,4)</sup><br>SDI1 <sup>(1)</sup> | _     |

| RC5                | 36               | _        | _       | _          | _                                          | _           | _                     | _   | —    | _                         | IOCC5     | —                                        | _                     | _                                            | _     |

| RC6                | 31               | _        | _       | _          | _                                          | _           | _                     | _   | _    | _                         | IOCC6     | CK1 <sup>(3)</sup>                       | _                     | _                                            | _     |

| RC7                | 32               | _        | _       | _          | _                                          | —           | -                     | —   | —    | _                         | IOCC7     | RX1 <sup>(1)</sup><br>DT1 <sup>(3)</sup> | —                     | _                                            | _     |

| RD0                | 58               | AND0     | _       | _          | _                                          | _           | _                     | _   | _    | _                         | _         | —                                        | _                     | _                                            | _     |

| RD1                | 55               | AND1     | _       | _          | T5CKI <sup>(1)</sup><br>T7G <sup>(1)</sup> | _           | -                     | —   | —    | _                         | -         | _                                        | _                     | _                                            | _     |

| RD2                | 54               | AND2     | _       | _          | —                                          | _           | _                     | _   | —    | _                         | _         | _                                        | _                     | _                                            | _     |

| RD3                | 53               | AND3     | _       | _          | _                                          | _           | _                     | _   | —    | _                         | _         | —                                        | MDCARL <sup>(1)</sup> |                                              | _     |

| RD4                | 52               | AND4     | _       | _          | _                                          | _           | _                     | _   | _    | _                         | _         | _                                        | MDCARH <sup>(1)</sup> | _                                            |       |

| RD5                | 51               | AND5     | _       | _          | —                                          | —           | -                     | _   | _    | —                         | _         | _                                        | MDSRC <sup>(1)</sup>  | SDA2 <sup>(3,4)</sup><br>SDI2 <sup>(1)</sup> | —     |

| RD6                | 50               | AND6     | _       | —          | —                                          | —           | -                     | _   | _    | —                         | _         | _                                        | —                     | SCL2 <sup>(3,4)</sup><br>SCK2 <sup>(1)</sup> |       |

| RD7                | 49               | AND7     | _       | _          | _                                          | _           | _                     | _   | —    | _                         | _         | _                                        | —                     | SS2 <sup>(1)</sup>                           | _     |

| RE0                | 2                | ANE0     | —       | _          | —                                          | _           | _                     | _   | —    | —                         | IOCE0     | CK3 <sup>(3)</sup>                       | _                     | _                                            | _     |

| RE1                | 1                | ANE1     | —       | —          | —                                          | —           | —                     | _   | _    | —                         | IOCE1     | RX3 <sup>(1)</sup><br>DT3 <sup>(3)</sup> | _                     |                                              | -     |

| RE2                | 64               | ANE2     | _       | _          | _                                          | _           | _                     | _   | —    | _                         | IOCE2     | CK5 <sup>(3)</sup>                       | _                     | _                                            | _     |

| RE3                | 63               | ANE3     | _       | —          | -                                          | _           | -                     | -   | _    | -                         | IOCE3     | RX5 <sup>(1)</sup><br>DT5 <sup>(3)</sup> | —                     | _                                            | _     |

#### TABLE 1: 64-PIN ALLOCATION TABLE (PIC18(L)F6XK40) (CONTINUED)

Note 1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to Table 17-1 for details on which PORT pins may be used for this signal.

2: All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options as described in Register 17-2

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

CCP2<sup>(1)</sup>

T4IN<sup>(1)</sup>

4: These pins are configured for I<sup>2</sup>C<sup>™</sup> logic levels; The SCLx/SDAx signals may be assigned to any of these pins. PPS assignments to the other pins (e.g., RB1) will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

\_

IOCE4

RE4

ANE4

62

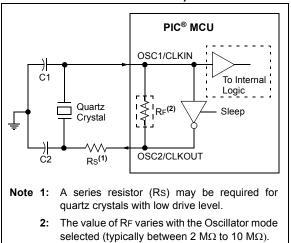

#### FIGURE 4-3: QUARTZ CRYSTAL OPERATION (LP, XT OR HS MODE)

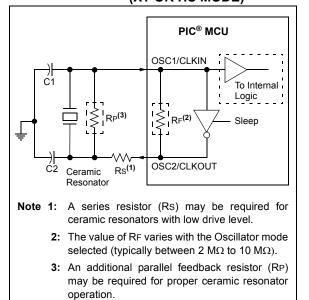

#### FIGURE 4-4: CERAMIC RESONATOR OPERATION (XT OR HS MODE)

# 4.3.1.3 Oscillator Start-up Timer (OST)

If the oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) counts 1024 oscillations from OSC1. This occurs following a Power-on Reset (POR), or a wake-up from Sleep. The OST ensures that the oscillator circuit, using a quartz crystal resonator or ceramic resonator, has started and is providing a stable system clock to the oscillator module.

# 4.3.1.4 4x PLL

The oscillator module contains a 4x PLL that can be used with the external clock sources to provide a system clock source. The input frequency for the PLL must fall within specifications. See the PLL Clock Timing Specifications in Table 37-9.

The PLL can be enabled for use by one of two methods:

- 1. Program the RSTOSC bits in the Configuration Word 1 to 010 (enable EXTOSC with 4x PLL).

- 2. Write the NOSC bits in the OSCCON1 register to 010 (enable EXTOSC with 4x PLL).

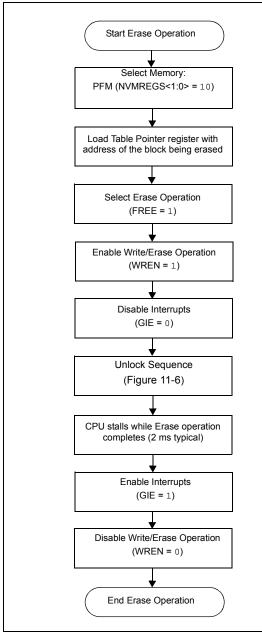

#### FIGURE 11-7: PFM ROW ERASE FLOWCHART

## 11.1.6 WRITING TO PROGRAM FLASH MEMORY

The programming write block size is described in Table 11-3. Word or byte programming is not supported. Table writes are used internally to load the holding registers needed to program the Flash memory. There are only as many holding registers as there are bytes in a write block. Refer to Table 11-3 for write latch size.

Since the table latch (TABLAT) is only a single byte, the TBLWT instruction needs to be executed multiple times for each programming operation. The write protection state is ignored for this operation. All of the table write operations will essentially be short writes because only the holding registers are written. NVMIF is not affected while writing to the holding registers.

After all the holding registers have been written, the programming operation of that block of memory is started by configuring the NVMCON1 register for a program memory write and performing the long write sequence.

If the PFM address in the TBLPTR is write-protected or if TBLPTR points to an invalid location, the WR bit is cleared without any effect and the WREER is signaled.

The long write is necessary for programming the internal Flash. CPU operation is suspended during a long write cycle and resumes when the operation is complete. The long write operation completes in one instruction cycle. When complete, WR is cleared in hardware and NVMIF is set and an interrupt will occur if NVMIE is also set. The latched data is reset to all '1s'. WREN is not changed.

The internal programming timer controls the write time. The write/erase voltages are generated by an on-chip charge pump, rated to operate over the voltage range of the device.

| R/W-0/0          | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|------------------|---------|-------------------|---------|----------------|------------------|------------------|-------------|

|                  |         |                   | ACC     | <7:0>          |                  |                  |             |

| bit 7            |         |                   |         |                |                  |                  | bit 0       |

|                  |         |                   |         |                |                  |                  |             |

| Legend:          |         |                   |         |                |                  |                  |             |

| R = Readable     | bit     | W = Writable      | bit     | U = Unimpler   | nented bit, read | l as '0'         |             |

| u = Bit is uncha | anged   | x = Bit is unkn   | nown    | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                  |             |

bit 7-0

**ACC<7:0>:** CRC Accumulator Register bits Writing to this register writes to the CRC accumulator register through the CRC write bus. Reading from this register reads the CRC accumulator.

#### REGISTER 13-7: CRCSHIFTH: CRC SHIFT HIGH BYTE REGISTER

| R-0         | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0   |  |  |  |  |

|-------------|-----|-----|-----|-----|-----|-----|-------|--|--|--|--|

| SHIFT<15:8> |     |     |     |     |     |     |       |  |  |  |  |

| bit 7       |     |     |     |     |     |     | bit 0 |  |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SHIFT<15:8>: CRC Shifter Register bits Reading from this register reads the CRC Shifter.

#### REGISTER 13-8: CRCSHIFTL: CRC SHIFT LOW BYTE REGISTER

| R-0   | R-0 | R-0 | R-0   | R-0   | R-0 | R-0 | R-0   |

|-------|-----|-----|-------|-------|-----|-----|-------|

|       |     |     | SHIFT | <7:0> |     |     |       |

| bit 7 |     |     |       |       |     |     | bit 0 |

|       |     |     |       |       |     |     |       |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SHIFT<7:0>: CRC Shifter Register bits

Reading from this register reads the CRC Shifter.

<sup>© 2016-2017</sup> Microchip Technology Inc.

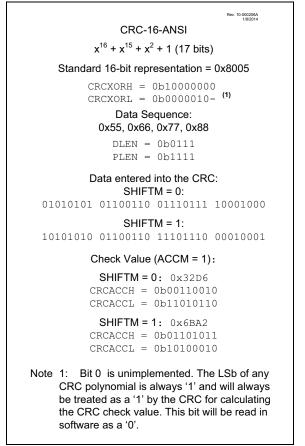

# 13.3 CRC Functional Overview

The CRC module can be used to detect bit errors in the Flash memory using the built-in memory scanner or through user input RAM memory. The CRC module can accept up to a 16-bit polynomial with up to a 16-bit seed value. A CRC calculated check value (or checksum) will then be generated into the CRCACC<15:0> registers for user storage. The CRC module uses an XOR shift register implementation to perform the polynomial division required for the CRC calculation.

## EXAMPLE 13-1: CRC EXAMPLE

| U-0          | U-0                                               | U-0                                                      | R/W-0/0    | R/W-0/0          | R/W-0/0          | R/W-0/0            | R/W-0/0 |  |  |

|--------------|---------------------------------------------------|----------------------------------------------------------|------------|------------------|------------------|--------------------|---------|--|--|

|              | _                                                 | —                                                        | CCP5IE     | CCP4IE           | CCP3IE           | CCP2IE             | CCP1IE  |  |  |

| bit 7        |                                                   |                                                          |            |                  |                  |                    | bit (   |  |  |

| Legend:      |                                                   |                                                          |            |                  |                  |                    |         |  |  |

| R = Readal   | ole bit                                           | W = Writable                                             | bit        | U = Unimpler     | nented bit, read | 1 as '0'           |         |  |  |

| -n = Value a | at POR                                            | '1' = Bit is set                                         | t          | '0' = Bit is cle | ared             | x = Bit is unknown |         |  |  |

|              |                                                   |                                                          |            |                  |                  |                    |         |  |  |

| bit 7-5      | Unimplement                                       | ted: Read as '                                           | 0'         |                  |                  |                    |         |  |  |

| bit 4        | <b>CCP5IE:</b> ECC<br>1 = Enabled<br>0 = Disabled | <b>CCP5IE:</b> ECCP5 Interrupt Enable bit<br>1 = Enabled |            |                  |                  |                    |         |  |  |

| bit 3        | <b>CCP4IE:</b> ECC<br>1 = Enabled<br>0 = Disabled | CP4 Interrupt E                                          | nable bit  |                  |                  |                    |         |  |  |

| bit 2        | <b>CCP3IE:</b> ECC<br>1 = Enabled<br>0 = Disabled | CP3 Interrupt E                                          | nable bit  |                  |                  |                    |         |  |  |

| bit 1        | <b>CCP2IE:</b> ECC<br>1 = Enabled<br>0 = Disabled | CP2 Interrupt E                                          | nable bit  |                  |                  |                    |         |  |  |

| bit 0        | <b>CCP1IE:</b> ECC<br>1 = Enabled<br>0 = Disabled | CP1 Interrupt E                                          | enable bit |                  |                  |                    |         |  |  |

# REGISTER 14-19: PIE7: PERIPHERAL INTERRUPT ENABLE REGISTER 7

| U-0             | U-0                                                  | U-0              | U-0             | R/W-1/1          | R/W-1/1          | R/W-1/1         | R/W-1/1 |

|-----------------|------------------------------------------------------|------------------|-----------------|------------------|------------------|-----------------|---------|

|                 | —                                                    | —                |                 | TMR7GIP          | TMR5GIP          | TMR3GIP         | TMR1GIP |

| bit 7           |                                                      |                  |                 |                  |                  |                 | bit 0   |

|                 |                                                      |                  |                 |                  |                  |                 |         |

| Legend:         |                                                      |                  |                 |                  |                  |                 |         |

| R = Readable    | bit                                                  | W = Writable     | bit             | U = Unimpler     | nented bit, read | l as '0'        |         |

| -n = Value at F | POR                                                  | '1' = Bit is set |                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

|                 |                                                      |                  |                 |                  |                  |                 |         |

| bit 7-4         | Unimplemen                                           | ted: Read as 'd  | )'              |                  |                  |                 |         |

| bit 3           | <b>TMR7GIP:</b> TM<br>1 = High prio<br>0 = Low prior | -                | rupt Priority b | it               |                  |                 |         |

| bit 2           | TMR5GIP: TM<br>1 = High prio<br>0 = Low prior        | •                | rupt Priority b | it               |                  |                 |         |

| bit 1           | TMR3GIP: TM<br>1 = High prio<br>0 = Low prior        | -                | rupt Priority b | it               |                  |                 |         |

| bit 0           | <b>TMR1GIP:</b> TM<br>1 = High prio<br>0 = Low prior | •                | rupt Priority b | it               |                  |                 |         |

#### REGISTER 14-28: IPR6: PERIPHERAL INTERRUPT PRIORITY REGISTER 6

# PIC18(L)F65/66K40

| R/W-0/0                                                                                                                                                                                                                                                                                                                                              | R/W-0/0                                                                                                                                                                                                                                       | R/W-0/0                               | R/W-0/0        | R/W-0/0        | R/W-0/0                  | R/W-0/0          | R/W-0/0      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------|----------------|--------------------------|------------------|--------------|

|                                                                                                                                                                                                                                                                                                                                                      | T0CS<2:0>                                                                                                                                                                                                                                     |                                       | TOASYNC        |                | TOCKP                    | S<3:0>           |              |

| bit 7                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                               |                                       |                |                |                          |                  | bit          |

|                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                               |                                       |                |                |                          |                  |              |

| Legend:                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                               |                                       |                |                |                          |                  |              |

| R = Readable                                                                                                                                                                                                                                                                                                                                         | bit                                                                                                                                                                                                                                           | W = Writable                          | bit            | U = Unimpler   | nented bit, read         | as '0'           |              |

| u = Bit is unchanged                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                               | x = Bit is unki                       | nown           | -n/n = Value a | at POR and BO            | R/Value at all c | other Resets |

| '1' = Bit is set                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                               | '0' = Bit is cle                      | ared           |                |                          |                  |              |

| bit 7-5         TOCS<2:0>:Timer0 Clock Source Select           111 = Reserved         110 = Reserved           101 = SOSC         100 = LFINTOSC           011 = HFINTOSC         010 = Fosc/4           001 = Pin selected by TOCKIPPS (Inve         000 = Pin selected by TOCKIPPS (Non           bit 4         TOASYNC: TMR0 Input Asynchronizati |                                                                                                                                                                                                                                               |                                       |                | d)<br>verted)  |                          |                  |              |

| bit 4                                                                                                                                                                                                                                                                                                                                                | 1 = The inpu                                                                                                                                                                                                                                  |                                       | counter is not | synchronized f | o system clock:<br>DSC/4 | S                |              |

| bit 3-0                                                                                                                                                                                                                                                                                                                                              | <b>TOCKPS&lt;3:0</b><br>1111 = 1:327<br>1110 = 1:163<br>1101 = 1:819<br>1000 = 1:409<br>1011 = 1:204<br>1010 = 1:102<br>1001 = 1:512<br>1000 = 1:256<br>0111 = 1:128<br>0110 = 1:64<br>0011 = 1:32<br>0100 = 1:16<br>0011 = 1:2<br>0000 = 1:1 | 384<br>92<br>96<br>48<br>24<br>2<br>5 | ate Select bit |                |                          |                  |              |

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |  |  |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|--|--|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1         | 1         |  |  |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |  |  |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |  |  |

## TABLE 21-3:EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

## TABLE 21-4:EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1          | 1         |

| PR2 Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

# 21.5.7 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the CCPx pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

#### 21.5.8 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See Section 4.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for additional details.

#### 21.5.9 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

# 24.0 COMPLEMENTARY WAVEFORM GENERATOR (CWG) MODULE

The Complementary Waveform Generator (CWG) produces half-bridge, full-bridge, and steering of PWM waveforms. It is backwards compatible with previous CCP functions. The PIC18(L)F6xK40 family has one instance of the CWG module.

The CWG has the following features:

- Six operating modes:

- Synchronous Steering mode

- Asynchronous Steering mode

- Full-Bridge mode, Forward

- Full-Bridge mode, Reverse

- Half-Bridge mode

- Push-Pull mode

- Output polarity control

- Output steering

- Independent 6-bit rising and falling event deadband timers

- Clocked dead band

- Independent rising and falling dead-band enables

- Auto-shutdown control with:

- Selectable shutdown sources

- Auto-restart option

- Auto-shutdown pin override control

# 24.1 Fundamental Operation

The CWG generates two output waveforms from the selected input source.

The off-to-on transition of each output can be delayed from the on-to-off transition of the other output, thereby, creating a time delay immediately where neither output is driven. This is referred to as dead time and is covered in **Section 24.6 "Dead-Band Control"**.

It may be necessary to guard against the possibility of circuit faults or a feedback event arriving too late or not at all. In this case, the active drive must be terminated before the Fault condition causes damage. This is referred to as auto-shutdown and is covered in **Section 24.10 "Auto-Shutdown"**.

## 24.2 Operating Modes

The CWG module can operate in six different modes, as specified by the MODE<2:0> bits of the CWG1CON0 register:

- Half-Bridge mode

- Push-Pull mode

- Asynchronous Steering mode

- Synchronous Steering mode

- Full-Bridge mode, Forward

- Full-Bridge mode, Reverse

All modes accept a single pulse data input, and provide up to four outputs as described in the following sections.

All modes include auto-shutdown control as described in Section 24.10 "Auto-Shutdown"

Note: Except as noted for Full-bridge mode (Section 24.2.3 "Full-Bridge Modes"), mode changes should only be performed while EN = 0 (Register 24-1).

#### 24.2.1 HALF-BRIDGE MODE

In Half-Bridge mode, two output signals are generated as true and inverted versions of the input as illustrated in Figure 24-2. A non-overlap (dead-band) time is inserted between the two outputs to prevent shoot through current in various power supply applications. Dead-band control is described in **Section 24.6 "Dead-Band Control"**. The output steering feature cannot be used in this mode. A basic block diagram of this mode is shown in Figure 24-1.

The unused outputs CWG1C and CWG1D drive similar signals, with polarity independently controlled by the POLC and POLD bits of the CWG1CON1 register, respectively.

#### 24.2.4.2 Asynchronous Steering Mode

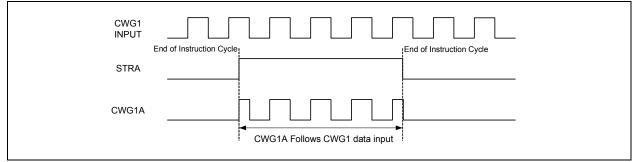

In Asynchronous mode (MODE<2:0> bits = 000, Register 24-1), steering takes effect at the end of the instruction cycle that writes to STR. In Asynchronous Steering mode, the output signal may be an incomplete waveform (Figure 24-10). This operation may be useful when the user firmware needs to immediately remove a signal from the output pin.

### FIGURE 24-10: EXAMPLE OF ASYNCHRONOUS STEERING (MODE<2:0>= 000)

## 24.2.4.3 Start-up Considerations

The application hardware must use the proper external pull-up and/or pull-down resistors on the CWG output pins. This is required because all I/O pins are forced to high-impedance at Reset.

The POLy bits (Register 24-2) allow the user to choose whether the output signals are active-high or active-low.

#### **Register Definitions: MSSP Control** 27.4

| R/W-0        | R/W-0                    | R-0                            | R-0            | R-0                 | R-0            | R-0             | R-0         |

|--------------|--------------------------|--------------------------------|----------------|---------------------|----------------|-----------------|-------------|

| SMP          | CKE <sup>(1)</sup>       | D/A                            | Р              | S                   | R/W            | UA              | BF          |

| bit 7        |                          |                                |                |                     |                |                 | bit         |

|              |                          |                                |                |                     |                |                 |             |

| Legend:      |                          |                                |                |                     |                |                 |             |

| R = Readat   |                          | W = Writable                   |                | U = Unimpler        |                |                 |             |

| -n = Value a | at POR                   | '1' = Bit is set               |                | '0' = Bit is cle    | ared           | x = Bit is unkr | nown        |

| bit 7        | SMP: Samp                | le hit                         |                |                     |                |                 |             |

|              | SPI Master               |                                |                |                     |                |                 |             |

|              |                          | ita is sampled at              | the end of da  | ata output time     |                |                 |             |

|              | 0 = Input da             | ita is sampled at              | the middle of  | f data output time  | e              |                 |             |

|              | <u>SPI Slave m</u>       |                                |                |                     |                |                 |             |

|              |                          | e cleared when                 |                | n Slave mode.       |                |                 |             |

| bit 6        |                          | lock Select bit <sup>(1)</sup> |                |                     |                |                 |             |

|              |                          |                                |                | active to Idle cl   |                |                 |             |

|              | _                        |                                | ransition from | n Idle to active cl | ock state      |                 |             |

| bit 5        | D/A: Data/A              |                                |                |                     |                |                 |             |

|              | Used in I <sup>2</sup> C | mode only.                     |                |                     |                |                 |             |

| bit 4        | P: Stop bit              |                                |                |                     |                |                 |             |

|              |                          | mode only. This                | bit is cleared | when the MSSF       | Px module is c | lisabled; SSPEN | is cleared. |

| bit 3        | S: Start bit             |                                |                |                     |                |                 |             |

|              | Used in I <sup>2</sup> C | ,                              |                |                     |                |                 |             |

| bit 2        |                          | Write Information              | n bit          |                     |                |                 |             |

|              | Used in I <sup>2</sup> C | ,                              |                |                     |                |                 |             |

| bit 1        | UA: Update               |                                |                |                     |                |                 |             |

|              | Used in I <sup>2</sup> C | ,                              |                |                     |                |                 |             |

| bit 0        |                          | Full Status bit (Re            |                | • ·                 |                |                 |             |

|              |                          | is complete, SS                |                |                     |                |                 |             |

|              |                          | is not complete                | , SSPXBUF IS   | sempty              |                |                 |             |

| Note 1:      | Polarity of clock        | state is set by t              | ne CKP bit (S  | SPxCON1<4>).        |                |                 |             |

|              |                          |                                |                |                     |                |                 |             |

#### REGISTER 27-1: SSPxSTAT: MSSPx STATUS REGISTER (SPI MODE)

# PIC18(L)F65/66K40

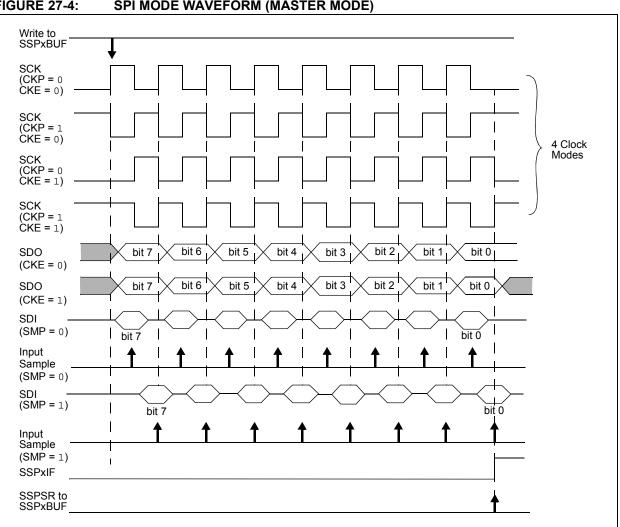

#### FIGURE 27-4: SPI MODE WAVEFORM (MASTER MODE)

#### 27.5.2 SPI SLAVE MODE

In Slave mode, the data is transmitted and received as external clock pulses appear on SCK. When the last bit is latched, the SSPxIF interrupt flag bit is set.

Before enabling the module in SPI Slave mode, the clock line must match the proper Idle state. The clock line can be observed by reading the SCK pin. The Idle state is determined by the CKP bit of the SSPxCON1 register.

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. The shift register is clocked from the SCK pin input and when a byte is received, the device will generate an interrupt. If enabled, the device will wake-up from Sleep.

#### 27.5.3 DAISY-CHAIN CONFIGURATION

The SPI bus can sometimes be connected in a daisy-chain configuration. The first slave output is connected to the second slave input, the second slave output is connected to the third slave input, and so on. The final slave output is connected to the master input. Each slave sends out, during a second group of clock pulses, an exact copy of what was received during the first group of clock pulses. The whole chain acts as one large communication shift register. The daisy-chain feature only requires a single Slave Select line from the master device.

Figure 27-5 shows the block diagram of a typical daisy-chain connection when operating in SPI mode.

In a daisy-chain configuration, only the most recent byte on the bus is required by the slave. Setting the BOEN bit of the SSPxCON3 register will enable writes to the SSPxBUF register, even if the previous byte has not been read. This allows the software to ignore data that may not apply to it.

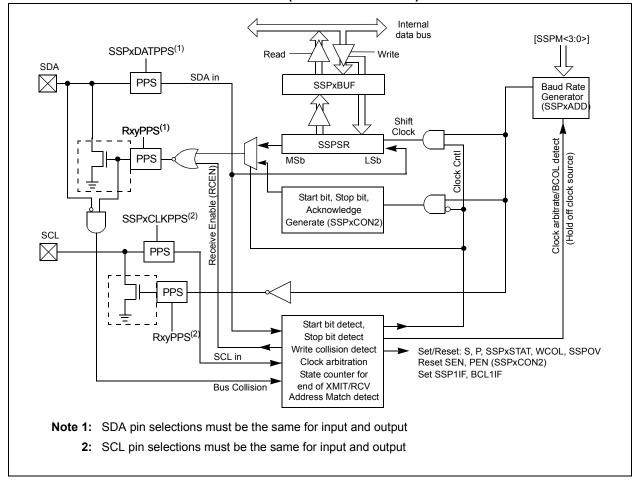

controlled through addressing. Figure 27-9 is a block diagram of the  $I^2C$  interface module in Master mode.

Figure 27-10 is a diagram of the  $I^2C$  interface module

in Slave mode.

# 27.6 I<sup>2</sup>C Mode Overview

The Inter-Integrated Circuit (I<sup>2</sup>C) bus is a multi-master serial data communication bus. Devices communicate in a master/slave environment where the master devices initiate the communication. A slave device is

FIGURE 27-9: MSSP BLOCK DIAGRAM (I<sup>2</sup>C MASTER MODE)

# **30.4 ADC Acquisition Time**

To ensure accurate temperature measurements, the user must wait at least 200  $\mu$ s after the ADC input multiplexer is connected to the temperature indicator output before the conversion is performed. In addition, the user must wait 200  $\mu$ s between consecutive conversions of the temperature indicator output.

#### TABLE 30-2: SUMMARY OF REGISTERS ASSOCIATED WITH THE TEMPERATURE INDICATOR

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0  | Register<br>on page |

|--------|-------|--------|-------|-------|-------|--------|-------|--------|---------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG | CDFV  | R<1:0> | ADFVF | R<1:0> | 479                 |

Legend: — = Unimplemented location, read as '0'. Shaded cells are unused by the temperature indicator module.

| U-0                  | U-0                          | U-0                                              | R/W-0/0           | R/W-0/0         | R/W-0/0            | R/W-0/0            | R/W-0/0 |  |  |

|----------------------|------------------------------|--------------------------------------------------|-------------------|-----------------|--------------------|--------------------|---------|--|--|

|                      | —                            | —                                                |                   |                 | ADACT<4:0>         |                    |         |  |  |

| bit 7                |                              |                                                  |                   |                 |                    |                    | bit     |  |  |

|                      |                              |                                                  |                   |                 |                    |                    |         |  |  |

| Legend:              |                              |                                                  |                   |                 |                    | (0)                |         |  |  |

| R = Readable         |                              | W = Writable                                     |                   |                 | ented bit, read as |                    | -       |  |  |

| u = Bit is unchanged |                              | x = Bit is unkr                                  |                   | -n/n = Value at | POR and BOR/       | Value at all other | Resets  |  |  |

| '1' = Bit is set     |                              | '0' = Bit is clea                                | ared              |                 |                    |                    |         |  |  |

| bit 7-5              | Unimpleme                    | nted: Read as '0'                                |                   |                 |                    |                    |         |  |  |

| bit 4-0              | ADACT<4:0                    | >: Auto-Conversion                               | on Trigger Select | Bits            |                    |                    |         |  |  |

|                      | 11111 <b>= Sof</b>           | ftware write to AD                               | РСН               |                 |                    |                    |         |  |  |

|                      |                              | served, do not use                               |                   |                 |                    |                    |         |  |  |

|                      |                              | ftware read of AD                                |                   |                 |                    |                    |         |  |  |

|                      |                              | ftware read of AD                                |                   |                 |                    |                    |         |  |  |

|                      | •                            | served, do not use                               | 5                 |                 |                    |                    |         |  |  |

|                      | •                            |                                                  |                   |                 |                    |                    |         |  |  |

|                      | •                            |                                                  |                   |                 |                    |                    |         |  |  |

|                      | 11000 = Reserved, do not use |                                                  |                   |                 |                    |                    |         |  |  |

|                      |                              | errupt-on-change                                 | Interrupt Flag    |                 |                    |                    |         |  |  |

|                      | 10110 = C3                   | _                                                |                   |                 |                    |                    |         |  |  |

|                      | 10101 = C2                   |                                                  |                   |                 |                    |                    |         |  |  |

|                      | -                            | 0100 = C1_out<br>0011 = PWM7_out                 |                   |                 |                    |                    |         |  |  |

|                      |                              | 10011 = PWM/_00t                                 |                   |                 |                    |                    |         |  |  |

|                      |                              | 10001 = CCP5_out                                 |                   |                 |                    |                    |         |  |  |

|                      |                              | 10000 = CCP4_out                                 |                   |                 |                    |                    |         |  |  |

|                      | 01111 <b>= CC</b>            |                                                  |                   |                 |                    |                    |         |  |  |

|                      | 01110 <b>= CC</b>            | _                                                |                   |                 |                    |                    |         |  |  |

|                      | 01101 = CC                   |                                                  |                   |                 |                    |                    |         |  |  |

|                      |                              | IT2_overflow                                     |                   |                 |                    |                    |         |  |  |

|                      |                              | 01011 = SMT1_overflow<br>01010 = TMR8_postscaled |                   |                 |                    |                    |         |  |  |

|                      | 01001 = TMR7_overflow        |                                                  |                   |                 |                    |                    |         |  |  |

|                      |                              | R6_postscaled                                    |                   |                 |                    |                    |         |  |  |

|                      |                              | R5_overflow                                      |                   |                 |                    |                    |         |  |  |

|                      |                              | R4_postscaled                                    |                   |                 |                    |                    |         |  |  |

|                      |                              | R3_overflow                                      |                   |                 |                    |                    |         |  |  |

|                      |                              | R2_postscaled                                    |                   |                 |                    |                    |         |  |  |

|                      |                              | R1_overflow<br>R0_overflow                       |                   |                 |                    |                    |         |  |  |

|                      |                              | selected by ADA                                  | CTPPS             |                 |                    |                    |         |  |  |

|                      | 00000 = Ext                  |                                                  |                   |                 |                    |                    |         |  |  |

# REGISTER 32-32: ADACT: ADC AUTO CONVERSION TRIGGER CONTROL REGISTER

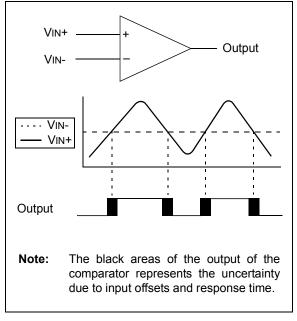

# 33.0 COMPARATOR MODULE (C1/2/3)

Comparators are used to interface analog circuits to a digital circuit by comparing two analog voltages and providing a digital indication of their relative magnitudes. Comparators are very useful mixed signal building blocks because they provide analog functionality independent of program execution. The PIC18(L)F6xK40 family has three comparators (C1/2/3).

The analog comparator module includes the following features:

- · Programmable input selection

- · Programmable output polarity

- Rising/falling output edge interrupts

- Wake-up from Sleep

- CWG Auto-shutdown source

- Selectable voltage reference

- ADC Auto-trigger

- TMR1/3/5/7 Gate

- TMR2/4/6/8 Reset

- CCP Capture Mode Input

- DSM Modulator Source

- Input and Window signal to Signal Measurement

Timer

# 33.1 Comparator Overview

A single comparator is shown in Figure 33-1 along with the relationship between the analog input levels and the digital output. When the analog voltage at VIN+ is less than the analog voltage at VIN-, the output of the comparator is a digital low level. When the analog voltage at VIN+ is greater than the analog voltage at VIN-, the output of the comparator is a digital high level.

# PIC18(L)F65/66K40

| RRN                         | NCF                                                                                                                                  | Rotate Right f (No Carry)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                         |               |                |  |  |  |  |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|---------------|----------------|--|--|--|--|

| Synt                        | ax:                                                                                                                                  | RRNCF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | f {,d {,a}}                                             |               |                |  |  |  |  |

| Oper                        | rands:                                                                                                                               | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                         |               |                |  |  |  |  |

| Oper                        | ration:                                                                                                                              | · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $(f) \rightarrow dest,$<br>$(f<0>) \rightarrow dest<7>$ |               |                |  |  |  |  |

| Statu                       | is Affected:                                                                                                                         | N, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                         |               |                |  |  |  |  |

| Enco                        | oding:                                                                                                                               | 0100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 00da                                                    | fff           | f ffff         |  |  |  |  |

| Desc                        | pription:                                                                                                                            | The contents of register 'f' are rotated<br>one bit to the right. If 'd' is '0', the result<br>is placed in W. If 'd' is '1', the result is<br>placed back in register 'f' (default).<br>If 'a' is '0', the Access Bank will be<br>selected (default), overriding the BSR<br>value. If 'a' is '1', then the bank will be<br>selected as per the BSR value.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See Sec-<br>tion 36.2.3 "Byte-Oriented and Bit-<br>Oriented Instructions in Indexed Lit-<br>eral Offset Mode" for details. |                                                         |               |                |  |  |  |  |

|                             |                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                         | egister f     |                |  |  |  |  |

|                             | 1- ·                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                         | <u> </u>      |                |  |  |  |  |

| Word                        |                                                                                                                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | L                                                       | <u> </u>      |                |  |  |  |  |

| Cycle                       | es:                                                                                                                                  | 1<br>1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                         | 0             |                |  |  |  |  |

| Cycle                       | es:<br>sycle Activity:                                                                                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                         | -             |                |  |  |  |  |

| Cycle                       | es:<br>cycle Activity:<br>Q1                                                                                                         | 1<br>Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Q3                                                      | 3             | <br>Q4         |  |  |  |  |

| Cycle                       | es:<br>sycle Activity:                                                                                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                         | ess           |                |  |  |  |  |

| Cycle<br>Q C                | es:<br>cycle Activity:<br>Q1                                                                                                         | 1<br>Q2<br>Read<br>register 'f'<br>RRNCF<br>tion<br>= 1101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Q3<br>Proce<br>Dat<br>REG, 1,<br>0111                   | ess<br>a      | Q4<br>Write to |  |  |  |  |

| Cycle<br>Q C<br><u>Exar</u> | es:<br>ycle Activity:<br>Q1<br>Decode<br><u>nple 1</u> :<br>Before Instruct<br>REG<br>After Instruction<br>REG                       | 1<br>Q2<br>Read<br>register 'f'<br>RRNCF<br>tion<br>= 1101<br>on<br>= 1110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Q3<br>Proce<br>Dat<br>REG, 1,<br>0111<br>1011           | ess<br>a<br>0 | Q4<br>Write to |  |  |  |  |

| Cycle<br>Q C<br><u>Exar</u> | es:<br>ycle Activity:<br>Q1<br>Decode<br>nple 1:<br>Before Instruct<br>REG<br>After Instruction<br>REG<br>nple 2:                    | 1<br>Q2<br>Read<br>register 'f'<br>RRNCF<br>tion<br>= 1101<br>on<br>= 1110<br>RRNCF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Q3<br>Proce<br>Dat<br>REG, 1,<br>0111<br>1011           | ess<br>a<br>0 | Q4<br>Write to |  |  |  |  |

| Cycle<br>Q C<br><u>Exar</u> | es:<br>ycle Activity:<br>Q1<br>Decode<br>nple 1:<br>Before Instruct<br>REG<br>After Instruction<br>REG<br>nple 2:<br>Before Instruct | 1<br>Q2<br>Read<br>register 'f'<br>RRNCF<br>tion<br>= 1101<br>on<br>= 1110<br>RRNCF<br>tion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Q3<br>Proce<br>Dat<br>REG, 1,<br>0111<br>1011           | ess<br>a<br>0 | Q4<br>Write to |  |  |  |  |

| Cycle<br>Q C<br><u>Exar</u> | es:<br>ycle Activity:<br>Q1<br>Decode<br>nple 1:<br>Before Instruct<br>REG<br>After Instruction<br>REG<br>nple 2:                    | 1<br>Q2<br>Read<br>register 'f'<br>RRNCF<br>tion<br>= 1101<br>m<br>= 1110<br>RRNCF<br>tion<br>= ?<br>= 1101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Q3<br>Proce<br>Dat<br>REG, 1,<br>0111<br>1011           | ess<br>a<br>0 | Q4<br>Write to |  |  |  |  |

| SETF                                       | Set f                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                       |  |  |  |  |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|--|--|--|

| Syntax:                                    | SETF f{,;                                                                                                                                     | a}                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                       |  |  |  |  |

| Operands:                                  | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                       |  |  |  |  |

| Operation:                                 | $FFh\tof$                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                       |  |  |  |  |