Welcome to E-XFL.COM

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                   |

|----------------------------|------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M7                                                                          |

| Core Size                  | 32-Bit Single-Core                                                                       |

| Speed                      | 216MHz                                                                                   |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                             |

| Number of I/O              | 138                                                                                      |

| Program Memory Size        | 512KB (512K x 8)                                                                         |

| Program Memory Type        | FLASH                                                                                    |

| EEPROM Size                | -                                                                                        |

| RAM Size                   | 256K x 8                                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                              |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                    |

| Oscillator Type            | Internal                                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                        |

| Mounting Type              | Surface Mount                                                                            |

| Package / Case             | 176-UFBGA                                                                                |

| Supplier Device Package    | 176-UFBGA (10x10)                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f723iek6                    |

|                            |                                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 3.5 | Genera   | I data processing instructions | . 85  |

|-----|----------|--------------------------------|-------|

|     | 3.5.1    | ADD, ADC, SUB, SBC, and RSB    |       |

|     | 3.5.2    | AND, ORR, EOR, BIC, and ORN    |       |

|     | 3.5.3    | ASR, LSL, LSR, ROR, and RRX    |       |

|     | 3.5.4    | CLZ                            |       |

|     | 3.5.5    | CMP and CMN                    |       |

|     | 3.5.6    | MOV and MVN                    | 93    |

|     | 3.5.7    | MOVT                           | 94    |

|     | 3.5.8    | REV, REV16, REVSH, and RBIT    | 95    |

|     | 3.5.9    | SADD16 and SADD8               | 96    |

|     | 3.5.10   | SHADD16 and SHADD8             | 97    |

|     | 3.5.11   | SHASX and SHSAX                | 98    |

|     | 3.5.12   | SHSUB16 and SHSUB8             | 99    |

|     | 3.5.13   | SSUB16 and SSUB8               | . 100 |

|     | 3.5.14   | SASX and SSAX                  | . 101 |

|     | 3.5.15   | TST and TEQ                    | . 102 |

|     | 3.5.16   | UADD16 and UADD8               | . 103 |

|     | 3.5.17   | UASX and USAX                  | . 104 |

|     | 3.5.18   | UHADD16 and UHADD8             | . 105 |

|     | 3.5.19   | UHASX and UHSAX                | . 106 |

|     | 3.5.20   | UHSUB16 and UHSUB8             | . 107 |

|     | 3.5.21   | SEL                            | . 108 |

|     | 3.5.22   | USAD8                          | . 108 |

|     | 3.5.23   | USADA8                         | . 109 |

|     | 3.5.24   | USUB16 and USUB8               | . 110 |

| 3.6 | Multiply | and divide instructions        | . 111 |

|     | 3.6.1    | MUL, MLA, and MLS              | . 112 |

|     | 3.6.2    | UMULL, UMAAL, UMLAL            | . 113 |

|     | 3.6.3    | SMLA and SMLAW                 | . 115 |

|     | 3.6.4    | SMLAD                          | . 116 |

|     | 3.6.5    | SMLAL and SMLALD               | . 117 |

|     | 3.6.6    | SMLSD and SMLSLD               | . 119 |

|     | 3.6.7    | SMMLA and SMMLS                | . 121 |

|     | 3.6.8    | SMMUL                          | . 122 |

|     | 3.6.9    | SMUAD and SMUSD                | . 123 |

|     | 3.6.10   | SMUL and SMULW                 | . 124 |

|     | 3.6.11   | UMULL, UMLAL, SMULL, and SMLAL | . 126 |

#### 2 The Cortex-M7 processor

#### 2.1 **Programmers model**

This section describes the Cortex<sup>®</sup>-M7 programmers model. In addition to the individual core register descriptions, it contains information about the processor modes and privilege levels for software execution and stacks.

#### 2.1.1 Processor mode and privilege levels for software execution

The processor modes are:

| Thread mode | Executes application software. The processor enters Thread mode when it comes out of reset. |

|-------------|---------------------------------------------------------------------------------------------|

|             |                                                                                             |

Handler mode Handles exceptions. The processor returns to Thread mode when it has finished all exception processing.

The privilege levels for software execution are:

| Unprivileged | The software:                                                                                                                                             |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | <ul> <li>Has limited access to system registers using the MSR and MRS<br/>instructions, and cannot use the CPS instruction to mask interrupts.</li> </ul> |

|              | Cannot access the system timer, NVIC, or system control block.                                                                                            |

|              | <ul> <li>Might have restricted access to memory or peripherals.</li> </ul>                                                                                |

|              | Unprivileged software executes at the unprivileged level.                                                                                                 |

| Privileged   | The software can use all the instructions and has access to all resources.                                                                                |

|              | Privileged software executes at the privileged level                                                                                                      |

*Privileged software* executes at the privileged level.

In Thread mode, the CONTROL register controls whether software execution is privileged or unprivileged, see CONTROL register on page 27. In Handler mode, software execution is always privileged.

Only privileged software can write to the CONTROL register to change the privilege level for software execution in Thread mode. Unprivileged software can use the SVC instruction to make a supervisor call to transfer control to privileged software.

#### 2.1.2 **Stacks**

The processor uses a full descending stack. This means the stack pointer holds the address of the last stacked item in memory. When the processor pushes a new item onto the stack, it decrements the stack pointer and then writes the item to the new memory location. The processor implements two stacks, the *main stack* and the *process stack*, with a pointer for each held in independent registers, see Stack Pointer on page 21.

In Thread mode, the CONTROL register controls whether the processor uses the main stack or the process stack, see CONTROL register on page 27. In Handler mode, the processor always uses the main stack. The options for processor operations are:

DocID028474 Rev 3

| Bits   | Name       | Function                                                                                                                                                                                                                                                                                                                                                                   |

|--------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [31:9] | -          | Reserved                                                                                                                                                                                                                                                                                                                                                                   |

| [8:0]  | ISR_NUMBER | This is the number of the current exception:<br>0 = Thread mode.<br>1 = Reserved.<br>2 = NMI.<br>3 = HardFault.<br>4 = MemManage.<br>5 = BusFault<br>6 = UsageFault<br>7-10 = Reserved<br>11 = SVCall.<br>12 = Reserved for debug<br>13 = Reserved<br>14 = PendSV.<br>15 = SysTick.<br>16 = IRQ0.<br>256 = IRQ239.<br>see Exception types on page 39 for more information. |

Table 5. IPSR bit assignments

# Execution Program Status register

The EPSR contains the Thumb state bit, and the execution state bits for either the:

- *If-Then* (IT) instruction.

- *Interruptible-Continuable Instruction* (ICI) field for an interrupted load multiple or store multiple instruction.

See the register summary in *Table 6 on page 24* for the EPSR attributes. The bit assignments are

| Bits             | Name | Function                                                                                                   |

|------------------|------|------------------------------------------------------------------------------------------------------------|

| [31:27]          | -    | Reserved.                                                                                                  |

| [26:25], [15:10] | ICI  | Interruptible-continuable instruction bits, see <i>Interruptible-continuable instructions on page 25</i> . |

| [26:25], [15:10] | IT   | Indicates the execution state bits of the IT instruction, see <i>IT on</i> page 148.                       |

| [24]             | Т    | Thumb state bit, see Thumb state.                                                                          |

| [23:16]          | -    | Reserved.                                                                                                  |

| [9:0]            | -    | Reserved.                                                                                                  |

| Table 6 | . EPSR | bit assi | gnments |

|---------|--------|----------|---------|

|---------|--------|----------|---------|

| Mnemonic                                 | Operands                                                 | Brief description                                                                                                    | Flags  | Page                |

|------------------------------------------|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------|---------------------|

| Witterfloritc                            | -                                                        | -                                                                                                                    | i lays | Fage                |

| VCMPE.F<32 64>                           | <sd dd>, &lt;<sm dm>  <br/>#0.0&gt;</sm dm></sd dd>      | Compare two floating-point<br>registers, or one floating-<br>point register and zero with<br>Invalid Operation check | FPSCR  | 3.11.3 on page 154  |

| VCVT                                     | F<32 64>. <s u>,<br/>&lt;16 32&gt;</s u>                 | Convert from floating-point to fixed point                                                                           | -      | 3.11.5 on page 156  |

| VCVT                                     | <s u>,<br/>&lt;16 32&gt;.F&lt;32 64&gt;</s u>            | Convert from fixed point to<br>floating-point                                                                        |        | 3.11.5 on page 156  |

| VCVT.S32.F<32 64>                        | <sd dd>, <sm dm></sm dm></sd dd>                         | Convert from floating-point to integer                                                                               | -      | 3.11.4 on page 155  |

| VCVT <b t>.F&lt;32 64<br/>&gt;.F16</b t> | <sd dd>, Sm</sd dd>                                      | Convert half-precision value<br>to single-precision or<br>double-precision                                           | -      | 3.11.6 on page 157  |

| VCVTA.F<32 64>                           | <sd dd>, <sm dm></sm dm></sd dd>                         | Convert from floating-point<br>to integer with directed<br>rounding to nearest ties<br>away                          | -      | 3.11.33 on page 173 |

| VCVTM.F<32 64>                           | <sd dd>, <sm dm></sm dm></sd dd>                         | Convert from floating-point<br>to integer with directed<br>rounding towards minus<br>infinity                        | -      | 3.11.33 on page 173 |

| VCVTN.F<32 64>                           | <sd dd>, <sm dm></sm dm></sd dd>                         | Convert from floating-point<br>to integer with directed<br>rounding to nearest even                                  | -      | 3.11.33 on page 173 |

| VCVTP.F<32 64>                           | <sd dd>, <sm dm></sm dm></sd dd>                         | Convert from floating-point<br>to integer with directed<br>rounding towards plus<br>infinity                         | -      | 3.11.33 on page 173 |

| VCVTR.S32.F<32 64<br>>                   | <sd dd>, <sm dm></sm dm></sd dd>                         | Convert between floating-<br>point and integer with<br>rounding.                                                     | FPSCR  | 3.11.4 on page 155  |

| VCVT <b t>.F16.F&lt;3<br/>2 64&gt;</b t> | Sd, <sm dm></sm dm>                                      | Convert single-precision or<br>double precision register to<br>half-precision                                        | -      | 3.11.5 on page 156  |

| VDIV.F<32 64>                            | { <sd dd>,} <sn dn>,<br/><sm dm></sm dm></sn dn></sd dd> | Floating-point Divide                                                                                                | -      | 3.11.7 on page 157  |

| VFMA.F<32 64>                            | { <sd dd>,} <sn dn>,<br/><sm dm></sm dm></sn dn></sd dd> | Floating-point Fused<br>Multiply Accumulate                                                                          | -      | 3.11.8 on page 158  |

| VFMS.F<32 64>                            | { <sd dd>,} <sn dn>,<br/><sm dm></sm dm></sn dn></sd dd> | Floating-point Fused<br>Multiply Subtract                                                                            | -      | 3.11.8 on page 158  |

| VFNMA.F<32 64>                           | { <sd dd>,} <sn dn>,<br/><sm dm></sm dm></sn dn></sd dd> | Floating-point Fused<br>Negate Multiply Accumulate                                                                   | -      | 3.11.9 on page 159  |

| VFNMS.F<32 64>                           | { <sd dd>,} <sn dn>,<br/><sm dm></sm dm></sn dn></sd dd> | Floating-point Fused<br>Negate Multiply Subtract                                                                     | -      | 3.11.9 on page 159  |

| Table 22. Cortex <sup>®</sup> -M7 instructions (continued) | Table 22. | Cortex <sup>®</sup> -M7 | instructions | (continued) | ) |

|------------------------------------------------------------|-----------|-------------------------|--------------|-------------|---|

|------------------------------------------------------------|-----------|-------------------------|--------------|-------------|---|

### **Condition code suffixes**

The instructions that can be conditional have an optional condition code, shown in syntax descriptions as {*cond*}. Conditional execution requires a preceding IT instruction. An instruction with a condition code is only executed if the condition code flags in the APSR meet the specified condition. *Table 25* shows the condition codes to use.

The conditional execution can be used with the IT instruction to reduce the number of branch instructions in the code.

*Table 25* also shows the relationship between condition code suffixes and the N, Z, C, and V flags.

| Suffix   | Flags              | Meaning                                                  |

|----------|--------------------|----------------------------------------------------------|

| EQ       | Z = 1              | Equal                                                    |

| NE       | Z = 0              | Not equal                                                |

| CS or HS | C = 1              | Higher or same, unsigned                                 |

| CC or LO | C = 0              | Lower, unsigned                                          |

| MI       | N = 1              | Negative                                                 |

| PL       | N = 0              | Positive or zero                                         |

| VS       | V = 1              | Overflow                                                 |

| VC       | V = 0              | No overflow                                              |

| н        | C = 1 and Z = 0    | Higher, unsigned                                         |

| LS       | C = 0 or Z = 1     | Lower or same, unsigned                                  |

| GE       | N = V              | Greater than or equal, signed                            |

| LT       | N != V             | Less than, signed                                        |

| GT       | Z = 0 and N = V    | Greater than, signed                                     |

| LE       | Z = 1 and N != V   | Less than or equal, signed                               |

| AL       | Can have any value | Always. This is the default when no suffix is specified. |

Table 25. Condition code suffixes

*Example 3-1: absolute value* shows the use of a conditional instruction to find the absolute value of a number. R0 = abs(R1).

#### Example 3-1: absolute value

| MOVS  | R0, R1     | ; R0 = R1, setting flags.                 |

|-------|------------|-------------------------------------------|

| IT    | MI         | ; Skipping next instruction if value 0 or |

|       |            | ; positive.                               |

| RSBMI | R0, R0, #0 | ; If negative, $R0 = -R0$ .               |

| Where: |                                                                                                                                                                                                                                    |  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| op     | Is one of:<br>LDR Load register.<br>STR Store register.                                                                                                                                                                            |  |

| type   | Is one of:BUnsigned byte, zero extend to 32 bits on loads.SBSigned byte, sign extend to 32 bits (LDR only).HUnsigned halfword, zero extend to 32 bits on loads.SHSigned halfword, sign extend to 32 bits (LDR only)Omit, for word. |  |

| cond   | Is an optional condition code. See <i>Conditional execution on page 68</i> .                                                                                                                                                       |  |

| Rt     | Is the register to load or store.                                                                                                                                                                                                  |  |

| Rn     | Is the register on which the memory address is based.                                                                                                                                                                              |  |

| offset | Is an offset from $Rn$ . If $offset$ is omitted, the address is the contents of $Rn$ .                                                                                                                                             |  |

| Rt2    | Is the additional register to load or store for two-word operations.                                                                                                                                                               |  |

# Operation

LDR instructions load one or two registers with a value from memory.

STR instructions store one or two register values to memory.

Load and store instructions with immediate offset can use the following addressing modes:

#### **Offset addressing**

The offset value is added to or subtracted from the address obtained from the register Rn. The result is used as the address for the memory access. The register Rn is unaltered. The assembly language syntax for this mode is:

[Rn, #offset]

#### **Pre-indexed addressing**

The offset value is added to or subtracted from the address obtained from the register Rn. The result is used as the address for the memory access and written back into the register Rn. The assembly language syntax for this mode is:

[Rn, #offset]!

#### Post-indexed addressing

The address obtained from the register Rn is used as the address for the memory access. The offset value is added to or subtracted from the address, and written back into the register Rn. The assembly language syntax for this mode is:

[Rn], #offset

The value to load or store can be a byte, halfword, word, or two words. Bytes and halfwords can either be signed or unsigned. See *Address alignment on page 68*.

Table 27 shows the ranges of offset for immediate, pre-indexed and post-indexed forms

| Instruction type                                         | Immediate offset                         | Pre-indexed                              | Post-indexed                             |

|----------------------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|

| Word, halfword, signed<br>halfword, byte, or signed byte | -255 to 4095                             | -255 to 255                              | -255 to 255                              |

| Two words                                                | multiple of 4 in the range -1020 to 1020 | multiple of 4 in the range -1020 to 1020 | multiple of 4 in the range -1020 to 1020 |

Table 27. Offset ranges

### Restrictions

For load instructions:

- *Rt* can be SP or PC for word loads only.

- *Rt* must be different from *Rt2* for two-word loads.

- *Rn* must be different from *Rt* and *Rt2* in the pre-indexed or post-indexed forms.

When *Rt* is PC in a word load instruction:

- Bit[0] of the loaded value must be 1 for correct execution.

- A branch occurs to the address created by changing bit[0] of the loaded value to 0.

- If the instruction is conditional, it must be the last instruction in the IT block.

For store instructions:

- *Rt* can be SP for word stores only.

- Rt must not be PC.

- *Rn* must not be PC.

- *Rn* must be different from *Rt* and *Rt2* in the pre-indexed or post-indexed forms.

#### **Condition flags**

These instructions do not change the flags.

| LDR<br>LDRNE | R8, [R10]<br>R2, [R5, #960]! | ; Loads R8 from the address in R10.<br>; Loads (conditionally) R2 from a word<br>; 960 bytes above the address in R5,<br>; and increments R5 by 960. |

|--------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| STR          | R2, [R9,#const-struc]        | -                                                                                                                                                    |

| STRH         | R3, [R4], #4                 | ; Store R3 as halfword data into<br>; address in R4, then increment R4 by<br>; 4.                                                                    |

| LDRD         | R8, R9, [R3, #0x20]          | ; Load R8 from a word 32 bytes above<br>; the address in R3, and load R9 from a<br>; word 36 bytes above the address in<br>; R3.                     |

| STRD         | R0, R1, [R8], #-16           | ; Store R0 to address in R8, and store<br>; R1 to a word 4 bytes above the<br>; address in R8, and then decrement R8<br>; by 16.                     |

*subtraction* shows instructions that subtract a 96-bit integer contained in R9, R1, and R11 from another contained in R6, R2, and R8. The example stores the result in R6, R9, and R2.

#### Example 3-5: 96-bit subtraction

SUBSR6, R6, R9; Subtract the least significant words.SBCSR9, R2, R1; Subtract the middle words with carry.SBCR2, R8, R11; Subtract the most significant words with; carry.

# 3.5.2 AND, ORR, EOR, BIC, and ORN

Logical AND, OR, Exclusive OR, Bit Clear, and OR NOT.

### Syntax

op{S}{cond} {Rd,} Rn, Operand2

#### Where:

| op       | Is one of:                                                                                                                                                     |  |  |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|          | AND Logical AND.                                                                                                                                               |  |  |

|          | ORR Logical OR, or bit set.                                                                                                                                    |  |  |

|          | EOR Logical Exclusive OR.                                                                                                                                      |  |  |

|          | BIC Logical AND NOT, or bit clear.                                                                                                                             |  |  |

|          | ORN Logical OR NOT.                                                                                                                                            |  |  |

| S        | Is an optional suffix. If $s$ is specified, the condition code flags are updated on the result of the operation, see <i>Conditional execution on page 68</i> . |  |  |

| cond     | Is an optional condition code. See Conditional execution on page 68.                                                                                           |  |  |

| Rd       | Is the destination register.                                                                                                                                   |  |  |

| Rn       | Is the register holding the first operand.                                                                                                                     |  |  |

| Operand2 | Is a flexible second operand. See <i>Flexible second operand on page 64</i> for details of the options.                                                        |  |  |

|          |                                                                                                                                                                |  |  |

# Operation

The AND, EOR, and ORR instructions perform bitwise AND, Exclusive OR, and OR operations on the values in *Rn* and *Operand2*.

The BIC instruction performs an AND operation on the bits in *Rn* with the complements of the corresponding bits in the value of *Operand2*.

The ORN instruction performs an OR operation on the bits in *Rn* with the complements of the corresponding bits in the value of *Operand2*.

#### Restrictions

Do not use SP and do not use PC.

# 3.5.10 SHADD16 and SHADD8

Signed Halving Add 16 and Signed Halving Add 8.

#### Syntax

| op{cond}{F | 2d,} Rn, Rm                                                                  |

|------------|------------------------------------------------------------------------------|

| Where:     |                                                                              |

| ор         | Is one of:                                                                   |

|            | SHADD16 Signed Halving Add 16                                                |

|            | SHADD8 Signed Halving Add 8                                                  |

| cond       | Is an optional condition code. See <i>Conditional execution on page 68</i> . |

| Rd         | Is the destination register.                                                 |

| Rn         | Is the first operand register.                                               |

| Rm         | Is the second operand register.                                              |

#### Operation

Use these instructions to add 16-bit and 8-bit data and then to halve the result before writing the result to the destination register.

The SHADD16 instruction:

- 1. Adds each halfword from the first operand to the corresponding halfword of the second operand.

- 2. Shuffles the result by one bit to the right, halving the data.

- 3. Writes the halfword results in the destination register.

The SHADDB8 instruction:

- 1. Adds each byte of the first operand to the corresponding byte of the second operand.

- 2. Shuffles the result by one bit to the right, halving the data.

- 3. Writes the byte results in the destination register.

#### Restrictions

Do not use SP and do not use PC.

#### **Condition flags**

These instructions do not change the flags.

| SHADD16 R1 | L, R0  |    | Adds halfwords in R0 to corresponding halfword of R1  |

|------------|--------|----|-------------------------------------------------------|

|            |        |    | and writes halved result to corresponding halfword in |

|            |        |    | ; R1.                                                 |

| SHADD8 R4  | 1, R0, | R5 | Adds bytes of R0 to corresponding byte in R5 and      |

|            |        |    | writes halved result to corresponding byte in R4.     |

#### Where:

| cond | Is an optional condition code. See <i>Conditional execution on page 68</i> . |

|------|------------------------------------------------------------------------------|

| Rd   | Is the destination register.                                                 |

| Rn   | Is the first operand register.                                               |

| Rm   | Is the second operand register.                                              |

#### Operation

The USAD8 instruction:

- 1. Subtracts each byte of the second operand register from the corresponding byte of the first operand register.

- 2. Adds the absolute values of the differences together.

- 1. Writes the result to the destination register.

#### Restrictions

Do not use SP and do not use PC.

#### **Condition flags**

These instructions do not change the flags.

### Examples

```

USAD8 R1, R4, R0 ; Subtracts each byte in R0 from corresponding byte

; of R4 adds the differences and writes to R1.

; Subtracts bytes of R5 from corresponding byte in

; R0, adds the differences and writes to R0.

```

# 3.5.23 USADA8

Unsigned Sum of Absolute Differences and Accumulate.

# Syntax

USADA8{cond}{Rd,} Rn, Rm, Ra

Where:

| cond | Is an optional condition code. See Conditional execution on page 68. |  |

|------|----------------------------------------------------------------------|--|

|------|----------------------------------------------------------------------|--|

*Rd* Is the destination register.

- *Rn* Is the first operand register.

- Rm Is the second operand register.

- *Ra* Is the register that contains the accumulation value.

# Operation

The USADA8 instruction:

The MLS instruction multiplies the values from *Rn* and *Rm*, subtracts the product from the value from *Ra*, and places the least significant 32 bits of the result in *Rd*.

The results of these instructions do not depend on whether the operands are signed or unsigned.

#### Restrictions

In these instructions, do not use SP and do not use PC.

If the S suffix is used with the MUL instruction:

- Rd, Rn, and Rm must all be in the range R0 to R7.

- Rd must be the same as Rm.

- The *cond* suffix must not be used.

#### Condition flags

If S is specified, the MUL instruction:

- Updates the N and Z flags according to the result.

- Does not affect the C and V flags.

#### Examples

```

MUL R10, R2, R5 ; Multiply, R10 = R2 x R5

MLA R10, R2, R1, R5 ; Multiply with accumulate, R10 = (R2 x R1) +

; R5

MULS R0, R2, R2 ; Multiply with flag update, R0 = R2 x R2

MULLT R2, R3, R2 ; Conditionally multiply, R2 = R3 x R2

MLS R4, R5, R6, R7 ; Multiply with subtract, R4 = R7 - (R5 x R6)

```

# 3.6.2 UMULL, UMAAL, UMLAL

Unsigned Long Multiply, with optional Accumulate, using 32-bit operands and producing a 64-bit result.

#### Syntax

op{cond} RdLo, RdHi, Rn, Rm

#### Where:

op Is one of: UMULL Unsigne

- UMULL Unsigned Long Multiply.

- UMAAL Unsigned Long Multiply with Accumulate Accumulate.

- UMLAL Unsigned Long Multiply, with Accumulate.

- *cond* Is an optional condition code. See *Conditional execution on page 68*.

- *RdHi*, *RdLo* Are the destination registers. For UMAAL, UMLAL and UMLAL they also hold the accumulating value.

- *Rn*, *Rm* Are registers holding the first and second operands.

# 3.7.2 SSAT16 and USAT16

Signed Saturate and Unsigned Saturate to any bit position for two halfwords.

#### Syntax

| op{cond} H | Rd, #n, Rm                                                                                                                                                     |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Where:     |                                                                                                                                                                |

| op         | Is one of:<br>SSAT16 Saturates a signed halfword value to a signed range.<br>USAT16 Saturates a signed halfword value to an unsigned range.                    |

| cond       | Is an optional condition code. See <i>Conditional execution on page 68</i> .                                                                                   |

| Rd         | Is the destination register.                                                                                                                                   |

| п          | <ul> <li>Specifies the bit position to saturate to:</li> <li><i>n</i> ranges from 1 to 16 for SSAT.</li> <li><i>n</i> ranges from 0 to 15 for USAT.</li> </ul> |

| Rm         | Is the register containing the value to saturate.                                                                                                              |

## Operation

The SSAT16 instruction:

- 1. Saturates two signed 16-bit halfword values of the register with the value to saturate from selected by the bit position in *n*.

- 2. Writes the results as two signed 16-bit halfwords to the destination register.

The USAT16 instruction:

- 1. Saturates two unsigned 16-bit halfword values of the register with the value to saturate from selected by the bit position in *n*.

- 2. Writes the results as two unsigned halfwords in the destination register.

#### Restrictions

Do not use SP and do not use PC.

#### **Condition flags**

These instructions do not affect the condition code flags.

If saturation occurs, these instructions set the Q flag to 1.

```

SSAT16 R7, #9, R2 ; Saturates the top and bottom highwords of R2

; as 9-bit values, writes to corresponding

; halfword of R7.

USAT16NE R0, #13, R5 ; Conditionally saturates the top and bottom

; halfwords of R5 as 13-bit values, writes to

; corresponding halfword of R0.

```

# **Condition flags**

These instructions do not affect the condition code flags.

### Examples

| QASX | R7, R4, R2 | ; Adds top halfword of R4 to bottom halfword of R2, |

|------|------------|-----------------------------------------------------|

|      |            | ; saturates to 16 bits, writes to top halfword of   |

|      |            | ; R7, Subtracts top highword of R2 from bottom      |

|      |            | ; halfword of R4, saturates to 16 bits and writes   |

|      |            | ; to bottom halfword of R7                          |

| QSAX | R0, R3, R5 | ; Subtracts bottom halfword of R5 from top halfword |

|      |            | ; of R3, saturates to 16 bits, writes to top        |

|      |            | ; halfword of R0                                    |

|      |            | ; Adds bottom halfword of R3 to top halfword of R5, |

|      |            | ; saturates to 16 bits, writes to bottom halfword   |

|      |            | ; of RO.                                            |

|      |            |                                                     |

# 3.7.5 QDADD and QDSUB

Saturating Double and Add and Saturating Double and Subtract, signed.

# Syntax

| op{cond} | { <i>Rd</i> }, <i>Rm</i> , <i>Rn</i>                                 |

|----------|----------------------------------------------------------------------|

| Where:   |                                                                      |

| ор       | Is one of:                                                           |

|          | QDADD Saturating Double and Add.                                     |

|          | QDSUB Saturating Double and Subtract.                                |

| cond     | Is an optional condition code. See Conditional execution on page 68. |

| Rd       | Is the destination register.                                         |

| Rm, Rn   | Are registers holding the first and second operands.                 |

# Operation

The QDADD instruction:

- Doubles the second operand value.

- Adds the result of the doubling to the signed saturated value in the first operand.

- Writes the result to the destination register.

The QDSUB instruction:

- Doubles the second operand value.

- Subtracts the doubled value from the signed saturated value in the first operand.

- Writes the result to the destination register.

Both the doubling and the addition or subtraction have their results saturated to the 32-bit signed integer range  $-2^{31} \le 2^{31} - 1$ . If saturation occurs in either operation, it sets the Q flag in the APSR.

# Restrictions

Do not use SP and do not use PC.

DocID028474 Rev 3

# Restrictions

Do not use SP and do not use PC.

# **Condition flags**

These instructions do not affect the condition code flags.

| R7, R4, R2 | ; Adds top halfword of R4 with bottom halfword of R2,  |

|------------|--------------------------------------------------------|

|            | ; saturates to 16 bits, writes to top halfword of R7   |

|            | ; Subtracts top halfword of R2 from bottom halfword of |

|            | ; R4, saturates to 16 bits, writes to bottom halfword  |

|            | ; of R7                                                |

| R0, R3, R5 | ; Subtracts bottom halfword of R5 from top halfword of |

|            | ; R3, saturates to 16 bits, writes to top halfword of  |

|            | ; R0                                                   |

|            | ; Adds bottom halfword of R4 to top halfword of R5     |

|            | ; saturates to 16 bits, writes to bottom halfword of   |

|            | ; R0.                                                  |

|            |                                                        |

# 3.9.2 SBFX and UBFX

Signed Bit Field Extract and Unsigned Bit Field Extract.

## Syntax

SBFX{cond} Rd, Rn, #lsb, #width

UBFX{cond} Rd, Rn, #lsb, #width

#### Where:

| cond  | Is an optional condition code. See Conditional execution on page 68.                               |

|-------|----------------------------------------------------------------------------------------------------|

| Rd    | Is the destination register.                                                                       |

| Rn    | Is the source register.                                                                            |

| lsb   | Is the position of the least significant bit of the bit field. $1sb$ must be in the range 0 to 31. |

| width | Is the width of the bit field and must be in the range 1 to 32-1sb.                                |

# Operation

SBFX extracts a bit field from one register, sign extends it to 32 bits, and writes the result to the destination register.

UBFX extracts a bit field from one register, zero extends it to 32 bits, and writes the result to the destination register.

### Restrictions

Do not use SP and do not use PC.

# **Condition flags**

These instructions do not affect the flags.

| SBFX | R0, | R1,  | #20, | #4  | ; | Extract bit 20 to bit 23 (4 bits) from R1 and  |

|------|-----|------|------|-----|---|------------------------------------------------|

|      |     |      |      |     | ; | sign extend to 32 bits and then write the      |

|      |     |      |      |     | ; | result to RO.                                  |

| UBFX | R8, | R11, | #9,  | #10 | ; | Extract bit 9 to bit 18 (10 bits) from R11 and |

|      |     |      |      |     | ; | zero extend to 32 bits and then write the      |

|      |     |      |      |     | ; | result to R8.                                  |

Other restrictions when using an IT block are:

- A branch or any instruction that modifies the PC must either be outside an IT block or must be the last instruction inside the IT block. These are:

- ADD PC, PC, Rm.

- MOV PC, Rm.

- B, BL, BX, BLX.

- Any LDM, LDR, or POP instruction that writes to the PC.

- TBB and TBH.

- Do not branch to any instruction inside an IT block, except when returning from an exception handler

- All conditional instructions except B*cond* must be inside an IT block. B*cond* can be either outside or inside an IT block but has a larger branch range if it is inside one

- Each instruction inside the IT block must specify a condition code suffix that is either the same or logical inverse as for the other instructions in the block.

The assembler might place extra restrictions on the use of IT blocks, such as prohibiting the use of assembler directives within them.

#### **Condition flags**

This instruction does not change the flags.

#### Example

| ADDSNE         | R2,               | R2,              | #1        | ;<br>;<br>;                             | Next 3 instructions are conditional<br>ANDNE does not update condition flags<br>ADDSNE updates condition flags<br>Conditional move                                             |

|----------------|-------------------|------------------|-----------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | GT<br>R1,         | R0,              |           | ;;;                                     | Convert R0 hex value (0 to 15) into ASCII<br>('0'-'9', 'A'-'F')<br>Next 2 instructions are conditional<br>Convert 0xA -> 'A'<br>Convert 0x0 -> '0'                             |

|                |                   |                  |           |                                         | IT block with only one conditional instruction<br>Increment R1 conditionally                                                                                                   |

| ADDEQ<br>ANDNE | R0,<br>R2,<br>R3, | R1<br>R2,<br>R3, | #10<br>#1 | ;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;; | Next 4 instructions are conditional<br>Conditional move<br>Conditional add<br>Conditional AND<br>Branch instruction can only be used in the last<br>instruction of an IT block |

| IT<br>ADD      | NE<br>R0,         | R0,              |           |                                         | Next instruction is conditional<br>Syntax error: no condition code used in IT block                                                                                            |

DocID028474 Rev 3

### Operation

These instructions:

- 1. Read the source register.

- 2. Round to the nearest integer value in floating-point format using the rounding mode specified by the FPSCR.

- 3. Write the result to the destination register.

- 4. For the VRINTZX instruction only. Generate a floating-point exception if the result is not exact.

# Restrictions

There are no restrictions.

# **Condition flags**

These instructions do not change the flags.

# 3.11.35 VRINTA, VRINTN, VRINTP, VRINTM, VRINTZ

Round a floating-point value to an integer in floating-point format using directed rounding.

# Encoding

VRINT<rmode>.F<32 | 64> <Sd | Dd>, <Sm | Dm>

#### Where:

<Sd/Dd> Is the destination single-precision or double-precision floating-point value. <Sn/Dn>, <Sm/Dm>

Are the operand single-precision or double-precision floating-point values.

#### <rmode> Is one of:

- A Round to nearest ties away.

- M Round to Nearest Even.

- N Round towards Plus Infinity.

- P Round towards Minus Infinity.

- z Round towards Zero.

# Operation

These instructions:

- 1. Read the source register.

- 2. Round to the nearest integer value with a directed rounding mode specified by the instruction.

- 3. Write the result to the destination register.

# Restrictions

These instructions cannot be conditional. These instructions cannot generate an inexact exception even if the result is not exact.

| Bits   | Name Function |                                                                                                                                                                       |  |  |  |  |  |

|--------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| [31:0] | SETPEND       | Interrupt set-pending bits.<br>Write:<br>0: No effect.<br>1: Changes interrupt state to pending.<br>Read:<br>0: Interrupt is not pending.<br>1: Interrupt is pending. |  |  |  |  |  |

Table 43. ISPR bit assignments

Writing 1 to the ISPR bit corresponding to:

- An interrupt that is pending has no effect.

- A disabled interrupt sets the state of that interrupt to pending.

# 4.2.5 Interrupt clear-pending registers

The NVIC\_ICPR0-NCVIC\_ICPR7 registers remove the pending state from interrupts, and show which interrupts are pending. See the register summary in *Table 39 on page 184* for the register attributes.

The bit assignments are:

### Figure 20. ICPR bit assignments

| 31 |  |  |  |              |  |  |  | 0 |  |

|----|--|--|--|--------------|--|--|--|---|--|

|    |  |  |  |              |  |  |  |   |  |

|    |  |  |  | CLRPEND bits |  |  |  |   |  |

|    |  |  |  |              |  |  |  |   |  |

#### Table 44. ICPR bit assignments

| Bits   | Name    | Function                                                                                                                                                                |

|--------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [31:0] | CLRPEND | Interrupt clear-pending bits.<br>Write:<br>0: No effect.<br>1: Removes pending state an interrupt.<br>Read:<br>0: Interrupt is not pending.<br>1: Interrupt is pending. |

Writing 1 to an ICPR bit does not affect the active state of the corresponding interrupt.

#### 4.6.1 **MPU Type register**

The MPU\_TYPE register indicates whether the MPU is present, and if so, how many regions it supports. If the MPU is not present the MPU TYPE register is RAZ. See the register summary in Table 83 for its attributes. The bit assignments are:

| 31       |  | 24 | 23      |  | 16 | 15      |  | 8 | 7 |         | 1    | 0         |

|----------|--|----|---------|--|----|---------|--|---|---|---------|------|-----------|

| Reserved |  |    | IREGION |  |    | DREGION |  |   | R | eserved |      |           |

|          |  |    |         |  |    |         |  |   |   | SEPARA  | ΓE — |           |

|          |  |    |         |  |    |         |  |   |   |         | N    | Sv39697V1 |

|       | Figure 48 | . TYPE bit as | ssignme | ents |  |

|-------|-----------|---------------|---------|------|--|

| 04.00 |           | 10 15         |         | 0 7  |  |

| Bits    | Name     | Function                                                                                                                                                    |

|---------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [31:24] | -        | Reserved.                                                                                                                                                   |

| [23:16] | IREGION  | Indicates the number of supported MPU instruction regions.<br>Always contains 0x00. The MPU memory map is unified and is described<br>by the DREGION field. |

| [15:8]  | DREGION  | Indicates the number of supported MPU data regions:<br>0x08: 8 MPU regions.<br>0x0F: 16 MPU regions.                                                        |

| [7:1]   | -        | Reserved.                                                                                                                                                   |

| [0]     | SEPARATE | Indicates support for unified or separate instruction and date memory maps:<br>0: Unified.                                                                  |

| Tahlo | 81  | TVDE | hit | assignments |

|-------|-----|------|-----|-------------|

| lable | 04. | IIFE | υιι | assignments |

#### 4.6.2 **MPU Control register**

The MPU\_CTRL register:

- Enables the MPU. .

- Enables the default memory map background region.

- Enables use of the MPU when in the hard fault, Non Maskable Interrupt (NMI), and . FAULTMASK escalated handlers.

See the register summary in Table 83 on page 222 for the MPU CTRL attributes. The bit assignments are:

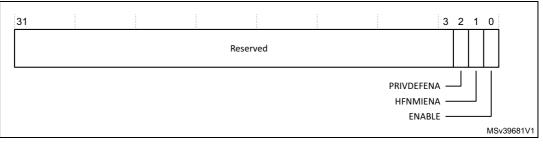

#### Figure 49. MPU\_CTRL bit assignments

| Bits    | Name  | Function                      |  |  |  |  |  |  |

|---------|-------|-------------------------------|--|--|--|--|--|--|

| [25]    | DN    | Default value for FPSCR.DN    |  |  |  |  |  |  |

| [24]    | FZ    | Default value for FPSCR.FZ    |  |  |  |  |  |  |

| [23:22] | RMode | Default value for FPSCR.RMode |  |  |  |  |  |  |

| [21:0]  | -     | Reserved                      |  |  |  |  |  |  |

Table 98. FPDSCR bit assignments (continued)

# 4.7.6 Enabling the FPU

The FPU is disabled from reset. The user must enable it before using any floating-point instructions. *Example 4-1: Enabling the FPU* shows an example code sequence for enabling the FPU in privileged mode. The processor must be in privileged mode to read from and write to the CPACR.

# Example 4-1: Enabling the FPU

| CPACR | EQU 0xE000ED88       |                                              |

|-------|----------------------|----------------------------------------------|

| LDR   | R0, =CPACR           | ; Read CPACR                                 |

| LDR   | r1, [R0]             | ; Set bits 20-23 to enable CP10 and CP11     |

|       |                      | ; coprocessors                               |

| ORR   | R1, R1, #(0xF << 20) |                                              |

| STR   | R1, [R0]             | ; Write back the modified value to the CPACR |

| DSB   |                      |                                              |

| ISB   |                      | ; Reset pipeline now the FPU is enabled.     |

# 4.8 Cache maintenance operations

The cache maintenance operations are only accessible by privileged loads and stores. Unprivileged accesses to these registers always generate a BusFault.

| Address    | Name     | Туре | Required privilege | Reset<br>value | Description                                                                              |

|------------|----------|------|--------------------|----------------|------------------------------------------------------------------------------------------|

| 0xE000EF50 | ICIALLU  | WO   | Privileged         | Unknown        | Instruction cache invalidate all to the <i>Point of Unification</i> (PoU) <sup>(1)</sup> |

| 0xE000EF54 | -        | -    | -                  | -              | Reserved                                                                                 |

| 0xE000EF58 | ICIMVAU  | WO   | Privileged         | Unknown        | Instruction cache invalidate by address to the $PoU^{(1)}$                               |

| 0xE000EF5C | DCIMVAC  | WO   | Privileged         | Unknown        | Data cache invalidate by address to the <i>Point of Coherency</i> (PoC) <sup>(2)</sup>   |

| 0xE000EF60 | DCISW    | WO   | Privileged         | Unknown        | Data cache invalidate by set/way                                                         |

| 0xE000EF64 | DCCMVAU  | WO   | Privileged         | Unknown        | Data cache by address to the PoU <sup>(1)</sup>                                          |

| 0xE000EF68 | DCCMVAC  | WO   | Privileged         | Unknown        | Data cache clean by address to the PoC <sup>(2)</sup>                                    |

| 0xE000EF6C | DCCSW    | WO   | Privileged         | Unknown        | Data cache clean by set/way                                                              |

| 0xE000EF70 | DCCIMVAC | WO   | Privileged         | Unknown        | Data cache clean and invalidate by address to the $PoC^{(2)}$                            |

Table 99. Cache maintenance space register summary