#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                        |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 40MHz                                                                        |

| Connectivity               | CANbus, UART/USART                                                           |

| Peripherals                | POR, PWM, WDT                                                                |

| Number of I/O              | 20                                                                           |

| Program Memory Size        | 16KB (16K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 2K x 8                                                                       |

| RAM Size                   | 512 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                    |

| Data Converters            | A/D 8x10b                                                                    |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 32-LQFP                                                                      |

| Supplier Device Package    | 32-VQFP (7x7)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/t89c51cc02ca-ratim |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Pin Description**

| Pin Name | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VSS      | GND  | Circuit ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VCC      |      | Supply Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VAREF    |      | Reference Voltage for ADC (input)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| VAVCC    |      | Supply Voltage for ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| VAGND    |      | Reference Ground for ADC (internaly connected with the VSS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| P1.0:7   | I/O  | Port 1:         Is an 8-bit bi-directional I/O port with internal pull-ups. Port 1 pins can be used for digital input/output or as analog inputs for the Analog Digital Converter (ADC). Port 1 pins that have 1's written to them are pulled high by the internal pull-up transistors and can be used as inputs in this state. As inputs, Port 1 pins that are being pulled low externally will be the source of current (I <sub>IL</sub> , See section 'Electrical Characteristic') because of the internal pull-ups. Port 1 pins are assigned to be used as analog inputs via the ADCCF register (in this case the internal pull-ups are disconnected).         As a secondary digital function, port 1 contains the Timer 2 external trigger and clock input; the PCA external clock input and the PCA module I/O.         P1.0/AN0/T2         Analog input channel 0,         External clock input and the PCA module I/O.         P1.1/AN1/T2EX         Analog input channel 1,         Trigger input for Timer/counter2.         P1.1/AN1/T2EX         Analog input channel 2,         PCA external clock input.         P1.3/AN3/CEX0         Analog input channel 3,         PCA module 0 Entry of input/PWM output.         P1.3/AN4/CEX1         Analog input channel 4,         PCA module 0 Entry of input/PWM output.         P1.5/AN5         Analog input channel 5,         P1.6/AN6         Analog input channel 6,         P1.7/AN7         Analog input channel |

| P2.0:1   | I/O  | <b>Port 2:</b><br>Is an 2-bit bi-directional I/O port with internal pull-ups. Port 2 pins that have 1's written to them are pulled high by the internal pull-ups and can be used as inputs in this state. As inputs, Port 2 pins that are being pulled low externally will be a source of current (IIL, on the datasheet) because of the internal pull-ups. In the T89C51CC02 Port 2 can sink or source 5mA. It can drive CMOS inputs without external pull-ups.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

#### Table 9. CAN SFRs (Continued)

| Mnemonic    | Add          | Name                                                                             | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|-------------|--------------|----------------------------------------------------------------------------------|---------|---------|---------|---------|---------|---------|---------|---------|

| CANIDM2     | C5h          | C5h CAN Identifier Mask<br>byte 2(PartA)<br>CAN Identifier Mask<br>byte 2(PartB) | IDMSK2  | IDMSK1  | IDMSK0  | -       | -       | -       | -       | -       |

|             |              |                                                                                  | IDMSK20 | IDMSK19 | IDMSK18 | IDMSK17 | IDMSK16 | IDMSK15 | IDMSK14 | IDMSK13 |

| CANIDM3     | Ceb          | C6h CAN Identifier Mask<br>byte 3(PartA)<br>CAN Identifier Mask<br>byte 3(PartB) | -       | -       | -       | -       | -       | -       | -       | -       |

| CANDING     | ANIDINIS Con |                                                                                  | IDMSK12 | IDMSK11 | IDMSK10 | IDMSK9  | IDMSK8  | IDMSK7  | IDMSK6  | IDMSK5  |

|             | C7h          | CAN Identifier Mask byte 4(PartA)                                                | -       | -       | -       | -       | -       | RTRMSK  |         | IDEMSK  |

| CANIDM4 C7h | 0/II         | CAN Identifier Mask byte 4(PartB)                                                | IDMSK4  | IDMSK3  | IDMSK2  | IDMSK1  | IDMSK0  | KINISK  | -       | IDENION |

#### Table 10. Other SFRs

| Mnemonic | Add | Name                 | 7     | 6     | 5      | 4     | 3    | 2     | 1     | 0      |

|----------|-----|----------------------|-------|-------|--------|-------|------|-------|-------|--------|

| PCON     | 87h | Power Control        | SMOD1 | SMOD0 |        | POF   | GF1  | GF0   | PD    | IDL    |

| AUXR1    | A2h | Auxiliary Register 1 |       |       | ENBOOT |       | GF3  | 0     |       | DPS    |

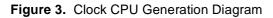

| CKCON    | 8Fh | Clock Control        | CANX2 | WDX2  | PCAX2  | SIX2  | T2X2 | T1X2  | T0X2  | X2     |

| FCON     | D1h | Flash Control        | FPL3  | FPL2  | FPL1   | FPL0  | FPS  | FMOD1 | FMOD0 | FBUSY  |

| EECON    | D2h | EEPROM Contol        | EEPL3 | EEPL2 | EEPL1  | EEPL0 |      |       | EEE   | EEBUSY |

| IIIEL |

|-------|

|       |

| R     |

| Reset Recommendation<br>to Prevent Flash<br>Corruption | When a Flash program memory is embedded on-chip, it is strongly recommended to<br>use an external reset chip (brown out device) to apply a reset (Figure 7). It prevents sys-<br>tem malfunction during periods of insufficient power-supply voltage (power-supply<br>failure, power supply switched off, etc.).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Idle Mode                                              | Idle mode is a power reduction mode that reduces the power consumption. In this mode, program execution halts. Idle mode freezes the clock to the CPU at known states while the peripherals continue to be clocked. The CPU status before entering Idle mode is preserved, i.e., the program counter and program status word register retain their data for the duration of Idle mode. The contents of the SFRs and RAM are also retained. The status of the Port pins during Idle mode is detailed in Table 13.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Entering Idle Mode                                     | To enter Idle mode, set the IDL bit in PCON register (See Table 15). The T89C51CC02<br>enters Idle mode upon execution of the instruction that sets IDL bit. The instruction that<br>sets IDL bit is the last instruction executed.<br>Note: If IDL bit and PD bit are set simultaneously, the T89C51CC02 enters Power-down mode.<br>Then it does not go in Idle mode when exiting Power-down mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| Exiting Idle Mode                                      | <ul> <li>There are two ways to exit Idle mode:</li> <li>1. Generate an enabled interrupt.<br/>Hardware clears IDL bit in PCON register which restores the clock to the CPU. Execution resumes with the interrupt service routine. Upon completion of the interrupt service routine, program execution resumes with the instruction immediately following the instruction that activated Idle mode. The general purpose flags (GF1 and GF0 in PCON register) may be used to indicate whether an interrupt occurred during normal operation or during Idle mode. When Idle mode is exited by an interrupt, the interrupt service routine may examine GF1 and GF0.</li> <li>2. Generate a reset.</li> <li>A logic high on the RST pin clears IDL bit in PCON register directly and asynchronously. This restores the clock to the CPU. Program execution momentarily resumes with the instruction immediately following the instruction that activated the Idle mode and may continue for a number of clock cycles before the internal reset algorithm takes control. Reset initializes the T89C51CC02 and vectors the CPU to address C:0000h.</li> <li>Notes: 1. During the time that execution resumes, the internal RAM cannot be accessed; however, it is possible for the Port pins to be accessed. To avoid unexpected outputs at the Port pins, the instruction immediately following the instruction that activated Idle mode should not write to a Port pin or to the external RAM.</li> <li>2. If Idle mode is invoked by ADC Idle, the ADC conversion completion will exit Idle.</li> </ul> |  |  |  |  |

| Power-down Mode                                        | The Power-down mode places the T89C51CC02 in a very low power state. Power-down mode stops the oscillator, freezes all clock at known states. The CPU status prior to entering Power-down mode is preserved, i.e., the program counter, program status word register retain their data for the duration of Power-down mode. In addition, the SFRs and RAM contents are preserved. The status of the Port pins during Power-down mode is detailed in Table 13.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| Entering Power-down Mode                               | To enter Power-down mode, set PD bit in PCON register. The T89C51CC02 enters the Power-down mode upon execution of the instruction that sets PD bit. The instruction that sets PD bit is the last instruction executed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| EEPROM Data<br>Memory               | The 2K bytes on-chip EEPROM memory block is located at addresses 0000h to 07FFh of the XRAM/XRAM memory space and is selected by setting control bits in the EECON register. A read in the EEPROM memory is done with a MOVX instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                     | A physical write in the EEPROM memory is done in two steps: write data in the column latches and transfer of all data latches into an EEPROM memory row (programming).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                     | The number of data written on the page may vary from 1 up to 128 Bytes (the page size). When programming, only the data written in the column latch is programmed and a ninth bit is used to obtain this feature. This provides the capability to program the whole memory by Bytes, by page or by a number of Bytes in a page. Indeed, each ninth bit is set when the writing the corresponding byte in a row and all these ninth bits are reset after the writing of the complete EEPROM row.                                                                                                                                                                                                                                                                        |

| Write Data in the Column<br>Latches | Data is written by byte to the column latches as for an external RAM memory. Out of the 11 address bits of the data pointer, the 4 MSBs are used for page selection (row) and 7 are used for byte selection. Between two EEPROM programming sessions, all the addresses in the column latches must stay on the same page, meaning that the 4 MSB must no be changed.                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                     | <ul> <li>The following procedure is used to write to the column latches:</li> <li>Save and disable interrupt</li> <li>Set bit EEE of EECON register</li> <li>Load DPTR with the address to write</li> <li>Store A register with the data to be written</li> <li>Execute a MOVX @DPTR, A</li> <li>If needed loop the three last instructions until the end of a 128 Bytes page</li> <li>Restore interrupt</li> <li>Note: The last page address used when loading the column latch is the one used to select the page programming address.</li> </ul>                                                                                                                                                                                                                    |

| Programming                         | <ul> <li>The EEPROM programming consists of the following actions:</li> <li>Write one or more Bytes of one page in the column latches. Normally, all Bytes must belong to the same page; if not, the last page address will be latched and the others discarded.</li> <li>Launch programming by writing the control sequence (50h followed by A0h) to the EECON register.</li> <li>EEBUSY flag in EECON is then set by hardware to indicate that programming is in progress and that the EEPROM segment is not available for reading.</li> <li>The end of programming is indicated by a hardware clear of the EEBUSY flag.</li> <li>Note: The sequence 5xh and Axh must be executed without instructions between then otherwise the programming is aborted.</li> </ul> |

| Read Data                           | <ul> <li>The following procedure is used to read the data stored in the EEPROM memory:</li> <li>Save and disable interrupt</li> <li>Set bit EEE of EECON register</li> <li>Load DPTR with the address to read</li> <li>Execute a MOVX A, @DPTR</li> <li>Restore interrupt</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

### Overview of FM0 The C Operations These

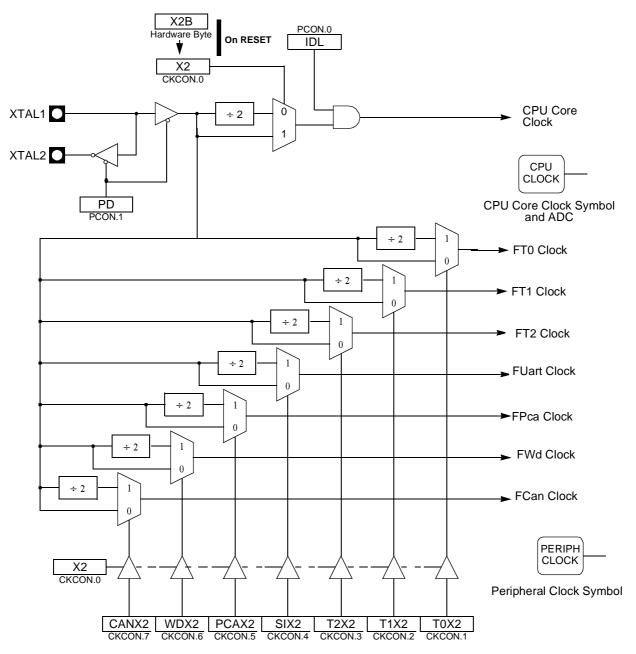

The CPU interfaces the Flash memory through the FCON register and AUXR1 register. These registers are used to:

- Map the memory spaces in the adressable space

- Launch the programming of the memory spaces

- Get the status of the Flash memory (busy/not busy)

Mapping of the Memory Space By default, the user space is accessed by MOVC instruction for read only. The column latches space is made accessible by setting the FPS bit in FCON register. Writing is possible from 0000h to 3FFFh, address bits 6 to 0 are used to select an address within a page while bits 14 to 7 are used to select the programming address of the page. Setting FPS bit takes precedence on the EEE bit in EECON register.

The other memory spaces (user, extra row, hardware security) are made accessible in the code segment by programming bits FMOD0 and FMOD1 in FCON register in accordance with Table 21. A MOVC instruction is then used for reading these spaces.

Table 21. FM0 blocks Select bits

| FMOD1 | FMOD0 | FM0 Adressable Space           |

|-------|-------|--------------------------------|

| 0     | 0     | User (0000h-3FFFh)             |

| 0     | 1     | Extra Row(FF80h-FFFFh)         |

| 1     | 0     | Hardware Security Byte (0000h) |

| 1     | 1     | Reserved                       |

**Launching Programming** FPL3:0 bits in FCON register are used to secure the launch of programming. A specific sequence must be written in these bits to unlock the write protection and to launch the programming. This sequence is 5xh followed by Axh. Table 22 summarizes the memory spaces to program according to FMOD1:0 bits.

Table 22. Programming Spaces

|                  |        | Write to |       |       |                                             |

|------------------|--------|----------|-------|-------|---------------------------------------------|

|                  | FPL3:0 | FPS      | FMOD1 | FMOD0 | Operation                                   |

|                  | 5      | х        | 0     | 0     | No action                                   |

| User             | А      | х        | 0     | 0     | Write the column latches in user space      |

| Extra Row        | 5      | х        | 0     | 1     | No action                                   |

|                  | А      | х        | 0     | 1     | Write the column latches in extra row space |

| Hardware         | 5      | х        | 1     | 0     | No action                                   |

| Security<br>Byte | А      | х        | 1     | 0     | Write the fuse bits space                   |

| Deserved         | 5      | х        | 1     | 1     | No action                                   |

| Reserved         | А      | х        | 1     | 1     | No action                                   |

Note: The sequence 5xh and Axh must be executing without instructions between them otherwise the programming is aborted.

Interrupts that may occur during programming time must be disabled to avoid any spurious exit of the programming mode.

Figure 17. Reading Procedure

Note: aa = 10 for the Hardware Security Byte.

#### Flash Protection from Parallel Programming

The three lock bits in Hardware Security Byte (See 'In-System Programming' section) are programmed according to Table 23 provide different level of protection for the onchip code and data located in FM0 and FM1.

The only way to write this bits are the parallel mode. They are set by default to level 3.

| Program Lock bits |     |     |     |                                                                                                                    |

|-------------------|-----|-----|-----|--------------------------------------------------------------------------------------------------------------------|

| Security<br>Level | LB0 | LB1 | LB2 | Protection Description                                                                                             |

| 1                 | U   | U   | U   | No program lock features enabled. MOVC instruction executed from external program memory returns code data.        |

| 2                 | Р   | U   | U   | Parallel programming of the Flash is disabled.                                                                     |

| 3                 | U   | Р   | U   | Same as 2, also verify through parallel programming interface is disabled. This is the factory defaul programming. |

Table 23. Program Lock bit

U: unprogrammed P: programmed

WARNING: Security level 2 and 3 should only be programmed after Flash and Core verification.

Preventing Flash Corruption See Section "Power Management".

#### **XROW Bytes** The EXTRA ROW (XROW) includes 128 bytes. Some of these bytes are used for specific purpose in conjonction with the bootloader.

| Table 30. | XROW | Mapping |

|-----------|------|---------|

|-----------|------|---------|

| Description                                     | Default Value | Address |

|-------------------------------------------------|---------------|---------|

| Copy of the Manufacturer Code                   | 58h           | 30h     |

| Copy of the Device ID#1: Family code            | D7h           | 31h     |

| Copy of the Device ID#2: Memories size and type | BBh           | 60h     |

| Copy of the Device ID#3: Name and Revision      | FFh           | 61h     |

**Hardware Conditions** It is possible to force the controller to execute the bootloader after a Reset with hardware conditions.

During the first programming, the user can define a configuration on Port1 that will be recognized by the chip as the hardware conditions during a Reset. If this condition is met, the chip will start executing the bootloader at the end of the Reset.

See a detailed description in the applicable Document.

- Datasheet Bootloader CAN T89C51CC02.

- Datasheet Bootloader UART T89C51CC02.

Table 52.WDTRST RegisterWDTRST (S:A6h Write Only) – Watchdog Timer Enable register

| 7             | 6               | 5           | 4            | 3 | 2 | 1 | 0 |

|---------------|-----------------|-------------|--------------|---|---|---|---|

| -             | -               | -           | -            | - | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description |              |   |   |   |   |

| 7             | -               | Watchdog Co | ontrol Value |   |   |   |   |

Reset Value = 1111 1111b

Note: The WDRST register is used to reset/enable the WDT by writing 1EH then E1H in sequence without instruction between these two sequences.

```

// Enable the CAN macro

CANGCON = 0.2h

2. Configure message object 3 in reception to receive only standard (11bit

identifier) message 100h

// Select the message object 3

CANPAGE = 30h

// Enable the interrupt on this message object

CANIE = 08h

// Clear the status and control register

CANSTCH = 00h

CANCONCH= 00h

// Init the acceptance filter to accept only message 100h in standard mode

CANIDT1 = 20h

CANIDT2 = 00h

CANIDT3 = 00h

CANIDT4 = 00h

CANIDM1 = FFh

CANIDM2 = FFh

CANIDM3 = FFh

CANIDM4 = FFh

// Enable channel in reception

CANCONCH = 88h // enable reception

Note: to enable the CAN interrupt in reception:

EA = 1

ECAN = 1

CANGIE = 20h

3. Send a message on the message object 0

// Select the message object 0

CANPAGE = 00h

// Enable the interrupt on this message object

CANIE = 01h

// Clear the Status register

CANSTCH = 00h;

// load the identifier to send (ex: 555h)

CANIDT1 = AAh;

CANIDT2 = A0h;

// load data to send

CANMSG = 00h

CANMSG = 01h

CANMSG = 02h

CANMSG = 03h

CANMSG = 04h

CANMSG = 05h

CANMSG = 06h

CANMSG = 07h

// configure the control register

CANCONCH = 18h

4. Interrupt routine

// Save the current CANPAGE

```

#### Table 60. CANGIE Register

CANGIE (S:C1h) – CAN

| 7        | 6      | 5        | 4                                                                                               | 3                     | 2               | 1               | 0            |

|----------|--------|----------|-------------------------------------------------------------------------------------------------|-----------------------|-----------------|-----------------|--------------|

| -        | -      | ENRX     | ENTX                                                                                            | ENERCH                | ENBUF           | ENERG           | -            |

| Bit Numb | er Bit | Mnemonic | Description                                                                                     |                       |                 |                 |              |

| 7 - 6    |        | -        | <b>Reserved</b><br>The values read from these bits are indeterminate. Do not set these<br>bits. |                       |                 |                 |              |

| 5        |        | ENRX     | <b>Enable Rece</b><br>0 - Disable<br>1 - Enable                                                 | ive Interrupt         |                 |                 |              |

| 4        |        | ENTX     | <b>Enable Tran</b><br>0 - Disable<br>1 - Enable                                                 | smit Interrupt        | :               |                 |              |

| 3        |        | ENERCH   | <b>Enable Mess</b><br>0 - Disable<br>1 - Enable                                                 | sage Object E         | rror Interrup   | t               |              |

| 2        |        | ENBUF    | <b>Enable BUF</b><br>0 - Disable<br>1 - Enable                                                  | Interrupt             |                 |                 |              |

| 1        |        | ENERG    | Enable General Error Interrupt<br>0 - Disable<br>1 - Enable                                     |                       |                 |                 |              |

| 0        |        | -        | <b>Reserved</b><br>The value rea<br>See Figure 3                                                | ad from this bi<br>5. | t is indetermir | nate. Do not se | et this bit. |

Reset Value = xx00 000xb

Table 66.CANBT3 RegisterCANBT3 (S:B6h)CAN bit Timing Registers 3

| 7        | 6       | 5        | 4                                                                                                                                                                                                                                                         | 3      | 2      | 1      | 0   |  |

|----------|---------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|--------|-----|--|

| -        | PHS2 2  | PHS2 1   | PHS2 0                                                                                                                                                                                                                                                    | PHS1 2 | PHS1 1 | PHS1 0 | SMP |  |

| Bit Numb | ber Bit | Mnemonic | Description                                                                                                                                                                                                                                               |        |        |        |     |  |

| 7        |         | -        | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                                                    |        |        |        |     |  |

| 6 - 4    | F       | PHS2 2:0 | Phase Segment 2<br>This phase is used to compensate for phase edge errors. This<br>segment can be shortened by the re-synchronization jump width.<br>Tphs2 = Tscl x (PHS2[20] + 1)                                                                        |        |        |        |     |  |

| 3 - 1    | F       | PHS1 2:0 | Phase Segment 1<br>This phase is used to compensate for phase edge errors. This<br>segment can be lengthened by the re-synchronization jump width.<br>Tphs1 = Tscl x (PHS1[20] + 1)                                                                       |        |        |        |     |  |

| 0        |         | SMP      | Sample Type<br>0 - once, at the sample point.<br>1 - three times, the threefold sampling of the bus is the sample<br>point and twice over a distance of a 1/2 period of the Tscl. The<br>result corresponds to the majority decision of the three values. |        |        |        |     |  |

Note: 1. The CAN controller bit timing registers must be accessed only if the CAN controller is disabled with the ENA bit of the CANGCON register set to 0. See Figure 37.

No default value after reset.

# **Table 78.** CANIDM1 Register for V2.0 part ACANIDM1 for V2.0 part A (S:C4h)CAN Identifier Mask Registers 1

|   | 7        | (   | 6    | 5        | 4                                                                                                            | 3       | 2       | 1       | 0       |

|---|----------|-----|------|----------|--------------------------------------------------------------------------------------------------------------|---------|---------|---------|---------|

| [ | IDMSK 10 | IDM | SK 9 | IDMSK 8  | IDMSK 7                                                                                                      | IDMSK 6 | IDMSK 5 | IDMSK 4 | IDMSK 3 |

| ſ | Bit Numb | er  | Bit  | Vnemonic | Description                                                                                                  |         |         |         |         |

|   | 7 - 0    |     | ID.  | TMSK10:3 | <b>IDentifier Mask Value</b><br>0 - comparison true forced.<br>1 - bit comparison enabled.<br>See Figure 39. |         |         |         |         |

No default value after reset.

**Table 79.** CANIDM2 Register for V2.0 part ACANIDM2 for V2.0 part A (S:C5h)CAN Identifier Mask Registers 2

| 7        | (   | 6    | 5        | 4                              | 3                            | 2 | 1 | 0 |

|----------|-----|------|----------|--------------------------------|------------------------------|---|---|---|

| IDMSK 2  | IDM | SK 1 | IDMSK 0  | -                              | -                            | - | - | - |

| Bit Numb | er  | Bit  | Mnemonic | Description                    |                              |   |   |   |

| 7 5      |     | Ĺ    | TMEKOO   | IDentifier Ma<br>0 - compariso | ask Value<br>on true forced. |   |   |   |

| 7 - 5 | IDTMSK2:0 | 1 - bit comparison enabled.<br>See Figure 39.                                                |

|-------|-----------|----------------------------------------------------------------------------------------------|

| 4 -0  | -         | <b>Reserved</b><br>The values read from these bits are indeterminate. Do not set these bits. |

No default value after reset.

**Table 80.** CANIDM3 Register for V2.0 part ACANIDM3 for V2.0 part A (S:C6h)CAN Identifier Mask Registers 3

| 7        | 6     | 5            | 4 3 2 1 0                                                      |   |   |   |   |

|----------|-------|--------------|----------------------------------------------------------------|---|---|---|---|

| -        | -     | -            | -                                                              | - | - | - | - |

| Bit Numb | ber E | Bit Mnemonic | Description                                                    |   |   |   |   |

| 7 - 0    |       | -            | Reserved<br>The values read from these bits are indeterminate. |   |   |   |   |

No default value after reset.

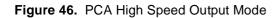

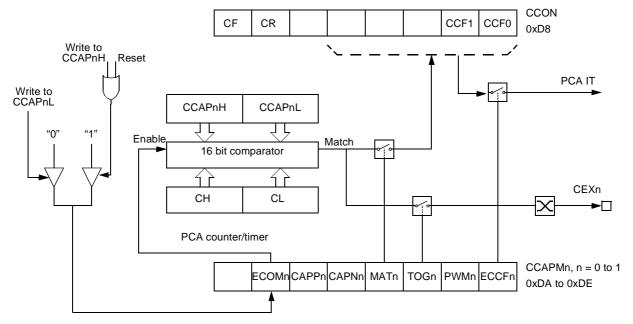

**High Speed Output Mode** In this mode the CEX output (on port 1) associated with the PCA module will toggle each time a match occurs between the PCA counter and the module's capture registers. To activate this mode the TOG, MAT, and ECOM bits in the module's CCAPMn SFR must be set.

#### **Pulse Width Modulator** Mode

All the PCA modules can be used as PWM outputs. The output frequency depends on the source for the PCA timer. All the modules will have the same output frequency because they all share the PCA timer. The duty cycle of each module is independently variable using the module's capture register CCAPLn. When the value of the PCA CL SFR is less than the value in the module's CCAPLn SFR the output will be low, when it is equal to or greater than it, the output will be high. When CL overflows from FF to 00, CCAPLn is reloaded with the value in CCAPHn. the allows the PWM to be updated without glitches. The PWM and ECOM bits in the module's CCAPMn register must be set to enable the PWM mode.

The bits SCH0 to SCH2 in ADCON register are used for the analog input channel selection.

| Fable 101. Selected Analog input | but |  |

|----------------------------------|-----|--|

|----------------------------------|-----|--|

Т

| SCH2 | SCH1 | SCH0 | Selected Analog Input |

|------|------|------|-----------------------|

| 0    | 0    | 0    | ANO                   |

| 0    | 0    | 1    | AN1                   |

| 0    | 1    | 0    | AN2                   |

| 0    | 1    | 1    | AN3                   |

| 1    | 0    | 0    | AN4                   |

| 1    | 0    | 1    | AN5                   |

| 1    | 1    | 0    | AN6                   |

| 1    | 1    | 1    | AN7                   |

**Voltage Conversion** When the ADCIN is equals to VAREF the ADC converts the signal to 3FFh (full scale). If the input voltage equals VAGND, the ADC converts it to 000h. Input voltage between VAREF and VAGND are a straight-line linear conversion. All other voltages will result in 3FFh if greater than VAREF and 000h if less than VAGND.

Note that ADCIN should not exceed VAREF absolute maximum range (See section "AC-DC").

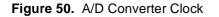

**Clock Selection** The ADC clock is the same as CPU.

The maximum clock frequency is defined in the DC parmeter for A/D converter. A prescaler is featured (ADCCLK) to generate the ADC clock from the oscillator frequency.

f<sub>ADC</sub> = fcpu clock/ (4 (or 2 in X2 mode)\* PRS )

**ADC Standby Mode** When the ADC is not used, it is possible to set it in standby mode by clearing bit ADEN in ADCON register. In this mode the power dissipation is reduced.

**IT ADC management** An interrupt end-of-conversion will occurs when the bit ADEOC is activated and the bit EADC is set. For re-arming the interrupt the bit ADEOC must be cleared by software.

Each of the interrupt sources can be individually enabled or disabled by setting or clearing a bit in the Interrupt Enable register. This register also contains a global disable bit which must be cleared to disable all the interrupts at the same time.

Each interrupt source can also be individually programmed to one of four priority levels by setting or clearing a bit in the Interrupt Priority registers. The Table below shows the bit values and priority levels associated with each combination.

| IPH.x | IPL.x | Interrupt Level Priority |

|-------|-------|--------------------------|

| 0     | 0     | 0 (Lowest)               |

| 0     | 1     | 1                        |

| 1     | 0     | 2                        |

| 1     | 1     | 3 (Highest)              |

Table 107. Priority Level bit Values

A low-priority interrupt can be interrupted by a high priority interrupt but not by another low-priority interrupt. A high-priority interrupt cannot be interrupted by any other interrupt source.

If two interrupt requests of different priority levels are received simultaneously, the request of the higher priority level is serviced. If interrupt requests of the same priority level are received simultaneously, an internal polling sequence determines which request is serviced. Thus within each priority level there is a second priority structure determined by the polling sequence, See Table 108.

| Table 108. | Interrupt | Priority | Within | Level |

|------------|-----------|----------|--------|-------|

|------------|-----------|----------|--------|-------|

| Interrupt Name                  | Interrupt Address Vector | Interrupt Number | Polling Priority |

|---------------------------------|--------------------------|------------------|------------------|

| External interrupt (INT0)       | 0003h                    | 1                | 1                |

| Timer0 (TF0)                    | 000Bh                    | 2                | 2                |

| External interrupt (INT1)       | 0013h                    | 3                | 3                |

| Timer 1 (TF1)                   | 001Bh                    | 4                | 4                |

| PCA (CF or CCFn)                | 0033h                    | 7                | 5                |

| UART (RI or TI)                 | 0023h                    | 5                | 6                |

| Timer 2 (TF2)                   | 002Bh                    | 6                | 7                |

| CAN (Txok, Rxok, Err or OvrBuf) | 003Bh                    | 8                | 8                |

| ADC (ADCI)                      | 0043h                    | 9                | 9                |

| CAN Timer Overflow (OVRTIM)     | 004Bh                    | 10               | 10               |

**Figure 54.** IEN1 Register IEN1 (S:E8h) Interrupt Enable Register

| 7             | 6               | 5                                                                                                                                 | 4                                                                               | 3 | 2    | 1    | 0    |

|---------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---|------|------|------|

| -             | -               | -                                                                                                                                 | -                                                                               |   | ETIM | EADC | ECAN |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                       | Description                                                                     |   |      |      |      |

| 7             | -               | <b>Reserved</b><br>The value rea                                                                                                  | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |   |      |      |      |

| 6             | -               | Reserved<br>The value rea                                                                                                         | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |   |      |      |      |

| 5             | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                   |                                                                                 |   |      |      |      |

| 4             | -               | Reserved<br>The value rea                                                                                                         | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |   |      |      |      |

| 3             | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                   |                                                                                 |   |      |      |      |

| 2             | ETIM            | Timer overrun Interrupt Enable bit<br>Clear to disable the timer overrun interrupt.<br>Set to enable the timer overrun interrupt. |                                                                                 |   |      |      |      |

| 1             | EADC            | ADC Interrupt Enable bit<br>Clear to disable the ADC interrupt.<br>Set to enable the ADC interrupt.                               |                                                                                 |   |      |      |      |

| 0             | ECAN            | CAN Interrupt Enable bit<br>Clear to disable the CAN interrupt.<br>Set to enable the CAN interrupt.                               |                                                                                 |   |      |      |      |

Reset Value = xxxx x000b bit addressable

For timing purposes as port pin is no longer floating when a 100 mV change from load voltage occurs and begins to float when a 100 mV change from the loaded  $V_{OH}/V_{OL}$  level occurs.  $I_{OL}/I_{OH} \ge \pm 20 \text{mA}$ .

**Clock Waveforms**

Valid in normal clock mode. In X2 Mode XTAL2 must be changed to XTAL2/2.

**Flash Memory**

#### Table 119. Memory AC Timing

$V_{cc}$  = 3.0V to 5.5V,  $T_A$  = -40°C to +85°C

| Symbol            | Parameter                              | Min | Тур | Max     | Unit   |

|-------------------|----------------------------------------|-----|-----|---------|--------|

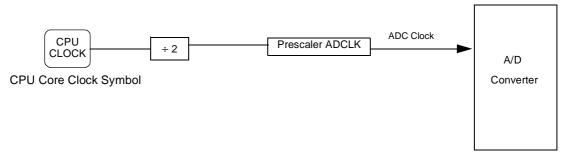

| T <sub>BHBL</sub> | Flash Internal Busy (Programming) Time |     | 13  | 17      | ms     |

| N <sub>FCY</sub>  | Number of Flash Erase/Write Cycles     |     |     | 100 000 | cycles |

| T <sub>FDR</sub>  | Flash Data Retention Time              |     |     | 10      | years  |

Figure 59. Flash Memory - Internal Busy Waveforms

#### A/D Converter

#### Table 120. AC Parameters for A/D Conversion

| Symbol              | Parameter | Min | Тур | Max | Unit |

|---------------------|-----------|-----|-----|-----|------|

| T <sub>SETUP</sub>  |           | 4   |     |     | μs   |

| ADC Clock Frequency |           |     | 700 |     | KHz  |

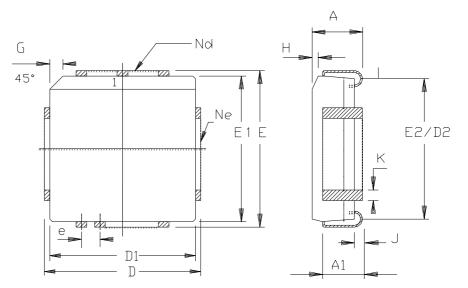

PLCC28

|    | [      |       |       |       |  |

|----|--------|-------|-------|-------|--|

|    | 1      | MM    | INCH  |       |  |

| A  | 4. 20  | 4.57  | . 165 | , 180 |  |

| A1 | 2, 29  | 3.04  | . 090 | . 120 |  |

| D  | 12.32  | 12.57 | . 485 | . 495 |  |

| D1 | 11.43  | 11.58 | . 450 | . 456 |  |

| D2 | 9. 91  | 10.92 | . 390 | . 430 |  |

| E  | 12.32  | 12.57 | . 485 | . 495 |  |

| E1 | 11.43  | 11.58 | . 450 | . 456 |  |

| E5 | 9. 91  | 10.92 | . 390 | . 430 |  |

| e  | 1.27   | BSC   | . 050 | BSC   |  |

| G  | 1.07   | 1.22  | .042  | . 048 |  |

| н  | 1.07   | 1.42  | .042  | . 056 |  |

| J  | 0.51   | -     | . 020 | -     |  |

| К  | 0.33   | 0.53  | . 013 | . 021 |  |

| Nd | 7      |       | 7     |       |  |

| Ne |        | 7     | 7     |       |  |

| P  | KG STD | 00    |       |       |  |

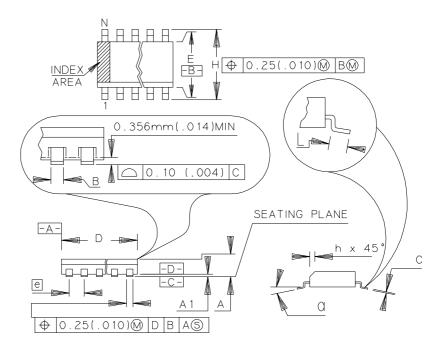

|    | M     | М     | I NCH |       |  |

|----|-------|-------|-------|-------|--|

| A  | 2, 35 | 2.65  | . 093 | . 104 |  |

| A1 | 0.10  | 0.30  | . 004 | . 012 |  |

| В  | 0.35  | 0.49  | . 014 | . 019 |  |

| С  | 0.23  | 0.32  | . 009 | . 013 |  |

| D  | 17.70 | 18.10 | . 697 | . 713 |  |

| E  | 7.40  | 7.60  | . 291 | . 299 |  |

| e  | 1.27  | BSC   | .050  | BSC   |  |

| н  | 10.00 | 10.65 | . 394 | . 419 |  |

| h  | 0.25  | 0.75  | . 010 | . 029 |  |

| L  | 0.40  | 1.27  | .016  | . 050 |  |

| N  | 28    |       | 28    |       |  |

| ۵  | 0 *   |       | 8°    |       |  |