Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                        |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 40MHz                                                                        |

| Connectivity               | CANbus, UART/USART                                                           |

| Peripherals                | POR, PWM, WDT                                                                |

| Number of I/O              | 20                                                                           |

| Program Memory Size        | 16KB (16K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 2K x 8                                                                       |

| RAM Size                   | 512 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                    |

| Data Converters            | A/D 8x10b                                                                    |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 24-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 24-50                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/t89c51cc02ca-tdsim |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P3.0:7   | I/O  | Port 3:         Is an 8-bit bi-directional I/O port with internal pull-ups. Port 3 pins that have 1's written to them are pulled high by the internal pull-up transistors and can be used as inputs in this state. As inputs, Port 3 pins that are being pulled low externally will be a source of current (I <sub>IL</sub> , See section 'Electrical Characteristic') because of the internal pull-ups.         The output latch corresponding to a secondary function must be programmed to one for that function to operate (except for TxD and WR). The secondary functions are assigned to the pins of port 3 as follows: P3.0/RxD: Receiver data input (asynchronous) or data input/output (synchronous) of the serial interface P3.1/TxD: Transmitter data output (asynchronous) or clock output (synchronous) of the serial interface P3.2/INT0: External interrupt 0 input/timer 0 gate control input         P3.3/INT1: External interrupt 1 input/timer 1 gate control input         P3.4/T0: Timer 0 counter input         P3.5/T1: Timer 1 counter input         P3.6: Regular I/O port pin         P3.7: Regular I/O port pin |

| P4.0:1   | I/O  | Port 4:         Is an 2-bit bi-directional I/O port with internal pull-ups. Port 4 pins that have 1's written to them are pulled high by the internal pull-ups and can be used as inputs in this state. As inputs, Port 4 pins that are being pulled low externally will be a source of current (IIL, on the datasheet) because of the internal pull-up transistor.         The output latch corresponding to a secondary function RxDC must be programmed to one for that function to operate. The secondary functions are assigned to the two pins of port 4 as follows:         P4.0/TxDC:         Transmitter output of CAN controller         P4.1/RxDC:         Receiver input of CAN controller.         It can drive CMOS inputs without external pull-ups.                                                                                                                                                                                                                                                                                                                                                                         |

| RESET    | I/O  | <b>Reset:</b><br>A high level on this pin during two machine cycles while the oscillator is running resets the device. An internal pull-down resistor to VSS permits power-on reset using only an external capacitor to VCC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| XTAL1    | I    | <b>XTAL1:</b><br>Input of the inverting oscillator amplifier and input of the internal clock generator circuits. To drive the device from an external clock source, XTAL1 should be driven, while XTAL2 is left unconnected. To operate above a frequency of 16 MHz, a duty cycle of 50% should be maintained.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| XTAL2    | 0    | XTAL2:<br>Output from the inverting oscillator amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| oscrst/vddrst | 1ms   | 10ms  | 100ms |

|---------------|-------|-------|-------|

| 5ms           | 2.7µF | 4.7µF | 47µF  |

| 20ms          | 10µF  | 15µF  | 47µF  |

Table 14. Minimum Reset Capacitor for a 15k Pull-down Resistor

Note: These values assume VDD starts from 0v to the nominal value. If the time between two on/off sequences is too fast, the power-supply decoupling capacitors may not be fully discharged, leading to a bad reset sequence.

#### During a Normal Operation (Warm Reset)

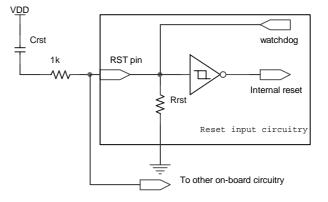

Reset pin must be maintained for at least 2 machine cycles (24 oscillator clock periods) to apply a reset sequence during normal operation. The number of clock periods is mode independent (X2 or X1).

#### Watchdog Reset

A 1K resistor must be added in series with the capacitor to allow the use of watchdog reset pulse output on the RST pin or when an external power-supply supervisor is used. Figure 6 shows the reset circuitry when a capacitor is used.

Figure 6. Reset Circuitry for a Watchdog Configuration

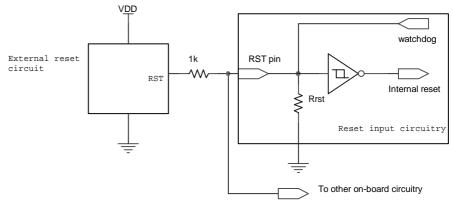

Figure 7 shows the reset circuitry when an external reset circuit is used.

Figure 7. Reset Circuitry Example Using an External Reset Circuit

#### Hardware Security Byte

Table 31.

Hardware Security byte

| 7             | 6               | 5                         | 4                                                                                              | 3                                | 2   | 1             | 0         |  |  |  |  |

|---------------|-----------------|---------------------------|------------------------------------------------------------------------------------------------|----------------------------------|-----|---------------|-----------|--|--|--|--|

| X2B           | BLJB            | -                         | LB2 LB1 LB0                                                                                    |                                  |     |               |           |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description               | Description                                                                                    |                                  |     |               |           |  |  |  |  |

| 7             | X2B             |                           | <b>X2 bit</b><br>Set this bit to start in standard mode<br>Clear this bit to start in X2 Mode. |                                  |     |               |           |  |  |  |  |

| 6             | BLJB            |                           | ne user's app                                                                                  | lication on nex<br>r(@F800h) loo | · · | 000h) located | d in FM0, |  |  |  |  |

| 5 - 3         | -               | Reserved<br>The value rea | Reserved<br>The value read from these bits are indeterminate.                                  |                                  |     |               |           |  |  |  |  |

| 2 - 0         | LB2:0           | Lock bits (see Table 22)  |                                                                                                |                                  |     |               |           |  |  |  |  |

Default value after erasing chip: FFh

Notes: 1. Only the 4 MSB bits can be accessed by software.

2. The 4 LSB bits can only be accessed by parallel mode.

#### Registers

#### Table 32. SCON Register

SCON (S:98h) Serial Control Register

| 7             | 6               | 5                             | 4                                                                                                                                                                                                        | 3                                                    | 2            | 1     | 0  |  |  |  |  |

|---------------|-----------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--------------|-------|----|--|--|--|--|

| FE/SM0        | SM1             | SM2                           | REN                                                                                                                                                                                                      | TB8                                                  | RB8          | ТІ    | RI |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                   | scription                                                                                                                                                                                                |                                                      |              |       |    |  |  |  |  |

| 7             | op bit.         |                               |                                                                                                                                                                                                          |                                                      |              |       |    |  |  |  |  |

|               | SM0             |                               | <b>Iode bit 0 (S</b><br>I for serial por                                                                                                                                                                 | MOD0 = 0)<br>rt mode select                          | on.          |       |    |  |  |  |  |

| 6             | SM1             | -                             | $\begin{array}{c cccc} 0 & 0 & Shift Register & F_{XTAL}/12 \ (or & F_{XTAL}/6 \ in \ mode \ X2) \\ 0 & 1 & 8-bit \ UART & Variable \\ 1 & 0 & 9bit \ UART & F_{XTAL}/64 \ or \ F_{XTAL}/32 \end{array}$ |                                                      |              |       |    |  |  |  |  |

| 5             | SM2             | Clear to disa                 | Serial port Mode 2 bit/Multiprocessor Communication Enable bit<br>Clear to disable multiprocessor communication feature.<br>Set to enable multiprocessor communication feature in mode 2 and 3.          |                                                      |              |       |    |  |  |  |  |

| 4             | REN             |                               | <b>nable bit</b><br>ble serial rece<br>serial recept                                                                                                                                                     | •                                                    |              |       |    |  |  |  |  |

| 3             | TB8             | Clear to trans                | <b>bit 8/Ninth b</b><br>smit a logic 0<br>hit a logic 1 in                                                                                                                                               |                                                      | in Modes 2 a | and 3 |    |  |  |  |  |

| 2             | RB8             | Cleared by h                  | ardware if 9th                                                                                                                                                                                           | Received in M<br>bit received is<br>received is a lo | s a logic 0. | 1     |    |  |  |  |  |

| 1             | ті              | Clear to ackr<br>Set by hardw | Transmit Interrupt Flag<br>Clear to acknowledge interrupt.<br>Set by hardware at the end of the 8th bit time in mode 0 or at the beginning of the<br>stop bit in the other modes.                        |                                                      |              |       |    |  |  |  |  |

| 0             | RI              | Clear to ackr<br>Set by hardw | Receive Interrupt Flag<br>Clear to acknowledge interrupt.<br>Set by hardware at the end of the 8th bit time in mode 0, See Figure 22. and<br>Figure 23. in the other modes.                              |                                                      |              |       |    |  |  |  |  |

Reset Value = 0000 0000b bit addressable

# **Table 36.** PCON RegisterPCON (S:87h)Power Control Register

| 7             | 6               | 5                                              | 4                                                                                                                                                                  | 3                              | 2          | 1  | 0   |  |  |  |  |

|---------------|-----------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------------|----|-----|--|--|--|--|

| SMOD1         | SMOD0           | -                                              | POF                                                                                                                                                                | GF1                            | GF0        | PD | IDL |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                    | escription                                                                                                                                                         |                                |            |    |     |  |  |  |  |

| 7             | SMOD1           |                                                | Serial port Mode bit 1<br>Set to select double baud rate in mode 1, 2 or 3.                                                                                        |                                |            |    |     |  |  |  |  |

| 6             | SMOD0           | Clear to sele                                  | Serial port Mode bit 0<br>Clear to select SM0 bit in SCON register.<br>Set to select FE bit in SCON register.                                                      |                                |            |    |     |  |  |  |  |

| 5             | -               | Reserved<br>The value re                       | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                    |                                |            |    |     |  |  |  |  |

| 4             | POF             | Clear to reco                                  | Power-off Flag<br>Clear to recognize next reset type.<br>Set by hardware when V <sub>CC</sub> rises from 0 to its nominal voltage. Can also be set by<br>software. |                                |            |    |     |  |  |  |  |

| 3             | GF1             |                                                | ser for genera                                                                                                                                                     | al purpose usa<br>rpose usage. | ige.       |    |     |  |  |  |  |

| 2             | GF0             |                                                | ser for generation                                                                                                                                                 | al purpose usa<br>rpose usage. | ige.       |    |     |  |  |  |  |

| 1             | PD              | Cleared by h                                   | Power-down Mode bit<br>Cleared by hardware when reset occurs.<br>Set to enter power-down mode.                                                                     |                                |            |    |     |  |  |  |  |

| 0             | IDL             | Idle Mode b<br>Clear by hard<br>Set to enter i | dware when i                                                                                                                                                       | nterrupt or res                | et occurs. |    |     |  |  |  |  |

Reset Value = 00X1 0000b Not bit addressable

I.

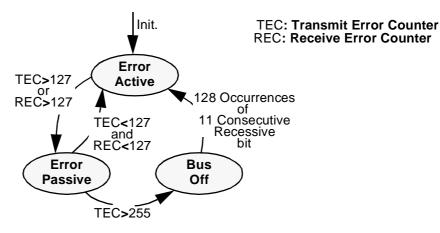

#### **Fault Confinement**

With respect to fault confinement, a unit may be in one of the three following status:

- Error active

- Error passive

- Bus off

An error active unit takes part in bus communication and can send an active error frame when the CAN macro detects an error.

An error passive unit cannot send an active error frame. It takes part in bus communication, but when an error is detected, a passive error frame is sent. Also, after a transmission, an error passive unit will wait before initiating further transmission.

A bus off unit is not allowed to have any influence on the bus.

For fault confinement, two error counters (TEC and REC) are implemented.

See CAN Specification for details on Fault confinement.

#### Figure 38. Line Error Mode

### T89C51CC02

#### CAN SFRs

Table 54. SFR Mapping

|     | 0/8 <sup>(1)</sup>        | 1/9                  | 2/A                               | 3/B                   | 4/C                  | 5/D                  | 6/E                   | 7/F                   |     |

|-----|---------------------------|----------------------|-----------------------------------|-----------------------|----------------------|----------------------|-----------------------|-----------------------|-----|

| F8h | IPL1<br>xxxx x000         | CH<br>0000 0000      | CCAP0H<br>0000 0000               | CCAP1H<br>0000 0000   |                      |                      |                       |                       | FFh |

| F0h | B<br>0000 0000            |                      | ADCLK<br>xxx0 0000                | ADCON<br>x000 0000    | ADDL<br>0000 0000    | ADDH<br>0000 0000    | ADCF<br>0000 0000     | IPH1<br>xxxx x000     | F7h |

| E8h | IEN1<br>xxxx x000         | CL<br>0000 0000      | CCAP0L<br>0000 0000               | CCAP1L<br>0000 0000   |                      |                      |                       |                       | EFh |

| E0h | ACC<br>0000 0000          |                      |                                   |                       |                      |                      |                       |                       | E7h |

| D8h | CCON<br>0000 0000         | CMOD<br>0xxx x000    | CCAPM0<br>x000 0000               | CCAPM1<br>x000 0000   |                      |                      |                       |                       | DFh |

| D0h | PSW<br>0000 0000          | FCON<br>0000 0000    | EECON<br>xxxx xx00                |                       |                      |                      |                       |                       | D7h |

| C8h | <b>T2CON</b><br>0000 0000 | T2MOD<br>xxxx xx00   | RCAP2L<br>0000 0000               | RCAP2H<br>0000 0000   | TL2<br>0000 0000     | TH2<br>0000 0000     |                       | CANEN<br>xxxx 0000    | CFh |

| C0h | P4<br>xxxx xx11           | CANGIE<br>1100 0000  |                                   | CANIE<br>1111 0000    | CANIDM1<br>xxxx xxxx | CANIDM2<br>xxxx xxxx | CANIDM3<br>xxxx xxxx  | CANIDM4<br>xxxx xxxx  | C7h |

| B8h | IPL0<br>x000 0000         | SADEN<br>0000 0000   |                                   | CANSIT<br>xxxx 0000   | CANIDT1<br>xxxx xxxx | CANIDT2<br>xxxx xxxx | CANIDT3<br>xxxx xxxx  | CANIDT4<br>xxxx xxxx  | BFh |

| B0h | P3<br>1111 1111           | CANPAGE<br>1100 0000 | CANSTCH<br>xxxx xxxx              | CANCONCH<br>xxxx xxxx | CANBT1<br>xxxx xxxx  | CANBT2<br>xxxx xxxx  | CANBT3<br>xxxx xxxx   | IPH0<br>x000 0000     | B7h |

| A8h | IEN0<br>0000 0000         | SADDR<br>0000 0000   | CANGSTA<br>1010 0000              | CANGCON<br>0000 0000  | CANTIML<br>0000 0000 | CANTIMH<br>0000 0000 | CANSTMPL<br>xxxx xxxx | CANSTMPH<br>xxxx xxxx | AFh |

| A0h | P2<br>xxxx xx11           | CANTCON<br>0000 0000 | AUXR1 <sup>(2)</sup><br>xxxx 00x0 | CANMSG<br>xxxx xxxx   | CANTTCL<br>0000 0000 | CANTTCH<br>0000 0000 | WDTRST<br>1111 1111   | WDTPRG<br>xxxx x000   | A7h |

| 98h | SCON<br>0000 0000         | SBUF<br>0000 0000    |                                   | CANGIT<br>0x00 0000   | CANTEC<br>0000 0000  | CANREC<br>0000 0000  |                       |                       | 9Fh |

| 90h | P1<br>1111 1111           |                      |                                   |                       |                      |                      |                       |                       | 97h |

| 88h | TCON<br>0000 0000         | TMOD<br>0000 0000    | TL0<br>0000 0000                  | TL1<br>0000 0000      | TH0<br>0000 0000     | TH1<br>0000 0000     |                       | CKCON<br>0000 0000    | 8Fh |

| 80h |                           | SP<br>0000 0111      | DPL<br>0000 0000                  | DPH<br>0000 0000      |                      |                      |                       | PCON<br>00x1 0000     | 87h |

|     | 0/8 <sup>(1)</sup>        | 1/9                  | 2/A                               | 3/B                   | 4/C                  | 5/D                  | 6/E                   | 7/F                   |     |

## Table 58. CANTEC RegisterCANTEC (S:9Ch Read Only) – CAN Transmit Error Counter

| 7        | e                   | 6 | 5        | 4                            | 3    | 2    | 1    | 0    |

|----------|---------------------|---|----------|------------------------------|------|------|------|------|

| TEC7     | TEC7 TEC6           |   | TEC5     | TEC4                         | TEC3 | TEC2 | TEC1 | TEC0 |

| Bit Numb | Bit Number Bit Mnen |   | Vnemonic | Description                  |      |      |      |      |

| 7 - 0    | 7 - 0               |   | TEC7:0   | Transmit Err<br>See Figure 3 |      |      |      |      |

Reset Value = 00h

## Table 59. CANREC RegisterCANREC (S:9Dh Read Only) – CAN Reception Error Counter

| 7        | (                       | 6 | 5           | 4                           | 3                 | 2    | 1    | 0    |

|----------|-------------------------|---|-------------|-----------------------------|-------------------|------|------|------|

| REC7     | C7 REC6                 |   | REC5        | REC4                        | REC3              | REC2 | REC1 | REC0 |

| Bit Numb | Bit Number Bit Mnemonic |   | Description |                             |                   |      |      |      |

| 7 - 0    | 7 - 0                   |   | REC7:0      | Reception E<br>See Figure 3 | rror Counter<br>8 |      |      |      |

Reset Value = 00h

#### Table 63. CANIE Register

CANIE (S:C3h) – CAN Enable Interrupt message object Registers 2

| 7          | 6                                                                                      | 5        | 4                                                                                                                                       | 3           | 2      | 1      | 0             |  |  |  |

|------------|----------------------------------------------------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------|--------|--------|---------------|--|--|--|

| -          | -                                                                                      | -        | -                                                                                                                                       | IECH 3      | IECH 2 | IECH 1 | IECH 0        |  |  |  |

| Bit Number | Bit                                                                                    | Vnemonic | Description                                                                                                                             | Description |        |        |               |  |  |  |

| 7 - 4      | - Reserved<br>- The values read from these bits are indeterminate. Do not set<br>bits. |          |                                                                                                                                         |             |        |        | not set these |  |  |  |

| 3 - 0      | I                                                                                      | ECH3:0   | Enable Interrupt by Message Object<br>0 - disable IT.<br>1 - enable IT.<br>IECH3:0 = 0b 0000 1100 -> Enable IT's of message objects 3 & |             |        |        |               |  |  |  |

Reset Value = xxxx 0000b

Table 64. CANBT1 RegisterCANBT1 (S:B4h) – CAN bit Timing Registers 1

| 7        | 6            | 5               | 4                                                                                      | 3            | 2                            | 1                                         | 0 |  |  |

|----------|--------------|-----------------|----------------------------------------------------------------------------------------|--------------|------------------------------|-------------------------------------------|---|--|--|

| -        | BRP 5        | BRP 4           | BRP 3                                                                                  | BRP 2        | BRP 1                        | BRP 0                                     | - |  |  |

| Bit Numb | er Bitl      | Mnemonic        | Description                                                                            |              |                              |                                           |   |  |  |

| 7        |              | t is indetermir | ate. Do not se                                                                         | et this bit. |                              |                                           |   |  |  |

| 6 - 1    | 6 - 1 BRP5:0 |                 |                                                                                        |              | ines the indivi<br>BRP[50] - | n clock Tscl is<br>dual bit timing<br>+ 1 |   |  |  |

| 0        |              | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit. |              |                              |                                           |   |  |  |

Note: 1. The CAN controller bit timing registers must be accessed only if the CAN controller is disabled with the ENA bit of the CANGCON register set to 0. See Figure 37.

No default value after reset.

## **Table 78.** CANIDM1 Register for V2.0 part ACANIDM1 for V2.0 part A (S:C4h)CAN Identifier Mask Registers 1

|   | 7          | (   | 6    | 5        | 4                                                                      | 3                                | 2       | 1       | 0       |

|---|------------|-----|------|----------|------------------------------------------------------------------------|----------------------------------|---------|---------|---------|

| [ | IDMSK 10   | IDM | SK 9 | IDMSK 8  | IDMSK 7                                                                | IDMSK 6                          | IDMSK 5 | IDMSK 4 | IDMSK 3 |

| ſ | Bit Number |     | Bit  | Vnemonic | Description                                                            |                                  |         |         |         |

|   | 7 - 0      |     | ID.  | TMSK10:3 | <b>IDentifier Ma</b><br>0 - compariso<br>1 - bit compa<br>See Figure 3 | on true forced.<br>rison enabled |         |         |         |

No default value after reset.

**Table 79.** CANIDM2 Register for V2.0 part ACANIDM2 for V2.0 part A (S:C5h)CAN Identifier Mask Registers 2

| 7        | 6    | ;     | 5        | 4                              | 3 | 2 | 1 | 0 |

|----------|------|-------|----------|--------------------------------|---|---|---|---|

| IDMSK 2  | IDMS | SK 1  | IDMSK 0  | -                              | - | - | - | - |

| Bit Numb | ber  | Bit I | Vnemonic | Description                    |   |   |   |   |

| 7 5      |      | חו    | TMSK20   | IDentifier Ma<br>0 - compariso |   |   |   |   |

| 7 - 5 | IDTMSK2:0 | 1 - bit comparison enabled.<br>See Figure 39.                                                   |

|-------|-----------|-------------------------------------------------------------------------------------------------|

| 4 -0  | -         | <b>Reserved</b><br>The values read from these bits are indeterminate. Do not set these<br>bits. |

No default value after reset.

**Table 80.** CANIDM3 Register for V2.0 part ACANIDM3 for V2.0 part A (S:C6h)CAN Identifier Mask Registers 3

| 7        | 6       | 5        | 4                         | 3              | 2               | 1           | 0 |

|----------|---------|----------|---------------------------|----------------|-----------------|-------------|---|

| -        | -       | -        | -                         | -              | -               | -           | - |

| Bit Numb | ber Bit | Mnemonic | Description               |                |                 |             |   |

| 7 - 0    |         | -        | Reserved<br>The values re | ead from these | e bits are inde | eterminate. |   |

No default value after reset.

**Table 81.** CANIDM4 Register for V2.0 part ACANIDM4 for V2.0 part A (S:C7h)CAN Identifier Mask Registers 4

| 7        | 6      | 5        | 4                                         | 3                                                | 2                | 1               | 0             |

|----------|--------|----------|-------------------------------------------|--------------------------------------------------|------------------|-----------------|---------------|

| -        | -      | -        | -                                         | -                                                | RTRMSK           | -               | IDEMSK        |

| Bit Numb | er Bit | Mnemonic | Description                               |                                                  |                  |                 |               |

| 7 - 3    |        | -        | <b>Reserved</b><br>The values re<br>bits. | ead from these                                   | e bits are indet | erminate. Do    | not set these |

| 2        |        | RTRMSK   | 0 - compariso                             | smission req<br>on true forced<br>rison enabled  |                  | alue            |               |

| 1        |        | -        | <b>Reserved</b><br>The value rea          | ad from this bi                                  | t is indetermir  | nate. Do not se | et this bit.  |

| 0        |        | IDEMSK   | 0 - compariso                             | tension Masl<br>on true forced.<br>rison enabled |                  |                 |               |

Note: The ID Mask is only used for reception.

No default value after reset.

**Table 82.** CANIDM1 Register for V2.0 Part BCANIDM1 for V2.0 Part B (S:C4h)CAN Identifier Mask Registers 1

| 7        | 6    | i     | 5        | 4           | 3                                | 2        | 1        | 0        |

|----------|------|-------|----------|-------------|----------------------------------|----------|----------|----------|

| IDMSK 28 | IDMS | K 27  | IDMSK 26 | IDMSK 25    | IDMSK 24                         | IDMSK 23 | IDMSK 22 | IDMSK 21 |

| Bit Numb | er   | Bit I | Vnemonic | Description |                                  |          |          |          |

| 7 - 0    |      | IDI   | MSK28:21 | •           | on true forced.<br>rison enabled |          |          |          |

Note: The ID Mask is only used for reception.

No default value after reset.

**Table 90.** CANSTMPH RegisterCANSTMPH (S:AFh Read Only)CAN Stamp Timer High

|   | 7             | (  | 6         | 5             | 4                         | 3             | 2             | 1         | 0         |

|---|---------------|----|-----------|---------------|---------------------------|---------------|---------------|-----------|-----------|

|   | TIMSTMP<br>15 |    | STMP<br>4 | TIMSTMP<br>13 | TIMSTMP<br>12             | TIMSTMP<br>11 | TIMSTMP<br>10 | TIMSTMP 9 | TIMSTMP 8 |

| ſ | Bit Numb      | er | Bit       | Mnemonic      | Description               |               |               |           |           |

|   | 7 - 0         |    | TIM       | ISTMP15:8     | High byte of See Figure 4 | •             |               |           |           |

No default value after reset

**Table 91.** CANSTMPL RegisterCANSTMPL (S:AEh Read Only)CAN Stamp Timer Low

| 7         | 6       | 5             | 4                        | 3         | 2         | 1         | 0         |

|-----------|---------|---------------|--------------------------|-----------|-----------|-----------|-----------|

| TIMSTMP 7 | TIMSTMF | P 6 TIMSTMP 5 | TIMSTMP 4                | TIMSTMP 3 | TIMSTMP 2 | TIMSTMP 1 | TIMSTMP 0 |

| Bit Numb  | er E    | Bit Mnemonic  | Description              |           |           |           |           |

| 7 - 0     |         | TIMSTMP7:0    | Low byte of See Figure 4 | •         |           |           |           |

No default value after reset

## **Table 92.** CANTTCH RegisterCANTTCH (S:A5h Read Only)CAN TTC Timer High

| 7         | 6         | 5         | 4         | 3         | 2         | 1        | 0        |

|-----------|-----------|-----------|-----------|-----------|-----------|----------|----------|

| TIMTTC 15 | TIMTTC 14 | TIMTTC 13 | TIMTTC 12 | TIMTTC 11 | TIMTTC 10 | TIMTTC 9 | TIMTTC 8 |

| Bit Number | Bit Mnemonic | Description                              |

|------------|--------------|------------------------------------------|

| 7 - 0      | TIMTTC15:8   | High byte of TTC Timer<br>See Figure 40. |

Reset Value = 0000 0000b

## **Table 93.** CANTTCL RegisterCANTTCL (S:A4h Read Only)CAN TTC Timer Low

| 7        | (    | 6     | 5        | 4                           | 3        | 2        | 1        | 0        |

|----------|------|-------|----------|-----------------------------|----------|----------|----------|----------|

| TIMTTC 7 | ТІМТ | TC 6  | TIMTTC 5 | TIMTTC 4                    | TIMTTC 3 | TIMTTC 2 | TIMTTC 1 | TIMTTC 0 |

| Bit Numb | er   | Bit I | Inemonic | Description                 |          |          |          |          |

| 7 - 0    |      | TI    | MTTC7:0  | Low Byte of<br>See Figure 4 |          |          |          |          |

Reset Value = 0000 0000b

Table 96. CCAPnH Registers

CCAP0H (S:FAh) CCAP1H (S:FBh) PCA High Byte Compare/Capture Module n Register (n=0..1)

| 7        | 6        | 5        | 4           | 3        | 2        | 1        | 0        |

|----------|----------|----------|-------------|----------|----------|----------|----------|

| CCAPnH 7 | CCAPnH 6 | CCAPnH 5 | CCAPnH 4    | CCAPnH 3 | CCAPnH 2 | CCAPnH 1 | CCAPnH 0 |

| Bit Numb | oer Bit  | Mnemonic | Description |          |          |          |          |

|--|

Reset Value = 0000 0000b

Table 97. CCAPnL Registers

CCAP0L (S:EAh) CCAP1L (S:EBh) PCA Low Byte Compare/Capture Module n Register (n=0..1)

| 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0        |

|----------|----------|----------|----------|----------|----------|----------|----------|

| CCAPnL 7 | CCAPnL 6 | CCAPnL 5 | CCAPnL 4 | CCAPnL 3 | CCAPnL 2 | CCAPnL 1 | CCAPnL 0 |

|          |          |          |          |          |          |          |          |

| Bit Number | Bit Mnemonic | Description                                      |

|------------|--------------|--------------------------------------------------|

| 7:0        | CCAPnL 7:0   | Low byte of EWC-PCA comparison or capture values |

Reset Value = 0000 0000b

| Analog-to-Digital<br>Converter (ADC) | This section describes the on-chip 10-bit analog-to-digital converter of the T89C51CC02. Eight ADC channels are available for sampling of the external sources AN0 to AN7. An analog multiplexer allows the single ADC converter to select one from the 8 ADC channels as ADC input voltage (ADCIN). ADCIN is converted by the 10-bit-cascaded potentiometric ADC.                                                                                                                                                                         |  |  |  |  |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                      | Two modes of conversion are available:<br>- Standard conversion (8 bits).<br>- Precision conversion (10 bits).                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|                                      | For the precision conversion, set bit PSIDLE in ADCON register and start conversion.<br>The device is in a pseudo-idle mode, the CPU does not run but the peripherals are<br>always running. This mode allows digital noise to be as low as possible, to ensure high<br>precision conversion.                                                                                                                                                                                                                                              |  |  |  |  |

|                                      | For this mode it is necessary to work with end of conversion interrupt, which is the only way to wake the device up.                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|                                      | If another interrupt occurs during the precision conversion, it will be served only after this conversion is completed.                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Features                             | <ul> <li>8 channels with multiplexed inputs</li> <li>10-bit cascaded potentiometric ADC</li> <li>Conversion time 16 micro-seconds (typ.)</li> <li>Zero Error (offset) ± 2 LSB max</li> <li>Positive External Reference Voltage Range (VAREF) 2.4 to 3.0-volt (typ.)</li> <li>ADCIN Range 0 to 3-volt</li> <li>Integral non-linearity typical 1 LSB, max. 2 LSB</li> <li>Differential non-linearity typical 0.5 LSB, max. 1 LSB</li> <li>Conversion Complete Flag or Conversion Complete Interrupt</li> <li>Selectable ADC Clock</li> </ul> |  |  |  |  |

| ADC Port1 I/O Functions              | Port 1 pins are general I/O that are shared with the ADC channels. The channel select bit in ADCF register define which ADC channel/port1 pin will be used as ADCIN. The remaining ADC channels/port1 pins can be used as general purpose I/O or as the alternate function that is available.                                                                                                                                                                                                                                              |  |  |  |  |

|                                      | A conversion launched on a channel which are not selected on ADCF register will not have any effect.                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| VAREF                                | VAREF should be connected to a low impedance point and must remain in the range specified VAREF absolute maximum range (See section "AC-DC").                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|                                      | . If the ADC is not used, it is recommended to tie VAREF to VAGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

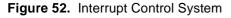

#### **Interrupt System**

#### Introduction

The CAN Controller has a total of 10 interrupt vectors: two external interrupts ( $\overline{INT0}$  and  $\overline{INT1}$ ), three timer interrupts (timers 0, 1 and 2), a serial port interrupt, a PCA, a CAN interrupt, a timer overrun interrupt and an ADC. These interrupts are shown below.

Table 112.IPH1 RegisterIPH1 (S:F7h)Interrupt high priority Register 1

| 7             | 6               | 5                        | 4                                                                               | 3                | 2              | 1            | 0     |  |

|---------------|-----------------|--------------------------|---------------------------------------------------------------------------------|------------------|----------------|--------------|-------|--|

| -             | -               | -                        | -                                                                               |                  | POVRH          | PADCH        | PCANH |  |

| Bit<br>Number | Bit<br>Mnemonic | Description              |                                                                                 |                  |                |              |       |  |

| 7             | -               | Reserved<br>The value re | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                  |                |              |       |  |

| 6             | -               | Reserved<br>The value re | ad from this b                                                                  | oit is indetermi | nate. Do not s | et this bit. |       |  |

| 5             | -               | Reserved<br>The value re | ad from this b                                                                  | oit is indetermi | nate. Do not s | et this bit. |       |  |

| 4             | -               | Reserved<br>The value re | ad from this b                                                                  | oit is indetermi | nate. Do not s | et this bit. |       |  |

| 3             | -               | Reserved<br>The value re | ad from this b                                                                  | oit is indetermi | nate. Do not s | et this bit. |       |  |

| 2             | POVRH           |                          | un Interrupt<br>OVRLPriorit<br>0 Lowest<br>1<br>0<br>1 Highest                  |                  | l Most Signifi | cant bit     |       |  |

| 1             | PADCH           | PADCH PA<br>0<br>0<br>1  | pt Priority Lo<br>A <u>DCL Priority</u><br>0 Lowest<br>1<br>0<br>1 Highest      |                  | nificant bit   |              |       |  |

| 0             | PCANH           |                          | pt Priority Lo<br>CANLPriorit<br>0 Lowest<br>1<br>0<br>1 Highest                | -                | nificant bit   |              |       |  |

Reset Value = XXXX X000b

#### **AC Parameters**

Serial Port Timing - Shift Register Mode

#### **Table 115.** Symbol Description (F = 40 MHz)

| Symbol            | Parameter                                |

|-------------------|------------------------------------------|

| T <sub>XLXL</sub> | Serial port clock cycle time             |

| T <sub>QVHX</sub> | Output data set-up to clock rising edge  |

| T <sub>XHQX</sub> | Output data hold after clock rising edge |

| T <sub>XHDX</sub> | Input data hold after clock rising edge  |

| T <sub>XHDV</sub> | Clock rising edge to input data valid    |

#### Table 116. AC Parameters for a Fix Clock (F = 40 MHz)

| Symbol            | Min | Мах | Units |

|-------------------|-----|-----|-------|

| T <sub>XLXL</sub> | 300 |     | ns    |

| T <sub>QVHX</sub> | 200 |     | ns    |

| T <sub>XHQX</sub> | 30  |     | ns    |

| T <sub>XHDX</sub> | 0   |     | ns    |

| T <sub>XHDV</sub> |     | 117 | ns    |

#### Table 117. AC Parameters for a Variable Clock

| Symbol            | Туре | Standard<br>Clock | X2 Clock | x parameter<br>for -M range | Units |

|-------------------|------|-------------------|----------|-----------------------------|-------|

| T <sub>XLXL</sub> | Min  | 12 T              | 6 T      |                             | ns    |

| T <sub>QVHX</sub> | Min  | 10 T - x          | 5 T - x  | 50                          | ns    |

| T <sub>XHQX</sub> | Min  | 2 T - x           | T - x    | 20                          | ns    |

| T <sub>XHDX</sub> | Min  | х                 | х        | 0                           | ns    |

| T <sub>XHDV</sub> | Max  | 10 T - x          | 5 T- x   | 133                         | ns    |

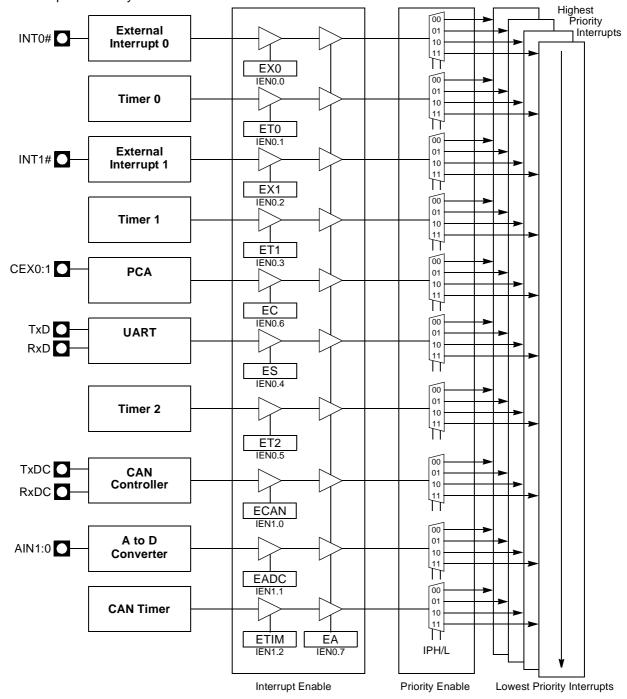

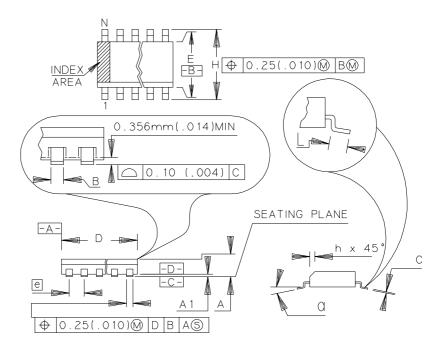

### Package Drawings

#### VQFP32

|    | м        | M        | INCH     |        |  |

|----|----------|----------|----------|--------|--|

|    | Min      | Max      | Min      | Max    |  |

| A  | I        | 1.60     | _        | . 063  |  |

| A1 | 0.05     | 0.15     | . 002    | .006   |  |

| A2 | 1.35     | 1.45     | . 053    | . 057  |  |

| С  | 0.09     | 0,20     | . 004    | . 008  |  |

| D  | 9.00 BSC |          | .354 BSC |        |  |

| D1 | 7.00 BSC |          | .276 BSC |        |  |

| E  | 9.00 BSC |          | .354 BSC |        |  |

| E1 | 7.00     | 7.00 BSC |          | BSC    |  |

| L  | 0.45     | 0.75     | . 018    | . 030  |  |

| е  | 0.80 BSC |          | . 03     | 15 BSC |  |

| b  | 0.30     | 0.45     | . 012    | . 018  |  |

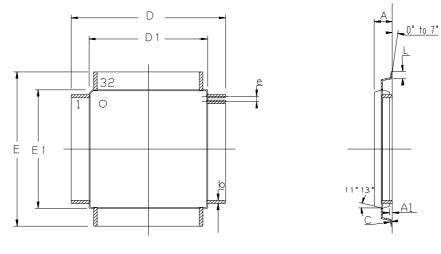

### T89C51CC02

SOIC24

|    | М     | M     | ΙN    | СН    |

|----|-------|-------|-------|-------|

| A  | 2.35  | 2.65  | . 093 | . 104 |

| A1 | 0.10  | 0.30  | . 004 | . 012 |

| В  | 0.35  | 0.49  | . 014 | .019  |

| С  | 0.23  | 0.32  | .009  | . 013 |

| D  | 15.20 | 15.60 | . 599 | . 614 |

| E  | 7.40  | 7.60  | . 291 | . 299 |

| e  | 1.27  | BZC   | .050  | BSC   |

| н  | 10.00 | 10.65 | . 394 | . 419 |

| h  | 0.25  | 0.75  | . 010 | . 029 |

| L  | 0.40  | 1.27  | . 016 | . 050 |

| N  | 24    |       |       | 24    |

| ۵  |       | 0°    | 8°    |       |

|    | M     | М     | IN    | СН    |

|----|-------|-------|-------|-------|

| A  | 2, 35 | 2.65  | . 093 | . 104 |

| A1 | 0.10  | 0.30  | . 004 | . 012 |

| В  | 0.35  | 0.49  | . 014 | . 019 |

| С  | 0.23  | 0.32  | . 009 | . 013 |

| D  | 17.70 | 18.10 | . 697 | . 713 |

| E  | 7.40  | 7.60  | . 291 | . 299 |

| e  | 1.27  | BSC   | .050  | BSC   |

| н  | 10.00 | 10.65 | . 394 | . 419 |

| h  | 0.25  | 0.75  | . 010 | . 029 |

| L  | 0.40  | 1.27  | . 016 | . 050 |

| N  | 28    |       |       | 28    |

| ۵  |       | 0°    |       | 8°    |