Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | 8051                                                                         |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 40MHz                                                                        |

| Connectivity               | CANbus, UART/USART                                                           |

| Peripherals                | POR, PWM, WDT                                                                |

| Number of I/O              | 20                                                                           |

| Program Memory Size        | 16KB (16K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 2K x 8                                                                       |

| RAM Size                   | 512 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                    |

| Data Converters            | A/D 8x10b                                                                    |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C                                                                 |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-LCC (J-Lead)                                                              |

| Supplier Device Package    | 28-PLCC (11.51x11.51)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/t89c51cc02ua-6ksim |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Read-Modify-Write Instructions

Some instructions read the latch data rather than the pin data. The latch based instructions read the data, modify the data and then rewrite the latch. These are called 'Read-Modify-Write' instructions. Below is a complete list of these special instructions (See Table 1). When the destination operand is a Port or a Port bit, these instructions read the latch rather than the pin:

Table 1. Read/Modify/Write Instructions

| Instruction | Description                       | Example         |  |  |

|-------------|-----------------------------------|-----------------|--|--|

| ANL         | Logical AND                       | ANL P1, A       |  |  |

| ORL         | Logical OR                        | ORL P2, A       |  |  |

| XRL         | Logical EX-OR                     | XRL P3, A       |  |  |

| JBC         | Jump if bit = 1 and clear bit     | JBC P1.1, LABEL |  |  |

| CPL         | Complement bit                    | CPL P3.0        |  |  |

| INC         | Increment                         | INC P2          |  |  |

| DEC         | Decrement                         | DEC P2          |  |  |

| DJNZ        | Decrement and jump if not zero    | DJNZ P3, LABEL  |  |  |

| MOV Px.y, C | Move carry bit to bit y of Port x | MOV P1.5, C     |  |  |

| CLR Px.y    | Clear bit y of Port x             | CLR P2.4        |  |  |

| SET Px.y    | Set bit y of Port x               | SET P3.3        |  |  |

It is not obvious that the last three instructions in this list are Read-Modify-Write instructions. These instructions read the port (all 8 bits), modify the specifically addressed bit and write the new byte back to the latch. These Read-Modify-Write instructions are directed to the latch rather than the pin in order to avoid possible misinterpretation of voltage (and therefore, logic) levels at the pin. For example, a Port bit used to drive the base of an external bipolar transistor cannot rise above the transistor's base-emitter junction voltage (a value lower than VIL). With a logic one written to the bit, attempts by the CPU to read the Port at the pin are misinterpreted as logic zero. A read of the latch rather than the pins returns the correct logic one value.

**Quasi Bi-directional Port Operation** Port 1, Port 3 and Port 4 have fixed internal pull-ups and are referred to as 'quasi-bidirectional' Ports. When configured as an input, the pin impedance appears as logic one and sources current in response to an external logic zero condition. Resets write logic one to all Port latches. If logical zero is subsequently written to a Port latch, it can be returned to input conditions by a logic one written to the latch.

> Note: Port latch values change near the end of Read-Modify-Write insruction cycles. Output buffers (and therefore the pin state) are updated early in the instruction after Read-Modify-Write instruction cycle.

> Logical zero-to-one transitions in Port 1, Port 3 and Port 4 use an additional pull-up (p1) to aid this logic transition See Figure 2. This increases switch speed. This extra pull-up sources 100 times normal internal circuit current during 2 oscillator clock periods. The internal pull-ups are field-effect transistors rather than linear resistors. Pull-ups consist of three p-channel FET (pFET) devices. A pFET is on when the gate senses logic zero and off when the gate senses logic one. pFET #1 is turned on for two oscillator periods immediately after a zero-to-one transition in the Port latch. A logic one at the Port pin turns on pFET #3 (a weak pull-up) through the inverter. This inverter and pFET pair form a latch to drive logic one. pFET #2 is a very weak pull-up switched on whenever the

|             | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock       | <ul> <li>The T89C51CC02 core needs only 6 clock periods per machine cycle. This feature, called "X2", provides the following advantages:</li> <li>Divides frequency crystals by 2 (cheaper crystals) while keeping the same CPU power.</li> <li>Saves power consumption while keeping the same CPU power (oscillator power saving).</li> <li>Saves power consumption by dividing dynamic operating frequency by 2 in operating and idle modes.</li> <li>Increases CPU power by 2 while keeping the same crystal frequency.</li> </ul> |

|             | In order to keep the original C51 compatibility, a divider-by-2 is inserted between the XTAL1 signal and the main clock input of the core (phase generator). This divider may be disabled by the software.                                                                                                                                                                                                                                                                                                                            |

|             | An extra feature is available to start after Reset in the X2 Mode. This feature can be<br>enabled by a bit X2B in the Hardware Security Byte. This bit is described in the section<br>'In-System Programming'.                                                                                                                                                                                                                                                                                                                        |

| Description | The X2 bit in the CKCON register (See Table 12) allows switching from 12 clock cycles per instruction to 6 clock cycles and vice versa. At reset, the standard speed is activated (STD mode).                                                                                                                                                                                                                                                                                                                                         |

|             | Setting this bit activates the X2 feature (X2 Mode) for the CPU Clock only (See Figure 3).                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|             | The Timers 0, 1 and 2, Uart, PCA, watchdog or CAN switch in X2 Mode only if the corre-<br>sponding bit is cleared in the CKCON register.                                                                                                                                                                                                                                                                                                                                                                                              |

|             | The clock for the whole circuit and peripheral is first divided by two before being used by the CPU core and peripherals. This allows any cyclic ratio to be accepted on the XTAL1 input. In X2 Mode, as this divider is bypassed, the signals on XTAL1 must have a cyclic ratio between 40 to 60%. Figure 3. shows the clock generation block diagram. The X2 bit is validated on the XTAL1 $\div$ 2 rising edge to avoid glitches when switching from the X2 to the STD mode. Figure 4 shows the mode switching waveforms.          |

AIMEL

#### Operation Cross Memory Access

Space addressable in read and write are:

RAM

•

- ERAM (Expanded RAM access by movx)

- EEPROM DATA

- FM0 ( user flash )

- Hardware byte

- XROW

- Boot Flash

- Flash Column latch

The table below provides the different kind of memory which can be accessed from different code location.

Table 25. Cross Memory Access

|             | Action | RAM | ERAM | Boot FLASH           | FM0       | E <sup>2</sup> Data | Hardware<br>Byte | XROW     |

|-------------|--------|-----|------|----------------------|-----------|---------------------|------------------|----------|

| boot FLASH  | Read   |     |      | OK                   | OK        | OK                  | ОК               | -        |

| DUDI FLASIT | Write  |     |      | -                    | OK (RWW)  | OK (RWW)            | OK (RWW)         | OK (RWW) |

| FM0         | Read   |     |      | OK<br>(confidential) | ОК        | ОК                  | -OK              | -        |

|             | Write  |     |      | -                    | OK (idle) | OK(RWW)             | -                | -OK      |

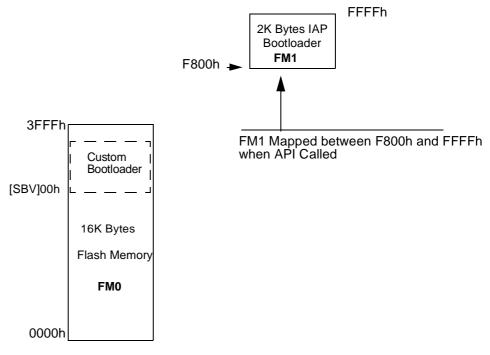

| In-System<br>Programming (ISP)   | <ul> <li>With the implementation of the User Space (FM0) and the Boot Space (FM1) in Flash technology the T89C51CC02 allows the system engineer the development of applications with a very high level of flexibility. This flexibility is based on the possibility to alter the customer program at any stages of a product's life:</li> <li>Before mounting the chip on the PCB, FM0 flash can be programmed with the application code. FM1 is always preprogrammed by Atmel with a bootloader (chip can be ordered with CAN bootloader or UART bootloader).<sup>(1)</sup></li> <li>Once the chip is mounted on the PCB, it can be programmed by serial mode via the CAN bus or UART.</li> <li>Note: 1. The user can also program his own bootloader in FM1.</li> <li>This ISP allows code modification over the total lifetime of the product.</li> <li>Besides the default Bootloaders Atmel provide customers all the needed Application-Programming-Interfaces (API) which are needed for the ISP. The API are located in the Boot memory.</li> <li>This allow the customer to have a full use of the 16-Kbyte user memory.</li> </ul> |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Flash Programming and<br>Erasure | <ul> <li>There are three methods for programming the Flash memory:</li> <li>The Atmel bootloader located in FM1 is activated by the application. Low level API routines (located in FM1)will be used to program FM0. The interface used for serial downloading to FM0 is the UART or the CAN. API can be called also by user's bootloader located in FM0 at [SBV]00h.</li> <li>A further method exist in activating the Atmel boot loader by hardware activation. See the Section "Hardware Security Byte".</li> <li>The FM0 can be programmed also by the parallel mode using a programmer.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Figure 18. Flash Memory Mapping

#### **XROW Bytes** The EXTRA ROW (XROW) includes 128 bytes. Some of these bytes are used for specific purpose in conjonction with the bootloader.

| Table 30. | XROW | Mapping |

|-----------|------|---------|

|-----------|------|---------|

| Description                                     | Default Value | Address |

|-------------------------------------------------|---------------|---------|

| Copy of the Manufacturer Code                   | 58h           | 30h     |

| Copy of the Device ID#1: Family code            | D7h           | 31h     |

| Copy of the Device ID#2: Memories size and type | BBh           | 60h     |

| Copy of the Device ID#3: Name and Revision      | FFh           | 61h     |

**Hardware Conditions** It is possible to force the controller to execute the bootloader after a Reset with hardware conditions.

During the first programming, the user can define a configuration on Port1 that will be recognized by the chip as the hardware conditions during a Reset. If this condition is met, the chip will start executing the bootloader at the end of the Reset.

See a detailed description in the applicable Document.

- Datasheet Bootloader CAN T89C51CC02.

- Datasheet Bootloader UART T89C51CC02.

Here is an example of how to use given addresses to address different slaves:

```

Slave A:SADDR1111 0001b

<u>SADEN1111 1010b</u>

Given1111 0X0Xb

Slave B:SADDR1111 0011b

<u>SADEN1111 1001b</u>

Given1111 0XX1b

Slave C:SADDR1111 0011b

<u>SADEN1111 1101b</u>

Given1111 00X1b

```

The SADEN byte is selected so that each slave may be addressed separately. For slave A, bit 0 (the LSB) is a don't-care bit; for slaves B and C, bit 0 is a 1. To communicate with slave A only, the master must send an address where bit 0 is clear (e.g.

1111 0000b**)**.

For slave A, bit 1 is a 0; for slaves B and C, bit 1 is a don't care bit. To communicate with slaves A and B, but not slave C, the master must send an address with bits 0 and 1 both set (e.g. 1111 0011b).

To communicate with slaves A, B and C, the master must send an address with bit 0 set, bit 1 clear, and bit 2 clear (e.g. 1111 0001b).

**Broadcast Address** A broadcast address is formed from the logical OR of the SADDR and SADEN registers with zeros defined as don't-care bits, e.g.:

SADDR 0101 0110b SADEN 1111 1100b SADDR OR SADEN1111 111Xb

The use of don't-care bits provides flexibility in defining the broadcast address, however in most applications, a broadcast address is FFh. The following is an example of using broadcast addresses:

```

Slave A:SADDR1111 0001b

<u>SADEN1111 1010b</u>

Given1111 1X11b,

Slave B:SADDR1111 0011b

<u>SADEN1111 1001b</u>

Given1111 1X11B,

Slave C:SADDR=1111 0010b

<u>SADEN1111 1101b</u>

Given1111 1111b

```

For slaves A and B, bit 2 is a don't care bit; for slave C, bit 2 is set. To communicate with all of the slaves, the master must send an address FFh. To communicate with slaves A and B, but not slave C, the master can send and address FBh.

| Timer/Counter<br>OperationsA basic operation is Timer registers THx and TLx (x = 0, 1) connected in cascade to<br>form a 16-bit Timer. Setting the run control bit (TRx) in TCON register (See Figure 37)<br>turns the Timer on by allowing the selected input to increment TLx. When TLx overflows<br>it increments THx; when THx overflows it sets the Timer overflow flag (TFx) in TCON<br>register. Setting the TRx does not clear the THx and TLx Timer registers. Timer regis-<br>ters can be accessed to obtain the current count or to enter preset values. They can be<br>read at any time but TRx bit must be cleared to preset their values, otherwise the behav-<br>ior of the Timer/Counter is unpredictable. |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The C/Tx# control bit selects Timer operation or Counter operation by selecting the divided-down peripheral clock or external pin Tx as the source for the counted signal. TRx bit must be cleared when changing the mode of operation, otherwise the behavior of the Timer/Counter is unpredictable.<br>For Timer operation (C/Tx# = 0), the Timer register counts the divided-down peripheral clock. The Timer register is incremented once every peripheral cycle (6 peripheral clock periods). The Timer clock rate is $f_{PER}/6$ , i.e. $f_{OSC}/12$ in standard mode or $f_{OSC}/6$ in X2 Mode.                                                                                                                     |

| For Counter operation (C/Tx# = 1), the Timer register counts the negative transitions on<br>the Tx external input pin. The external input is sampled every peripheral cycles. When<br>the sample is high in one cycle and low in the next one, the Counter is incremented.<br>Since it takes 2 cycles (12 peripheral clock periods) to recognize a negative transition,<br>the maximum count rate is $f_{PER}/12$ , i.e. $f_{OSC}/24$ in standard mode or $f_{OSC}/12$ in X2 Mode.<br>There are no restrictions on the duty cycle of the external input signal, but to ensure that<br>a given level is sampled at least once before it changes, it should be held for at least<br>one full peripheral cycle.               |

| Timer 0Timer 0 functions as either a Timer or event Counter in four modes of operation.Figure 24 through Figure 27 show the logical configuration of each mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Timer 0 is controlled by the four lower bits of TMOD register (See Figure 38) and bits 0,<br>1, 4 and 5 of TCON register (See Figure 37). TMOD register selects the method of<br>Timer gating (GATE0), Timer or Counter operation (T/C0#) and mode of operation (M10<br>and M00). TCON register provides Timer 0 control functions: overflow flag (TF0), run<br>control bit (TR0), interrupt flag (IE0) and interrupt type control bit (IT0).<br>For normal Timer operation (GATE0 = 0), setting TR0 allows TL0 to be incremented by<br>the selected input. Setting GATE0 and TR0 allows external pin INT0# to control Timer<br>operation.                                                                                 |

| Timer 0 overflow (count rolls over from all 1s to all 0s) sets TF0 flag generating an inter-<br>rupt request.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

It is important to stop Timer/Counter before changing mode.

**Table 44.** T2MOD RegisterT2MOD (S:C9h)Timer 2 Mode Control Register

| 7             | 6               | 5                         | 4                                                                                                                            | 3                                         | 2 | 1    | 0    |  |  |  |

|---------------|-----------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|---|------|------|--|--|--|

| -             | -               | -                         | -                                                                                                                            | -                                         | - | T2OE | DCEN |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description               | Description                                                                                                                  |                                           |   |      |      |  |  |  |

| 7             | -               | Reserved<br>The value rea | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                              |                                           |   |      |      |  |  |  |

| 6             | -               | Reserved<br>The value rea | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                              |                                           |   |      |      |  |  |  |

| 5             | -               | Reserved<br>The value rea | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                              |                                           |   |      |      |  |  |  |

| 4             | -               | Reserved<br>The value rea | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                              |                                           |   |      |      |  |  |  |

| 3             | -               | Reserved<br>The value rea | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                              |                                           |   |      |      |  |  |  |

| 2             | -               | Reserved<br>The value rea | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                              |                                           |   |      |      |  |  |  |

| 1             | T2OE            | Clear to prog             | Timer 2 Output Enable bit<br>Clear to program P1.0/T2 as clock input or I/O port.<br>Set to program P1.0/T2 as clock output. |                                           |   |      |      |  |  |  |

| 0             | DCEN            |                           | ble Timer 2 a                                                                                                                | <b>t</b><br>s up/down cou<br>p/down count |   |      |      |  |  |  |

Reset Value = XXXX XX00b Not bit addressable

#### Table 45. TH2 Register

TH2 (S:CDh) Timer 2 High Byte Register

| 7             | 6               | 5            | 4       | 3 | 2 | 1 | 0 |

|---------------|-----------------|--------------|---------|---|---|---|---|

| -             | -               | -            | -       | - | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description  |         |   |   |   |   |

| 7 - 0         |                 | High Byte of | Timer 2 |   |   |   |   |

Reset Value = 0000 0000b Not bit addressable

To enable an interrupt on Buffer-full condition:

- Enable General CAN IT in the interrupt system register

- Enable interrupt on Buffer full, ENBUF

To enable an interrupt when Timer overruns:

• Enable Overrun IT in the interrupt system register

When an interrupt occurs, the corresponding message object bit is set in the SIT register.

To acknowledge an interrupt, the corresponding CANSTCH bits (RXOK, TXOK,...) or CANGIT bits (OVRTIM, OVRBUF,...), must be cleared by the software application.

When the CAN node is in transmission and detects a Form Error in its frame, a bit Error will also be raised. Consequently, two consecutive interrupts can occur, both due to the same error.

When a message object error occurs and is set in CANSTCH register, no general error are set in CANGIE register.

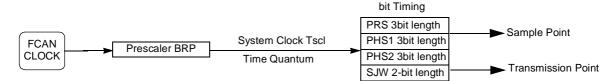

#### bit Timing and Baud Rate

Figure 36. Sample and Transmission Point

The baud rate selection is made by Tbit calculation:

Tbit = Tsyns + Tprs + Tphs1 + Tphs2

- 1. Tsyns = Tscl = (BRP[5..0] + 1)/Fcan = 1TQ

- 2. Tprs = (1 to 8) \* Tscl = (PRS[2..0]+ 1) \* Tscl

- 3. Tphs1 = (1 to 8) \* Tscl = (PHS1[2..0]+ 1) \* Tscl

- 4. Tphs2 = (1 to 8) \* Tscl = (PHS2[2..0]+ 1) \* Tscl

- 5. Tsjw = (1 to 4) \* Tscl = (SJW[1..0]+ 1) \* Tscl

The total number of Tscl (Time Quanta) in a bit time must be comprised between 8 to 25.

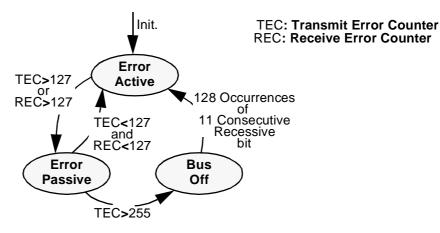

#### **Fault Confinement**

With respect to fault confinement, a unit may be in one of the three following status:

- Error active

- Error passive

- Bus off

An error active unit takes part in bus communication and can send an active error frame when the CAN macro detects an error.

An error passive unit cannot send an active error frame. It takes part in bus communication, but when an error is detected, a passive error frame is sent. Also, after a transmission, an error passive unit will wait before initiating further transmission.

A bus off unit is not allowed to have any influence on the bus.

For fault confinement, two error counters (TEC and REC) are implemented.

See CAN Specification for details on Fault confinement.

#### Figure 38. Line Error Mode

#### Time Trigger Communication (TTC) and Message Stamping

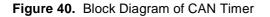

The T89C51CC02 has a programmable 16-bit Timer (CANTIMH&CANTIML) for message stamp and TTC.

This CAN Timer starts after the CAN controller is enabled by the ENA bit in the CANG-CON register.

Two modes in the timer are implemented:

- Time Trigger Communication:

- Capture of this timer value in the CANTTCH & CANTTCL registers on Start Of Frame (SOF) or End Of Frame (EOF), depending on the SYNCTTC bit in the CANGCON register, when the network is configured in TTC by the TTC bit in the CANGCON register.

Note: In this mode, CAN only sends the frame once, even if an error occurs.

- Message Stamping

- Capture of this timer value in the CANSTMPH & CANSTMPL registers of the message object which received or sent the frame.

- All messages can be stamps.

- The stamping of a received frame occurs when the RxOk flag is set.

- The stamping of a sent frame occurs when the TxOk flag is set.

The CAN Timer works in a roll-over from FFFFh to 0000h which serves as a time base.

When the timer roll-over from FFFFh to 0000h, an interrupt is generated if the ETIM bit in the interrupt enable register IEN1 is set.

Table 67. CANPAGE Register

CANPAGE (S:B1h) – CAN Message Object Page Register

| 7        | 6            | 6   | 5        | 4                                                                                                                                    | 3                                                                                       | 2     | 1     | 0     |  |  |

|----------|--------------|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------|-------|-------|--|--|

| -        | -            | •   | CHNB 1   | CHNB 0                                                                                                                               | AINC                                                                                    | INDX2 | INDX1 | INDX0 |  |  |

| Bit Numb | ber          | Bit | Vnemonic | Description                                                                                                                          |                                                                                         |       |       |       |  |  |

| 7 - 6    |              |     | -        | Reserved<br>The values re<br>bits.                                                                                                   | erminate. Do not set these                                                              |       |       |       |  |  |

| 5 - 4    | 5-4 (CHNB30) |     |          |                                                                                                                                      | Selection of Message Object Number<br>The available numbers are: 0 to 3(See Figure 33). |       |       |       |  |  |

| 3        | 3            |     | AINC     | Auto Increment of the Index (Active Low)<br>0 - auto-increment of the index (default value).<br>1 - non-auto-increment of the index. |                                                                                         |       |       |       |  |  |

| 2 - 0    |              | I   | NDX2:0   | 2:0 Index<br>Byte location of the data field for the defined message object<br>Figure 33).                                           |                                                                                         |       |       |       |  |  |

Reset Value = xx00 0000b

Table 68. CANCONCH Register

CANCONCH (S:B3h) – CAN Message Object Control and DLC Register

| 7        | 6       | 5        | 4                                                                                                                                                                                                                                                                                                                              | 3                                                   | 2     | 1     | 0     |  |

|----------|---------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-------|-------|-------|--|

| CONCH 1  | CONCH 0 | RPLV     | IDE                                                                                                                                                                                                                                                                                                                            | DLC 3                                               | DLC 2 | DLC 1 | DLC 0 |  |

| Bit Numb | ber Bit | Mnemonic | Description                                                                                                                                                                                                                                                                                                                    |                                                     |       |       |       |  |

| 7 - 6    | с       | ONCH1:0  | Configuration of Message Object         CONCH1       CONCH0         0       0: disable         0       1: Launch transmission         1       0: Enable Reception         1       1: Enable Reception Buffer         NOTE: The user must re-write the configuration to enable the corresponding bit in the CANEN1:2 registers. |                                                     |       |       |       |  |

| 5        |         | RPLV     | Reply validUsed in the automatic reply mode after receiving a remote frame0 - reply not ready.1 - reply ready & valid.                                                                                                                                                                                                         |                                                     |       |       |       |  |

| 4        |         | IDE      |                                                                                                                                                                                                                                                                                                                                | t <b>ension</b><br>dard rev 2.0 A<br>dard rev 2.0 B | · ·   | ,     |       |  |

| 3 - 0    |         | DLC3:0   | Data Length Code         Number of Bytes in the data field of the message.         The range of DLC is from 0 up to 8.         This value is updated when a frame is received (data or remote frame).         If the expected DLC differs from the incoming DLC, a warning appears in the CANSTCH register.                    |                                                     |       |       |       |  |

### Table 70.CANIDT1 Register for V2.0 part ACANIDT1 for V2.0 part A (S:BCh) – CAN Identifier Tag Registers 1

| 7        | 6                       | 6  | 5                                      | 4     | 3     | 2     | 1     | 0     |

|----------|-------------------------|----|----------------------------------------|-------|-------|-------|-------|-------|

| IDT 10   | IDT                     | Г9 | IDT 8                                  | IDT 7 | IDT 6 | IDT 5 | IDT 4 | IDT 3 |

| Bit Numb | Bit Number Bit Mnemonic |    | Description                            |       |       |       |       |       |

| 7 - 0    | 7 - 0 IDT10:3           |    | IDentifier Tag Value<br>See Figure 39. |       |       |       |       |       |

No default value after reset.

### **Table 71.** CANIDT2 Register for V2.0 part ACANIDT2 for V2.0 part A (S:BDh) - CAN Identifier Tag Registers 2

| 7        | 6     | 5           | 4                                                                                          | 3 | 2 | 1 | 0 |

|----------|-------|-------------|--------------------------------------------------------------------------------------------|---|---|---|---|

| IDT 2    | IDT 1 | IDT 0       | -                                                                                          | - | - | - | - |

| Bit Numb | er B  | it Mnemonic | Description                                                                                |   |   |   |   |

| 7 - 5    |       | IDT2:0      | IDentifier Tag Value<br>See Figure 39.                                                     |   |   |   |   |

| 4-0      |       | -           | <b>Reserved</b><br>The values read from these bits are indeterminate. Do not set the bits. |   |   |   |   |

No default value after reset.

## **Table 72.** CANIDT3 Register for V2.0 part ACANIDT3 for V2.0 part A (S:BEh) –CAN Identifier Tag Registers 3

| 7        | 6      | 5        | 4                                                                                             | 3 | 2 | 1 | 0             |

|----------|--------|----------|-----------------------------------------------------------------------------------------------|---|---|---|---------------|

| -        | -      | -        | -                                                                                             | - | - | - | -             |

| Bit Numb | er Bit | Mnemonic | Description                                                                                   |   |   |   |               |

| 7 - 0    |        | -        | <b>Reserved</b><br>The values read from these bits are indeterminate. Do not set the<br>bits. |   |   |   | not set these |

**Table 81.** CANIDM4 Register for V2.0 part ACANIDM4 for V2.0 part A (S:C7h)CAN Identifier Mask Registers 4

| 7        | 6      | 5        | 4                                                                                                    | 3                                                | 2               | 1               | 0            |  |

|----------|--------|----------|------------------------------------------------------------------------------------------------------|--------------------------------------------------|-----------------|-----------------|--------------|--|

| -        | -      | -        | -                                                                                                    | -                                                | RTRMSK          | -               | IDEMSK       |  |

| Bit Numb | er Bit | Mnemonic | Description                                                                                          |                                                  |                 |                 |              |  |

| 7 - 3    |        | -        | Reserved<br>The values read from these bits are indeterminate. Do not set these<br>bits.             |                                                  |                 |                 |              |  |

| 2        |        | RTRMSK   | Remote transmission request Mask Value<br>0 - comparison true forced.<br>1 - bit comparison enabled. |                                                  |                 |                 |              |  |

| 1        |        | -        | <b>Reserved</b><br>The value rea                                                                     | ad from this bi                                  | t is indetermir | nate. Do not se | et this bit. |  |

| 0        |        | IDEMSK   | 0 - compariso                                                                                        | tension Masl<br>on true forced.<br>rison enabled |                 |                 |              |  |

Note: The ID Mask is only used for reception.

No default value after reset.

**Table 82.** CANIDM1 Register for V2.0 Part BCANIDM1 for V2.0 Part B (S:C4h)CAN Identifier Mask Registers 1

| 7        | 6    | i     | 5        | 4                                                                                                     | 3        | 2        | 1        | 0        |

|----------|------|-------|----------|-------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|

| IDMSK 28 | IDMS | K 27  | IDMSK 26 | IDMSK 25                                                                                              | IDMSK 24 | IDMSK 23 | IDMSK 22 | IDMSK 21 |

| Bit Numb | er   | Bit I | Vnemonic | Description                                                                                           |          |          |          |          |

| 7 - 0    |      | IDI   | MSK28:21 | IDentifier Mask Value<br>0 - comparison true forced.<br>1 - bit comparison enabled.<br>See Figure 39. |          |          |          |          |

Note: The ID Mask is only used for reception.

# **Table 83.** CANIDM2 Register for V2.0 Part BCANIDM2 for V2.0 Part B (S:C5h)CAN Identifier Mask Registers 2

| 7        | (    | 6     | 5         | 4                                                               | 3                               | 2        | 1        | 0        |

|----------|------|-------|-----------|-----------------------------------------------------------------|---------------------------------|----------|----------|----------|

| IDMSK 20 | IDMS | SK 19 | IDMSK 18  | IDMSK 17                                                        | IDMSK 16                        | IDMSK 15 | IDMSK 14 | IDMSK 13 |

| Bit Numb | er   | Bit I | Vinemonic | Description                                                     |                                 |          |          |          |

| 7 - 0    |      | IDI   | MSK20:13  | IDentifier Ma<br>0 - compariso<br>1 - bit compa<br>See Figure 3 | on true forced<br>rison enabled |          |          |          |

Note: 1. The ID Mask is only used for reception.

No default value after reset.

# **Table 84.** CANIDM3 Register for V2.0 Part BCANIDM3 for V2.0 Part B (S:C6h)CAN Identifier Mask Registers 3

| 7        | 6    | 5     | 5        | 4                                                                      | 3                               | 2       | 1       | 0       |

|----------|------|-------|----------|------------------------------------------------------------------------|---------------------------------|---------|---------|---------|

| IDMSK 12 | IDMS | 5K 11 | IDMSK 10 | IDMSK 9                                                                | IDMSK 8                         | IDMSK 7 | IDMSK 6 | IDMSK 5 |

| Bit Numb | er   | Bit   | Mnemonic | Description                                                            |                                 |         |         |         |

| 7 - 0    |      | ID    | MSK12:5  | <b>IDentifier Ma</b><br>0 - compariso<br>1 - bit compa<br>See Figure 3 | on true forced<br>rison enabled |         |         |         |

Note: The ID Mask is only used for reception.

**Table 85.** CANIDM4 Register for V2.0 Part BCANIDM4 for V2.0 Part B (S:C7h)CAN Identifier Mask Registers 4

| 7        | 6                       |    | 5        | 4                                                                                                     | 3       | 2      | 1 | 0            |  |

|----------|-------------------------|----|----------|-------------------------------------------------------------------------------------------------------|---------|--------|---|--------------|--|

| IDMSK 4  | IDMSH                   | (3 | IDMSK 2  | IDMSK 1                                                                                               | IDMSK 0 | RTRMSK | - | IDEMSK       |  |

| Bit Numb | Bit Number Bit Mnemonic |    | Inemonic | Description                                                                                           |         |        |   |              |  |

| 7 - 3    |                         | IC | 0MSK4:0  | IDentifier Mask Value<br>0 - comparison true forced.<br>1 - bit comparison enabled.<br>See Figure 39. |         |        |   |              |  |

| 2        |                         | R  | TRMSK    | Remote transmission request Mask Value<br>0 - comparison true forced.<br>1 - bit comparison enabled.  |         |        |   |              |  |

| 1        |                         |    | -        | Reserved<br>The value read from this bit is indeterminate. Do not se                                  |         |        |   | et this bit. |  |

| 0        |                         | I  | DEMSK    | IDentifier Extension Mask Value<br>0 - comparison true forced.<br>1 - bit comparison enabled.         |         |        |   |              |  |

Note: The ID Mask is only used for reception.

No default value after reset.

**Table 86.** CANMSG RegisterCANMSG (S:A3h)CAN Message Data Register

| 7        | 6       | 5        | 4                                                                                      | 3                                                                                                                        | 2                                                                                                        | 1                                                                        | 0                                                          |  |  |

|----------|---------|----------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------|--|--|

| MSG 7    | MSG 6   | MSG 5    | MSG 4                                                                                  | MSG 3                                                                                                                    | MSG 2                                                                                                    | MSG 1                                                                    | MSG 0                                                      |  |  |

| Bit Numb | er Bitl | Vnemonic | Description                                                                            |                                                                                                                          |                                                                                                          |                                                                          |                                                            |  |  |

| 7 - 0    | ſ       | MSG7:0   | message obje<br>After writing i<br>to the specifie<br>defined identi<br>of the data re | contains the r<br>ect register.<br>n the page me<br>ed message lo<br>fier + index. If<br>gister writing<br>nted. The ran | nailbox data b<br>essage object<br>ocation (in the<br>f auto-increme<br>or reading cyo<br>ge of the cour | register, this l<br>mailbox) of th<br>entation is use<br>cle, the mailbo | byte is equal<br>ne pre-<br>d, at the end<br>px pointer is |  |  |

## AMEL

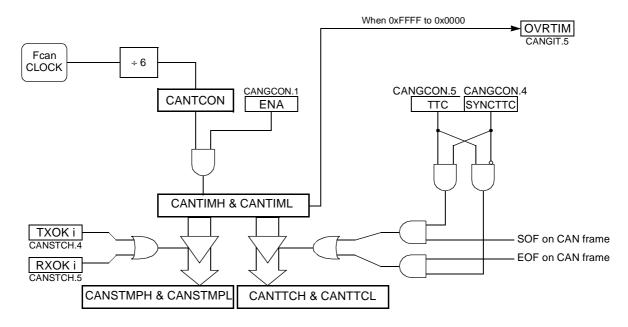

#### 16-bit Software Timer Mode

The PCA modules can be used as software timers by setting both the ECOM and MAT bits in the modules CCAPMn register. The PCA timer will be compared to the module's capture registers and when a match occurs an interrupt will occur if the CCFn (CCON SFR) and the ECCFn (CCAPMn SFR) bits for the module are both set.

Figure 45. PCA 16-bit Software Timer and High Speed Output Mode

| Analog-to-Digital<br>Converter (ADC) | This section describes the on-chip 10-bit analog-to-digital converter of the T89C51CC02. Eight ADC channels are available for sampling of the external sources AN0 to AN7. An analog multiplexer allows the single ADC converter to select one from the 8 ADC channels as ADC input voltage (ADCIN). ADCIN is converted by the 10-bit-cascaded potentiometric ADC.                                                                                                                                                                         |  |  |  |  |  |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                                      | Two modes of conversion are available:<br>- Standard conversion (8 bits).<br>- Precision conversion (10 bits).                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|                                      | For the precision conversion, set bit PSIDLE in ADCON register and start conversion.<br>The device is in a pseudo-idle mode, the CPU does not run but the peripherals are<br>always running. This mode allows digital noise to be as low as possible, to ensure high<br>precision conversion.                                                                                                                                                                                                                                              |  |  |  |  |  |

|                                      | For this mode it is necessary to work with end of conversion interrupt, which is the only way to wake the device up.                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|                                      | If another interrupt occurs during the precision conversion, it will be served only after this conversion is completed.                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| Features                             | <ul> <li>8 channels with multiplexed inputs</li> <li>10-bit cascaded potentiometric ADC</li> <li>Conversion time 16 micro-seconds (typ.)</li> <li>Zero Error (offset) ± 2 LSB max</li> <li>Positive External Reference Voltage Range (VAREF) 2.4 to 3.0-volt (typ.)</li> <li>ADCIN Range 0 to 3-volt</li> <li>Integral non-linearity typical 1 LSB, max. 2 LSB</li> <li>Differential non-linearity typical 0.5 LSB, max. 1 LSB</li> <li>Conversion Complete Flag or Conversion Complete Interrupt</li> <li>Selectable ADC Clock</li> </ul> |  |  |  |  |  |

| ADC Port1 I/O Functions              | Port 1 pins are general I/O that are shared with the ADC channels. The channel select bit in ADCF register define which ADC channel/port1 pin will be used as ADCIN. The remaining ADC channels/port1 pins can be used as general purpose I/O or as the alternate function that is available.                                                                                                                                                                                                                                              |  |  |  |  |  |

|                                      | A conversion launched on a channel which are not selected on ADCF register will not have any effect.                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| VAREF                                | VAREF should be connected to a low impedance point and must remain in the range specified VAREF absolute maximum range (See section "AC-DC").                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|                                      | . If the ADC is not used, it is recommended to tie VAREF to VAGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

Each of the interrupt sources can be individually enabled or disabled by setting or clearing a bit in the Interrupt Enable register. This register also contains a global disable bit which must be cleared to disable all the interrupts at the same time.

Each interrupt source can also be individually programmed to one of four priority levels by setting or clearing a bit in the Interrupt Priority registers. The Table below shows the bit values and priority levels associated with each combination.

| IPH.x | IPL.x | Interrupt Level Priority |

|-------|-------|--------------------------|

| 0     | 0     | 0 (Lowest)               |

| 0     | 1     | 1                        |

| 1     | 0     | 2                        |

| 1     | 1     | 3 (Highest)              |

Table 107. Priority Level bit Values

A low-priority interrupt can be interrupted by a high priority interrupt but not by another low-priority interrupt. A high-priority interrupt cannot be interrupted by any other interrupt source.

If two interrupt requests of different priority levels are received simultaneously, the request of the higher priority level is serviced. If interrupt requests of the same priority level are received simultaneously, an internal polling sequence determines which request is serviced. Thus within each priority level there is a second priority structure determined by the polling sequence, See Table 108.

| Table 108. | Interrupt | Priority | Within | Level |

|------------|-----------|----------|--------|-------|

|------------|-----------|----------|--------|-------|

| Interrupt Name                  | Interrupt Address Vector | Interrupt Number | Polling Priority |  |

|---------------------------------|--------------------------|------------------|------------------|--|

| External interrupt (INT0)       | 0003h                    | 1                | 1                |  |

| Timer0 (TF0)                    | 000Bh                    | 2                | 2                |  |

| External interrupt (INT1)       | 0013h                    | 3                | 3                |  |

| Timer 1 (TF1)                   | 001Bh                    | 4                | 4                |  |

| PCA (CF or CCFn)                | 0033h                    | 7                | 5                |  |

| UART (RI or TI)                 | 0023h                    | 5                | 6                |  |

| Timer 2 (TF2)                   | 002Bh                    | 6                | 7                |  |

| CAN (Txok, Rxok, Err or OvrBuf) | 003Bh                    | 8                | 8                |  |

| ADC (ADCI)                      | 0043h                    | 9                | 9                |  |

| CAN Timer Overflow (OVRTIM)     | 004Bh                    | 10               | 10               |  |

Table 109.IPL0 RegisterIPL0 (S:B8h)Interrupt Enable Register

| 7             | 6               | 5                                                                                      | 4  | 3   | 2   | 1   | 0   |  |  |

|---------------|-----------------|----------------------------------------------------------------------------------------|----|-----|-----|-----|-----|--|--|

| -             | PPC             | PT2                                                                                    | PS | PT1 | PX1 | PT0 | PX0 |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                            |    |     |     |     |     |  |  |

| 7             | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit. |    |     |     |     |     |  |  |

| 6             | PPC             | PCA Interrupt Priority bit<br>Refer to PPCH for priority level                         |    |     |     |     |     |  |  |

| 5             | PT2             | Timer 2 Overflow Interrupt Priority bit<br>Refer to PT2H for priority level.           |    |     |     |     |     |  |  |

| 4             | PS              | Serial Port Priority bit<br>Refer to PSH for priority level.                           |    |     |     |     |     |  |  |

| 3             | PT1             | Timer 1 Overflow Interrupt Priority bit<br>Refer to PT1H for priority level.           |    |     |     |     |     |  |  |

| 2             | PX1             | External Interrupt 1 Priority bit<br>Refer to PX1H for priority level.                 |    |     |     |     |     |  |  |

| 1             | PT0             | Timer 0 Overflow Interrupt Priority bit<br>Refer to PT0H for priority level.           |    |     |     |     |     |  |  |

| 0             | PX0             | External Interrupt 0 Priority bit<br>Refer to PX0H for priority level.                 |    |     |     |     |     |  |  |

Reset Value = X000 0000b bit addressable