Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                     |

| Core Processor             | 80C51                                                                        |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 40MHz                                                                        |

| Connectivity               | CANbus, UART/USART                                                           |

| Peripherals                | POR, PWM, WDT                                                                |

| Number of I/O              | 20                                                                           |

| Program Memory Size        | 16KB (16K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 2K x 8                                                                       |

| RAM Size                   | 512 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                    |

| Data Converters            | A/D 8x10b                                                                    |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-LCC (J-Lead)                                                              |

| Supplier Device Package    | 28-PLCC (11.51x11.51)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/t89c51cc02ua-sitim |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

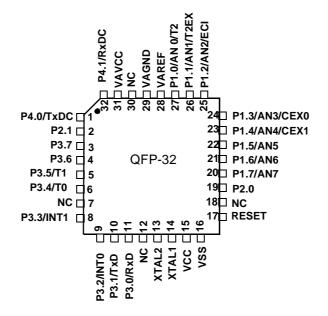

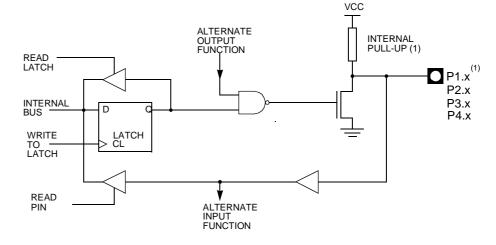

## **I/O Configurations**

Each Port SFR operates via type-D latches, as illustrated in Figure 1 for Ports 3 and 4. A CPU 'write to latch' signal initiates transfer of internal bus data into the type-D latch. A CPU 'read latch' signal transfers the latched Q output onto the internal bus. Similarly, a 'read pin' signal transfers the logical level of the Port pin. Some Port data instructions activate the 'read latch' signal while others activate the 'read pin' signal. Latch instructions are referred to as Read-Modify-Write instructions. Each I/O line may be independently programmed as input or output.

**Port Structure** Figure 1 shows the structure of Ports, which have internal pull-ups. An external source can pull the pin low. Each Port pin can be configured either for general-purpose I/O or for its alternate input output function.

To use a pin for general-purpose output, set or clear the corresponding bit in the Px register (x = 1 to 4). To use a pin for general-purpose input, set the bit in the Px register. This turns off the output FET drive.

To configure a pin for its alternate function, set the bit in the Px register. When the latch is set, the 'alternate output function' signal controls the output level (See Figure 1). The operation of Ports is discussed further in 'Quasi-Bi-directional Port Operation' paragraph.

Note: 1. The internal pull-up can be disabled on P1 when analog function is selected.

# T89C51CC02

#### Table 11. SFR Mapping

|     | 0/8 <sup>(1)</sup>        | 1/9                  | 2/A                               | 3/B                   | 4/C                  | 5/D                  | 6/E                   | 7/F                   |     |

|-----|---------------------------|----------------------|-----------------------------------|-----------------------|----------------------|----------------------|-----------------------|-----------------------|-----|

| F8h | IPL1<br>xxxx x000         | CH<br>0000 0000      | CCAP0H<br>0000 0000               | CCAP1H<br>0000 0000   |                      |                      |                       |                       | FFh |

| F0h | B<br>0000 0000            |                      | ADCLK<br>xxx0 0000                | ADCON<br>x000 0000    | ADDL<br>0000 0000    | ADDH<br>0000 0000    | ADCF<br>0000 0000     | IPH1<br>xxxx x000     | F7h |

| E8h | IEN1<br>xxxx x000         | CL<br>0000 0000      | CCAP0L<br>0000 0000               | CCAP1L<br>0000 0000   |                      |                      |                       |                       | EFh |

| E0h | ACC<br>0000 0000          |                      |                                   |                       |                      |                      |                       |                       | E7h |

| D8h | CCON<br>0000 0000         | CMOD<br>0xxx x000    | CCAPM0<br>x000 0000               | CCAPM1<br>x000 0000   |                      |                      |                       |                       | DFh |

| D0h | PSW<br>0000 0000          | FCON<br>0000 0000    | EECON<br>xxxx xx00                |                       |                      |                      |                       |                       | D7h |

| C8h | <b>T2CON</b><br>0000 0000 | T2MOD<br>xxxx xx00   | RCAP2L<br>0000 0000               | RCAP2H<br>0000 0000   | TL2<br>0000 0000     | TH2<br>0000 0000     |                       | CANEN<br>xxxx 0000    | CFh |

| C0h | P4<br>xxxx xx11           | CANGIE<br>1100 0000  |                                   | CANIE<br>1111 0000    | CANIDM1<br>xxxx xxxx | CANIDM2<br>xxxx xxxx | CANIDM3<br>xxxx xxxx  | CANIDM4<br>xxxx xxxx  | C7h |

| B8h | IPL0<br>x000 0000         | SADEN<br>0000 0000   |                                   | CANSIT<br>xxxx 0000   | CANIDT1<br>xxxx xxxx | CANIDT2<br>xxxx xxxx | CANIDT3<br>xxxx xxxx  | CANIDT4<br>xxxx xxxx  | BFh |

| B0h | P3<br>1111 1111           | CANPAGE<br>1100 0000 | CANSTCH<br>xxxx xxxx              | CANCONCH<br>xxxx xxxx | CANBT1<br>xxxx xxxx  | CANBT2<br>xxxx xxxx  | CANBT3<br>xxxx xxxx   | IPH0<br>x000 0000     | B7h |

| A8h | IEN0<br>0000 0000         | SADDR<br>0000 0000   | CANGSTA<br>1010 0000              | CANGCON<br>0000 0000  | CANTIML<br>0000 0000 | CANTIMH<br>0000 0000 | CANSTMPL<br>xxxx xxxx | CANSTMPH<br>xxxx xxxx | AFh |

| A0h | P2<br>xxxx xx11           | CANTCON<br>0000 0000 | AUXR1 <sup>(2)</sup><br>xxxx 00x0 | CANMSG<br>xxxx xxxx   | CANTTCL<br>0000 0000 | CANTTCH<br>0000 0000 | WDTRST<br>1111 1111   | WDTPRG<br>xxxx x000   | A7h |

| 98h | SCON<br>0000 0000         | SBUF<br>0000 0000    |                                   | CANGIT<br>0x00 0000   | CANTEC 0000 0000     | CANREC<br>0000 0000  |                       |                       | 9Fh |

| 90h | P1<br>1111 1111           |                      |                                   |                       |                      |                      |                       |                       | 97h |

| 88h | TCON<br>0000 0000         | TMOD<br>0000 0000    | TL0<br>0000 0000                  | TL1<br>0000 0000      | TH0<br>0000 0000     | TH1<br>0000 0000     |                       | CKCON<br>0000 0000    | 8Fh |

| 80h |                           | SP<br>0000 0111      | DPL<br>0000 0000                  | DPH<br>0000 0000      |                      |                      |                       | PCON<br>00x1 0000     | 87h |

| L   | 0/8 <sup>(1)</sup>        | 1/9                  | 2/A                               | 3/B                   | 4/C                  | 5/D                  | 6/E                   | 7/F                   | 4   |

#### Reserved

Notes: 1. These registers are bit-addressable.

Sixteen addresses in the SFR space are both byte-addressable and bit-addressable. The bit-addressable SFRs are those whose address ends in 0 and 8. The bit addresses, in this area, are 0x80 through to 0xFF.

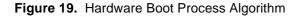

2. AUXR1 bit ENBOOT is initialized with the content of the BLJB bit inverted.

# Registers

**Table 17.** PSW RegisterPSW (S:D0h)Program Status Word Register

| 7             | 6               | 5                           | 4                                                                                                             | 3           | 2  | 1  | 0 |  |  |  |

|---------------|-----------------|-----------------------------|---------------------------------------------------------------------------------------------------------------|-------------|----|----|---|--|--|--|

| СҮ            | AC              | F0                          | RS1                                                                                                           | RS0         | ov | F1 | Р |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                 | Description                                                                                                   |             |    |    |   |  |  |  |

| 7             | CY              | Carry Flag<br>Carry out fro | m bit 1 of ALL                                                                                                | J operands. |    |    |   |  |  |  |

| 6             | AC              | -                           | Auxiliary Carry Flag<br>Carry out from bit 1 of addition operands.                                            |             |    |    |   |  |  |  |

| 5             | F0              | User Defina                 | ble Flag 0                                                                                                    |             |    |    |   |  |  |  |

| 4 - 3         | RS1:0           | -                           | n <b>k Select bit</b> s<br>e 16 for bits c                                                                    |             |    |    |   |  |  |  |

| 2             | OV              | Overflow Fla                | <b>ag</b><br>by arithmetic                                                                                    | operations. |    |    |   |  |  |  |

| 1             | F1              | User Defina                 | ble Flag 1                                                                                                    |             |    |    |   |  |  |  |

| 0             | Р               |                             | Parity bit<br>Set when ACC contains an odd number of 1's.<br>Cleared when ACC contains an even number of 1's. |             |    |    |   |  |  |  |

Reset Value = 0000 0000b

| EEPROM Data<br>Memory               | The 2K bytes on-chip EEPROM memory block is located at addresses 0000h to 07FFh of the XRAM/XRAM memory space and is selected by setting control bits in the EECON register. A read in the EEPROM memory is done with a MOVX instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                     | A physical write in the EEPROM memory is done in two steps: write data in the column latches and transfer of all data latches into an EEPROM memory row (programming).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                     | The number of data written on the page may vary from 1 up to 128 Bytes (the page size). When programming, only the data written in the column latch is programmed and a ninth bit is used to obtain this feature. This provides the capability to program the whole memory by Bytes, by page or by a number of Bytes in a page. Indeed, each ninth bit is set when the writing the corresponding byte in a row and all these ninth bits are reset after the writing of the complete EEPROM row.                                                                                                                                                                                                                                                                        |

| Write Data in the Column<br>Latches | Data is written by byte to the column latches as for an external RAM memory. Out of the 11 address bits of the data pointer, the 4 MSBs are used for page selection (row) and 7 are used for byte selection. Between two EEPROM programming sessions, all the addresses in the column latches must stay on the same page, meaning that the 4 MSB must no be changed.                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                     | <ul> <li>The following procedure is used to write to the column latches:</li> <li>Save and disable interrupt</li> <li>Set bit EEE of EECON register</li> <li>Load DPTR with the address to write</li> <li>Store A register with the data to be written</li> <li>Execute a MOVX @DPTR, A</li> <li>If needed loop the three last instructions until the end of a 128 Bytes page</li> <li>Restore interrupt</li> <li>Note: The last page address used when loading the column latch is the one used to select the page programming address.</li> </ul>                                                                                                                                                                                                                    |

| Programming                         | <ul> <li>The EEPROM programming consists of the following actions:</li> <li>Write one or more Bytes of one page in the column latches. Normally, all Bytes must belong to the same page; if not, the last page address will be latched and the others discarded.</li> <li>Launch programming by writing the control sequence (50h followed by A0h) to the EECON register.</li> <li>EEBUSY flag in EECON is then set by hardware to indicate that programming is in progress and that the EEPROM segment is not available for reading.</li> <li>The end of programming is indicated by a hardware clear of the EEBUSY flag.</li> <li>Note: The sequence 5xh and Axh must be executed without instructions between then otherwise the programming is aborted.</li> </ul> |

| Read Data                           | <ul> <li>The following procedure is used to read the data stored in the EEPROM memory:</li> <li>Save and disable interrupt</li> <li>Set bit EEE of EECON register</li> <li>Load DPTR with the address to read</li> <li>Execute a MOVX A, @DPTR</li> <li>Restore interrupt</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

T89C51CC02 30

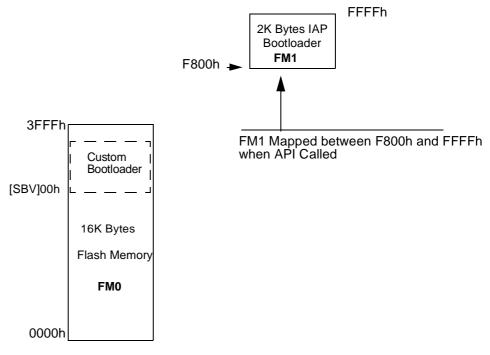

| In-System<br>Programming (ISP)   | <ul> <li>With the implementation of the User Space (FM0) and the Boot Space (FM1) in Flash technology the T89C51CC02 allows the system engineer the development of applications with a very high level of flexibility. This flexibility is based on the possibility to alter the customer program at any stages of a product's life:</li> <li>Before mounting the chip on the PCB, FM0 flash can be programmed with the application code. FM1 is always preprogrammed by Atmel with a bootloader (chip can be ordered with CAN bootloader or UART bootloader).<sup>(1)</sup></li> <li>Once the chip is mounted on the PCB, it can be programmed by serial mode via the CAN bus or UART.</li> <li>Note: 1. The user can also program his own bootloader in FM1.</li> <li>This ISP allows code modification over the total lifetime of the product.</li> <li>Besides the default Bootloaders Atmel provide customers all the needed Application-Programming-Interfaces (API) which are needed for the ISP. The API are located in the Boot memory.</li> <li>This allow the customer to have a full use of the 16-Kbyte user memory.</li> </ul> |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Flash Programming and<br>Erasure | <ul> <li>There are three methods for programming the Flash memory:</li> <li>The Atmel bootloader located in FM1 is activated by the application. Low level API routines (located in FM1)will be used to program FM0. The interface used for serial downloading to FM0 is the UART or the CAN. API can be called also by user's bootloader located in FM0 at [SBV]00h.</li> <li>A further method exist in activating the Atmel boot loader by hardware activation. See the Section "Hardware Security Byte".</li> <li>The FM0 can be programmed also by the parallel mode using a programmer.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Figure 18. Flash Memory Mapping

### **Boot Process**

Software Boot Process Many algorithms can be used for the software boot process. Below are descriptions of Example the different flags and Bytes. Boot Loader Jump bit (BLJB): - This bit indicates if on RESET the user wants to jump to this application at address @0000h on FM0 or execute the boot loader at address @F800h on FM1. - BLJB = 0 (i.e. bootloader FM1 executed after a reset) is the default Atmel factory programming. -To read or modify this bit, the APIs are used. Boot Vector Address (SBV): - This byte contains the MSB of the user boot loader address in FM0. - The default value of SBV is FFh (no user boot loader in FM0). - To read or modify this byte, the APIs are used. Extra Byte (EB) & Boot Status Byte (BSB): - These Bytes are reserved for customer use.

- To read or modify these Bytes, the APIs are used.

## Application-Programming-Interface

Several Application Program Interface (API) calls are available for use by an application program to permit selective erasing and programming of Flash pages. All calls are made by functions.

All these APIs are described in detail in the following documents on the Atmel web site.

- Datasheet Bootloader CAN T89C51CC02.

- Datasheet Bootloader UART T89C51CC02.

# 46 **T89C51CC02**

Here is an example of how to use given addresses to address different slaves:

```

Slave A:SADDR1111 0001b

<u>SADEN1111 1010b</u>

Given1111 0X0Xb

Slave B:SADDR1111 0011b

<u>SADEN1111 1001b</u>

Given1111 0XX1b

Slave C:SADDR1111 0011b

<u>SADEN1111 1101b</u>

Given1111 00X1b

```

The SADEN byte is selected so that each slave may be addressed separately. For slave A, bit 0 (the LSB) is a don't-care bit; for slaves B and C, bit 0 is a 1. To communicate with slave A only, the master must send an address where bit 0 is clear (e.g.

1111 0000b**)**.

For slave A, bit 1 is a 0; for slaves B and C, bit 1 is a don't care bit. To communicate with slaves A and B, but not slave C, the master must send an address with bits 0 and 1 both set (e.g. 1111 0011b).

To communicate with slaves A, B and C, the master must send an address with bit 0 set, bit 1 clear, and bit 2 clear (e.g. 1111 0001b).

**Broadcast Address** A broadcast address is formed from the logical OR of the SADDR and SADEN registers with zeros defined as don't-care bits, e.g.:

SADDR 0101 0110b SADEN 1111 1100b SADDR OR SADEN1111 111Xb

The use of don't-care bits provides flexibility in defining the broadcast address, however in most applications, a broadcast address is FFh. The following is an example of using broadcast addresses:

```

Slave A:SADDR1111 0001b

<u>SADEN1111 1010b</u>

Given1111 1X11b,

Slave B:SADDR1111 0011b

<u>SADEN1111 1001b</u>

Given1111 1X11B,

Slave C:SADDR=1111 0010b

<u>SADEN1111 1101b</u>

Given1111 1111b

```

For slaves A and B, bit 2 is a don't care bit; for slave C, bit 2 is set. To communicate with all of the slaves, the master must send an address FFh. To communicate with slaves A and B, but not slave C, the master can send and address FBh.

# Registers

Table 43.T2CON RegisterT2CON (S:C8h)Timer 2 Control Register

| 7             | 6               | 5                                                           | 4                                                                                                                                                                                   | 3                                                                 | 2             | 1                        | 0        |  |  |  |

|---------------|-----------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|---------------|--------------------------|----------|--|--|--|

| TF2           | EXF2            | RCLK                                                        | TCLK                                                                                                                                                                                | EXEN2                                                             | TR2           | C/T2#                    | CP/RL2#  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                 |                                                                                                                                                                                     |                                                                   |               |                          |          |  |  |  |

| 7             | TF2             | Must be clea                                                | rflow Flag<br>ti if RCLK=1 c<br>red by softwa<br>vare on Timer                                                                                                                      | re.                                                               |               |                          |          |  |  |  |

| 6             | EXF2            | Set when a c<br>EXEN2=1.<br>Set to cause<br>interrupt is en | <b>Timer 2 External Flag</b><br>Set when a capture or a reload is caused by a negative transition on T2EX pin if                                                                    |                                                                   |               |                          |          |  |  |  |

| 5             | RCLK            | Clear to use                                                | Receive Clock bit<br>Clear to use timer 1 overflow as receive clock for serial port in mode 1 or 3.<br>Set to use Timer 2 overflow as receive clock for serial port in mode 1 or 3. |                                                                   |               |                          |          |  |  |  |

| 4             | TCLK            |                                                             | timer 1 overfle                                                                                                                                                                     | ow as transmi<br>w as transmit o                                  |               |                          |          |  |  |  |

| 3             | EXEN2           | Clear to igno<br>Set to cause                               | a capture or                                                                                                                                                                        | <b>bit</b><br>T2EX pin for T<br>reload when a<br>used to clock t  | negative tran | sition on T2E            | X pin is |  |  |  |

| 2             | TR2             | Timer 2 Run<br>Clear to turn<br>Set to turn or              | off Timer 2.                                                                                                                                                                        |                                                                   |               |                          |          |  |  |  |

| 1             | C/T2#           | Clear for time                                              |                                                                                                                                                                                     | <b>it</b><br>nput from inte<br>input from T2                      |               | tem: f <sub>OSC</sub> ). |          |  |  |  |

| 0             | CP/RL2#         | If RCLK=1 or<br>Timer 2 over<br>Clear to auto<br>EXEN2=1.   | flow.<br>-reload on Tir                                                                                                                                                             | <b>bit</b><br>//RL2# is ignol<br>ner 2 overflow<br>transitions or | s or negative | transitions on           |          |  |  |  |

Reset Value = 0000 0000b bit addressable

Table 46.TL2 RegisterTL2 (S:CCh)Timer 2 Low Byte Register

| 7             | 6               | 5           | 4       | 3 | 2 | 1 | 0 |

|---------------|-----------------|-------------|---------|---|---|---|---|

| -             | -               | -           | -       | - | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description |         |   |   |   |   |

| 7 - 0         |                 | Low Byte of | Timer 2 |   |   |   |   |

Reset Value = 0000 0000b Not bit addressable

Table 47.RCAP2H RegisterRCAP2H (S:CBh)

Timer 2 Reload/Capture High Byte Register

| 7             | 6               | 5                                    | 4           | 3 | 2 | 1 | 0 |  |  |

|---------------|-----------------|--------------------------------------|-------------|---|---|---|---|--|--|

| -             | -               | -                                    | -           | - | - | - | - |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                          | Description |   |   |   |   |  |  |

| 7 - 0         |                 | High Byte of Timer 2 Reload/Capture. |             |   |   |   |   |  |  |

Reset Value = 0000 0000b Not bit addressable

### Table 48. RCAP2L Register

RCAP2L (S:CAh) Timer 2 Reload/Capture Low Byte Register

| 7             | 6               | 5           | 4                                   | 3 | 2 | 1 | 0 |  |  |

|---------------|-----------------|-------------|-------------------------------------|---|---|---|---|--|--|

| -             | -               | -           | -                                   | - | - | - | - |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description | Description                         |   |   |   |   |  |  |

| 7 - 0         |                 | Low Byte of | Low Byte of Timer 2 Reload/Capture. |   |   |   |   |  |  |

Reset Value = 0000 0000b Not bit addressable

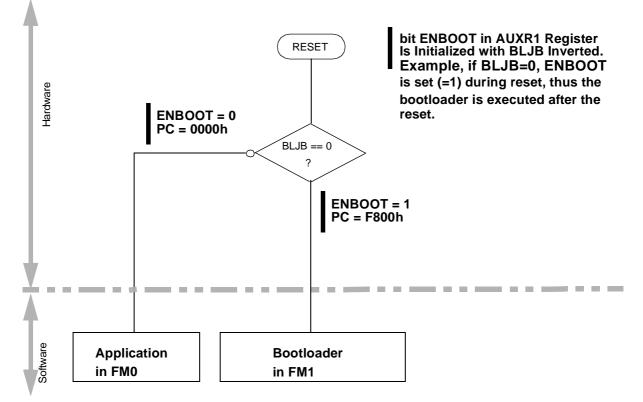

#### Figure 35. CAN Controller Interrupt Structure

To enable a transmission interrupt:

- Enable General CAN IT in the interrupt system register

- Enable interrupt by message object, EICHi

- Enable transmission interrupt, ENTX

To enable a reception interrupt:

- Enable General CAN IT in the interrupt system register

- Enable interrupt by message object, EICHi

- Enable reception interrupt, ENRX

To enable an interrupt on message object error:

- Enable General CAN IT in the interrupt system register

- Enable interrupt by message object, EICHi

- Enable interrupt on error, ENERCH

To enable an interrupt on general error:

- Enable General CAN IT in the interrupt system register

- Enable interrupt on error, ENERG

### **Fault Confinement**

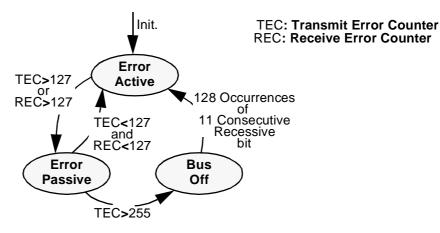

With respect to fault confinement, a unit may be in one of the three following status:

- Error active

- Error passive

- Bus off

An error active unit takes part in bus communication and can send an active error frame when the CAN macro detects an error.

An error passive unit cannot send an active error frame. It takes part in bus communication, but when an error is detected, a passive error frame is sent. Also, after a transmission, an error passive unit will wait before initiating further transmission.

A bus off unit is not allowed to have any influence on the bus.

For fault confinement, two error counters (TEC and REC) are implemented.

See CAN Specification for details on Fault confinement.

#### Figure 38. Line Error Mode

// Find the first message object which generate an interrupt in CANSIT

// Select the corresponding message object

$\ensuremath{{\prime}}\xspace$  // Analyse the CANSTCH register to identify which kind of interrupt is generated

// Manage the interrupt

// Clear the status register CANSTCH = 00h;

// if it is not a channel interrupt but a general interrupt

$\ensuremath{{\ensuremath{\text{-/}}}}$  Manage the general interrupt and clear CANGIT register

$/\,/$  restore the old <code>CANPAGE</code>

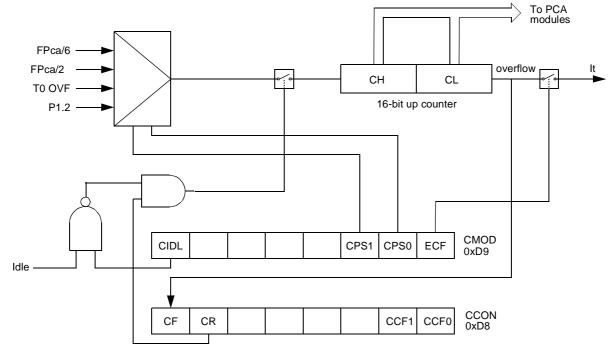

#### Figure 42. PCA Timer/Counter

The CMOD register includes three additional bits associated with the PCA.

- The CIDL bit which allows the PCA to stop during idle mode.

- The ECF bit which when set causes an interrupt and the PCA overflow flag CF in CCON register to be set when the PCA timer overflows.

The CCON register contains the run control bit for the PCA and the flags for the PCA timer and each module.

- The CR bit must be set to run the PCA. The PCA is shut off by clearing this bit.

- The CF bit is set when the PCA counter overflows and an interrupt will be generated if the ECF bit in CMOD register is set. The CF bit can only be cleared by software.

- The CCF0:1 bits are the flags for the modules (CCF0 for module0...) and are set by hardware when either a match or a capture occurs. These flags also can be cleared by software.

# T89C51CC02

Table 104.ADCLK RegisterADCLK (S:F2h)ADC Clock Prescaler

| 7             | 6               | 5                                                                                            | 4                                                                                    | 3     | 2     | 1     | 0     |  |  |  |

|---------------|-----------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------|-------|-------|-------|--|--|--|

| -             | -               | -                                                                                            | PRS 4                                                                                | PRS 3 | PRS 2 | PRS 1 | PRS 0 |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                  | Description                                                                          |       |       |       |       |  |  |  |

| 7 - 5         | -               | Reserved<br>The value rea                                                                    | Reserved<br>The value read from these bits are indeterminate. Do not set these bits. |       |       |       |       |  |  |  |

| 4-0           | PRS4:0          | Clock Prescaler<br>Fadc = Fcpuclock/(4*PRS)) in X1 mode<br>Fadc=Fcpuclock/(2*PRS) in X2 mode |                                                                                      |       |       |       |       |  |  |  |

Reset Value = XXX0 0000b

**Table 105.** ADDH RegisterADDH (S:F5h Read Only)ADC Data High Byte Register

| 7             | 6               | 5                      | 4      | 3      | 2      | 1      | 0      |

|---------------|-----------------|------------------------|--------|--------|--------|--------|--------|

| ADAT 9        | ADAT 8          | ADAT 7                 | ADAT 6 | ADAT 5 | ADAT 4 | ADAT 3 | ADAT 2 |

| Bit<br>Number | Bit<br>Mnemonic | Description            |        |        |        |        |        |

| 7 - 0         | ADAT9:2         | ADC result<br>bits 9-2 |        |        |        |        |        |

Reset Value = 00h

**Table 106.** ADDL RegisterADDL (S:F4h Read Only)ADC Data Low Byte Register

| 7             | 6               | 5                               | 4                                                                                    | 3 | 2 | 1      | 0      |  |  |

|---------------|-----------------|---------------------------------|--------------------------------------------------------------------------------------|---|---|--------|--------|--|--|

| -             | -               | -                               | -                                                                                    | - | - | ADAT 1 | ADAT 0 |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                     |                                                                                      |   |   |        |        |  |  |

| 7 - 2         | -               | <b>Reserved</b><br>The value re | Reserved<br>The value read from these bits are indeterminate. Do not set these bits. |   |   |        |        |  |  |

| 1-0           | ADAT1:0         | ADC result<br>bits 1-0          |                                                                                      |   |   |        |        |  |  |

Reset Value = 00h

## Registers

**Figure 53.** IEN0 Register IEN0 (S:A8h) Interrupt Enable Register

| 7             | 6               | 5                                                                                                                                                                                                                       | 4                                                                                                                                  | 3   | 2   | 1   | 0   |

|---------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|

| EA            | EC              | ET2                                                                                                                                                                                                                     | ES                                                                                                                                 | ET1 | EX1 | ET0 | EX0 |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                             |                                                                                                                                    |     |     |     |     |

| 7             | EA              | Enable All Interrupt bit<br>Clear to disable all interrupts.<br>Set to enable all interrupts.<br>If EA=1, each interrupt source is individually enabled or disabled by setting or<br>clearing its interrupt enable bit. |                                                                                                                                    |     |     |     |     |

| 6             | EC              | PCA Interrupt Enable<br>Clear to disable the PCA interrupt.<br>Set to enable the PCA interrupt.                                                                                                                         |                                                                                                                                    |     |     |     |     |

| 5             | ET2             | Clear to disa                                                                                                                                                                                                           | Timer 2 Overflow Interrupt Enable bit<br>Clear to disable Timer 2 overflow interrupt.<br>Set to enable Timer 2 overflow interrupt. |     |     |     |     |

| 4             | ES              | Clear to disa                                                                                                                                                                                                           | Serial port Enable bit<br>Clear to disable serial port interrupt.<br>Set to enable serial port interrupt.                          |     |     |     |     |

| 3             | ET1             | Timer 1 Overflow Interrupt Enable bit<br>Clear to disable timer 1 overflow interrupt.<br>Set to enable timer 1 overflow interrupt.                                                                                      |                                                                                                                                    |     |     |     |     |

| 2             | EX1             | External Interrupt 1 Enable bit<br>Clear to disable external interrupt 1.<br>Set to enable external interrupt 1.                                                                                                        |                                                                                                                                    |     |     |     |     |

| 1             | ET0             | Timer 0 Overflow Interrupt Enable bit<br>Clear to disable timer 0 overflow interrupt.<br>Set to enable timer 0 overflow interrupt.                                                                                      |                                                                                                                                    |     |     |     |     |

| 0             | EX0             | External Interrupt 0 Enable bit<br>Clear to disable external interrupt 0.<br>Set to enable external interrupt 0.                                                                                                        |                                                                                                                                    |     |     |     |     |

Reset Value = 0000 0000b bit addressable

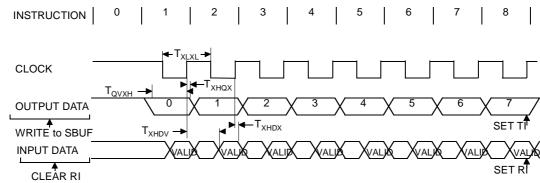

#### **Shift Register Timing Waveforms**

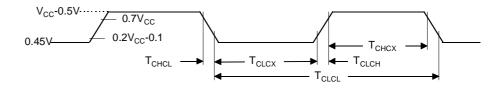

#### **External Clock Drive Characteristics (XTAL1)**

#### Table 118. AC Parameters

| Symbol                               | Parameter               | Min | Мах | Units |

|--------------------------------------|-------------------------|-----|-----|-------|

| T <sub>CLCL</sub>                    | Oscillator Period       | 25  |     | ns    |

| T <sub>CHCX</sub>                    | High Time               | 5   |     | ns    |

| T <sub>CLCX</sub>                    | Low Time                | 5   |     | ns    |

| T <sub>CLCH</sub>                    | Rise Time               |     | 5   | ns    |

| T <sub>CHCL</sub>                    | Fall Time               |     | 5   | ns    |

| T <sub>CHCX</sub> /T <sub>CLCX</sub> | Cyclic ratio in X2 Mode | 40  | 60  | %     |

#### **External Clock Drive** Waveforms

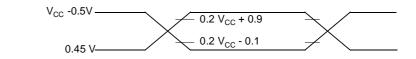

### **AC Testing Input/Output Waveforms**

INPUT/OUTPUT

AC inputs during testing are driven at V<sub>CC</sub> - 0.5 for a logic "1" and 0.45V for a logic "0". Timing measurement are made at V<sub>IH</sub> min for a logic "1" and V<sub>IL</sub> max for a logic "0".

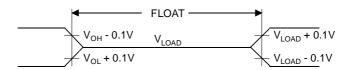

#### Float Waveforms

# T89C51CC02

# **Ordering Information**

| Part Number        | Bootloader          | Temperature<br>Range | Package | Packing | Product Marking |

|--------------------|---------------------|----------------------|---------|---------|-----------------|

| T89C51CC02CA-RATIM | CAN <sup>(2)</sup>  | Industrial           | VQFP32  | Tray    | 89C51CC02CA-IM  |

| T89C51CC02CA-SISIM | CAN <sup>(2)</sup>  | Industrial           | PLCC28  | Stick   | 89C51CC02CA-IM  |

| T89C51CC02CA-TDSIM | CAN <sup>(2)</sup>  | Industrial           | SOIC24  | Stick   | 89C51CC02CA-IM  |

| T89C51CC02CA-TISIM | CAN <sup>(2)</sup>  | Industrial           | SOIC28  | Stick   | 89C51CC02CA-IM  |

| T89C51CC02UA-RATIM | UART <sup>(2)</sup> | Industrial           | VQFP32  | Tray    | 89C51CC02UA-IM  |

| T89C51CC02UA-SISIM | UART <sup>(2)</sup> | Industrial           | PLCC28  | Stick   | 89C51CC02UA-IM  |

| T89C51CC02UA-TDSIM | UART <sup>(2)</sup> | Industrial           | SOIC24  | Stick   | 89C51CC02UA-IM  |

| T89C51CC02UA-TISIM | UART <sup>(2)</sup> | Industrial           | SOIC28  | Stick   | 89C51CC02UA-IM  |

Factory default programming for T89C51CC02CA-xxxx is Bootloader CAN and HSB = BBh:

- X1 mode

- BLJB = 0 : jump to Bootloader

- LB2 = 0 : Security Level  $3.^{(1)}$

Factory default programming for T89C51CC02UA-xxxx is Bootloader UART and HSB = BBh:

- X1 mode

- BLJB = 0 : jump to Bootloader

- LB2 = 0 : Security Level  $3.^{(1)}$

- Notes: 1. LB2 = 0 is not described in Table 22 Program load bit. LB2 = 0 is equivalent to LB1 = 0: Security Level 3.

- 2. Customer can change these modes by re-programming with a parallel programmer, this can be done by an Atmel distributor.

| DC Parameters for Standard Voltage          | 132 |

|---------------------------------------------|-----|

| DC Parameters for A/D Converter.            |     |

| AC Parameters                               |     |

| Ordering Information                        | 138 |

| Package Drawings                            | 139 |

| VQFP32                                      | 139 |

| PLCC28                                      | 140 |

| SOIC24                                      | 141 |

| SOIC28                                      | 142 |

| Datasheet Change Log for T89C51CC02         | 143 |

| Changes from 4126C - 10/02 to 4126D - 04/03 | 143 |

| Changes from 4126D - 05/03 to 4126E - 10/03 | 143 |

| Changes from 4126E - 10/03 to 4126F - 12/03 | 143 |

| Table of Contents                           | i   |