Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

EXF

| Product Status             | Active                                                                                              |

|----------------------------|-----------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                                  |

| Speed                      | 180MHz                                                                                              |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SAI, SDIO, SPI, UART/USART, USB, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                                   |

| Number of I/O              | 161                                                                                                 |

| Program Memory Size        | 1MB (1M × 8)                                                                                        |

| Program Memory Type        | FLASH                                                                                               |

| EEPROM Size                | -                                                                                                   |

| RAM Size                   | 384K x 8                                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                         |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                               |

| Oscillator Type            | Internal                                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                   |

| Mounting Type              | Surface Mount                                                                                       |

| Package / Case             | 216-TFBGA                                                                                           |

| Supplier Device Package    | 216-TFBGA (13x13)                                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f479ngh6                               |

|                            |                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## List of figures

| Figure 1.  | Incompatible board design for LQFP176 package                                         | 16 |

|------------|---------------------------------------------------------------------------------------|----|

| Figure 2.  | Incompatible board design for LQFP208 package                                         | 17 |

| Figure 3.  | UFBGA176 port-to-terminal assignment differences                                      | 18 |

| Figure 4.  | TFBGA216 port-to-terminal assignment differences.                                     | 19 |

| Figure 5.  | STM32F479xx block diagram                                                             | 20 |

| Figure 6.  | STM32F479xx Multi-AHB matrix                                                          | 23 |

| Figure 7.  | VDDUSB connected to an external independent power supply                              | 29 |

| Figure 8.  | Power supply supervisor interconnection with internal reset OFF                       | 30 |

| Figure 9.  | PDR_ON control with internal reset OFF                                                | 31 |

| Figure 10. | Regulator OFF                                                                         | 33 |

| Figure 11. | Startup in regulator OFF: slow V <sub>DD</sub> slope                                  |    |

|            | - power-down reset risen after V <sub>CAP_1</sub> , V <sub>CAP_2</sub> stabilization  | 34 |

| Figure 12. | Startup in regulator OFF mode: fast V <sub>DD</sub> slope                             |    |

|            | - power-down reset risen before V <sub>CAP_1</sub> , V <sub>CAP_2</sub> stabilization | 34 |

| Figure 13. | STM32F47x LQFP100 pinout                                                              |    |

| Figure 14. | STM32F47x LQFP144 pinout                                                              |    |

| Figure 15. | STM32F47x WLCSP168 pinout                                                             |    |

| Figure 16. | STM32F47x UFBGA169 ballout                                                            |    |

| Figure 17. | STM32F47x UFBGA176 ballout                                                            |    |

| Figure 18. | STM32F47x LQFP176 pinout                                                              |    |

| Figure 19. | STM32F47x LQFP208 pinout                                                              |    |

| Figure 20. | STM32F47x TFBGA216 ballout                                                            |    |

| Figure 21. | Memory map                                                                            |    |

| Figure 22. | Pin loading conditions                                                                |    |

| Figure 23. | Pin input voltage                                                                     |    |

| Figure 24. | Power supply scheme                                                                   |    |

| Figure 25. | Current consumption measurement scheme                                                |    |

| Figure 26. | External capacitor C <sub>EXT</sub>                                                   | 94 |

| Figure 27. | Typical V <sub>BAT</sub> current consumption                                          |    |

|            | (RTC ON / backup SRAM ON and LSE in Low drive mode) 1                                 | 06 |

| Figure 28. | Typical V <sub>BAT</sub> current consumption                                          |    |

|            | (RTC ON / backup SRAM ON and LSE in High drive mode) 1                                |    |

| Figure 29. | High-speed external clock source AC timing diagram                                    |    |

| Figure 30. | Low-speed external clock source AC timing diagram1                                    |    |

| Figure 31. | Typical application with an 8 MHz crystal                                             |    |

| Figure 32. | Typical application with a 32.768 kHz crystal                                         |    |

| Figure 33. | ACCHSI vs. temperature                                                                |    |

| Figure 34. | ACC <sub>LSI</sub> versus temperature                                                 |    |

| Figure 35. | PLL output clock waveforms in center spread mode1                                     |    |

| Figure 36. | PLL output clock waveforms in down spread mode 1                                      |    |

| Figure 37. | MIPI D-PHY HS/LP clock lane transition timing diagram                                 |    |

| Figure 38. | MIPI D-PHY HS/LP data lane transition timing diagram                                  |    |

| Figure 39. | FT I/O input characteristics                                                          |    |

| Figure 40. | I/O AC characteristics definition 1                                                   |    |

| Figure 41. | Recommended NRST pin protection                                                       |    |

| Figure 42. | SPI timing diagram - slave mode and CPHA = 0                                          | 43 |

| Figure 43. | SPI timing diagram - slave mode and CPHA = $1^{(1)}$                                  | 43 |

| Figure 44. | SPI timing diagram - master mode <sup>(1)</sup> 1                                     | 44 |

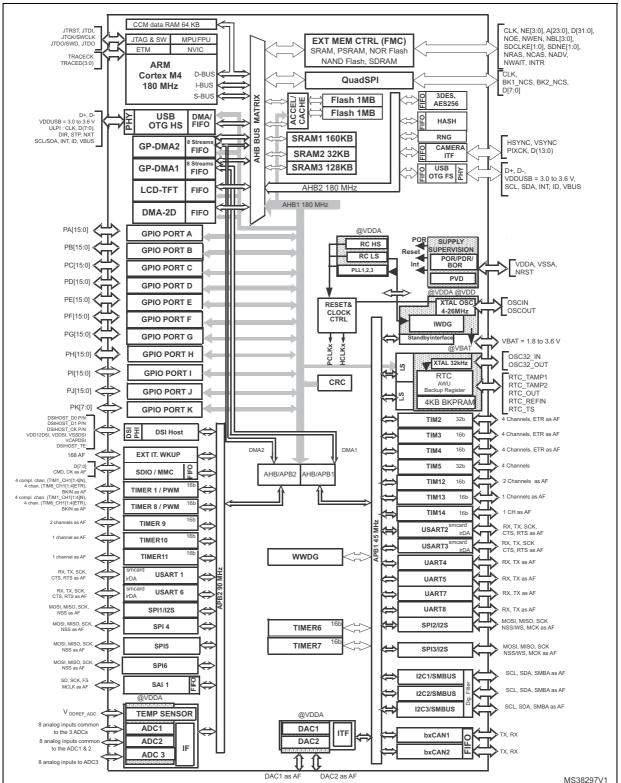

Figure 5. STM32F479xx block diagram

The timers connected to APB2 are clocked from TIMxCLK up to 180 MHz, while the timers connected to APB1 are clocked from TIMxCLK either up to 90 MHz or 180 MHz depending on TIMPRE bit configuration in the RCC\_DCKCFGR register.

## 2 Functional overview

## 2.1 **ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU and embedded Flash and SRAM**

The ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU processor is the latest generation of ARM processors for embedded systems. It was developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced response to interrupts.

The ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU core is a 32-bit RISC processor that features exceptional code-efficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices.

The processor supports a set of DSP instructions which allow efficient signal processing and complex algorithm execution.

Its single precision FPU (floating point unit) speeds up software development by using metalanguage development tools, while avoiding saturation.

The STM32F47x line is compatible with all ARM tools and software.

Figure 5 shows the general block diagram of the STM32F47x line.

Note: Cortex<sup>®</sup>-M4 with FPU core is binary compatible with the Cortex<sup>®</sup>-M3 core.

## 2.2 Adaptive real-time memory accelerator (ART Accelerator<sup>™</sup>)

The ART Accelerator<sup>™</sup> is a memory accelerator optimized for STM32 industry-standard ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU processors. It balances the inherent performance advantage of the ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU over Flash memory technologies, which normally require the processor to wait for the Flash memory at higher frequencies.

To release the processor full 225 DMIPS performance at this frequency, the accelerator implements an instruction prefetch queue and branch cache, which increases program execution speed from the 128-bit Flash memory. Based on CoreMark<sup>®</sup> benchmark, the performance achieved thanks to the ART Accelerator is equivalent to 0 wait state program execution from Flash memory at a CPU frequency up to 180 MHz.

## 2.3 Memory protection unit

The memory protection unit (MPU) is used to manage the CPU accesses to memory to prevent one task to accidentally corrupt the memory or resources used by any other active task. This memory area is organized into up to 8 protected areas that can in turn be divided up into 8 subareas. The protection area sizes are between 32 bytes and the whole 4 gigabytes of addressable memory.

The MPU is especially helpful for applications where some critical or certified code has to be protected against the misbehavior of other tasks. It is usually managed by an RTOS (real-time operating system). If a program accesses a memory location that is prohibited by the MPU, the RTOS can detect it and take action. In an RTOS environment, the kernel can dynamically update the MPU area setting, based on the process to be executed.

The MPU is optional and can be bypassed for applications that do not need it.

## 2.10 Quad-SPI memory interface (QUADSPI)

All STM32F479xx devices embeds a Quad-SPI memory interface, which is a specialized communication interface targeting Single, Dual, Quad or Dual-flash SPI memories. It can work in direct mode through registers, external flash status register polling mode and memory mapped mode. Up to 256 Mbytes external Flash memory are mapped, supporting 8, 16 and 32-bit access. Code execution is supported.

The opcode and the frame format are fully programmable. Communication can be either in Single Data Rate or Dual Data Rate.

## 2.11 LCD-TFT controller

The LCD-TFT display controller provides a 24-bit parallel digital RGB (Red, Green, Blue) and delivers all signals to interface directly to a broad range of LCD and TFT panels up to XGA (1024x768) resolution with the following features:

- 2 displays layers with dedicated FIFO (64x32-bit)

- Color Look-Up table (CLUT) up to 256 colors (256x24-bit) per layer

- Up to 8 Input color formats selectable per layer

- Flexible blending between two layers using alpha value (per pixel or constant)

- Flexible programmable parameters for each layer

- Color keying (transparency color)

- Up to 4 programmable interrupt events.

## 2.12 DSI Host (DSIHOST)

The DSI Host is a dedicated peripheral for interfacing with MIPI<sup>®</sup> DSI compliant displays. It includes a dedicated video interface internally connected to the LTDC and a generic APB interface that can be used to transmit information to the display.

These interfaces are as follows:

- LTDC interface:

- Used to transmit information in Video Mode, in which the transfers from the host processor to the peripheral take the form of a real-time pixel stream (DPI).

- Through a customized for mode, this interface can be used to transmit information in full bandwidth in the Adapted Command Mode (DBI).

- APB slave interface:

- Allows the transmission of generic information in Command mode, and follows a proprietary register interface.

- Can operate concurrently with either LTDC interface in either Video Mode or Adapted Command Mode.

- Video mode pattern generator:

- Allows the transmission of horizontal/vertical color bar and D-PHY BER testing pattern without any kind of stimuli.

## 2.19 Power supply supervisor

#### 2.19.1 Internal reset ON

On packages embedding the PDR\_ON pin, the power supply supervisor is enabled by holding PDR\_ON high. On the other package, the power supply supervisor is always enabled.

The device has an integrated power-on reset (POR)/ power-down reset (PDR) circuitry coupled with a Brownout reset (BOR) circuitry. At power-on, POR/PDR is always active and ensures proper operation starting from 1.8 V. After the 1.8 V POR threshold level is reached, the option byte loading process starts, either to confirm or modify default BOR thresholds, or to disable BOR permanently. Three BOR thresholds are available through option bytes. The device remains in reset mode when V<sub>DD</sub> is below a specified threshold,  $V_{POR/PDR}$  or  $V_{BOR}$ , without the need for an external reset circuit.

The device also features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

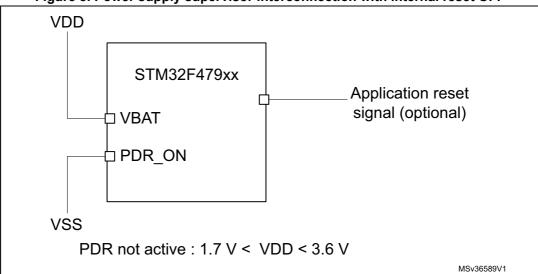

#### 2.19.2 Internal reset OFF

This feature is available only on packages featuring the PDR\_ON pin. The internal power-on reset (POR) / power-down reset (PDR) circuitry is disabled through the PDR\_ON pin.

An external power supply supervisor should monitor  $V_{DD}$  and NRST and should maintain the device in reset mode as long as  $V_{DD}$  is below a specified threshold. PDR\_ON must be connected to VSS, as shown in *Figure 8*.

Figure 8. Power supply supervisor interconnection with internal reset OFF

The  $V_{DD}$  specified threshold, below which the device must be maintained under reset, is 1.7 V (see *Figure 9*).

A comprehensive set of power-saving mode allows to design low-power applications.

DocID028010 Rev 4

### 2.21 Real-time clock (RTC), backup SRAM and backup registers

The backup domain includes:

- The real-time clock (RTC)

- 4 Kbytes of backup SRAM

- 20 backup registers

The real-time clock (RTC) is an independent BCD timer/counter. Dedicated registers contain the second, minute, hour (in 12/24 hour), week day, date, month, year, in BCD (binary-coded decimal) format. Correction for 28, 29 (leap year), 30, and 31 day of the month are performed automatically. The RTC provides a programmable alarm and programmable periodic interrupts with wakeup from Stop and Standby modes. The sub-seconds value is also available in binary format.

It is clocked by a 32.768 kHz external crystal, resonator or oscillator, the internal low-power RC oscillator or the high-speed external clock divided by 128. The internal low-speed RC has a typical frequency of 32 kHz. The RTC can be calibrated using an external 512 Hz output to compensate for any natural quartz deviation.

Two alarm registers are used to generate an alarm at a specific time and calendar fields can be independently masked for alarm comparison. To generate a periodic interrupt, a 16-bit programmable binary auto-reload downcounter with programmable resolution is available and allows automatic wakeup and periodic alarms from every 120 µs to every 36 hours.

A 20-bit prescaler is used for the time base clock. It is by default configured to generate a time base of 1 second from a clock at 32.768 kHz.

The 4-Kbyte backup SRAM is an EEPROM-like memory area. It can be used to store data which need to be retained in VBAT and standby mode. This memory area is disabled by default to minimize power consumption (see *Section 2.22*). It can be enabled by software.

The backup registers are 32-bit registers used to store 80 bytes of user application data when  $V_{DD}$  power is not present. Backup registers are not reset by a system, a power reset, or when the device wakes up from the Standby mode (see Section 2.22).

Additional 32-bit registers contain the programmable alarm subseconds, seconds, minutes, hours, day, and date.

Like backup SRAM, the RTC and backup registers are supplied through a switch that is powered either from the  $V_{DD}$  supply when present or from the  $V_{BAT}$  pin.

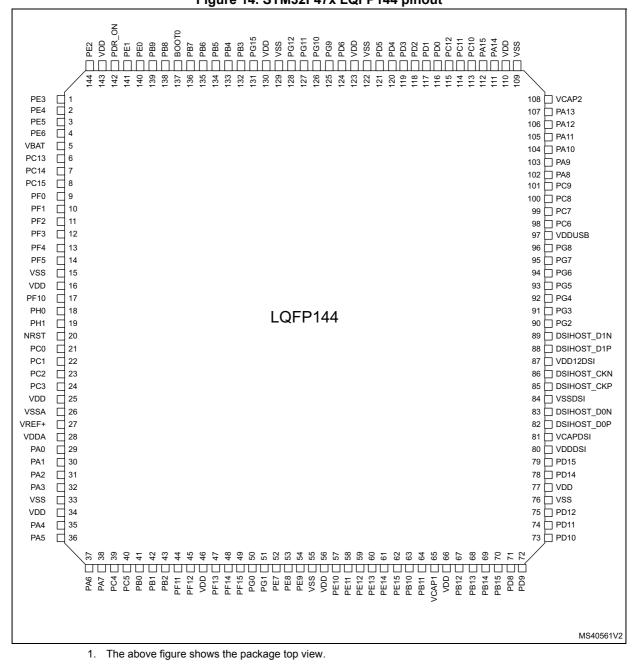

## Figure 14. STM32F47x LQFP144 pinout

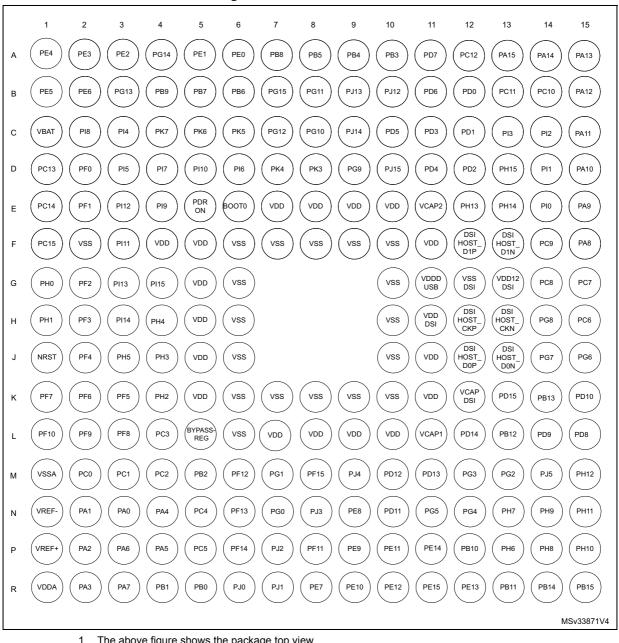

#### Figure 20. STM32F47x TFBGA216 ballout

1. The above figure shows the package top view.

| Bus  | Boundary address          | Peripheral               |

|------|---------------------------|--------------------------|

| -    | 0x4008 0000- 0x4FFF FFFF  | Reserved                 |

|      | 0x4004 0000 - 0x4007 FFFF | USB OTG HS               |

|      | 0x4002 BC00- 0x4003 FFFF  | Reserved                 |

|      | 0x4002 B000 - 0x4002 BBFF | Chrom (DMA2D)            |

|      | 0x4002 9400 - 0x4002 AFFF | Reserved                 |

|      | 0x4002 9000 - 0x4002 93FF |                          |

|      | 0x4002 8C00 - 0x4002 8FFF |                          |

|      | 0x4002 8800 - 0x4002 8BFF | ETHERNET MAC             |

|      | 0x4002 8400 - 0x4002 87FF |                          |

|      | 0x4002 8000 - 0x4002 83FF |                          |

|      | 0x4002 6800 - 0x4002 7FFF | Reserved                 |

|      | 0x4002 6400 - 0x4002 67FF | DMA2                     |

|      | 0x4002 6000 - 0x4002 63FF | DMA1                     |

|      | 0x4002 5000 - 0x4002 5FFF | Reserved                 |

|      | 0x4002 4000 - 0x4002 4FFF | BKPSRAM                  |

| AHB1 | 0x4002 3C00 - 0x4002 3FFF | Flash interface register |

| АПВТ | 0x4002 3800 - 0x4002 3BFF | RCC                      |

|      | 0x4002 3400 - 0x4002 37FF | Reserved                 |

|      | 0x4002 3000 - 0x4002 33FF | CRC                      |

|      | 0x4002 2C00 - 0x4002 2FFF | Reserved                 |

|      | 0x4002 2800 - 0x4002 2BFF | GPIOK                    |

|      | 0x4002 2400 - 0x4002 27FF | GPIOJ                    |

|      | 0x4002 2000 - 0x4002 23FF | GPIOI                    |

|      | 0x4002 1C00 - 0x4002 1FFF | GPIOH                    |

|      | 0x4002 1800 - 0x4002 1BFF | GPIOG                    |

|      | 0x4002 1400 - 0x4002 17FF | GPIOF                    |

|      | 0x4002 1000 - 0x4002 13FF | GPIOE                    |

|      | 0x4002 0C00 - 0x4002 0FFF | GPIOD                    |

|      | 0x4002 0800 - 0x4002 0BFF | GPIOC                    |

|      | 0x4002 0400 - 0x4002 07FF | GPIOB                    |

|      | 0x4002 0000 - 0x4002 03FF | GPIOA                    |

## Table 13. STM32F479xx register boundary addresses<sup>(1)</sup> (continued)

| Symbol | Parameter                         | Conditions |  |  |  |

|--------|-----------------------------------|------------|--|--|--|

| CEXT   | Capacitance of external capacitor | 2.2 μF     |  |  |  |

| ESR    | ESR of external capacitor         | < 2 Ω      |  |  |  |

#### Table 19. VCAP1/VCAP2 operating conditions<sup>(1)</sup>

1. When bypassing the voltage regulator, the two 2.2  $\mu$ F V<sub>CAP</sub> capacitors are not required and should be replaced by two 100 nF decoupling capacitors.

#### 5.3.3 Operating conditions at power-up / power-down (regulator ON)

Subject to general operating conditions for T<sub>A</sub>.

#### Table 20. Operating conditions at power-up / power-down (regulator ON)

| Symbol | Parameter                      | Min | Мах | Unit |

|--------|--------------------------------|-----|-----|------|

| +      | V <sub>DD</sub> rise time rate | 20  | ∞   | µs/V |

| tvdd   | V <sub>DD</sub> fall time rate | 20  | 8   | μ5/ν |

#### 5.3.4 Operating conditions at power-up / power-down (regulator OFF)

Subject to general operating conditions for  $T_A$ .

#### Table 21. Operating conditions at power-up / power-down (regulator OFF)<sup>(1)</sup>

| Symbol            | Parameter                                    | Conditions | Min | Max | Unit |

|-------------------|----------------------------------------------|------------|-----|-----|------|

| t <sub>VDD</sub>  | V <sub>DD</sub> rise time rate               | Power-up   | 20  | ~   |      |

|                   | V <sub>DD</sub> fall time rate               | Power-down | 20  | ~   | µs/V |

| +                 | $V_{CAP_1}$ and $V_{CAP_2}$ rise time rate   | Power-up   | 20  | ~   | μ5/ν |

| t <sub>VCAP</sub> | $V_{CAP\_1}$ and $V_{CAP\_2}$ fall time rate | Power-down | 20  | ∞   |      |

1. To reset the internal logic at power-down, a reset must be applied on pin PA0 when  $V_{\text{DD}}$  reach below 1.08 V.

#### 5.3.5 Reset and power control block characteristics

The parameters given in *Table 22* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 17*.

the current from the MCU supply voltage to supply the I/O pin circuitry and to charge/discharge the capacitive load (internal or external) connected to the pin:

$$I_{SW} = V_{DD} \times f_{SW} \times C$$

where

$I_{SW}$  is the current sunk by a switching I/O to charge/discharge the capacitive load  $V_{DD}$  is the MCU supply voltage

$f_{SW}$  is the I/O switching frequency

C is the total capacitance seen by the I/O pin: C =  $C_{INT}$ +  $C_{EXT}$

The test pin is configured in push-pull output mode and is toggled by software at a fixed frequency.

| Symbol            | Parameter                | Conditions                              | I/O toggling<br>frequency<br>(fsw) | Тур  | Unit |

|-------------------|--------------------------|-----------------------------------------|------------------------------------|------|------|

|                   |                          |                                         | 2 MHz                              | 0.0  |      |

|                   |                          |                                         | 8 MHz                              | 0.2  |      |

|                   |                          |                                         | 25 MHz                             | 0.6  |      |

|                   | I/O switching<br>Current | $V_{DD} = 3.3 V$<br>$C = C_{INT}^{(2)}$ | 50 MHz                             | 1.1  |      |

|                   |                          |                                         | 60 MHz                             | 1.3  |      |

|                   |                          |                                         | 84 MHz                             | 1.8  |      |

|                   |                          |                                         | 90 MHz                             | 1.9  | mA   |

| I <sub>DDIO</sub> |                          | V <sub>DD</sub> = 3.3 V                 | 2 MHz                              | 0.1  | IIIA |

|                   |                          |                                         | 8 MHz                              | 0.4  |      |

|                   |                          |                                         | 25 MHz                             | 1.23 |      |

|                   |                          | C <sub>EXT</sub> = 0 pF                 | 50 MHz                             | 2.43 |      |

|                   |                          | $C = C_{INT} + C_{EXT} + C_S$           | 60 MHz                             | 2.93 |      |

|                   |                          |                                         | 84 MHz                             | 3.86 |      |

|                   |                          |                                         | 90 MHz                             | 4.07 |      |

| Table 32. Switching output I/C | current consumption <sup>(1)</sup> |

|--------------------------------|------------------------------------|

|--------------------------------|------------------------------------|

### I<sup>2</sup>S interface characteristics

Unless otherwise specified, the parameters given in *Table 65* for the I<sup>2</sup>S interface are derived from tests performed under the ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 17*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5 V<sub>DD</sub>

Refer to Section 5.3.20 for more details on the input/output alternate function characteristics (CK, SD, WS).

| Symbol                 | Parameter                                                      | Conditions                                        | Min    | Max                   | Unit |

|------------------------|----------------------------------------------------------------|---------------------------------------------------|--------|-----------------------|------|

| f <sub>MCK</sub>       | I2S Main clock output                                          | -                                                 | 256x8K | 256xFs <sup>(2)</sup> |      |

| f                      | I2S clock frequency                                            | Master data                                       | -      | 64xFs                 | MHz  |

| f <sub>СК</sub>        | 125 Clock frequency                                            | Slave data                                        | -      | 64xFs                 |      |

| D <sub>CK</sub>        | I2S clock frequency duty cycle                                 | Slave receiver                                    | 30     | 70                    | %    |

| t <sub>v(WS)</sub>     | WS valid time                                                  | Master mode                                       | 0      | 5                     |      |

| t <sub>h(WS)</sub>     | WS hold time                                                   | Master mode                                       | 0      | -                     |      |

|                        |                                                                | Slave mode                                        | 3.5    | -                     |      |

| t <sub>su(WS)</sub>    | /S) WS setup time                                              | Slave mode<br>PCM short pulse mode <sup>(3)</sup> | 3.5    | -                     |      |

|                        | WS hold time Slave mode<br>PCM short pulse mode <sup>(3)</sup> | Slave mode                                        | 0.5    | -                     |      |

| t <sub>h(WS)</sub>     |                                                                |                                                   | 1      | -                     |      |

| t <sub>su(SD_MR)</sub> | Data input setup time                                          | Master receiver                                   | 5      | -                     | ns   |

| t <sub>su(SD_SR)</sub> | Data input setup time                                          | Slave receiver                                    | 1.5    | -                     |      |

| t <sub>h(SD_MR)</sub>  | Data input hold time                                           | Master receiver                                   | 5      | -                     |      |

| t <sub>h(SD_SR)</sub>  | Data input noid time                                           | Slave receiver                                    | 1.5    | -                     |      |

| t <sub>v(SD_ST)</sub>  | Data output valid time                                         | Slave transmitter (after enable edge)             | -      | 19                    |      |

| t <sub>v(SD_MT)</sub>  | Data output valid time                                         | Master transmitter (after enable edge)            | -      | 2.50                  |      |

| t <sub>h(SD_ST)</sub>  | Data output hold time                                          | Slave transmitter (after enable edge)             | 5      | -                     |      |

| t <sub>h(SD_MT)</sub>  |                                                                | Master transmitter (after enable edge)            | 0      | -                     |      |

#### Table 65. I<sup>2</sup>S dynamic characteristics<sup>(1)</sup>

1. Guaranteed based on test during characterization.

2. 128xFs maximum is 24.756 MHz (APB1 Maximum frequency).

3. Measurement done with respect to I2S\_CK rising edge.

Note:

Refer to the I2S section of RM0386 reference manual for more details on the sampling frequency (F<sub>S</sub>).

$f_{MCK}$ ,  $f_{CK}$ , and  $D_{CK}$  values reflect only the digital peripheral behavior, source clock precision might slightly change the values. The values of these parameters might be slightly impacted by the source clock precision.  $D_{CK}$  depends mainly on the value of ODD bit. The digital

DocID028010 Rev 4

# Table 91. Asynchronous non-multiplexed SRAM/PSRAM/NOR write - NWAIT timings<sup>(1)</sup>

| Symbol                    | Parameter                                 | Min                     | Мах                   | Unit |

|---------------------------|-------------------------------------------|-------------------------|-----------------------|------|

| t <sub>w(NE)</sub>        | FMC_NE low time                           | 8T <sub>HCLK</sub> +1   | 8T <sub>HCLK</sub> +2 |      |

| t <sub>w(NWE)</sub>       | FMC_NWE low time                          | 6T <sub>HCLK</sub> – 1  | 6T <sub>HCLK</sub> +2 | ns   |

| t <sub>su(NWAIT_NE)</sub> | FMC_NWAIT valid before FMC_NEx high       | 6T <sub>HCLK</sub> +1.5 | -                     | 110  |

| t <sub>h(NE_NWAIT)</sub>  | FMC_NEx hold time after FMC_NWAIT invalid | 4T <sub>HCLK</sub> +1   | -                     |      |

1. Based on test during characterization.

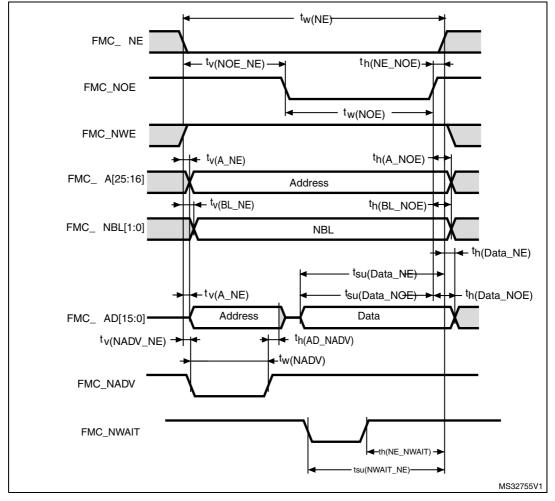

Figure 61. Asynchronous multiplexed PSRAM/NOR read waveforms

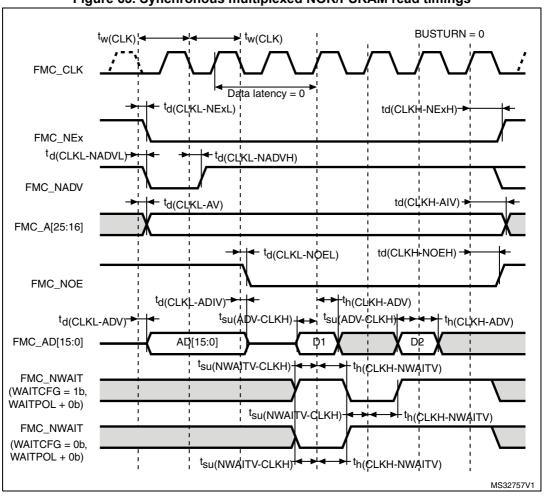

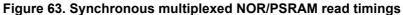

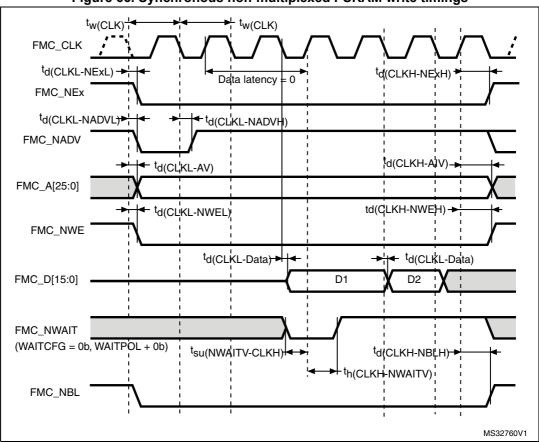

Table 99. Synchronous non-multiplexed PSRAM write timings<sup>(1)</sup>

| Symbol                      | Parameter                                | Min                    | Max | Unit |

|-----------------------------|------------------------------------------|------------------------|-----|------|

| t <sub>(CLK)</sub>          | FMC_CLK period                           | 2T <sub>HCLK</sub> – 1 | -   |      |

| t <sub>d(CLKL-NExL)</sub>   | FMC_CLK low to FMC_NEx low (x=02)        | -                      | 0.5 |      |

| t <sub>(CLKH-NExH)</sub>    | FMC_CLK high to FMC_NEx high (x= 02)     | T <sub>HCLK</sub>      | -   |      |

| t <sub>d(CLKL-NADVL)</sub>  | FMC_CLK low to FMC_NADV low              | -                      | 0   |      |

| t <sub>d(CLKL-NADVH)</sub>  | FMC_CLK low to FMC_NADV high             | 0                      | -   |      |

| t <sub>d(CLKL-AV)</sub>     | FMC_CLK low to FMC_Ax valid (x=1625)     | -                      | 0   |      |

| t <sub>d(CLKH-AIV)</sub>    | FMC_CLK high to FMC_Ax invalid (x=1625)  | 0                      | -   | ns   |

| t <sub>d(CLKL-NWEL)</sub>   | FMC_CLK low to FMC_NWE low               | -                      | 0   | 115  |

| t <sub>d(CLKH-NWEH)</sub>   | FMC_CLK high to FMC_NWE high             | T <sub>HCLK</sub> -0.5 | -   |      |

| t <sub>d(CLKL-Data)</sub>   | FMC_D[15:0] valid data after FMC_CLK low | -                      | 2.5 |      |

| t <sub>d(CLKL-NBLL)</sub>   | FMC_CLK low to FMC_NBL low               | 0                      | -   | Ī    |

| t <sub>d(CLKH-NBLH)</sub>   | FMC_CLK high to FMC_NBL high             | T <sub>HCLK</sub> -0.5 | -   |      |

| t <sub>su(NWAIT-CLKH)</sub> | FMC_NWAIT valid before FMC_CLK high      | 4                      | -   |      |

| t <sub>h(CLKH-NWAIT)</sub>  | FMC_NWAIT valid after FMC_CLK high       | 0                      | -   |      |

1. Based on test during characterization.

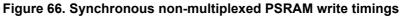

### 5.3.30 Quad-SPI interface characteristics

Unless otherwise specified, the parameters given in *Table 106* and *Table 107* for Quad-SPI are derived from tests performed under the ambient temperature,  $f_{AHB}$  frequency and  $V_{DD}$  supply voltage conditions summarized in Table xx, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 11

- Measurement points are done at CMOS levels: 0.5 V<sub>DD</sub>

Refer to *Section 5.3.20* for more details on the input/output alternate function characteristics.

| Symbol                                 | Parameter                | Test conditions                                                                                  | Min                    | Тур | Max                    | Unit |

|----------------------------------------|--------------------------|--------------------------------------------------------------------------------------------------|------------------------|-----|------------------------|------|

| F <sub>ck</sub><br>1/t <sub>(CK)</sub> | Qued CDL clock frequency | $2.7 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}, \text{ C}_{\text{L}} = 20 \text{ pF}$ | -                      | -   | 90                     |      |

|                                        | Quad-SPI clock frequency | 1.71 V ≤ V <sub>DD</sub> ≤ 3.6 V, C <sub>L</sub> = 15 pF                                         | -                      | -   | 84                     | MHz  |

| t <sub>w(CKH)</sub>                    | Quad-SPI clock high time | -                                                                                                | t <sub>(CK)</sub> /2-1 | -   | t <sub>(CK)</sub> /2   |      |

| t <sub>w(CKL)</sub>                    | Quad-SPI clock low time  | -                                                                                                | t <sub>(CK)</sub> /2   | -   | t <sub>(CK)</sub> /2+1 |      |

| t <sub>s(IN)</sub>                     | Data input set-up time   | -                                                                                                | 0.5                    | -   | -                      | ns   |

| t <sub>h(IN)</sub>                     | Data input hold time     | -                                                                                                | 3                      | -   | -                      | 115  |

| t <sub>v(OUT)</sub>                    | Data output valid time   | -                                                                                                | -                      | 3   | 4                      |      |

| t <sub>h(OUT)</sub>                    | Data output hold time    | -                                                                                                | 2.5                    | -   | -                      |      |

| Table 106. Quad-SPI characteristics in SDR mode <sup>(1)</sup> | Table 106. | Quad-SPI | characteristics | in | SDR mode <sup>(1)</sup> |

|----------------------------------------------------------------|------------|----------|-----------------|----|-------------------------|

|----------------------------------------------------------------|------------|----------|-----------------|----|-------------------------|

1. Guaranteed based on test during characterization.

#### Figure 73. Quad-SPI SDR timing diagram

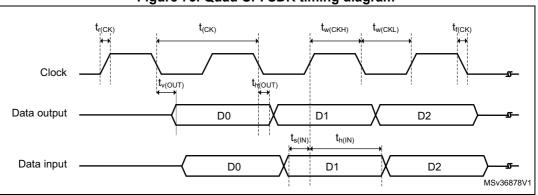

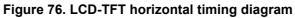

| Symbol                                       | Parameter                        | Min                          | Мах                        | Unit |

|----------------------------------------------|----------------------------------|------------------------------|----------------------------|------|

| f <sub>CLK</sub>                             | LTDC clock output frequency      | -                            | 65                         | MHz  |

| D <sub>CLK</sub>                             | LTDC clock output duty cycle     | 45                           | 55                         | %    |

| t <sub>w(CLKH)</sub><br>t <sub>w(CLKL)</sub> | Clock High time, low time        | t <sub>w(CLK)</sub> /2 – 0.5 | t <sub>w(CLK)</sub> /2+0.5 |      |

| t <sub>v(DATA)</sub>                         | Data output valid time           | -                            | 1.5                        |      |

| t <sub>h(DATA)</sub>                         | Data output hold time            | 0                            | -                          |      |

| t <sub>v(HSYNC)</sub>                        |                                  |                              |                            |      |

| t <sub>v(VSYNC)</sub>                        | HSYNC/VSYNC/DE output valid time | -                            | 0.5                        | ns   |

| t <sub>v(DE)</sub>                           |                                  |                              |                            |      |

| t <sub>h(HSYNC)</sub>                        |                                  |                              |                            |      |

| t <sub>h(VSYNC)</sub>                        | HSYNC/VSYNC/DE output hold time  | 0                            | -                          |      |

| th(DE)                                       |                                  |                              |                            |      |

Table 109. LTDC characteristics<sup>(1)</sup>

1. Based on test during characterization.

usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

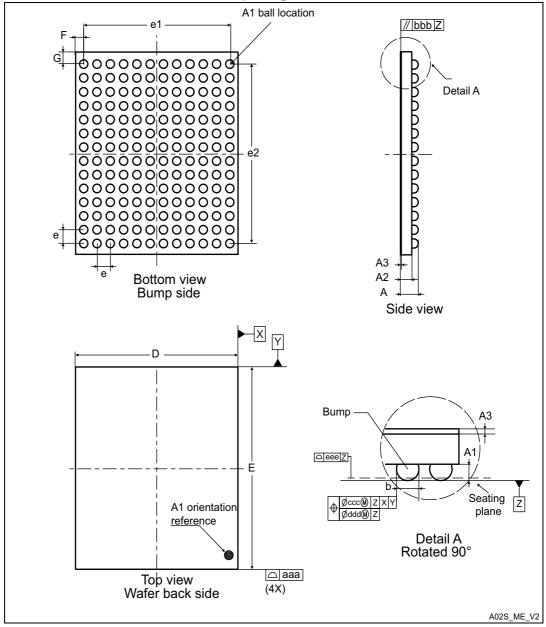

## 6.3 WLCSP168 package information

Figure 86. WLCSP168 - 168-pin, 4.891 x 5.692 mm, 0.4 mm pitch wafer level chip scale package outline

| package mechanical data |             |        |       |                       |        |        |  |  |  |

|-------------------------|-------------|--------|-------|-----------------------|--------|--------|--|--|--|

| Symbol -                | millimeters |        |       | inches <sup>(1)</sup> |        |        |  |  |  |

|                         | Min         | Тур    | Мах   | Min                   | Тур    | Max    |  |  |  |

| А                       | 0.525       | 0.555  | 0.585 | 0.0207                | 0.0219 | 0.0230 |  |  |  |

| A1                      | -           | 0.170  | -     | -                     | 0.0067 | -      |  |  |  |

| A2                      | -           | 0.380  | -     | -                     | 0.0150 | -      |  |  |  |

| A3 <sup>(2)</sup>       | -           | 0.025  | -     | -                     | 0.0010 | -      |  |  |  |

| b <sup>(3)</sup>        | 0.220       | 0.250  | 0.280 | 0.0087                | 0.0098 | 0.0110 |  |  |  |

| D                       | 4.856       | 4.891  | 4.926 | 0.1912                | 0.1926 | 0.1939 |  |  |  |

| E                       | 5.657       | 5.692  | 5.727 | 0.2227                | 0.2241 | 0.2255 |  |  |  |

| е                       | -           | 0.400  | -     | -                     | 0.0157 | -      |  |  |  |

| e1                      | -           | 4.400  | -     | -                     | 0.1732 | -      |  |  |  |

| e2                      | -           | 5.200  | -     | -                     | 0.2047 | -      |  |  |  |

| F                       | -           | 0.2455 | -     | -                     | 0.0097 | -      |  |  |  |

| G                       | -           | 0.246  | -     | -                     | 0.0097 | -      |  |  |  |

| aaa                     | -           | -      | 0.100 | -                     | -      | 0.0039 |  |  |  |

| bbb                     | -           | -      | 0.100 | -                     | -      | 0.0039 |  |  |  |

| ссс                     | -           | -      | 0.100 | -                     | -      | 0.0039 |  |  |  |

| ddd                     | -           | -      | 0.050 | -                     | -      | 0.0020 |  |  |  |

| eee                     | -           | -      | 0.050 | -                     | -      | 0.0020 |  |  |  |

# Table 115. WLCSP168 - 168-pin, 4.891 x 5.692 mm, 0.4 mm pitch wafer level chip scalepackage mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. Back side coating.

3. Dimension is measured at the maximum bump diameter parallel to primary datum Z.

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2017 STMicroelectronics – All rights reserved

DocID028010 Rev 4