# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                                    |

|----------------------------|-------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                        |

| Speed                      | 180MHz                                                                                    |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, SAI, SDIO, SPI, UART/USART, USB, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                         |

| Number of I/O              | 131                                                                                       |

| Program Memory Size        | 2MB (2M x 8)                                                                              |

| Program Memory Type        | FLASH                                                                                     |

| EEPROM Size                | -                                                                                         |

| RAM Size                   | 384K x 8                                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                               |

| Data Converters            | A/D 20x12b; D/A 2x12b                                                                     |

| Oscillator Type            | Internal                                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                         |

| Mounting Type              | Surface Mount                                                                             |

| Package / Case             | 144-LQFP                                                                                  |

| Supplier Device Package    | 144-LQFP (20x20)                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f479zit6                     |

|                            |                                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| 1 | Desc | ription                                                                                        | 12   |

|---|------|------------------------------------------------------------------------------------------------|------|

|   | 1.1  | Compatibility throughout the family                                                            | 15   |

|   |      | 1.1.1 LQFP176 package                                                                          | . 16 |

|   |      | 1.1.2 LQFP208 package                                                                          | . 17 |

|   |      | 1.1.3 UFBGA176 package                                                                         |      |

|   |      | 1.1.4 TFBGA216 package                                                                         | . 19 |

| 2 | Func | tional overview                                                                                | 21   |

|   | 2.1  | $ARM^{	extsf{B}}$ Cortex <sup>®</sup> -M4 with FPU and embedded Flash and SRAM $\ldots \ldots$ | 21   |

|   | 2.2  | Adaptive real-time memory accelerator (ART Accelerator™)                                       | 21   |

|   | 2.3  | Memory protection unit                                                                         | 21   |

|   | 2.4  | Embedded Flash memory                                                                          | 22   |

|   | 2.5  | CRC (cyclic redundancy check) calculation unit                                                 | 22   |

|   | 2.6  | Embedded SRAM                                                                                  | 22   |

|   | 2.7  | Multi-AHB bus matrix                                                                           | 22   |

|   | 2.8  | DMA controller (DMA)                                                                           | 23   |

|   | 2.9  | Flexible Memory Controller (FMC)                                                               | 24   |

|   | 2.10 | Quad-SPI memory interface (QUADSPI)                                                            | 25   |

|   | 2.11 | LCD-TFT controller                                                                             | 25   |

|   | 2.12 | DSI Host (DSIHOST)                                                                             | 25   |

|   | 2.13 | Chrom-ART Accelerator™ (DMA2D)                                                                 | 27   |

|   | 2.14 | Nested vectored interrupt controller (NVIC)                                                    | 27   |

|   | 2.15 | External interrupt/event controller (EXTI)                                                     | 27   |

|   | 2.16 | Clocks and startup                                                                             | 28   |

|   | 2.17 | Boot modes                                                                                     | 28   |

|   | 2.18 | Power supply schemes                                                                           | 28   |

|   | 2.19 | Power supply supervisor                                                                        | 30   |

|   |      | 2.19.1 Internal reset ON                                                                       | . 30 |

|   |      | 2.19.2 Internal reset OFF                                                                      | . 30 |

|   | 2.20 | Voltage regulator                                                                              | 31   |

|   |      | 2.20.1 Regulator ON                                                                            | . 31 |

|   |      | 2.20.2 Regulator OFF                                                                           | . 32 |

# 2.32 Secure digital input/output interface (SDIO)

An SD/SDIO/MMC host interface is available, that supports MultiMediaCard System Specification Version 4.2 in three different databus modes: 1-bit (default), 4-bit and 8-bit.

The interface allows data transfer at up to 48 MHz, and is compliant with the SD Memory Card Specification Version 2.0.

The SDIO Card Specification Version 2.0 is also supported with two different databus modes: 1-bit (default) and 4-bit.

The current version supports only one SD/SDIO/MMC4.2 card at any one time and a stack of MMC4.1 or previous.

In addition to SD/SDIO/MMC, this interface is fully compliant with the CE-ATA digital protocol Rev1.1.

# 2.33 Ethernet MAC interface with dedicated DMA and IEEE 1588 support

The devices provide an IEEE-802.3-2002-compliant media access controller (MAC) for ethernet LAN communications through an industry-standard medium-independent interface (MII) or a reduced medium-independent interface (RMII). The microcontroller requires an external physical interface device (PHY) to connect to the physical LAN bus (twisted-pair, fiber, etc.). The PHY is connected to the device MII port using 17 signals for MII or 9 signals for RMII, and can be clocked using the 25 MHz (MII) from the microcontroller.

The devices include the following features:

- Supports 10 and 100 Mbit/s rates

- Dedicated DMA controller allowing high-speed transfers between the dedicated SRAM and the descriptors (see the STM32F4xx reference manual for details)

- Tagged MAC frame support (VLAN support)

- Half-duplex (CSMA/CD) and full-duplex operation

- MAC control sublayer (control frames) support

- 32-bit CRC generation and removal

- Several address filtering modes for physical and multicast address (multicast and group addresses)

- 32-bit status code for each transmitted or received frame

- Internal FIFOs to buffer transmit and receive frames. The transmit FIFO and the receive FIFO are both 2 Kbytes.

- Supports hardware PTP (precision time protocol) in accordance with IEEE 1588 2008 (PTP V2) with the time stamp comparator connected to the TIM2 input

- Triggers interrupt when system time becomes greater than target time

# 2.34 Controller area network (bxCAN)

The two CANs are compliant with the 2.0A and B (active) specifications with a bitrate up to 1 Mbit/s. They can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers. Each CAN has three transmit mailboxes, two receive

Universal hash

- SHA-1 and SHA-2 (secure hash algorithms)

- MD5

- HMAC

The cryptographic accelerator supports DMA request generation.

# 2.39 Random number generator (RNG)

All devices embed an RNG that delivers 32-bit random numbers generated by an integrated analog circuit.

# 2.40 General-purpose input/outputs (GPIOs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain, with or without pull-up or pull-down), as input (floating, with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions. All GPIOs are high-current-capable and have speed selection to better manage internal noise, power consumption and electromagnetic emission.

The I/O configuration can be locked if needed by following a specific sequence in order to avoid spurious writing to the I/Os registers.

Fast I/O handling allowing maximum I/O toggling up to 90 MHz.

# 2.41 Analog-to-digital converters (ADCs)

Three 12-bit analog-to-digital converters are embedded and each ADC shares up to 16 external channels, performing conversions in the single-shot or scan mode. In scan mode, automatic conversion is performed on a selected group of analog inputs.

Additional logic functions embedded in the ADC interface allow:

- Simultaneous sample and hold

- Interleaved sample and hold

The ADC can be served by the DMA controller. An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

To synchronize A/D conversion and timers, the ADCs could be triggered by any of TIM1, TIM2, TIM3, TIM4, TIM5, or TIM8 timer.

## 2.42 Temperature sensor

The temperature sensor has to generate a voltage that varies linearly with temperature. The conversion range is between 1.7 V and 3.6 V. The temperature sensor is internally connected to the same input channel as V<sub>BAT</sub>, ADC1\_IN18, which is used to convert the sensor output voltage into a digital value. When the temperature sensor and V<sub>BAT</sub> conversion are enabled at the same time, only V<sub>BAT</sub> conversion is performed.

DocID028010 Rev 4

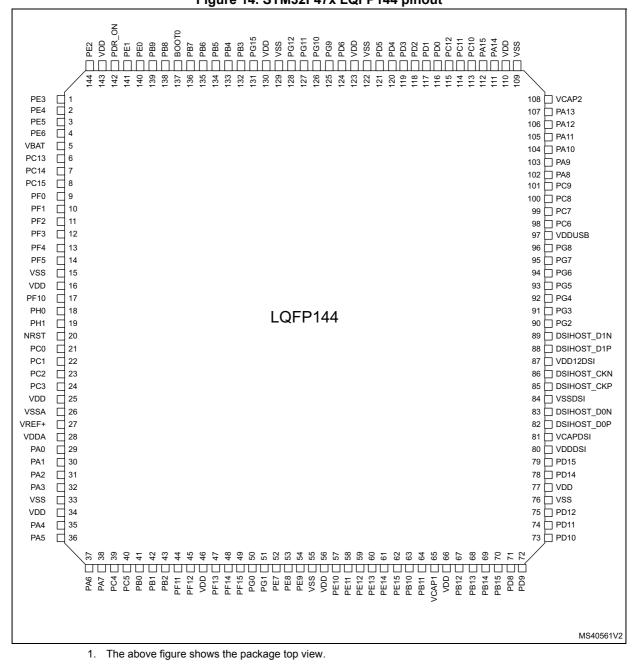

# Figure 14. STM32F47x LQFP144 pinout

- If the device is delivered in an WLCSP168, UFBGA169, UFBGA176, LQFP176 or TFBGA216 package, and the BYPASS\_REG pin is set to VDD (Regulator OFF/internal reset ON mode), then PA0 is used as an internal Reset (active low).

- 7. PI0 and PI1 cannot be used for I2S2 full-duplex mode.

| ST   |  |

|------|--|

| M3   |  |

| 2F4  |  |

| 1793 |  |

| Ž    |  |

Pinouts and pin description

|                   | _      |      |     |        |              |                  | Г        | able 12.              | Alterna         | te funct                  | ion (co                            | ontinued                                       | )                                       |                   |                              |                      |               |               |

|-------------------|--------|------|-----|--------|--------------|------------------|----------|-----------------------|-----------------|---------------------------|------------------------------------|------------------------------------------------|-----------------------------------------|-------------------|------------------------------|----------------------|---------------|---------------|

| 5                 |        |      | AF0 | AF1    | AF2          | AF3              | AF4      | AF5                   | AF6             | AF7                       | AF8                                | AF9                                            | AF10                                    | AF11              | AF12                         | AF13                 | AF14          | AF15          |

|                   | P      | ort  | SYS | TIM1/2 | TIM3/4/<br>5 | TIM8/9/<br>10/11 | I2C1/2/3 | SPI1/2/3<br>/4/5/6    | SPI2/3/<br>SAI1 | SPI2/3/<br>USART<br>1/2/3 | USAR<br>T6/<br>UART<br>4/5/7/<br>8 | CAN1/2/<br>TIM12/<br>13/14/<br>QUAD<br>SPI/LCD | QUAD<br>SPI/OT<br>G2_HS<br>/OTG1<br>_FS | ETH               | FMC/<br>SDIO/<br>OTG2_<br>FS | DCMI/<br>DSI<br>HOST | LCD           | SYS           |

|                   |        | PI0  | -   | -      | TIM5_CH4     | -                | -        | SPI2_NSS/I<br>2S2_WS  | -               | -                         | -                                  | -                                              | -                                       | -                 | FMC_D24                      | DCMI_D13             | LCD_G5        | EVENT<br>OUT  |

|                   |        | PI1  | -   | -      | -            | -                | -        | SPI2_SCK/I<br>2S2_CK  | -               | -                         | -                                  | -                                              | -                                       | -                 | FMC_D25                      | DCMI_D8              | LCD_G6        | EVENT<br>OUT  |

|                   |        | PI2  | -   | -      | -            | TIM8_CH4         | -        | SPI2_MISO             | I2S2ext_S<br>D  | -                         | -                                  | -                                              | -                                       | -                 | FMC_D26                      | DCMI_D9              | LCD_G7        | EVENT<br>OUT  |

|                   |        | PI3  | -   | -      | -            | TIM8_ETR         | -        | SPI2_MOSI<br>/I2S2_SD | -               | -                         | -                                  | -                                              | -                                       | -                 | FMC_D27                      | DCMI_D10             |               | EVENT<br>OUT  |

| _                 |        | PI4  | -   | -      | -            | TIM8_BKI<br>N    | -        | -                     | -               | -                         | -                                  | -                                              | -                                       | -                 | FMC_NBL2                     | DCMI_D5              | LCD_B4        | EVENT<br>OUT  |

| DocID028010 Rev 4 |        | PI5  | -   | -      | -            | TIM8_CH1         | -        | -                     | -               | -                         | -                                  | -                                              | -                                       | -                 | FMC_NBL3                     | DCMI_VS<br>YNC       | LCD_B5        | EVENT<br>OUT  |

| 0280              |        | PI6  | -   | -      | -            | TIM8_CH2         | -        | -                     | -               | -                         | -                                  | -                                              | -                                       | -                 | FMC_D28                      | DCMI_D6              | LCD_B6        | EVENT<br>OUT  |

| 10 R              |        | PI7  | -   | -      | -            | TIM8_CH3         | -        | -                     | -               | -                         | -                                  | -                                              | -                                       | -                 | FMC_D29                      | DCMI_D7              | LCD_B7        | EVENT<br>OUT  |

| ev 4              | Port I | PI8  | -   | -      | -            | -                | -        | -                     | -               | -                         | -                                  | -                                              | -                                       | -                 | -                            | -                    |               | EVENT<br>OUT  |

|                   |        | PI9  | -   | -      | -            | -                | -        | -                     | -               | -                         | -                                  | CAN1_RX                                        | -                                       | -                 | FMC_D30                      | -                    | LCD_VSY<br>NC | EVENT<br>OUT  |

|                   |        | PI10 | -   | -      | -            | -                | -        | -                     | -               | -                         | -                                  | -                                              | -                                       | ETH_MII_RX_<br>ER | FMC_D31                      | -                    | LCD_HSY<br>NC | EVENT<br>OUT  |

|                   |        | PI11 | -   | -      | -            | -                | -        | -                     | -               | -                         | -                                  | LCD_G6                                         | OTG_HS<br>_ULPI<br>_DIR                 | -                 | -                            | -                    | -             | EVENT<br>OUT  |

|                   |        | PI12 | -   | -      | -            | -                | -        | -                     | -               | -                         | -                                  | -                                              | -                                       | -                 | -                            | -                    | LCD_HSY<br>NC | EVENT<br>OUT  |

|                   |        | PI13 | -   | -      | -            | -                | -        | -                     | -               | -                         | -                                  | -                                              | -                                       | -                 | -                            | -                    | LCD_VSY<br>NC | EVENT<br>OUT  |

|                   |        | PI14 | -   | -      | -            | -                | -        | -                     | -               | -                         | -                                  | -                                              | -                                       | -                 | -                            | -                    | LCD_CLK       | EVENT<br>OUT  |

|                   |        | PI15 | -   | -      | -            | -                | -        | -                     | -               | -                         | -                                  | LCD_G2                                         | -                                       | -                 | -                            | -                    | LCD_R0        | EVENT<br>'OUT |

81/217

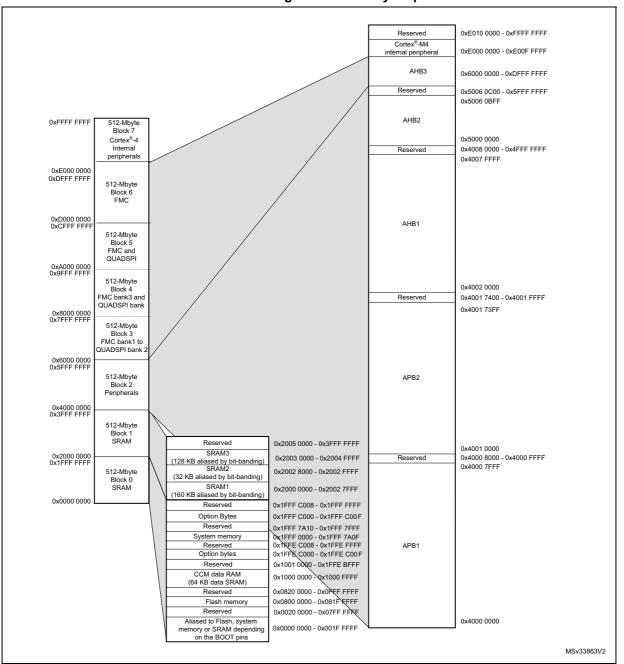

# 4 Memory mapping

The memory map is shown in *Figure 21*.

Figure 21. Memory map

DocID028010 Rev 4

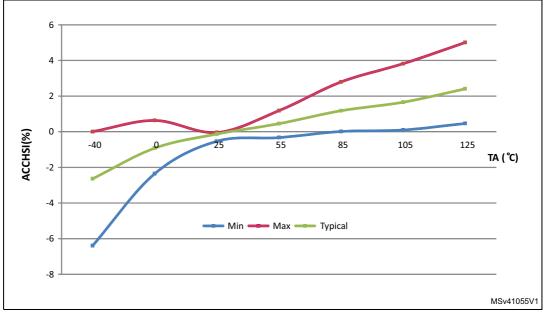

### 5.3.10 Internal clock source characteristics

The parameters given in *Table 39* and *Table 40* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 17*.

### High-speed internal (HSI) RC oscillator

| Symbol                              | Parameter                             | Conditions                            | Min | Тур | Max | Unit |

|-------------------------------------|---------------------------------------|---------------------------------------|-----|-----|-----|------|

| f <sub>HSI</sub>                    | Frequency                             | -                                     | -   | 16  | -   | MHz  |

| ACC <sub>HSI</sub>                  | HSI user trimming step <sup>(2)</sup> | -                                     | -   | -   | 1   | %    |

|                                     |                                       | $T_A = -40$ to 105 °C <sup>(3)</sup>  | - 8 | -   | 4.5 | %    |

|                                     | HSI oscillator accuracy               | $T_A = -10$ to 85 °C <sup>(3)</sup>   | - 4 | -   | 4   | %    |

|                                     |                                       | T <sub>A</sub> = 25 °C <sup>(4)</sup> | - 1 | -   | 1   | %    |

| t <sub>su(HSI)</sub> <sup>(2)</sup> | HSI oscillator startup time           | -                                     | -   | 2.2 | 4   | μs   |

| I <sub>DD(HSI)</sub> <sup>(2)</sup> | HSI oscillator power consumption      | -                                     | -   | 60  | 80  | μA   |

| Table 39. HS | l oscillator | characteristics | (1) |

|--------------|--------------|-----------------|-----|

|--------------|--------------|-----------------|-----|

1.  $V_{DD}$  = 3.3 V,  $T_A$  = -40 to 105 °C unless otherwise specified.

2. Guaranteed by design

3. Based on test during characterization.

4. Factory calibrated, parts not soldered.

### Figure 33. ACCHSI vs. temperature

1. Based on test during characterization.

| Symbol                               | Parameter                                                   | Condi                            | Min          | Тур          | Max  | Unit         |    |

|--------------------------------------|-------------------------------------------------------------|----------------------------------|--------------|--------------|------|--------------|----|

| +                                    | PLL lock time                                               | VCO freq = 192                   | MHz          | 75           | -    | 200          |    |

| t <sub>LOCK</sub>                    |                                                             | VCO freq = 432                   | MHz          | 100          | -    | 300          | μs |

|                                      | Cycle-to-cycle jitter                                       |                                  | RMS          | -            | 25   | -            |    |

|                                      |                                                             | System clock                     | peak to peak | -            | ±150 | -            |    |

| Jitter <sup>(3)</sup>                | Period Jitter                                               | 120 MHz                          | RMS          | -            | 15   | -            |    |

|                                      |                                                             |                                  | peak to peak | -            | ±200 | -            |    |

|                                      | Main clock output (MCO) for RMII<br>Ethernet                | Cycle to cycle a 1000 samples    | -            | 32           | -    | ps           |    |

|                                      | Main clock output (MCO) for MII<br>Ethernet                 | Cycle to cycle a 1000 samples    | -            | 40           | -    |              |    |

|                                      | Bit Time CAN jitter Cycle to cycle at 1 MH:<br>1000 samples |                                  | t 1 MHz on   | -            | 330  | -            |    |

| I <sub>DD(PLL)</sub> <sup>(4)</sup>  | PLL power consumption on VDD                                | VCO freq = 192 MHz               |              | 0.15         | _    | 0.40         |    |

| יטט(PLL)                             |                                                             | VCO freq = 432                   | 0.45         |              | 0.75 | mA           |    |

| I <sub>DDA(PLL)</sub> <sup>(4)</sup> | PLL power consumption on VDDA                               | VCO freq = 192<br>VCO freq = 432 |              | 0.30<br>0.55 | -    | 0.40<br>0.85 |    |

### Table 41. Main PLL characteristics (continued)

1. Take care of using the appropriate division factor M to obtain the specified PLL input clock values. The M factor is shared between PLL and PLLI2S.

2. Guaranteed by design.

3. The use of 2 PLLs in parallel can degrade the Jitter up to +30%.

4. Based on test during characterization.

| Symbol                  | Parameter                         | Condition                                                | Min          | Тур | Max  | Unit |     |

|-------------------------|-----------------------------------|----------------------------------------------------------|--------------|-----|------|------|-----|

| f <sub>PLLI2S_IN</sub>  | PLLI2S input clock <sup>(1)</sup> | -                                                        | -            |     |      | 2.10 |     |

| f <sub>PLLI2S_OUT</sub> | PLLI2S multiplier output<br>clock | -                                                        |              | -   | -    | 216  | MHz |

| f <sub>VCO_OUT</sub>    | PLLI2S VCO output                 | -                                                        | -            |     | -    | 432  |     |

| +                       | PLLI2S lock time                  | VCO freq = 192 MHz                                       | 75           | -   | 200  | μs   |     |

| t <sub>LOCK</sub>       | FLLIZS IOCK UITIE                 | VCO freq = 432 MHz                                       | 100          | -   | 300  |      |     |

|                         |                                   | Cycle to cycle at                                        | RMS          | -   | 90   | -    | -   |

|                         | Master 120 slask ütter            | 12.288 MHz on 48KHz<br>period, N=432, R=5                | peak to peak | -   | ±280 | -    | ps  |

| Jitter <sup>(3)</sup>   | Master I2S clock jitter           | Average frequency of 12<br>N=432, R=5<br>on 1000 samples | -            | 90  | -    | ps   |     |

|                         | WS I2S clock jitter               | Cycle to cycle at 48 KHz<br>on 1000 samples              | -            | 400 | -    | ps   |     |

### Table 42. PLLI2S (audio PLL) characteristics

| Symbol                                                 | Parameter                                                                                                                                            | Conditions | Min                           | Тур | Max            | Unit |

|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------------------|-----|----------------|------|

| T <sub>LPX</sub>                                       | Transmitted length of any Low-<br>Power state period                                                                                                 | -          | 50                            | -   | -              |      |

| T <sub>CLK-PREPARE</sub>                               | Time that the transmitter drives<br>the Clock Lane LP-00 Line<br>state immediately before the<br>HS-0 Line state starting the HS<br>transmission.    | -          | 38                            | -   | 95             | ns   |

| T <sub>CLK-PREPARE</sub><br>+<br>T <sub>CLK-ZERO</sub> | Time that the transmitter drives<br>the HS-0 state prior to starting<br>the clock.                                                                   | -          | 300                           | -   | -              |      |

| T <sub>CLK-PRE</sub>                                   | Time that the HS clock shall be<br>driven by the transmitter prior to<br>any associated Data Lane<br>beginning the transition from<br>LP to HS mode. | -          | 8                             | -   | -              | UI   |

| T <sub>CLK-POST</sub>                                  | Time that the transmitter<br>continues to send HS clock<br>after the last associated Data<br>Lane has transitioned to LP<br>Mode.                    | -          | 62+52*UI                      | -   | -              |      |

| T <sub>CLK-TRAIL</sub>                                 | Time that the transmitter drives<br>the HS-0 state after the last<br>payload clock bit of an HS<br>transmission burst.                               | -          | 60                            | -   | -              |      |

| T <sub>HS-PREPARE</sub>                                | Time that the transmitter drives<br>the Data Lane LP-00 Line state<br>immediately before the HS-0<br>Line state starting the HS<br>transmission.     | -          | 40+4*UI                       | -   | 85+6*UI        |      |

| T <sub>HS-PREPARE</sub><br>+<br>T <sub>HS-ZERO</sub>   | T <sub>HS-PREPARE+</sub> Time that the transmitter drives the HS-0 state prior to transmitting the Sync sequence.                                    | -          | 145+10*UI                     | -   | -              | ns   |

| T <sub>HS-TRAIL</sub>                                  | Time that the transmitter drives<br>the flipped differential state<br>after last payload data bit of a<br>HS transmission burst.                     | -          | Max<br>(n*8*UI,<br>60+n*4*UI) | -   | -              |      |

| T <sub>HS-EXIT</sub>                                   | Time that the transmitter drives LP-11 following a HS burst.                                                                                         | -          | 100                           | -   | -              |      |

| T <sub>REOT</sub>                                      | 30%-85% rise time and fall time                                                                                                                      | -          | -                             | -   | 35             | 1    |

| Т <sub>ЕОТ</sub>                                       | Transmitted time interval from<br>the start of $T_{HS-TRAIL}$ or<br>$T_{CLK-TRAIL}$ , to the start of the<br>LP-11 state following a HS<br>burst.    | -          | -                             | -   | 105+<br>n*12UI |      |

1. Guaranteed based on test during characterization.

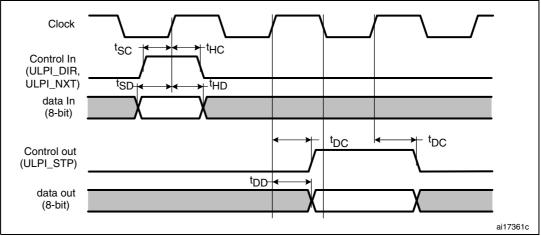

| Symbol                  | Parameter                                                                 | Min              | Тур   | Max    | Unit  |     |  |

|-------------------------|---------------------------------------------------------------------------|------------------|-------|--------|-------|-----|--|

| -                       | f <sub>HCLK</sub> value to guarantee proper operation of USB HS interface |                  | 30    | -      | -     |     |  |

| F <sub>START_8BIT</sub> | Frequency (first transition)                                              | 8-bit ±10%       | 54    | 60     | 66    | MHz |  |

| F <sub>STEADY</sub>     | Frequency (steady state) ±500                                             | ) ppm            | 59.97 | 60     | 60.03 |     |  |

| D <sub>START_8BIT</sub> | Duty cycle (first transition)                                             | 8-bit ±10%       | 40    | 50     | 60    | %   |  |

| D <sub>STEADY</sub>     | Duty cycle (steady state) ±500                                            | 49.975           | 50    | 50.025 | 70    |     |  |

| t <sub>STEADY</sub>     | Time to reach the steady state duty cycle after the first transiti        | -                | -     | 1.4    | ms    |     |  |

| t <sub>START_DEV</sub>  | Clock startup time after the                                              | Peripheral       | -     | -      | 5.6   | 20  |  |

| t <sub>START_HOST</sub> | de-assertion of SuspendM                                                  | Host             | -     | -      | -     | ms  |  |

| t <sub>PREP</sub>       | PHY preparation time after the of the input clock                         | first transition | -     | -      | -     | μs  |  |

| Table 71. USB HS clock timing parameters <sup>(1)</sup> | 3 HS clock timing parameters <sup>(1)</sup> |

|---------------------------------------------------------|---------------------------------------------|

|---------------------------------------------------------|---------------------------------------------|

1. Guaranteed by design.

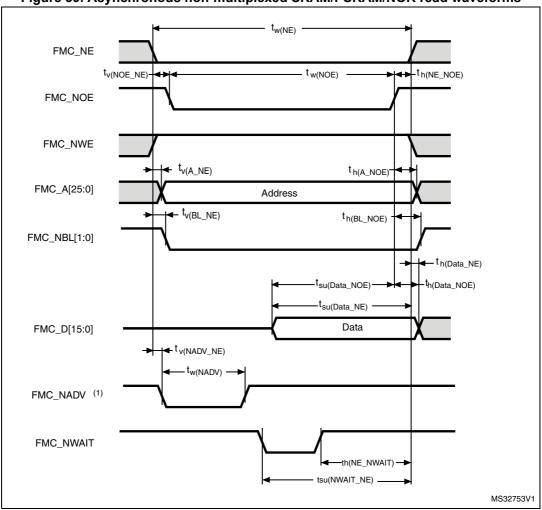

Figure 59. Asynchronous non-multiplexed SRAM/PSRAM/NOR read waveforms

1. Mode 2/B, C and D only. In Mode 1, FMC\_NADV is not used.

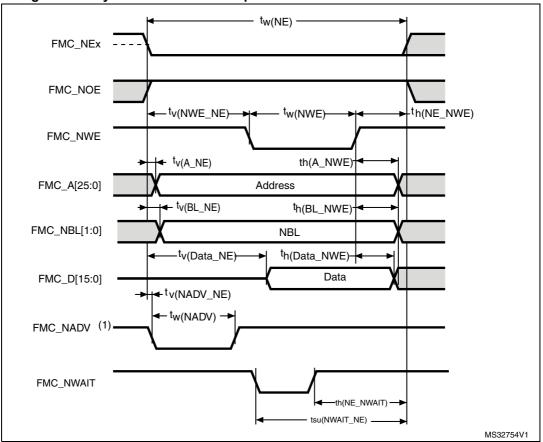

Figure 60. Asynchronous non-multiplexed SRAM/PSRAM/NOR write waveforms

1. Mode 2/B, C and D only. In Mode 1, FMC\_NADV is not used.

| Table 90. Asynchronous non-multiplexed SRAM/PSRAM/NOR write timings <sup>(1)</sup> |

|------------------------------------------------------------------------------------|

|------------------------------------------------------------------------------------|

| Symbol                   | Parameter                             | Min                     | Мах                     | Unit |

|--------------------------|---------------------------------------|-------------------------|-------------------------|------|

| t <sub>w(NE)</sub>       | FMC_NE low time                       | 3T <sub>HCLK</sub>      | 3T <sub>HCLK</sub> +1   |      |

| t <sub>v(NWE_NE)</sub>   | FMC_NEx low to FMC_NWE low            | T <sub>HCLK</sub> – 0.5 | T <sub>HCLK</sub> + 0.5 |      |

| t <sub>w(NWE)</sub>      | FMC_NWE low time                      | T <sub>HCLK</sub>       | T <sub>HCLK</sub> + 0.5 |      |

| t <sub>h(NE_NWE)</sub>   | FMC_NWE high to FMC_NE high hold time | T <sub>HCLK</sub> +1.5  | -                       |      |

| t <sub>v(A_NE)</sub>     | FMC_NEx low to FMC_A valid            | -                       | 0                       |      |

| t <sub>h(A_NWE)</sub>    | Address hold time after FMC_NWE high  | T <sub>HCLK</sub> +0.5  | -                       | 20   |

| t <sub>v(BL_NE)</sub>    | FMC_NEx low to FMC_BL valid           | -                       | 1.5                     | ns   |

| t <sub>h(BL_NWE)</sub>   | FMC_BL hold time after FMC_NWE high   | T <sub>HCLK</sub> +0.5  | -                       |      |

| t <sub>v(Data_NE)</sub>  | Data to FMC_NEx low to Data valid     | -                       | T <sub>HCLK</sub> + 2   |      |

| t <sub>h(Data_NWE)</sub> | Data hold time after FMC_NWE high     | T <sub>HCLK</sub> +0.5  | -                       |      |

| t <sub>v(NADV_NE)</sub>  | FMC_NEx low to FMC_NADV low           | -                       | 0.5                     |      |

| t <sub>w(NADV)</sub>     | FMC_NADV low time                     | -                       | T <sub>HCLK</sub> + 0.5 |      |

1. Based on test during characterization.

|                           | · ·                                       |                         |                         |      |

|---------------------------|-------------------------------------------|-------------------------|-------------------------|------|

| Symbol                    | Parameter                                 | Min                     | Max                     | Unit |

| t <sub>w(NE)</sub>        | FMC_NE low time                           | 9T <sub>HCLK</sub>      | 9T <sub>HCLK</sub> +0.5 |      |

| t <sub>w(NWE)</sub>       | FMC_NWE low time                          |                         | 7T <sub>HCLK</sub> +2   | ns   |

| t <sub>su(NWAIT_NE)</sub> | FMC_NWAIT valid before FMC_NEx high       | 6T <sub>HCLK</sub> +1.5 | -                       |      |

| t <sub>h(NE_NWAIT)</sub>  | FMC_NEx hold time after FMC_NWAIT invalid | 4T <sub>HCLK</sub> –1   | -                       |      |

Table 95. Asynchronous multiplexed PSRAM/NOR write-NWAIT timings<sup>(1)</sup>

1. Based on test during characterization.

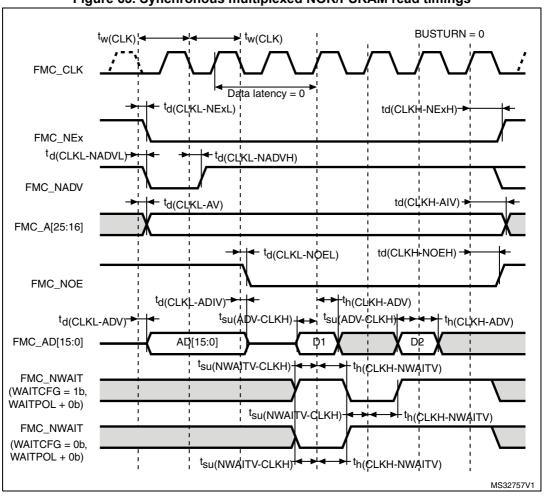

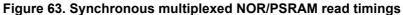

### Synchronous waveforms and timings

Figures 63 through 66 represent synchronous waveforms and *Table 96* through *Table 99* provide the corresponding timings. The results shown in these tables are obtained with the following FMC configuration:

- BurstAccessMode = FMC\_BurstAccessMode\_Enable;

- MemoryType = FMC\_MemoryType\_CRAM;

- WriteBurst = FMC\_WriteBurst\_Enable;

- CLKDivision = 1;

- DataLatency = 1 for NOR Flash; DataLatency = 0 for PSRAM

- C<sub>L</sub> = 30 pF on data and address lines. C<sub>L</sub> = 10 pF on FMC\_CLK unless otherwise specified.

In all timing tables, the  $T_{\text{HCLK}}$  is the HCLK clock period:

- For 2.7 V $\leq$  V<sub>DD</sub> $\leq$  3.6 V, maximum FMC\_CLK = 90 MHz at C<sub>L</sub> = 30 pF (on FMC\_CLK).

- For 1.71 V $\leq$  V<sub>DD</sub><1.9 V, maximum FMC\_CLK = 60 MHz at C<sub>L</sub> = 10 pF (on FMC\_CLK).

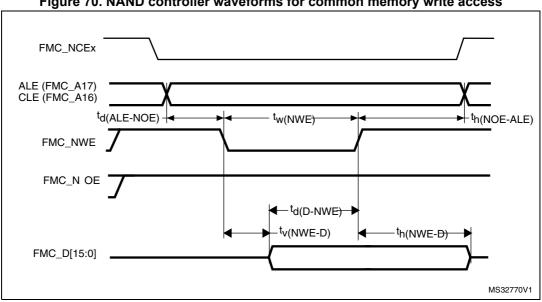

Table 100. Switching characteristics for NAND Flash read cycles

| Symbol                  | Parameter                                  | Min                      | Мах                      | Unit |

|-------------------------|--------------------------------------------|--------------------------|--------------------------|------|

| t <sub>w(N0E)</sub>     | FMC_NOE low width                          | 4T <sub>HCLK</sub> – 0.5 | 4T <sub>HCLK</sub> +0.5  |      |

| t <sub>su(D-NOE)</sub>  | FMC_D[15-0] valid data before FMC_NOE high | 9                        | -                        |      |

| t <sub>h(NOE-D)</sub>   | FMC_D[15-0] valid data after FMC_NOE high  | 0                        | -                        | ns   |

| t <sub>d(ALE-NOE)</sub> | FMC_ALE valid before FMC_NOE low           | -                        | 3T <sub>HCLK</sub> – 0.5 |      |

| t <sub>h(NOE-ALE)</sub> | FMC_NWE high to FMC_ALE invalid            | 3T <sub>HCLK</sub> – 2   | -                        |      |

| Symbol                  | Parameter                             | Min                    | Мах                     | Unit |

|-------------------------|---------------------------------------|------------------------|-------------------------|------|

| t <sub>w(NWE)</sub>     | FMC_NWE low width                     | 4T <sub>HCLK</sub>     | 4T <sub>HCLK</sub> +1   |      |

| t <sub>v(NWE-D)</sub>   | FMC_NWE low to FMC_D[15-0] valid      | 0                      | -                       |      |

| t <sub>h(NWE-D)</sub>   | FMC_NWE high to FMC_D[15-0] invalid   | 3T <sub>HCLK</sub> – 1 | -                       | ns   |

| t <sub>d(D-NWE)</sub>   | FMC_D[15-0] valid before FMC_NWE high | 5T <sub>HCLK</sub> – 3 | -                       | 115  |

| t <sub>d(ALE-NWE)</sub> | FMC_ALE valid before FMC_NWE low      | -                      | 3T <sub>HCLK</sub> -0.5 |      |

| t <sub>h(NWE-ALE)</sub> | FMC_NWE high to FMC_ALE invalid       | 3T <sub>HCLK</sub> – 1 | -                       |      |

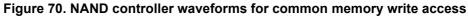

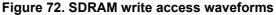

### SDRAM waveforms and timings

- $C_L$  = 30 pF on data and address lines.

- $C_L$  = 10 pF on FMC\_SDCLK unless otherwise specified.

| Symbol                        | Parameter              | Min                      | Мах                     | Unit |

|-------------------------------|------------------------|--------------------------|-------------------------|------|

| t <sub>W(SDCLK)</sub>         | FMC_SDCLK period       | 2T <sub>HCLK</sub> – 0.5 | 2T <sub>HCLK</sub> +0.5 |      |

| t <sub>su(SDCLKH_Data)</sub>  | Data input setup time  | 2.5                      | -                       |      |

| t <sub>h(SDCLKH_Data)</sub>   | Data input hold time   | 0                        | -                       |      |

| t <sub>d(SDCLKL_Add)</sub>    | Address valid time     | -                        | 1                       |      |

| t <sub>d(SDCLKL_SDNE)</sub>   | Chip select valid time | -                        | 1                       | ns   |

| t <sub>h(SDCLKL_SDNE)</sub>   | Chip select hold time  | 1                        | -                       | 113  |

| t <sub>d(SDCLKL_SDNRAS</sub>  | SDNRAS valid time      | -                        | 1                       |      |

| t <sub>h(SDCLKL_SDNRAS)</sub> | SDNRAS hold time       | 1                        | -                       |      |

| t <sub>d(SDCLKL_SDNCAS)</sub> | SDNCAS valid time      | -                        | 1                       |      |

| t <sub>h(SDCLKL_SDNCAS)</sub> | SDNCAS hold time       | 1                        | -                       |      |

### Table 103. LPSDR SDRAM read timings<sup>(1)</sup>

1. Guaranteed based on test during characterization.

DocID028010 Rev 4

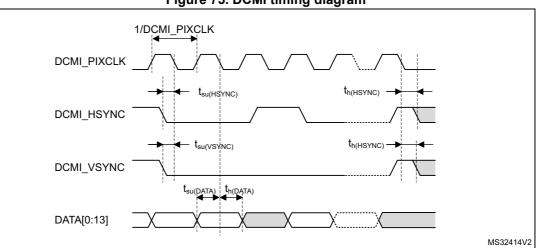

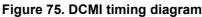

| Symbol                                           | Parameter                                     |     | Мах | Unit |  |

|--------------------------------------------------|-----------------------------------------------|-----|-----|------|--|

| -                                                | Frequency ratio DCMI_PIXCLK/f <sub>HCLK</sub> | -   | 0.4 | -    |  |

| DCMI_PIXCLK                                      | Pixel clock input                             | -   | 54  | MHz  |  |

| D <sub>Pixel</sub>                               | Pixel clock input duty cycle                  | 30  | 70  | %    |  |

| t <sub>su(DATA)</sub>                            | Data input setup time                         | 4   | -   |      |  |

| t <sub>h(DATA)</sub>                             | Data input hold time                          | 1   | -   |      |  |

| t <sub>su(HSYNC)</sub><br>t <sub>su(VSYNC)</sub> | DCMI_HSYNC/DCMI_VSYNC input setup time        | 3.5 | -   | ns   |  |

| t <sub>h(HSYNC)</sub><br>t <sub>h(VSYNC)</sub>   | DCMI_HSYNC/DCMI_VSYNC input hold time         | 0   | -   |      |  |

| Table 10 | 8. DCMI | characteristics <sup>(1)</sup> |

|----------|---------|--------------------------------|

|----------|---------|--------------------------------|

1. 1.Guaranteed based on test during characterization.

## 5.3.32 LCD-TFT controller (LTDC) characteristics

Unless otherwise specified, the parameters given in *Table 109* for LCD-TFT are derived from tests performed under the ambient temperature,  $f_{HCLK}$  frequency and VDD supply voltage summarized in *Table 17*, with the following configuration:

- LCD\_CLK polarity: high

- LCD\_DE polarity: low

- LCD\_VSYNC and LCD\_HSYNC polarity: high

- Pixel formats: 24 bits

- Output speed is set to OSPEEDRy[1:0] = 11

- Capacitive load C<sub>L</sub> = 30 pF

- Measurement points are done at CMOS levels: 0.5 V<sub>DD</sub>

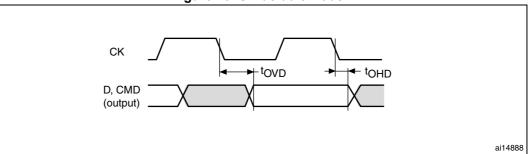

### Figure 79. SD default mode

|                     | Table 110. Dynamic characteris          | tics: SD / MMC          | character | istics, V <sub>DD</sub> | = 2.7 to 3. | 6 V <sup>(1)</sup> |

|---------------------|-----------------------------------------|-------------------------|-----------|-------------------------|-------------|--------------------|

| Symbol              | Parameter                               | Conditions              | Min       | Тур                     | Max         | Unit               |

| f <sub>PP</sub>     | Clock frequency in data transfer mode   | -                       | 0         | -                       | 50          | MHz                |

| -                   | SDIO_CK/fPCLK2 frequency ratio          | -                       | -         | -                       | 8/3         | -                  |

| t <sub>W(CKL)</sub> | Clock low time                          | f = 50 MHz              | 9.5       | 10.5                    | -           | ns                 |

| t <sub>W(CKH)</sub> | Clock high time                         | f <sub>pp</sub> =50 MHz | 8.5       | 9.5                     | -           |                    |

| CMD, D in           | puts (referenced to CK) in MMC and SE   | ) HS mode               |           |                         |             |                    |

| t <sub>ISU</sub>    | Input setup time HS                     |                         | 2.0       | -                       | -           | ns                 |

| t <sub>IH</sub>     | Input hold time HS                      | f <sub>pp</sub> =50 MHz | 2.0       | -                       | -           |                    |

| CMD, D ou           | tputs (referenced to CK) in MMC and S   | SD HS mode              |           |                         |             |                    |

| t <sub>OV</sub>     | Output valid time HS                    | 6 - FO MU-              | -         | 13                      | 13.5        |                    |

| t <sub>OH</sub>     | Output hold time HS                     | f <sub>pp</sub> =50 MHz | 12.5      | -                       | -           | – ns               |

| CMD, D in           | puts (referenced to CK) in SD default m | node                    |           |                         |             |                    |

| t <sub>ISUD</sub>   | Input setup time SD                     | £ 05 MU-                | 2.0       | -                       | -           |                    |

| t <sub>IHD</sub>    | Input hold time SD                      | f <sub>pp</sub> =25 MHz | 2.5       | -                       | -           | ns                 |

| CMD, D ou           | tputs (referenced to CK) in SD default  | mode                    |           | -                       |             |                    |

| t <sub>OVD</sub>    | Output valid default time SD            | f _25 ML-               | -         | 1.5                     | 2.0         | -                  |

| t <sub>OHD</sub>    | Output hold default time SD             | f <sub>pp</sub> =25 MHz | 1.0       | -                       | -           | – ns               |

1. Guaranteed based on test during characterization.

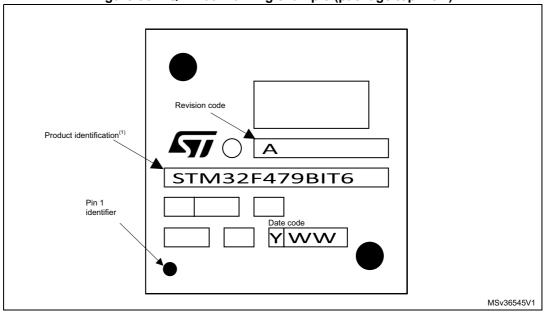

### **Device Marking for LQFP208**

The following figure gives an example of topside marking orientation versus pin 1 identifier location. Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

### Figure 96. LQFP208 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.