Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                    |

|----------------------------|------------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                           |

| Core Processor             | C166SV2                                                                            |

| Core Size                  | 16/32-Bit                                                                          |

| Speed                      | 128MHz                                                                             |

| Connectivity               | CANbus, EBI/EMI, FlexRay, I <sup>2</sup> C, LINbus, SPI, UART/USART                |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                    |

| Number of I/O              | 75                                                                                 |

| Program Memory Size        | 1.06MB (1.06M x 8)                                                                 |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 90K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                          |

| Data Converters            | A/D 16x12b                                                                         |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 100-LQFP Exposed Pad                                                               |

| Supplier Device Package    | PG-LQFP-100-8                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc2368e136f128laakxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Summary of Features**

- Multi-functional general purpose timer unit with 5 timers

- 16-channel general purpose capture/compare unit (CAPCOM2)

- Up to four capture/compare units for flexible PWM signal generation (CCU6x)

- Two synchronizable 12-bit A/D Converters with up to 24 channels, conversion time below 1 μs, optional data preprocessing (data reduction, range check), broken wire detection

- Up to 10 serial interface channels to be used as UART, LIN, high-speed synchronous channel (SPI), IIC bus interface (10-bit addressing, 400 kbit/s), IIS interface

- On-chip MultiCAN interface (Rev. 2.0B active) with up to 64 message objects (Full CAN/Basic CAN) on up to 3 CAN nodes and gateway functionality

- FlexRay<sup>™</sup> module (E-Ray) according to protocol specification V2.1, 2 nodes

- On-chip system timer and on-chip real time clock

- Up to 12 Mbytes external address space for code and data

- Programmable external bus characteristics for different address ranges

- Multiplexed or demultiplexed external address/data buses

- Selectable address bus width

- 16-bit or 8-bit data bus width

- Five programmable chip-select signals

- Single power supply from 3.0 V to 5.5 V

- Power reduction and wake-up modes with flexible power management

- Programmable watchdog timer and oscillator watchdog

- Up to 75 general purpose I/O lines

- · On-chip bootstrap loaders

- Supported by a full range of development tools including C compilers, macroassembler packages, emulators, evaluation boards, HLL debuggers, simulators, logic analyzer disassemblers, programming boards

- On-chip debug support via Device Access Port (DAP) or JTAG interface

- 100-pin Green LQFP package, 0.5 mm (19.7 mil) pitch

### **Summary of Features**

### **Ordering Information**

The ordering code for an Infineon microcontroller provides an exact reference to a specific product. This ordering code identifies:

- the function set of the corresponding product type

- the temperature range:

- SAF-...: -40°C to 85°C

- SAH-...: -40°C to 110°C

- SAK-...: -40°C to 125°C

the package and the type of delivery.

For ordering codes for the XC2368E please contact your sales representative or local distributor.

This document describes several derivatives of the XC2368E group:

Basic Device Types are readily available and

Special Device Types are only available on request.

As this document refers to all of these derivatives, some descriptions may not apply to a specific product, in particular to the special device types.

For simplicity the term **XC2368E** is used for all derivatives throughout this document.

## 1.1 Basic Device Types

Basic device types are available and can be ordered through Infineon's direct and/or distribution channels.

Table 1 Synopsis of XC2368E Basic Device Types

| Derivative <sup>1)</sup> | Flash<br>Memory <sup>2)</sup> | PSRAM<br>DSRAM <sup>3)</sup> | Capt./Comp.<br>Modules | ADC <sup>4)</sup><br>Chan. | Interfaces <sup>4)</sup>                            |

|--------------------------|-------------------------------|------------------------------|------------------------|----------------------------|-----------------------------------------------------|

| XC2368E-136FxxLR         | 1 088<br>Kbytes               | 64 Kbytes<br>24 Kbytes       | CC2<br>CCU60/1/2/3     | 11 + 5                     | 3 CAN Nodes<br>6 Serial Chan.<br>2 FlexRay<br>Nodes |

<sup>1)</sup> xx is a placeholder for the available speed grade (in MHz).

<sup>2)</sup> Specific information about the on-chip Flash memory in Table 3.

<sup>3)</sup> All derivatives additionally provide 8 Kbytes SBRAM and 2 Kbytes DPRAM.

Specific information about the available channels in Table 5.

Analog input channels are listed for each Analog/Digital Converter module separately (ADC0 + ADC1).

## **General Device Information**

Table 6 Pin Definitions and Functions (cont'd)

| - uni |                  | ,,,,,,,,,,, | io una | Tunotions (cont a)                             |

|-------|------------------|-------------|--------|------------------------------------------------|

| Pin   | Symbol           | Ctrl.       | Туре   | Function                                       |

| 32    | P5.10            | I           | In/A   | Bit 10 of Port 5, General Purpose Input        |

|       | ADC0_CH10        | I           | In/A   | Analog Input Channel 10 for ADC0               |

|       | ADC1_CH10        | I           | In/A   | Analog Input Channel 10 for ADC1               |

|       | BRKIN_A          | I           | In/A   | OCDS Break Signal Input                        |

|       | U2C1_DX0F        | I           | In/A   | USIC2 Channel 1 Shift Data Input               |

|       | CCU61_T13<br>HRA | I           | In/A   | External Run Control Input for T13 of CCU61    |

| 33    | P5.11            | I           | In/A   | Bit 11 of Port 5, General Purpose Input        |

|       | ADC0_CH11        | I           | In/A   | Analog Input Channel 11 for ADC0               |

|       | ADC1_CH11        | I           | In/A   | Analog Input Channel 11 for ADC1               |

| 34    | P5.13            | I           | In/A   | Bit 13 of Port 5, General Purpose Input        |

|       | ADC0_CH13        | I           | In/A   | Analog Input Channel 13 for ADC0               |

|       | ERU_0B1          | I           | St/B   | External Request Unit Channel 0 Input B1       |

|       | CCU63_T13<br>HRF | I           | In/A   | External Run Control Input for T13 of CCU63    |

| 35    | P5.15            | I           | In/A   | Bit 15 of Port 5, General Purpose Input        |

|       | ADC0_CH15        | I           | In/A   | Analog Input Channel 15 for ADC0               |

|       | RxDC2F           | I           | In/A   | CAN Node 2 Receive Data Input                  |

| 36    | P2.12            | O0 / I      | St/B   | Bit 12 of Port 2, General Purpose Input/Output |

|       | U0C0_SELO<br>4   | 01          | St/B   | USIC0 Channel 0 Select/Control 4 Output        |

|       | U0C1_SELO<br>3   | O2          | St/B   | USIC0 Channel 1 Select/Control 3 Output        |

|       | TXDC2            | О3          | St/B   | CAN Node 2 Transmit Data Output                |

|       | READY            | IH          | St/B   | External Bus Interface READY Input             |

|       |                  |             |        |                                                |

### **General Device Information**

Table 6 Pin Definitions and Functions (cont'd)

| Pin | Symbol           | Ctrl.      | Туре | Function                                                                                                                                                  |

|-----|------------------|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 82  | P10.10           | O0 / I     | St/B | Bit 10 of Port 10, General Purpose Input/Output                                                                                                           |

|     | U0C0_SELO<br>0   | O1         | St/B | USIC0 Channel 0 Select/Control 0 Output                                                                                                                   |

|     | CCU60_COU<br>T63 | O2         | St/B | CCU60 Channel 3 Output                                                                                                                                    |

|     | ERAY_TxEN<br>A   | О3         | St/B | ERAY Transmit Enable Output Channel A                                                                                                                     |

|     | AD10             | OH /<br>IH | St/B | External Bus Interface Address/Data Line 10                                                                                                               |

|     | U0C0_DX2C        | I          | St/B | USIC0 Channel 0 Shift Control Input                                                                                                                       |

|     | U0C1_DX1A        | I          | St/B | USIC0 Channel 1 Shift Clock Input                                                                                                                         |

|     | TDI_B            | IH         | St/B | JTAG Test Data Input If JTAG pos. B is selected during start-up, an internal pull-up device will hold this pin high when nothing is driving it.           |

| 83  | P10.11           | O0 / I     | St/B | Bit 11 of Port 10, General Purpose Input/Output                                                                                                           |

|     | U1C0_SCLK<br>OUT | O1         | St/B | USIC1 Channel 0 Shift Clock Output                                                                                                                        |

|     | BRKOUT           | O2         | St/B | OCDS Break Signal Output                                                                                                                                  |

|     | AD11             | OH /<br>IH | St/B | External Bus Interface Address/Data Line 11                                                                                                               |

|     | U1C0_DX1D        | I          | St/B | USIC1 Channel 0 Shift Clock Input                                                                                                                         |

|     | RxDC2B           | I          | St/B | CAN Node 2 Receive Data Input                                                                                                                             |

|     | TMS_B            | IH         | St/B | JTAG Test Mode Selection Input If JTAG pos. B is selected during start-up, an internal pull-up device will hold this pin high when nothing is driving it. |

| 84  | P9.2             | O0 / I     | St/B | Bit 2 of Port 9, General Purpose Input/Output                                                                                                             |

|     | CCU63_CC6<br>2   | O1         | St/B | CCU63 Channel 2 Output                                                                                                                                    |

|     | ERAY_TxEN<br>B   | О3         | St/B | ERAY Transmit Enable Output Channel B                                                                                                                     |

|     | CAPINB           | I          | St/B | GPT12E Register CAPREL Capture Input                                                                                                                      |

**Functional Description**

## 3.4 Memory Protection Unit (MPU)

The XC2368E's Memory Protection Unit (MPU) protects user-specified memory areas from unauthorized read, write, or instruction fetch accesses. The MPU can protect the whole address space including the peripheral area. This completes established mechanisms such as the register security mechanism or stack overrun/underrun detection.

Four Protection Levels support flexible system programming where operating system, low level drivers, and applications run on separate levels. Each protection level permits different access restrictions for instructions and/or data.

Every access is checked (if the MPU is enabled) and an access violating the permission rules will be marked as invalid and leads to a protection trap.

A set of protection registers for each protection level specifies the address ranges and the access permissions. Applications requiring more than 4 protection levels can dynamically re-program the protection registers.

## 3.5 Memory Checker Module (MCHK)

The XC2368E's Memory Checker Module calculates a checksum (fractional polynomial division) on a block of data, often called Cyclic Redundancy Code (CRC). It is based on a 32-bit linear feedback shift register and may, therefore, also be used to generate pseudo-random numbers.

The Memory Checker Module is a 16-bit parallel input signature compression circuitry which enables error detection within a block of data stored in memory, registers, or communicated e.g. via serial communication lines. It reduces the probability of error masking due to repeated error patterns by calculating the signature of blocks of data.

The polynomial used for operation is configurable, so most of the commonly used polynomials may be used. Also, the block size for generating a CRC result is configurable via a local counter. An interrupt may be generated if testing the current data block reveals an error.

An autonomous CRC compare circuitry is included to enable redundant error detection, e.g. to enable higher safety integrity levels.

The Memory Checker Module provides enhanced fault detection (beyond parity or ECC) for data and instructions in volatile and non volatile memories. This is especially important for the safety and reliability of embedded systems.

### **Functional Description**

Table 9 Compare Modes (cont'd)

| Compare Modes           | Function                                                                                                                  |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Mode 2                  | Interrupt-only compare mode; Only one compare interrupt per timer period is generated                                     |

| Mode 3                  | Pin set '1' on match; pin reset '0' on compare timer overflow;<br>Only one compare event per timer period is generated    |

| Double Register<br>Mode | Two registers operate on one pin; Pin toggles on each compare match; Several compare events per timer period are possible |

| Single Event Mode       | Generates single edges or pulses; Can be used with any compare mode                                                       |

When a capture/compare register has been selected for capture mode, the current contents of the allocated timer will be latched ('captured') into the capture/compare register in response to an external event at the port pin associated with this register. In addition, a specific interrupt request for this capture/compare register is generated. Either a positive, a negative, or both a positive and a negative external signal transition at the pin can be selected as the triggering event.

The contents of all registers selected for one of the five compare modes are continuously compared with the contents of the allocated timers.

When a match occurs between the timer value and the value in a capture/compare register, specific actions will be taken based on the compare mode selected.

### **Functional Description**

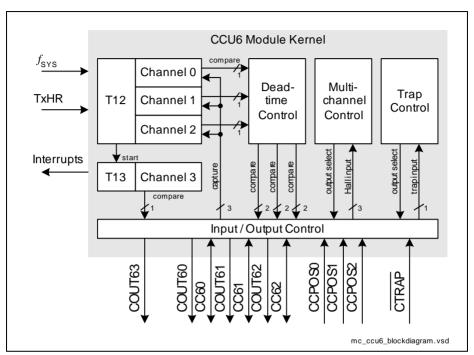

## 3.9 Capture/Compare Units CCU6x

The XC2368E types feature the CCU60, CCU61, CCU62 and CCU63 unit(s).

CCU6 is a high-resolution capture and compare unit with application-specific modes. It provides inputs to start the timers synchronously, an important feature in devices with several CCU6 modules.

The module provides two independent timers (T12, T13), that can be used for PWM generation, especially for AC motor control. Additionally, special control modes for block commutation and multi-phase machines are supported.

#### **Timer 12 Features**

- Three capture/compare channels, where each channel can be used either as a capture or as a compare channel.

- Supports generation of a three-phase PWM (six outputs, individual signals for highside and low-side switches)

- 16-bit resolution, maximum count frequency = peripheral clock

- Dead-time control for each channel to avoid short circuits in the power stage

- Concurrent update of the required T12/13 registers

- Center-aligned and edge-aligned PWM can be generated

- Single-shot mode supported

- Many interrupt request sources

- Hysteresis-like control mode

- Automatic start on a HW event (T12HR, for synchronization purposes)

#### **Timer 13 Features**

- One independent compare channel with one output

- 16-bit resolution, maximum count frequency = peripheral clock

- Can be synchronized to T12

- Interrupt generation at period match and compare match

- · Single-shot mode supported

- Automatic start on a HW event (T13HR, for synchronization purposes)

#### **Additional Features**

- Block commutation for brushless DC drives implemented

- Position detection via Hall sensor pattern

- Automatic rotational speed measurement for block commutation

- Integrated error handling

- Fast emergency stop without CPU load via external signal (CTRAP)

- Control modes for multi-channel AC drives

- Output levels can be selected and adapted to the power stage

## **Functional Description**

Figure 4 CCU6 Block Diagram

Timer T12 can work in capture and/or compare mode for its three channels. The modes can also be combined. Timer T13 can work in compare mode only. The multi-channel control unit generates output patterns that can be modulated by timer T12 and/or timer T13. The modulation sources can be selected and combined for signal modulation.

### **Functional Description**

## 3.19 Instruction Set Summary

Table 11 lists the instructions of the XC2368E.

The addressing modes that can be used with a specific instruction, the function of the instructions, parameters for conditional execution of instructions, and the opcodes for each instruction can be found in the "Instruction Set Manual".

This document also provides a detailed description of each instruction.

Table 11 Instruction Set Summary

| Mnemonic      | Description                                                                                       | Bytes |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------|-------|--|--|--|

| ADD(B)        | Add word (byte) operands                                                                          | 2/4   |  |  |  |

| ADDC(B)       | Add word (byte) operands with Carry                                                               | 2/4   |  |  |  |

| SUB(B)        | Subtract word (byte) operands                                                                     | 2/4   |  |  |  |

| SUBC(B)       | Subtract word (byte) operands with Carry                                                          | 2/4   |  |  |  |

| MUL(U)        | (Un)Signed multiply direct GPR by direct GPR (16- × 16-bit)                                       |       |  |  |  |

| DIV(U)        | (Un)Signed divide register MDL by direct GPR (16-/16-bit)                                         | 2     |  |  |  |

| DIVL(U)       | (Un)Signed long divide reg. MD by direct GPR (32-/16-bit)                                         | 2     |  |  |  |

| CPL(B)        | Complement direct word (byte) GPR                                                                 | 2     |  |  |  |

| NEG(B)        | Negate direct word (byte) GPR                                                                     | 2     |  |  |  |

| AND(B)        | Bitwise AND, (word/byte operands)                                                                 | 2/4   |  |  |  |

| OR(B)         | Bitwise OR, (word/byte operands)                                                                  | 2/4   |  |  |  |

| XOR(B)        | Bitwise exclusive OR, (word/byte operands)                                                        | 2/4   |  |  |  |

| BCLR/BSET     | Clear/Set direct bit                                                                              | 2     |  |  |  |

| BMOV(N)       | Move (negated) direct bit to direct bit                                                           | 4     |  |  |  |

| BAND/BOR/BXOR | AND/OR/XOR direct bit with direct bit                                                             | 4     |  |  |  |

| ВСМР          | Compare direct bit to direct bit                                                                  | 4     |  |  |  |

| BFLDH/BFLDL   | Bitwise modify masked high/low byte of bit-addressable direct word memory with immediate data     | 4     |  |  |  |

| CMP(B)        | Compare word (byte) operands                                                                      | 2/4   |  |  |  |

| CMPD1/2       | Compare word data to GPR and decrement GPR by 1/2                                                 | 2/4   |  |  |  |

| CMPI1/2       | Compare word data to GPR and increment GPR by 1/2                                                 | 2/4   |  |  |  |

| PRIOR         | Determine number of shift cycles to normalize direct word GPR and store result in direct word GPR | 2     |  |  |  |

| SHL/SHR       | Shift left/right direct word GPR                                                                  | 2     |  |  |  |

|               |                                                                                                   |       |  |  |  |

#### **Electrical Parameters**

Table 13 Operating Conditions (cont'd)

| Parameter                                              | Symbol                        | Values |      |      | Unit | Note /                         |

|--------------------------------------------------------|-------------------------------|--------|------|------|------|--------------------------------|

|                                                        |                               | Min.   | Тур. | Max. |      | Test Condition                 |

| Absolute sum of overload currents                      | $\Sigma  I_{ m OV} $ SR       | _      | -    | 50   | mA   | not subject to production test |

| Digital core supply voltage for domain M <sup>8)</sup> | $V_{DDIM}$ CC                 | _      | 1.5  | -    |      |                                |

| Digital core supply voltage for domain 18)             | $V_{ m DDI1}$ CC              | _      | 1.5  | -    |      |                                |

| Digital supply voltage for                             | $V_{\mathrm{DDP}}\mathrm{SR}$ | 3.0    | _    | 5.5  | V    | Operation                      |

| IO pads and voltage regulators                         |                               | 3.1    | _    | _    | V    | Power up <sup>9)</sup>         |

| Digital ground voltage                                 | $V_{\rm SS}$ SR               | _      | 0    | _    | V    |                                |

- 1) To ensure the stability of the voltage regulators the EVRs must be buffered with ceramic capacitors. Separate buffer capacitors with the recomended values shall be connected as close as possible to each  $V_{\rm DDIM}$  and  $V_{\rm DDIM}$  pin to keep the resistance of the board tracks below 2  $\Omega$ . Connect all  $V_{\rm DDII}$  pins together. The minimum capacitance value is required for proper operation under all conditions (e.g. temperature). Higher values slightly increase the startup time.

- 2) Use one Capacitor for each pin.

- This is the reference load. For bigger capacitive loads, use the derating factors listed in the PAD properties section.

- 4) The timing is valid for pin drivers operating in default current mode (selected after reset). Reducing the output current may lead to increased delays or reduced driving capability (C<sub>1</sub>).

- 5) The operating frequency range may be reduced for specific device types. This is indicated in the device designation (...FxxL). 80 MHz devices are marked ...F80L.

- 6) Overload conditions occur if the standard operating conditions are exceeded, i.e. the voltage on any pin exceeds the specified range: V<sub>OV</sub> > V<sub>IHmax</sub> (I<sub>OV</sub> > 0) or V<sub>OV</sub> < V<sub>ILmin</sub> ((I<sub>OV</sub> < 0). The absolute sum of input overload currents on all pins may not exceed 50 mA. The supply voltages must remain within the specified limits. Proper operation under overload conditions depends on the application. Overload conditions must not occur on pin XTAL1 (powered by V<sub>DDIM</sub>).

- 7) An overload current (I<sub>OV</sub>) through a pin injects a certain error current (I<sub>IN</sub>) into the adjacent pins. This error current adds to the respective pins leakage current (I<sub>OZ</sub>). The amount of error current depends on the overload current and is defined by the overload coupling factor K<sub>OV</sub>. The polarity of the injected error current is inverse compared to the polarity of the overload current that produces it. The total current through a pin is |I<sub>TOT</sub>| = |I<sub>OZ</sub>| + (|I<sub>OV</sub>| K<sub>OV</sub>). The additional error current may distort the input voltage on analog inputs.

- 8) Value is controlled by on-chip regulator

- 9) To ensure a stable power up sequence, the external supply voltage must reach or exceed a level of 3.1 V during power up for at least 0.5 ms.

- For normal operation the complete specified voltage range is available.

### **Electrical Parameters**

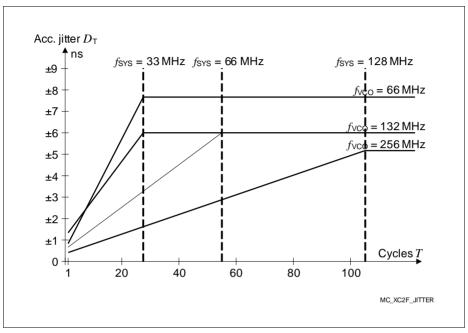

Figure 17 Approximated Accumulated PLL Jitter

Note: The specified PLL jitter values are valid if the capacitive load per pin does not exceed  $C_1 = 20$  pF.

The maximum peak-to-peak noise on the pad supply voltage (measured between  $V_{\rm DDPB}$  pin 100 and  $V_{\rm SS}$  pin 1) is limited to a peak-to-peak voltage of  $V_{\rm PP}$  = 50 mV. This can be achieved by appropriate blocking of the supply voltage as close as possible to the supply pins and using PCB supply and ground planes.

### **Electrical Parameters**

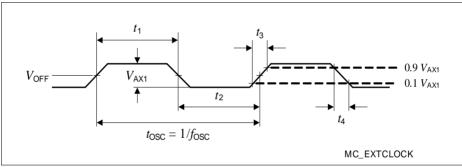

- 1) The FlexRay PLL is optimized for an input frequency of 20 MHz.

- For frequencies above 16 MHz, it is mandatory to measure the oscillation allowance. Please refer to the general note below.

- 3) The amplitude voltage  $V_{\text{AX1}}$  refers to the offset voltage  $V_{\text{OFF}}$ . This offset voltage must be stable during the operation and the resulting voltage peaks must remain within the limits defined by  $V_{\text{IX1}}$ .

- 4) Overload conditions must not occur on pin XTAL1.

Note: For crystal or ceramic resonator operation, it is strongly recommended to measure the oscillation allowance (negative resistance) in the final target system (layout) to determine the optimum parameters for oscillator operation.

The manufacturers of crystals and ceramic resonators offer an oscillator evaluation service. This evaluation checks the crystal/resonator specification limits to ensure a reliable oscillator operation.

Figure 18 External Clock Drive XTAL1

**Electrical Parameters**

## 4.6.4 Pad Properties

The output pad drivers of the XC2368E can operate in several user-selectable modes. Strong driver mode allows controlling external components requiring higher currents such as power bridges or LEDs. Reducing the driving power of an output pad reduces electromagnetic emissions (EME). In strong driver mode, selecting a slower edge reduces EME.

The dynamic behavior, i.e. the rise time and fall time, depends on the applied external capacitance that must be charged and discharged. Timing values are given for a capacitance of 20 pF, unless otherwise noted.

In general, the performance of a pad driver depends on the available supply voltage  $V_{\rm DDP}$ . Therefore the following tables list the pad parameters for the upper voltage range and the lower voltage range, respectively.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply.

**Electrical Parameters**

## 4.6.5 External Bus Timing

The following parameters specify the behavior of the XC2368E bus interface.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply.

#### **Bus Interface Performance Limits**

The output frequency at the bus interface pins is limited by the performance of the output drivers. The fast clock driver (used for CLKOUT) can drive 80-MHz signals, the standard drivers can drive 40-MHz signals

Therefore, the speed of the EBC must be limited, either by limiting the system frequency to  $f_{\rm SYS} \le 80$  MHz or by adding waitstates so that signal transitions have a minimum distance of 12.5 ns.

For a description of the bus protocol and the programming of its variable timing parameters, please refer to the User's Manual.

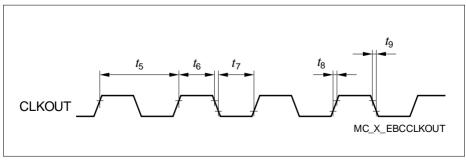

Table 33 EBC Parameters

| Symbol            | Values                              |                      |      | Unit                                                                                                                                                                              | Note /         |

|-------------------|-------------------------------------|----------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|                   | Min.                                | Тур.                 | Max. |                                                                                                                                                                                   | Test Condition |

| t <sub>5</sub> CC | -                                   | 1 / f <sub>SYS</sub> | -    | ns                                                                                                                                                                                |                |

| t <sub>6</sub> CC | 2                                   | _                    | -    |                                                                                                                                                                                   |                |

| t <sub>7</sub> CC | 2                                   | _                    | -    |                                                                                                                                                                                   |                |

| t <sub>8</sub> CC | -                                   | _                    | 3    | ns                                                                                                                                                                                |                |

| t <sub>9</sub> CC | -                                   | _                    | 3    |                                                                                                                                                                                   |                |

|                   | $t_5$ CC $t_6$ CC $t_7$ CC $t_8$ CC |                      |      | Min.         Typ.         Max. $t_5$ CC         - $1/f_{\text{SYS}}$ - $t_6$ CC         2         -         - $t_7$ CC         2         -         - $t_8$ CC         -         3 |                |

The CLKOUT cycle time is influenced by PLL jitter. For longer periods the relative deviation decreases (see PLL deviation formula).

Figure 19 CLKOUT Signal Timing

#### **Electrical Parameters**

Note: The term CLKOUT refers to the reference clock output signal which is generated by selecting  $f_{\rm SYS}$  as the source signal for the clock output signal EXTCLK on pin P2.8 and by enabling the high-speed clock driver on this pin.

### **Variable Memory Cycles**

External bus cycles of the XC2368E are executed in five consecutive cycle phases (AB, C, D, E, F). The duration of each cycle phase is programmable (via the TCONCSx registers) to adapt the external bus cycles to the respective external module (memory, peripheral, etc.).

The duration of the access phase can optionally be controlled by the external module using the READY handshake input.

This table provides a summary of the phases and the ranges for their length.

Table 34 Programmable Bus Cycle Phases (see timing diagrams)

| Bus Cycle Phase                                                                                                                | Parameter | Valid Values | Unit |

|--------------------------------------------------------------------------------------------------------------------------------|-----------|--------------|------|

| Address setup phase, the standard duration of this phase (1 2 TCS) can be extended by 0 3 TCS if the address window is changed | tpAB      | 1 2 (5)      | TCS  |

| Command delay phase                                                                                                            | tpC       | 0 3          | TCS  |

| Write Data setup/MUX Tristate phase                                                                                            | tpD       | 0 1          | TCS  |

| Access phase                                                                                                                   | tpE       | 1 32         | TCS  |

| Address/Write Data hold phase                                                                                                  | tpF       | 0 3          | TCS  |

Note: The bandwidth of a parameter (from minimum to maximum value) covers the whole operating range (temperature, voltage) as well as process variations. Within a given device, however, this bandwidth is smaller than the specified range. This is also due to interdependencies between certain parameters. Some of these interdependencies are described in additional notes (see standard timing).

Note: Operating Conditions apply;  $C_L = 20 \text{ pF}$ .

### **Electrical Parameters**

Table 36 EBC External Bus Timing for Lower Voltage Range

| Parameter                                                                                   | Symbol                    |      | Values |      | Unit | Note /<br>Test Condition |

|---------------------------------------------------------------------------------------------|---------------------------|------|--------|------|------|--------------------------|

|                                                                                             |                           | Min. | Тур.   | Max. |      |                          |

| Output valid delay for RD, WR(L/H)                                                          | t <sub>10</sub> CC        | -    | 11     | 20   | ns   |                          |

| Output valid delay for BHE, ALE                                                             | t <sub>11</sub> CC        | _    | 10     | 21   | ns   |                          |

| Address output valid delay for A23 A0                                                       | t <sub>12</sub> CC        | _    | 11     | 22   | ns   |                          |

| Address output valid delay for AD15 AD0 (MUX mode)                                          | t <sub>13</sub> CC        | -    | 10     | 22   | ns   |                          |

| Output valid delay for CS                                                                   | t <sub>14</sub> CC        | -    | 10     | 13   | ns   |                          |

| Data output valid delay for AD15 AD0 (write data, MUX mode)                                 | t <sub>15</sub> CC        | -    | 10     | 22   | ns   |                          |

| Data output valid delay for D15 D0 (write data, DEMUX mode)                                 | t <sub>16</sub> CC        | -    | 10     | 22   | ns   |                          |

| Output hold time for $\overline{\text{RD}}$ , $\overline{\text{WR}}(\overline{\text{L/H}})$ | t <sub>20</sub> CC        | -2   | 8      | 10   | ns   |                          |

| Output hold time for BHE, ALE                                                               | t <sub>21</sub> CC        | -2   | 8      | 10   | ns   |                          |

| Address output hold time for AD15 AD0                                                       | t <sub>23</sub> CC        | -3   | 8      | 10   | ns   |                          |

| Output hold time for CS                                                                     | t <sub>24</sub> CC        | -3   | 8      | 11   | ns   |                          |

| Data output hold time for D15 D0 and AD15 AD0                                               | t <sub>25</sub> CC        | -3   | 8      | 10   | ns   |                          |

| Input setup time for<br>READY, D15 D0, AD15<br>AD0                                          | t <sub>30</sub> SR        | 29   | 17     | -    | ns   |                          |

| Input hold time READY,<br>D15 D0, AD15 AD0 <sup>1)</sup>                                    | <i>t</i> <sub>31</sub> SR | 0    | -9     | -    | ns   |                          |

Read data are latched with the same internal clock edge that triggers the address change and the rising edge

of RD. Address changes before the end of RD have no impact on (demultiplexed) read cycles. Read data can

change after the rising edge of RD.

### **Electrical Parameters**

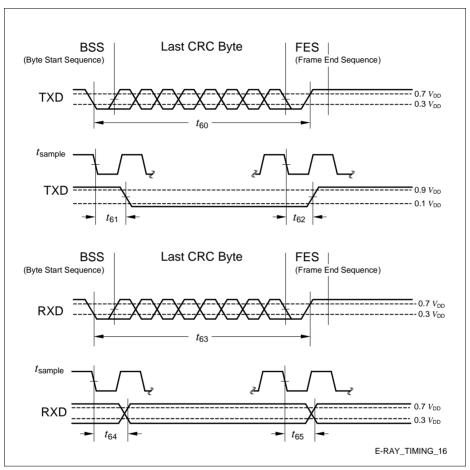

Figure 24 FlexRay Timing

### **Electrical Parameters**

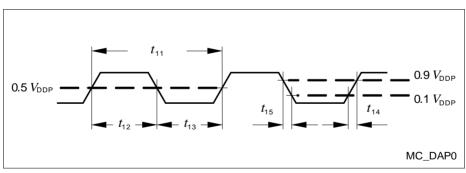

## 4.6.8 Debug Interface Timing

The debugger can communicate with the XC2368E either via the 2-pin DAP interface or via the standard JTAG interface.

### Debug via DAP

The following parameters are applicable for communication through the DAP debug interface.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply;  $C_1$  = 20 pF.

Table 42 DAP Interface Timing for Upper Voltage Range

| Parameter                                      | Symbol             |                  | Value | 5    | Unit | Note /                 |

|------------------------------------------------|--------------------|------------------|-------|------|------|------------------------|

|                                                |                    | Min.             | Тур.  | Max. |      | Test Condition         |

| DAP0 clock period                              | t <sub>11</sub> SR | 25 <sup>1)</sup> | _     | _    | ns   |                        |

| DAP0 high time                                 | t <sub>12</sub> SR | 8                | _     | _    | ns   |                        |

| DAP0 low time                                  | t <sub>13</sub> SR | 8                | _     | _    | ns   |                        |

| DAP0 clock rise time                           | t <sub>14</sub> SR | -                | _     | 4    | ns   |                        |

| DAP0 clock fall time                           | t <sub>15</sub> SR | -                | _     | 4    | ns   |                        |

| DAP1 setup to DAP0 rising edge                 | t <sub>16</sub> SR | 6                | -     | _    | ns   | pad_type= stan<br>dard |

| DAP1 hold after DAP0 rising edge               | t <sub>17</sub> SR | 6                | -     | _    | ns   | pad_type= stan dard    |

| DAP1 valid per DAP0 clock period <sup>2)</sup> | t <sub>19</sub> CC | 17               | 20    | _    | ns   | pad_type= stan dard    |

<sup>1)</sup> The debug interface cannot operate faster than the overall system, therefore  $t_{11} \ge t_{SYS}$ .

<sup>2)</sup> The Host has to find a suitable sampling point by analyzing the sync telegram response.

### **Electrical Parameters**

Table 43 DAP Interface Timing for Lower Voltage Range

| Parameter                                      | Symbol                    |                  | Values | S    | Unit | Note /              |

|------------------------------------------------|---------------------------|------------------|--------|------|------|---------------------|

|                                                |                           | Min.             | Тур.   | Max. |      | Test Condition      |

| DAP0 clock period                              | t <sub>11</sub> SR        | 25 <sup>1)</sup> | _      | _    | ns   |                     |

| DAP0 high time                                 | t <sub>12</sub> SR        | 8                | _      | _    | ns   |                     |

| DAP0 low time                                  | t <sub>13</sub> SR        | 8                | _      | _    | ns   |                     |

| DAP0 clock rise time                           | t <sub>14</sub> SR        | -                | _      | 4    | ns   |                     |

| DAP0 clock fall time                           | t <sub>15</sub> SR        | -                | _      | 4    | ns   |                     |

| DAP1 setup to DAP0 rising edge                 | t <sub>16</sub> SR        | 6                | _      | _    | ns   | pad_type= stan dard |

| DAP1 hold after DAP0 rising edge               | <i>t</i> <sub>17</sub> SR | 6                | _      | _    | ns   | pad_type= stan dard |

| DAP1 valid per DAP0 clock period <sup>2)</sup> | t <sub>19</sub> CC        | 12               | 17     | _    | ns   | pad_type= stan dard |

<sup>1)</sup> The debug interface cannot operate faster than the overall system, therefore  $t_{11} \ge t_{SYS}$ .

<sup>2)</sup> The Host has to find a suitable sampling point by analyzing the sync telegram response.

Figure 25 Test Clock Timing (DAP0)

### Package and Reliability

## 5.3 Quality Declarations

The operation lifetime of the XC2368E depends on the applied temperature profile in the application. For a typical example, please refer to **Table 48**; for other profiles, please contact your Infineon counterpart to calculate the specific lifetime within your application.

Table 47 Quality Parameters

| Parameter                                                        | Symbol                 | Values |      |       | Unit | Note /                      |

|------------------------------------------------------------------|------------------------|--------|------|-------|------|-----------------------------|

|                                                                  |                        | Min.   | Тур. | Max.  |      | Test Condition              |

| Operation lifetime                                               | t <sub>OP</sub> CC     | -      | -    | 20    | а    | See Table 48 and Table 49   |

| ESD susceptibility<br>according to Human Body<br>Model (HBM)     | V <sub>HBM</sub><br>SR | _      | -    | 2 000 | V    | AEC-Q100-002                |

| ESD susceptibility<br>according to Charged<br>Device Model (CDM) | V <sub>CDM</sub><br>SR | _      | _    | 500   | V    | JESD22-C101                 |

|                                                                  |                        | -      | _    | 750   | V    | Corner Pins,<br>JESD22-C101 |

| Moisture sensitivity level                                       | MSL CC                 | -      | -    | 3     | _    | JEDEC<br>J-STD-020C         |

Table 48 Typical Usage Temperature Profile

| Operating Time (Sum = 20 years) | Operating Temperat.                            | Notes            |

|---------------------------------|------------------------------------------------|------------------|

| 1 200 h                         | T <sub>J</sub> = 150°C                         | Normal operation |

| 3 600 h                         | T <sub>J</sub> = 125°C                         | Normal operation |

| 7 200 h                         | $T_{\rm J} = 110^{\circ}{\rm C}$               | Normal operation |

| 12 000 h                        | $T_{\rm J} = 100 {\rm ^{\circ}C}$              | Normal operation |

| 7 × 21 600 h                    | $T_{\rm J} = 010^{\circ} \text{C},,$<br>6070°C | Power reduction  |

Table 49 Long Time Storage Temperature Profile

| Operating Time (Sum = 20 years) | Operating Temperat.       | Notes            |

|---------------------------------|---------------------------|------------------|

| 2 000 h                         | T <sub>J</sub> = 150°C    | Normal operation |

| 16 000 h                        | T <sub>J</sub> = 125°C    | Normal operation |

| 6 000 h                         | $T_{\rm J}$ = 110°C       | Normal operation |

| 151 200 h                       | $T_{J} \leq 150^{\circ}C$ | No operation     |