Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Details                    |                                                                                     |

|----------------------------|-------------------------------------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                                            |

| Core Processor             | C166SV2                                                                             |

| Core Size                  | 16/32-Bit                                                                           |

| Speed                      | 128MHz                                                                              |

| Connectivity               | CANbus, EBI/EMI, FlexRay, I <sup>2</sup> C, LINbus, SPI, UART/USART                 |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                     |

| Number of I/O              | 75                                                                                  |

| Program Memory Size        | 1.06MB (1.06M x 8)                                                                  |

| Program Memory Type        | FLASH                                                                               |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | 90K x 8                                                                             |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                           |

| Data Converters            | A/D 16x12b                                                                          |

| Oscillator Type            | Internal                                                                            |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                       |

| Package / Case             | 100-LQFP Exposed Pad                                                                |

| Supplier Device Package    | PG-LQFP-100-8                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc2368e136f128lraakxuma1 |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2 General Device Information

## The XC2368E series (16/32-Bit Single-Chip Microcontroller

with 32-Bit Performance) is a part of the Infineon XC2000 Family of full-feature singlechip CMOS microcontrollers. These devices extend the functionality and performance of the C166 Family in terms of instructions (MAC unit), peripherals, and speed. They combine high CPU performance (up to 128 million instructions per second) with extended peripheral functionality and enhanced IO capabilities. Optimized peripherals can be adapted flexibly to meet the application requirements. These derivatives utilize clock generation via PLL and internal or external clock sources. On-chip memory modules include program Flash, program RAM, and data RAM.

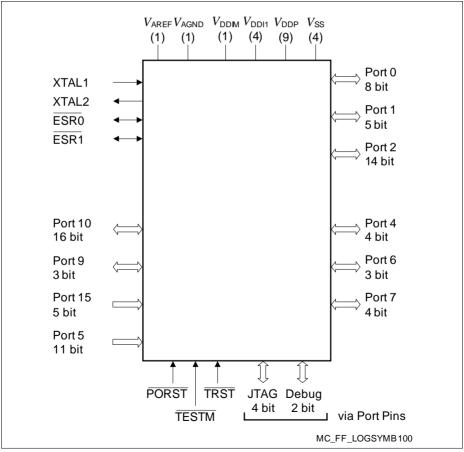

Figure 1 XC2368E Logic Symbol

| Table 6         Pin Definitions and Functions (cont'd) |                   |        |      |                                                |  |  |  |  |  |  |

|--------------------------------------------------------|-------------------|--------|------|------------------------------------------------|--|--|--|--|--|--|

| Pin                                                    | Symbol            | Ctrl.  | Туре | Function                                       |  |  |  |  |  |  |

| 13                                                     | P6.2              | O0 / I | DA/A | Bit 2 of Port 6, General Purpose Input/Output  |  |  |  |  |  |  |

|                                                        | EMUX2             | 01     | DA/A | External Analog MUX Control Output 2 (ADC      |  |  |  |  |  |  |

|                                                        | T6OUT             | O2     | DA/A | GPT12E Timer T6 Toggle Latch Output            |  |  |  |  |  |  |

|                                                        | U1C1_SCLK<br>OUT  | O3     | DA/A | USIC1 Channel 1 Shift Clock Output             |  |  |  |  |  |  |

|                                                        | U1C1_DX1C         | I      | DA/A | USIC1 Channel 1 Shift Clock Input              |  |  |  |  |  |  |

| 15                                                     | P15.0             | I      | In/A | Bit 0 of Port 15, General Purpose Input        |  |  |  |  |  |  |

|                                                        | ADC1_CH0          | I      | In/A | Analog Input Channel 0 for ADC1                |  |  |  |  |  |  |

| 16                                                     | P15.2             | I      | In/A | Bit 2 of Port 15, General Purpose Input        |  |  |  |  |  |  |

|                                                        | ADC1_CH2          | I      | In/A | Analog Input Channel 2 for ADC1                |  |  |  |  |  |  |

|                                                        | T5INA             | I      | In/A | GPT12E Timer T5 Count/Gate Input               |  |  |  |  |  |  |

| 17                                                     | P15.4             | I      | In/A | Bit 4 of Port 15, General Purpose Input        |  |  |  |  |  |  |

|                                                        | ADC1_CH4          | I      | In/A | Analog Input Channel 4 for ADC1                |  |  |  |  |  |  |

|                                                        | T6INA             | I      | In/A | GPT12E Timer T6 Count/Gate Input               |  |  |  |  |  |  |

| 18                                                     | P15.5             | I      | In/A | Bit 5 of Port 15, General Purpose Input        |  |  |  |  |  |  |

|                                                        | ADC1_CH5          | I      | In/A | Analog Input Channel 5 for ADC1                |  |  |  |  |  |  |

|                                                        | T6EUDA            | I      | In/A | GPT12E Timer T6 External Up/Down Control Input |  |  |  |  |  |  |

| 19                                                     | P15.6             | I      | In/A | Bit 6 of Port 15, General Purpose Input        |  |  |  |  |  |  |

|                                                        | ADC1_CH6          | I      | In/A | Analog Input Channel 6 for ADC1                |  |  |  |  |  |  |

| 20                                                     | V <sub>AREF</sub> | -      | PS/A | Reference Voltage for A/D Converters ADC0/1    |  |  |  |  |  |  |

| 21                                                     | V <sub>AGND</sub> | -      | PS/A | Reference Ground for A/D Converters ADC0/1     |  |  |  |  |  |  |

| 22                                                     | P5.0              | I      | In/A | Bit 0 of Port 5, General Purpose Input         |  |  |  |  |  |  |

|                                                        | ADC0_CH0          | I      | In/A | Analog Input Channel 0 for ADC0                |  |  |  |  |  |  |

| 23                                                     | P5.2              | I      | In/A | Bit 2 of Port 5, General Purpose Input         |  |  |  |  |  |  |

|                                                        | ADC0_CH2          | I      | In/A | Analog Input Channel 2 for ADC0                |  |  |  |  |  |  |

|                                                        | TDI_A             | I      | In/A | JTAG Test Data Input                           |  |  |  |  |  |  |

| Table | Table 6         Pin Definitions and Functions (cont'd) |            |      |                                                   |  |  |  |  |

|-------|--------------------------------------------------------|------------|------|---------------------------------------------------|--|--|--|--|

| Pin   | Symbol                                                 | Ctrl.      | Туре | Function                                          |  |  |  |  |

| 78    | P10.8                                                  | O0 / I     | St/B | Bit 8 of Port 10, General Purpose Input/Output    |  |  |  |  |

|       | U0C0_MCLK<br>OUT                                       | O1         | St/B | USIC0 Channel 0 Master Clock Output               |  |  |  |  |

|       | U0C1_SELO<br>0                                         | O2         | St/B | USIC0 Channel 1 Select/Control 0 Output           |  |  |  |  |

|       | U2C1_DOUT                                              | O3         | St/B | USIC2 Channel 1 Shift Data Output                 |  |  |  |  |

|       | AD8                                                    | OH /<br>IH | St/B | External Bus Interface Address/Data Line 8        |  |  |  |  |

|       | CCU60_CCP<br>OS1A                                      | I          | St/B | CCU60 Position Input 1                            |  |  |  |  |

|       | U0C0_DX1C                                              | I          | St/B | USIC0 Channel 0 Shift Clock Input                 |  |  |  |  |

|       | BRKIN_B                                                | I          | St/B | OCDS Break Signal Input                           |  |  |  |  |

|       | T3EUDB                                                 | 1          | St/B | GPT12E Timer T3 External Up/Down Control<br>Input |  |  |  |  |

|       | ERAY_RxDA                                              | I          | St/B | ERAY Receive Data Input Channel A                 |  |  |  |  |

|       | ESR2_11                                                | I          | St/B | ESR2 Trigger Input 11                             |  |  |  |  |

| 79    | P9.1                                                   | O0 / I     | DP/B | Bit 1 of Port 9, General Purpose Input/Output     |  |  |  |  |

|       | CCU63_CC6<br>1                                         | O1         | DP/B | CCU63 Channel 1 Output                            |  |  |  |  |

|       | ERAY_TxDB                                              | O3         | DP/B | ERAY Transmit Data Output Channel B               |  |  |  |  |

|       | CCU63_CC6<br>1INA                                      | 1          | DP/B | CCU63 Channel 1 Input                             |  |  |  |  |

| Table                                               | Table 6         Pin Definitions and Functions (cont'd) |       |      |                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|-----------------------------------------------------|--------------------------------------------------------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin                                                 | Symbol                                                 | Ctrl. | Туре | Function                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 2,<br>25,<br>27,<br>50,<br>52,<br>75,<br>77,<br>100 | V <sub>DDPB</sub>                                      | -     | PS/B | <b>Digital Pad Supply Voltage for Domain B</b><br>Connect decoupling capacitors to adjacent<br>$V_{DDP}/V_{SS}$ pin pairs as close as possible to the pins.<br>Note: The on-chip voltage regulators and all ports<br>except P5, P6 and P15 are fed from supply<br>voltage $V_{DDPB}$ .                                                                                                                |  |  |  |

| 1,<br>26,<br>51,<br>76                              | V <sub>SS</sub>                                        | -     | PS/  | <b>Digital Ground</b><br>All $V_{SS}$ pins must be connected to the ground-line<br>or ground-plane.<br>Note: Also the exposed pad is connected<br>internally to $V_{SS}$ . To improve the EMC<br>behavior, it is recommended to connect the<br>exposed pad to the board ground.<br>For thermal aspects, please refer to the<br>Data Sheet. Board layout examples are<br>given in an application note. |  |  |  |

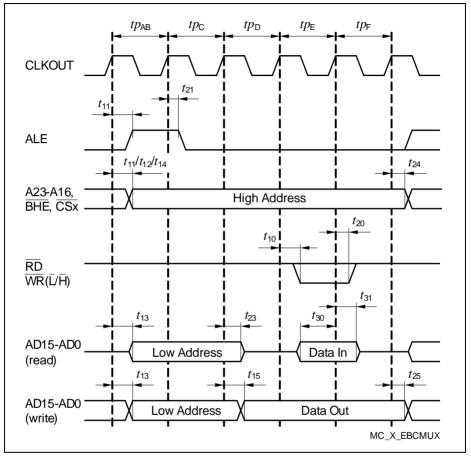

To generate the reference clock output for bus timing measurement, f<sub>SYS</sub> must be selected as source for EXTCLK and P2.8 must be selected as output pin. Also the high-speed clock pad must be enabled. This configuration is referred to as reference clock output signal CLKOUT.

## 2.2 Identification Registers

The identification registers describe the current version of the XC2368E and of its modules.

## Table 7 XC2368E Identification Registers

| Short Name  | Value                  | Address              | Notes   |

|-------------|------------------------|----------------------|---------|

| SCU_IDMANUF | 1820 <sub>H</sub>      | 00'F07E <sub>H</sub> |         |

| SCU_IDCHIP  | 4801 <sub>H</sub>      | 00'F07C <sub>H</sub> | Step AA |

| SCU_IDMEM   | 310F <sub>H</sub>      | 00'F07A <sub>H</sub> |         |

| SCU_IDPROG  | 1313 <sub>H</sub>      | 00'F078 <sub>H</sub> |         |

| JTAG_ID     | 101B'F083 <sub>H</sub> |                      |         |

## **Functional Description**

# 3.4 Memory Protection Unit (MPU)

The XC2368E's Memory Protection Unit (MPU) protects user-specified memory areas from unauthorized read, write, or instruction fetch accesses. The MPU can protect the whole address space including the peripheral area. This completes established mechanisms such as the register security mechanism or stack overrun/underrun detection.

Four Protection Levels support flexible system programming where operating system, low level drivers, and applications run on separate levels. Each protection level permits different access restrictions for instructions and/or data.

Every access is checked (if the MPU is enabled) and an access violating the permission rules will be marked as invalid and leads to a protection trap.

A set of protection registers for each protection level specifies the address ranges and the access permissions. Applications requiring more than 4 protection levels can dynamically re-program the protection registers.

# 3.5 Memory Checker Module (MCHK)

The XC2368E's Memory Checker Module calculates a checksum (fractional polynomial division) on a block of data, often called Cyclic Redundancy Code (CRC). It is based on a 32-bit linear feedback shift register and may, therefore, also be used to generate pseudo-random numbers.

The Memory Checker Module is a 16-bit parallel input signature compression circuitry which enables error detection within a block of data stored in memory, registers, or communicated e.g. via serial communication lines. It reduces the probability of error masking due to repeated error patterns by calculating the signature of blocks of data.

The polynomial used for operation is configurable, so most of the commonly used polynomials may be used. Also, the block size for generating a CRC result is configurable via a local counter. An interrupt may be generated if testing the current data block reveals an error.

An autonomous CRC compare circuitry is included to enable redundant error detection, e.g. to enable higher safety integrity levels.

The Memory Checker Module provides enhanced fault detection (beyond parity or ECC) for data and instructions in volatile and non volatile memories. This is especially important for the safety and reliability of embedded systems.

## **Functional Description**

## **Functional Description**

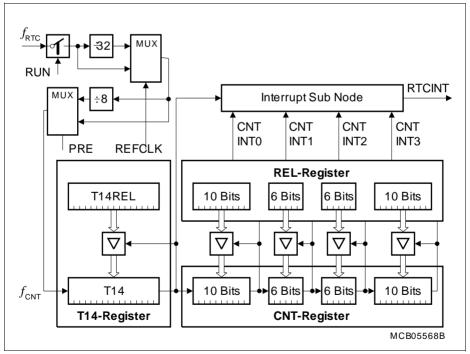

# 3.11 Real Time Clock

The Real Time Clock (RTC) module of the XC2368E can be clocked with a clock signal selected from internal sources or external sources (pins).

The RTC basically consists of a chain of divider blocks:

- Selectable 32:1 and 8:1 dividers (on off)

- The reloadable 16-bit timer T14

- The 32-bit RTC timer block (accessible via registers RTCH and RTCL) consisting of: – a reloadable 10-bit timer

- a reloadable 6-bit timer

- a reloadable 6-bit timer

- a reloadable 10-bit timer

All timers count up. Each timer can generate an interrupt request. All requests are combined to a common node request.

# Figure 7 RTC Block Diagram

Note: The registers associated with the RTC are only affected by a power reset.

# 4.1.2 Operating Conditions

The following operating conditions must not be exceeded to ensure correct operation of the XC2368E. All parameters specified in the following sections refer to these operating conditions, unless otherwise noticed.

Note: Typical parameter values refer to room temperature and nominal supply voltage, minimum/maximum parameter values also include conditions of minimum/maximum temperature and minimum/maximum supply voltage. Additional details are described where applicable.

| Parameter                                                        | Symbol                                                  | Values |                           |                           | Unit | Note /                                                              |

|------------------------------------------------------------------|---------------------------------------------------------|--------|---------------------------|---------------------------|------|---------------------------------------------------------------------|

|                                                                  |                                                         | Min.   | Тур.                      | Typ. Max.                 |      | <b>Test Condition</b>                                               |

| Voltage Regulator Buffer<br>Capacitance for DMP_M                | $\begin{array}{c} C_{\rm EVRM} \\ {\rm SR} \end{array}$ | 1.0    | -                         | 4.7                       | μF   | 1)                                                                  |

| Voltage Regulator Buffer<br>Capacitance for DMP_1                | $C_{\rm EVR1} \ { m SR}$                                | 0.68   | -                         | 2.2                       | μF   | 1)2)                                                                |

| External Load<br>Capacitance                                     | $C_{L}$ SR                                              | -      | 20 <sup>3)</sup>          | -                         | pF   | pin out<br>driver= default                                          |

| System frequency                                                 | $f_{\rm SYS}{ m SR}$                                    | -      | -                         | 128                       | MHz  | 5)                                                                  |

| Overload current for analog inputs <sup>6)</sup>                 | $I_{\rm OVA}{ m SR}$                                    | -2     | -                         | 5                         | mA   | not subject to<br>production test                                   |

| Overload current for digital inputs <sup>6)</sup>                | $I_{\rm OVD}{\rm SR}$                                   | -5     | -                         | 5                         | mA   | not subject to<br>production test                                   |

| Overload current coupling factor for analog inputs <sup>7)</sup> | K <sub>OVA</sub><br>CC                                  | -      | 2.5 x<br>10 <sup>-4</sup> | 1.5 x<br>10 <sup>-3</sup> | -    | <i>I</i> <sub>OV</sub> < 0 mA;<br>not subject to<br>production test |

|                                                                  |                                                         | _      | 1.0 x<br>10 <sup>-6</sup> | 1.0 x<br>10 <sup>-4</sup> | -    | <i>I</i> <sub>OV</sub> > 0 mA;<br>not subject to<br>production test |

| Overload current coupling factor for digital I/O pins            | K <sub>OVD</sub><br>CC                                  | _      | 1.0 x<br>10 <sup>-2</sup> | 3.0 x<br>10 <sup>-2</sup> |      | <i>I</i> <sub>OV</sub> < 0 mA;<br>not subject to<br>production test |

|                                                                  |                                                         | -      | 1.0 x<br>10 <sup>-4</sup> | 5.0 x<br>10 <sup>-3</sup> |      | I <sub>OV</sub> > 0 mA;<br>not subject to<br>production test        |

# Table 13 Operating Conditions

# 4.2.2 DC Parameters for Lower Voltage Area

Keeping signal levels within the limits specified in this table ensures operation without overload conditions. For signal levels outside these specifications, also refer to the specification of the overload current  $I_{OV}$ .

Note: Operating Conditions apply.

Table 17 is valid under the following conditions:

$V_{\text{DDP}} \ge 3.0 \text{ V}; V_{\text{DDPtyp}} = 3.3 \text{ V}; V_{\text{DDP}} \le 4.5 \text{ V}$

| Parameter                                                                                            | Symbol                   |                                    | Values | 5                         | Unit | Note /                                                                                             |

|------------------------------------------------------------------------------------------------------|--------------------------|------------------------------------|--------|---------------------------|------|----------------------------------------------------------------------------------------------------|

|                                                                                                      |                          | Min.                               | Тур.   | Max.                      |      | Test Condition                                                                                     |

| Pin capacitance (digital<br>inputs/outputs). To be<br>doubled for double bond<br>pins. <sup>1)</sup> | C <sub>IO</sub> CC       | -                                  | -      | 10                        | pF   | not subject to production test                                                                     |

| Input Hysteresis <sup>2)</sup>                                                                       | HYS CC                   | $0.07 	ext{ x}$<br>$V_{	ext{DDP}}$ | _      | -                         | V    | $R_{\rm S} = 0 \ \Omega$                                                                           |

| Absolute input leakage current on pins of analog ports <sup>3)</sup>                                 | I <sub>OZ1</sub>  <br>CC | -                                  | 10     | 200                       | nA   | $V_{\rm IN} > V_{\rm SS}; \\ V_{\rm IN} < V_{\rm DDP}$                                             |

| Absolute input leakage<br>current for all other pins.<br>To be doubled for double                    | I <sub>OZ2</sub>  <br>CC | -                                  | 0.2    | 2.5                       | μA   | $T_{\rm J} \leq 110 ~^{\circ}{\rm C};$<br>$V_{\rm IN} < V_{\rm DDP};$<br>$V_{\rm IN} > V_{\rm SS}$ |

| bond pins. <sup>3)1)4)</sup>                                                                         |                          | -                                  | 0.2    | 8                         | μA   | $T_{\rm J} \leq 150 ~^{\circ}{\rm C};$<br>$V_{\rm IN} < V_{\rm DDP};$<br>$V_{\rm IN} > V_{\rm SS}$ |

| Pull Level Force Current <sup>5)</sup>                                                               | $ I_{PLF} $ SR           | 150                                | -      | -                         |      | 6)                                                                                                 |

| Pull Level Keep Current <sup>7)</sup>                                                                | I <sub>PLK</sub>  <br>SR | -                                  | _      | 10                        | μA   | 6)                                                                                                 |

| Input high voltage<br>(all except XTAL1)                                                             | $V_{\rm IH}{ m SR}$      | 0.7  x<br>$V_{\text{DDP}}$         | -      | V <sub>DDP</sub><br>+ 0.3 | V    |                                                                                                    |

| Input low voltage<br>(all except XTAL1)                                                              | $V_{\rm IL}{\rm SR}$     | -0.3                               | -      | 0.3 x<br>V <sub>DDP</sub> | V    |                                                                                                    |

| Output High voltage <sup>8)</sup>                                                                    | V <sub>OH</sub> CC       | V <sub>DDP</sub><br>- 1.0          | -      | -                         | V    | $I_{\rm OH} \ge I_{\rm OHmax}$                                                                     |

|                                                                                                      |                          | V <sub>DDP</sub><br>- 0.4          | _      | -                         | V    | $I_{\rm OH} \ge I_{\rm OHnom}^{9)}$                                                                |

## Table 17 DC Characteristics for Lower Voltage Range

## 4.4 System Parameters

The following parameters specify several aspects which are important when integrating the XC2368E into an application system.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply.

| Parameter                                                             | Symbol                 | Values                                  |                 |                                            | Unit | Note /                               |

|-----------------------------------------------------------------------|------------------------|-----------------------------------------|-----------------|--------------------------------------------|------|--------------------------------------|

|                                                                       |                        | Min.                                    | Тур.            | Max.                                       |      | Test Condition                       |

| Short-term deviation of internal clock source frequency <sup>1)</sup> | ∆f <sub>INT</sub> CC   | -1                                      | -               | 1                                          | %    | ⊿ <i>T</i> <sub>J</sub> ≤ 10 °C      |

| Internal clock source frequency                                       | $f_{\rm INT}{\rm CC}$  | 4.8                                     | 5.0             | 5.2                                        | MHz  |                                      |

| Wakeup clock source                                                   | $f_{\rm WU}  {\rm CC}$ | 400                                     | -               | 700                                        | kHz  | FREQSEL= 00                          |

| frequency <sup>2)</sup>                                               |                        | 210                                     | -               | 390                                        | kHz  | FREQSEL= 01                          |

|                                                                       |                        | 140                                     | -               | 260                                        | kHz  | FREQSEL= 10                          |

|                                                                       |                        | 110                                     | -               | 200                                        | kHz  | FREQSEL= 11                          |

| Startup time from power-<br>on with code execution<br>from Flash      | t <sub>SPO</sub> CC    | 1.9                                     | 2.5             | 3.7                                        | ms   | $f_{\rm WU}$ = 500 kHz               |

| Startup time from stopover<br>mode with code execution<br>from PSRAM  | t <sub>SSO</sub> CC    | 11 /<br>f <sub>WU</sub> <sup>3)</sup>   | -               | 12 /<br>f <sub>wu</sub> <sup>3)</sup>      | μS   |                                      |

| Core voltage (PVC)<br>supervision level                               | V <sub>PVC</sub> CC    | V <sub>LV</sub><br>- 0.03               | V <sub>LV</sub> | V <sub>LV</sub><br>+ 0.07<br><sub>4)</sub> | V    | 5)                                   |

| Supply watchdog (SWD) supervision level                               | V <sub>SWD</sub><br>CC | V <sub>LV</sub><br>- 0.10 <sup>6)</sup> | $V_{\rm LV}$    | V <sub>LV</sub><br>+ 0.15                  | V    | Lower voltage range <sup>5)</sup>    |

|                                                                       |                        | V <sub>LV</sub><br>- 0.15               | $V_{\rm LV}$    | V <sub>LV</sub><br>+ 0.15                  | V    | Upper voltage<br>range <sup>5)</sup> |

## Table 24Various System Parameters

The short-term frequency deviation refers to a timeframe of a few hours and is measured relative to the current frequency at the beginning of the respective timeframe. This parameter is useful to determine a time span for re-triggering a LIN synchronization.

This parameter is tested for the fastest and the slowest selection. The medium selections are not subject to production test - verified by design/characterization

- 3)  $f_{\rm WU}$  in MHz

- 4) This value includes a hysteresis of approximately 50 mV for rising voltage.

- 5)  $V_{LV}$  = selected PVC/SWD voltage level

- 6) The limit  $V_{LV}$  0.10 V is valid for the OK1 level. The limit for the OK2 level is  $V_{LV}$  0.15 V.

## Conditions for t<sub>SPO</sub> Timing Measurement

The time required for the transition from **Power-On** to **Base** mode is called  $t_{SPO}$ . It is measured under the following conditions:

Precondition: The pad supply is valid, i.e.  $V_{\text{DDPB}}$  is above 3.0 V and remains above 3.0 V even though the XC2368E is starting up. See also  $V_{\text{DDPB}}$  requirements in **Table 13**.

Start condition: Power-on reset is removed ( $\overline{PORST} = 1$ ).

End condition: External pin toggle caused by first user instruction executed from FLASH after startup.

## Conditions for t<sub>SSO</sub> Timing Measurement

The time required for the transition from **Stopover** to **Stopover Waked-Up** mode is called  $t_{SSO}$ . It is measured under the following conditions:

Precondition: The **Stopover** mode has been entered using the procedure defined in the Programmer's Guide.

Start condition: Pin toggle on ESR pin triggering the startup sequence.

End condition: External pin toggle caused by first user instruction executed from PSRAM after startup.

The timing in the AC Characteristics refers to TCSs. Timing must be calculated using the minimum TCS possible under the given circumstances.

The actual minimum value for TCS depends on the jitter of the PLL. Because the PLL is constantly adjusting its output frequency to correspond to the input frequency (from crystal or oscillator), the accumulated jitter is limited. This means that the relative deviation for periods of more than one TCS is lower than for a single TCS (see formulas and Figure 17).

This is especially important for bus cycles using waitstates and for the operation of timers, serial interfaces, etc. For all slower operations and longer periods (e.g. pulse train generation or measurement, lower baudrates, etc.) the deviation caused by the PLL jitter is negligible.

The value of the accumulated PLL jitter depends on the number of consecutive VCO output cycles within the respective timeframe. The VCO output clock is divided by the output prescaler K2 to generate the system clock signal  $f_{SYS}$ . The number of VCO cycles is K2 × **T**, where **T** is the number of consecutive  $f_{SYS}$  cycles (TCS).

The maximum accumulated jitter (long-term jitter) D<sub>Tmax</sub> is defined by:

$D_{\text{Tmax}}$  [ns] = ±(220 / (K2 ×  $f_{\text{SYS}}$ ) + 4.3)

This maximum value is applicable, if either the number of clock cycles T > ( $f_{SYS}$  / 1.2) or the prescaler value K2 > 17.

In all other cases for a timeframe of  $\mathbf{T} \times TCS$  the accumulated jitter  $D_T$  is determined by:

$D_{T}$  [ns] =  $D_{Tmax} \times [(1 - 0.058 \times K2) \times (T - 1) / (0.83 \times f_{SYS} - 1) + 0.058 \times K2]$

$f_{SYS}$  in [MHz] in all formulas.

Example, for a period of 3 TCSs @ 33 MHz and K2 = 4:

$D_{max}$  =  $\pm(220$  / (4  $\times$  33) + 4.3) = 5.97 ns (Not applicable directly in this case!)

$D_3 = 5.97 \times [(1 - 0.058 \times 4) \times (3 - 1) / (0.83 \times 33 - 1) + 0.058 \times 4]$

= 5.97 × [0.768 × 2 / 26.39 + 0.232]

Example, for a period of 3 TCSs @ 33 MHz and K2 = 2:

$D_{max} = \pm(220 / (2 \times 33) + 4.3) = 7.63 \text{ ns}$  (Not applicable directly in this case!)

$\begin{array}{l} \mathsf{D}_3 = 7.63 \times [(1 - 0.058 \times 2) \times (3 - 1) \ / \ (0.83 \times 33 - 1) + 0.058 \times 2] \\ = 7.63 \times [0.884 \times 2 \ / \ 26.39 + 0.116] \end{array}$

Note: The term CLKOUT refers to the reference clock output signal which is generated by selecting  $f_{SYS}$  as the source signal for the clock output signal EXTCLK on pin P2.8 and by enabling the high-speed clock driver on this pin.

## Variable Memory Cycles

External bus cycles of the XC2368E are executed in five consecutive cycle phases (AB, C, D, E, F). The duration of each cycle phase is programmable (via the TCONCSx registers) to adapt the external bus cycles to the respective external module (memory, peripheral, etc.).

The duration of the access phase can optionally be controlled by the external module using the READY handshake input.

This table provides a summary of the phases and the ranges for their length.

|  | Table 34 | Programmable Bus Cy | cle Phases ( | (see timind | diagrams) |

|--|----------|---------------------|--------------|-------------|-----------|

|--|----------|---------------------|--------------|-------------|-----------|

| Bus Cycle Phase                                                                                                                                | Parameter | Valid Values | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------|------|

| Address setup phase, the standard duration of this phase (1 $\dots$ 2 TCS) can be extended by 0 $\dots$ 3 TCS if the address window is changed | tpAB      | 1 2 (5)      | TCS  |

| Command delay phase                                                                                                                            | tpC       | 03           | TCS  |

| Write Data setup/MUX Tristate phase                                                                                                            | tpD       | 0 1          | TCS  |

| Access phase                                                                                                                                   | tpE       | 1 32         | TCS  |

| Address/Write Data hold phase                                                                                                                  | tpF       | 0 3          | TCS  |

Note: The bandwidth of a parameter (from minimum to maximum value) covers the whole operating range (temperature, voltage) as well as process variations. Within a given device, however, this bandwidth is smaller than the specified range. This is also due to interdependencies between certain parameters. Some of these interdependencies are described in additional notes (see standard timing).

Note: Operating Conditions apply;  $C_L = 20 \text{ pF}$ .

Figure 20 Multiplexed Bus Cycle

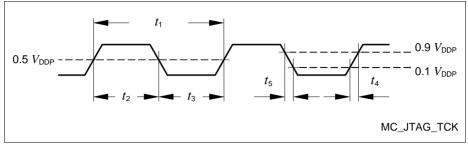

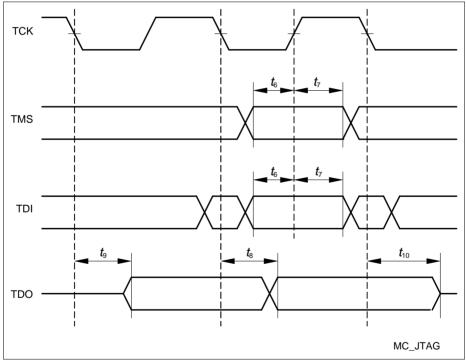

## Debug via JTAG

The following parameters are applicable for communication through the JTAG debug interface. The JTAG module is fully compliant with IEEE1149.1-2000.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply;  $C_L$ = 20 pF.

| Parameter                                                                | Symbol                    | Values           |      |      | Unit | Note /         |

|--------------------------------------------------------------------------|---------------------------|------------------|------|------|------|----------------|

|                                                                          |                           | Min.             | Тур. | Max. |      | Test Condition |

| TCK clock period                                                         | t <sub>1</sub> SR         | 50 <sup>1)</sup> | -    | -    | ns   | 2)             |

| TCK high time                                                            | t <sub>2</sub> SR         | 16               | -    | -    | ns   |                |

| TCK low time                                                             | t <sub>3</sub> SR         | 16               | -    | -    | ns   |                |

| TCK clock rise time                                                      | t <sub>4</sub> SR         | -                | -    | 8    | ns   |                |

| TCK clock fall time                                                      | t <sub>5</sub> SR         | -                | -    | 8    | ns   |                |

| TDI/TMS setup to TCK rising edge                                         | t <sub>6</sub> SR         | 6                | -    | -    | ns   |                |

| TDI/TMS hold after TCK rising edge                                       | t <sub>7</sub> SR         | 6                | -    | -    | ns   |                |

| TDO valid from TCK falling edge (propagation delay) <sup>3)</sup>        | t <sub>8</sub> CC         | -                | 25   | 29   | ns   |                |

| TDO high impedance to valid output from TCK falling edge <sup>4)3)</sup> | t <sub>9</sub> CC         | -                | 25   | 29   | ns   |                |

| TDO valid output to high impedance from TCK falling edge <sup>3)</sup>   | <i>t</i> <sub>10</sub> CC | -                | 25   | 29   | ns   |                |

| TDO hold after TCK falling edge <sup>3)</sup>                            | <i>t</i> <sub>18</sub> CC | 5                | -    | -    | ns   |                |

## Table 44 Interface Timing for Upper Voltage Range

1) The debug interface cannot operate faster than the overall system, therefore  $t_1 \ge t_{SYS}$ .

2) Under typical conditions, the interface can operate at transfer rates up to 20 MHz.

3) The falling edge on TCK is used to generate the TDO timing.

4) The setup time for TDO is given implicitly by the TCK cycle time.

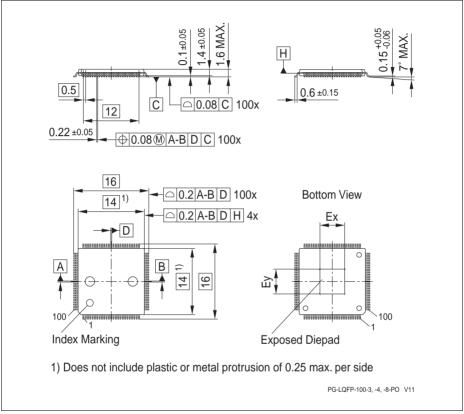

## Package and Reliability

# 5 Package and Reliability

The XC2000 Family devices use the package type PG-LQFP (Plastic Green - Low Profile Quad Flat Package). The following specifications must be regarded to ensure proper integration of the XC2368E in its target environment.

# 5.1 Packaging

These parameters specify the packaging rather than the silicon.

| Parameter                              | Symbol           | Limit | Values        | Unit | Notes                                  |

|----------------------------------------|------------------|-------|---------------|------|----------------------------------------|

|                                        |                  | Min.  | Max.          |      |                                        |

| Exposed Pad Dimension                  | $E x \times E y$ | -     | 7.5 	imes 7.5 | mm   | -                                      |

| Thermal resistance<br>Junction-Ambient | $R_{\Theta JA}$  | -     | 23            | K/W  | 4-layer,<br>pad soldered <sup>1)</sup> |

Table 46

Package Parameters (PG-LQFP-100-8/-15)

Device mounted on a 4-layer JEDEC board (according to JESD 51-7) with thermal vias; exposed pad soldered to the board.

Using this device without the exposed pad soldered or on boards without thermal vias is not recommended.

Note: To improve the EMC behavior, it is recommended to connect the exposed pad to the board ground, independent of the thermal requirements. Board layout examples are given in an application note.

# **Usage in High-Performance Applications**

The XC2368E can deliver a high performance to the system. In some cases additional measures are required to remove the heat from the device.

This may be necessary if the XC2368E is supplied with  $V_{\text{DDP}}$  = 5 V and is operated at a high system frequency in a hot environment.

Applications with  $V_{\text{DDP}}$  = 3.3 V usually require no extra measures.

## Package Compatibility Considerations

The XC2368E is a member of the XC2000 Family of microcontrollers. It is also compatible to a certain extent with members of similar families or subfamilies.

Each package is optimized for the device it houses. Therefore, there may be slight differences between packages of the same pin-count but for different device types. In particular, the size of the Exposed Pad (if present) may vary.

If different device types are considered or planned for an application, it must be ensured that the board layout fits all packages under consideration.

## Package and Reliability

# Package Outlines

Figure 30 PG-LQFP-100-8/-15 (Plastic Green Thin Quad Flat Package)

All dimensions in mm.

You can find complete information about Infineon packages, packing and marking in our Infineon Internet Page "Packages": http://www.infineon.com/packages

## Package and Reliability

# 5.2 Thermal Considerations

When operating the XC2368E in a system, the total heat generated in the chip must be dissipated to the ambient environment to prevent overheating and the resulting thermal damage.

The maximum heat that can be dissipated depends on the package and its integration into the target board. The "Thermal resistance  $R_{\Theta JA}$ " quantifies these parameters. The power dissipation must be limited so that the average junction temperature does not exceed 150 °C.

The difference between junction temperature and ambient temperature is determined by  $\Delta T = (P_{INT} + P_{IOSTAT} + P_{IODYN}) \times R_{\Theta,IA}$

The internal power consumption is defined as

$P_{\text{INT}} = V_{\text{DDP}} \times I_{\text{DDP}}$  (switching current and leakage current).

The static external power consumption caused by the output drivers is defined as  $P_{\text{IOSTAT}} = \Sigma((V_{\text{DDP}} \cdot V_{\text{OH}}) \times I_{\text{OH}}) + \Sigma(V_{\text{OL}} \times I_{\text{OL}})$

The dynamic external power consumption caused by the output drivers ( $P_{IODYN}$ ) depends on the capacitive load connected to the respective pins and their switching frequencies.

If the total power dissipation for a given system configuration exceeds the defined limit, countermeasures must be taken to ensure proper system operation:

- Reduce  $V_{\text{DDP}}$ , if possible in the system

- Reduce the system frequency

- · Reduce the number of output pins

- Reduce the load on active output drivers