Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

ĿXFl

| Details                    |                                                                                         |

|----------------------------|-----------------------------------------------------------------------------------------|

| Product Status             | Last Time Buy                                                                           |

| Core Processor             | ARM® Cortex®-M0                                                                         |

| Core Size                  | 32-Bit Single-Core                                                                      |

| Speed                      | 50MHz                                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LVD, POR, PS2, PWM, WDT                  |

| Number of I/O              | 35                                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                                        |

| Program Memory Type        | FLASH                                                                                   |

| EEPROM Size                | -                                                                                       |

| RAM Size                   | 16K x 8                                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                             |

| Data Converters            | A/D 8x12b                                                                               |

| Oscillator Type            | Internal                                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                       |

| Mounting Type              | Surface Mount                                                                           |

| Package / Case             | 48-LQFP                                                                                 |

| Supplier Device Package    | 48-LQFP (7x7)                                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/nuc100le3an |

|                            |                                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Figures

| Figure 3-1 NuMicro™ NUC100 Medium Density LQFP 100-pin Pin Diagram |

|--------------------------------------------------------------------|

| Figure 3-2 NuMicro™ NUC100 Medium Density LQFP 64-pin Pin Diagram  |

| Figure 3-3 NuMicro™ NUC100 Medium Density LQFP 48-pin Pin Diagram  |

| Figure 3-4 NuMicro™ NUC100 Low Density LQFP 64-pin Pin Diagram     |

| Figure 3-5 NuMicro™ NUC100 Low Density LQFP 48-pin Pin Diagram     |

| Figure 4-1 NuMicro™ NUC100 Medium Density Block Diagram            |

| Figure 4-2 NuMicro™ NUC100 Low Density Block Diagram               |

| Figure 5-1 Functional Controller Diagram                           |

| Figure 5-3 NuMicro™ NUC100 Power Distribution Diagram23            |

| Figure 5-4 Clock generator global view diagram                     |

| Figure 5-5 Clock generator block diagram                           |

| Figure 5-6 System Clock Block Diagram                              |

| Figure 5-7 SysTick Clock Control Block Diagram                     |

| Figure 5-8 Clock Source of Frequency Divider                       |

| Figure 5-9 Block Diagram of Frequency Divider                      |

| Figure 5-10 I <sup>2</sup> C Bus Timing                            |

| Figure 5-11 Timing of Interrupt and Reset Signal                   |

| Figure 7-1 Typical Crystal Application Circuit                     |

| Figure 7-2 SPI Master dynamic characteristics timing               |

| Figure 7-3 SPI Slave dynamic characteristics timing                |

## Tables

| Table 1-1 Connectivity Supported Table                      | 7  |

|-------------------------------------------------------------|----|

| Table 5-1 Address Space Assignments for On-Chip Controllers | 25 |

| Table 5-2 Exception Model                                   | 28 |

| Table 5-3 System Interrupt Map                              | 29 |

| Table 5-4 Vector Table Format                               | 30 |

| Table 5-5 Watchdog Timeout Interval Selection               | 45 |

| Table 5-6 UART Baud Rate Equation                           | 47 |

| Table 5-7 UART Baud Rate Setting Table                      | 48 |

### **1 GENERAL DESCRIPTION**

The NuMicro<sup>™</sup> NUC100 Series is 32-bit microcontrollers with embedded ARM<sup>®</sup> Cortex<sup>™</sup>-M0 core for industrial control and applications which need rich communication interfaces. The Cortex<sup>™</sup>-M0 is the newest ARM<sup>®</sup> embedded processor with 32-bit performance and at a cost equivalent to traditional 8-bit microcontroller. NuMicro<sup>™</sup> NUC100 Series includes NUC100, NUC120, NUC130 and NUC140 product line.

The NuMicro<sup>TM</sup> NUC100 Advanced Line embeds Cortex<sup>TM</sup>-M0 core running up to 50 MHz with 32K/64K/128K-byte embedded flash, 4K/8K/16K-byte embedded SRAM, and 4K-byte loader ROM for the ISP. It also equips with plenty of peripheral devices, such as Timers, Watchdog Timer, RTC, PDMA, UART, SPI, I<sup>2</sup>C, I<sup>2</sup>S, PWM Timer, GPIO, PS/2, 12-bit ADC, Analog Comparator, Low Voltage Reset Controller and Brown-Out Detector.

| Product Line | UART | SPI | l <sup>2</sup> C | USB | LIN | CAN | PS/2 | l <sup>2</sup> S |

|--------------|------|-----|------------------|-----|-----|-----|------|------------------|

| NUC100       | •    | ٠   | •                |     |     |     | •    | •                |

| NUC120       | •    | •   | •                | •   |     |     | •    | •                |

| NUC130       | •    | ٠   | •                |     | •   | •   | •    | •                |

| NUC140       | •    | •   | •                | •   | •   | •   | •    | •                |

Table 1-1 Connectivity Supported Table

- Analog Comparator

- Up to two analog comparators

- External input or internal bandgap voltage selectable at negative node

- Interrupt when compare result change

- Power down wake-up

- $\bullet$  One built-in temperature sensor with 1  $^\circ\!\mathrm{C}$  resolution

- Brown-Out detector

- With 4 levels: 4.5 V/3.8 V/2.7 V/2.2 V

- Support Brown-Out Interrupt and Reset option

- Low Voltage Reset

- Threshold voltage levels: 2.0 V

- Operating Temperature: -40°C ~85°C

- Packages:

- All Green package (RoHS)

- LQFP 100-pin / 64-pin / 48-pin (100-pin for NuMicro<sup>™</sup> NUC100/NUC120 Medium Density Only)

## **3 PARTS INFORMATION LIST AND PIN CONFIGURATION**

### 3.1 NuMicro™ NUC100 Products Selection Guide

| Part number | umbor APPOM PAM Data Load |       | ISP<br>Loader | er I/O Time | Timer    | Connectivity |      |     |                  |     |     | I <sup>2</sup> S | Comp. | PWM   | ADC | RTC      | FBI | ISP      | Package |         |

|-------------|---------------------------|-------|---------------|-------------|----------|--------------|------|-----|------------------|-----|-----|------------------|-------|-------|-----|----------|-----|----------|---------|---------|

|             |                           |       | Flash         | ROM         |          | -            | UART | SPI | I <sup>2</sup> C | USB | LIN | CAN              |       | •••p. |     |          |     | <u> </u> | ICP     |         |

| NUC100LD3AN | 64 KB                     | 16 KB | 4 KB          | 4 KB        | up to 35 | 4x32-bit     | 2    | 1   | 2                | -   | -   | -                | 1     | 1     | 6   | 8x12-bit | v   | -        | v       | LQFP48  |

| NUC100LE3AN | 128 KB                    | 16 KB | Definable     | 4 KB        | up to 35 | 4x32-bit     | 2    | 1   | 2                | -   | -   | -                | 1     | 1     | 6   | 8x12-bit | v   | -        | v       | LQFP48  |

| NUC100RD3AN | 64 KB                     | 16 KB | 4 KB          | 4 KB        | up to 49 | 4x32-bit     | 3    | 2   | 2                | -   | -   | -                | 1     | 2     | 6   | 8x12-bit | v   | -        | v       | LQFP64  |

| NUC100RE3AN | 128 KB                    | 16 KB | Definable     | 4 KB        | up to 49 | 4x32-bit     | 3    | 2   | 2                | -   | -   | -                | 1     | 2     | 6   | 8x12-bit | v   | -        | v       | LQFP64  |

| NUC100VD2AN | 64 KB                     | 8 KB  | 4 KB          | 4 KB        | up to 80 | 4x32-bit     | 3    | 4   | 2                | -   | -   | -                | 1     | 2     | 8   | 8x12-bit | v   | -        | v       | LQFP100 |

| NUC100VD3AN | 64 KB                     | 16 KB | 4 KB          | 4 KB        | up to 80 | 4x32-bit     | 3    | 4   | 2                | -   | -   | -                | 1     | 2     | 8   | 8x12-bit | v   | -        | v       | LQFP100 |

| NUC100VE3AN | 128 KB                    | 16 KB | Definable     | 4 KB        | up to 80 | 4x32-bit     | 3    | 4   | 2                | -   | -   | -                | 1     | 2     | 8   | 8x12-bit | v   | -        | v       | LQFP100 |

#### 3.1.1 NuMicro<sup>™</sup> NUC100 Medium Density Advance Line Selection Guide

### 3.1.2 NuMicro<sup>™</sup> NUC100 Low Density Advance Line Selection Guide

| Part number | APROM | RAM  | Data  | ISP<br>Loader | I/O      | Timer    |      |     |                  | onnectivity |     |     |   | Comp. | PWM | ADC      | RTC | FBI | ISP | Package |

|-------------|-------|------|-------|---------------|----------|----------|------|-----|------------------|-------------|-----|-----|---|-------|-----|----------|-----|-----|-----|---------|

|             |       |      | Flash | ROM           |          | -        | UART | SPI | I <sup>2</sup> C | USB         | LIN | CAN |   |       |     |          |     |     | ICP |         |

| NUC100LC1BN | 32 KB | 4 KB | 4 KB  | 4 KB          | up to 35 | 4x32-bit | 2    | 1   | 2                | -           | -   | -   | 1 | 1     | 4   | 8x12-bit | v   | -   | v   | LQFP48  |

| NUC100LD1BN | 64 KB | 4 KB | 4 KB  | 4 KB          | up to 35 | 4x32-bit | 2    | 1   | 2                | -           | -   | -   | 1 | 1     | 4   | 8x12-bit | v   | -   | v   | LQFP48  |

| NUC100LD2BN | 64 KB | 8 KB | 4 KB  | 4 KB          | up to 35 | 4x32-bit | 2    | 1   | 2                | -           | -   | -   | 1 | 1     | 4   | 8x12-bit | v   | -   | v   | LQFP48  |

| NUC100RC1BN | 32 KB | 4 KB | 4 KB  | 4 KB          | up to 49 | 4x32-bit | 2    | 2   | 2                | -           | -   | -   | 1 | 2     | 4   | 8x12-bit | v   | v   | v   | LQFP64  |

| NUC100RD1BN | 64 KB | 4 KB | 4 KB  | 4 KB          | up to 49 | 4x32-bit | 2    | 2   | 2                | -           | -   | -   | 1 | 2     | 4   | 8x12-bit | v   | v   | v   | LQFP64  |

| NUC100RD2BN | 64 KB | 8 KB | 4 KB  | 4 KB          | up to 49 | 4x32-bit | 2    | 2   | 2                | -           | -   | -   | 1 | 2     | 4   | 8x12-bit | v   | v   | v   | LQFP64  |

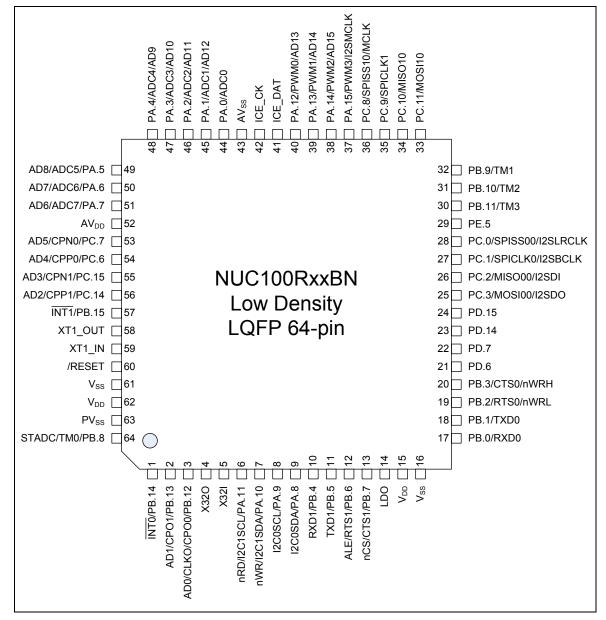

### 3.2.2 NuMicro™ NUC100 Low Density Pin Diagram

3.2.2.1 NuMicro™NUC100 Low Density LQFP 64 pin

Figure 3-4 NuMicro™ NUC100 Low Density LQFP 64-pin Pin Diagram

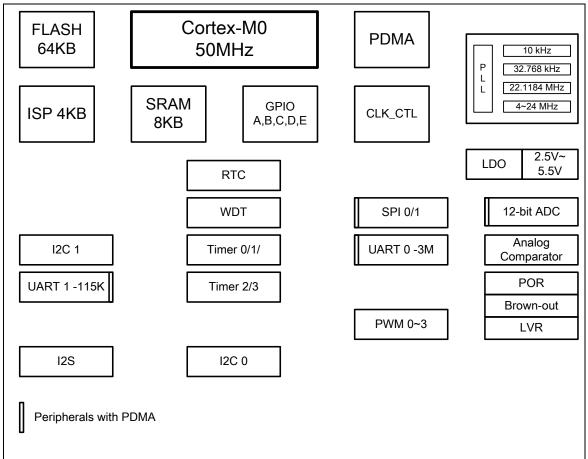

### 4.2 NuMicro<sup>™</sup> NUC100 Low Density Block Diagram

Figure 4-2 NuMicro™ NUC100 Low Density Block Diagram

## **5 FUNCTIONAL DESCRIPTION**

### 5.1 ARM<sup>®</sup> Cortex<sup>™</sup>-M0 Core

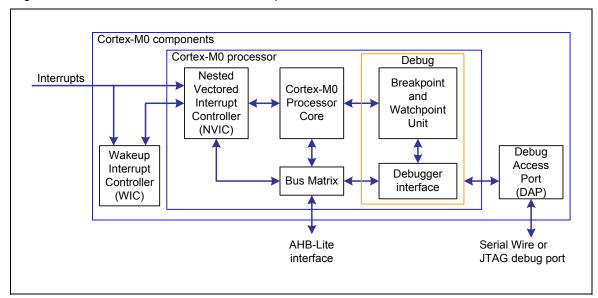

The Cortex<sup>™</sup>-M0 processor is a configurable, multistage, 32-bit RISC processor. It has an AMBA AHB-Lite interface and includes an NVIC component. It also has optional hardware debug functionality. The processor can execute Thumb code and is compatible with other Cortex-M profile processor. The profile supports two modes -Thread mode and Handler mode. Handler mode is entered as a result of an exception. An exception return can only be issued in Handler mode. Thread mode is entered on Reset, and can be entered as a result of an exception return. Figure 5-1 shows the functional controller of processor.

Figure 5-1 Functional Controller Diagram

The implemented device provides:

- A low gate count processor that features:

- The ARMv6-M Thumb® instruction set

- Thumb-2 technology

- ARMv6-M compliant 24-bit SysTick timer

- A 32-bit hardware multiplier

- The system interface supports little-endian data accesses

- The ability to have deterministic, fixed-latency, interrupt handling

- Load/store-multiples and multicycle-multiplies that can be abandoned and restarted to facilitate rapid interrupt handling

- C Application Binary Interface compliant exception model. This is the ARMv6-M, C Application Binary Interface (C-ABI) compliant exception model that enables the use of pure C functions as interrupt handlers

- Low power sleep mode entry using Wait For Interrupt (WFI), Wait For Event (WFE) instructions, or the return from interrupt sleep-on-exit feature

### 5.2 System Manager

#### 5.2.1 Overview

System management includes these following sections:

- System Resets

- System Memory Map

- System management registers for Part Number ID, chip reset and on-chip controllers reset , multi-functional pin control

- System Timer (SysTick)

- Nested Vectored Interrupt Controller (NVIC)

- System Control registers

#### 5.2.2 System Reset

The system reset can be issued by one of the below listed events. For these reset event flags can be read by RSTSRC register.

- The Power-On Reset

- The low level on the /RESET pin

- Watchdog Time Out Reset

- Low Voltage Reset

- Brown-Out Detector Reset

- CPU Reset

- System Reset

System Reset and Power-On Reset all reset the whole chip including all peripherals. The difference between System Reset and Power-On Reset is external crystal circuit and ISPCON.BS bit. System Reset doesn't reset external crystal circuit and ISPCON.BS bit, but Power-On Reset does.

#### 5.2.6 Nested Vectored Interrupt Controller (NVIC)

Cortex-M0 provides an interrupt controller as an integral part of the exception mode, named as "Nested Vectored Interrupt Controller (NVIC)". It is closely coupled to the processor kernel and provides following features:

- Nested and Vectored interrupt support

- Automatic processor state saving and restoration

- Reduced and deterministic interrupt latency

The NVIC prioritizes and handles all supported exceptions. All exceptions are handled in "Handler Mode". This NVIC architecture supports 32 (IRQ[31:0]) discrete interrupts with 4 levels of priority. All of the interrupts and most of the system exceptions can be configured to different priority levels. When an interrupt occurs, the NVIC will compare the priority of the new interrupt to the current running one's priority. If the priority of the new interrupt is higher than the current one, the new interrupt handler will override the current handler.

When any interrupts is accepted, the starting address of the interrupt service routine (ISR) is fetched from a vector table in memory. There is no need to determine which interrupt is accepted and branch to the starting address of the correlated ISR by software. While the starting address is fetched, NVIC will also automatically save processor state including the registers "PC, PSR, LR, R0~R3, R12" to the stack. At the end of the ISR, the NVIC will restore the mentioned registers from stack and resume the normal execution. Thus it will take less and deterministic time to process the interrupt request.

The NVIC supports "Tail Chaining" which handles back-to-back interrupts efficiently without the overhead of states saving and restoration and therefore reduces delay time in switching to pending ISR at the end of current ISR. The NVIC also supports "Late Arrival" which improves the efficiency of concurrent ISRs. When a higher priority interrupt request occurs before the current ISR starts to execute (at the stage of state saving and starting address fetching), the NVIC will give priority to the higher one without delay penalty. Thus it advances the real-time capability.

For more detailed information, please refer to the documents "ARM<sup>®</sup> Cortex<sup>™</sup>-M0 Technical Reference Manual" and "ARM<sup>®</sup> v6-M Architecture Reference Manual".

#### 5.3.3 System Clock and SysTick Clock

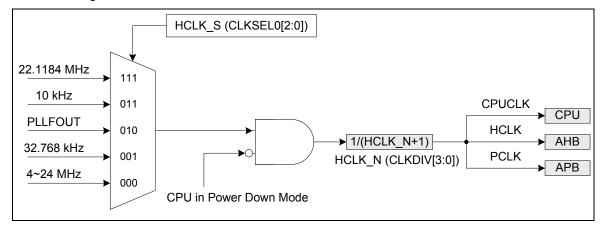

The system clock has 5 clock sources which were generated from clock generator block. The clock source switch depends on the register HCLK\_S (CLKSEL0[2:0]). The block diagram is showed in Figure 5-5.

Figure 5-5 System Clock Block Diagram

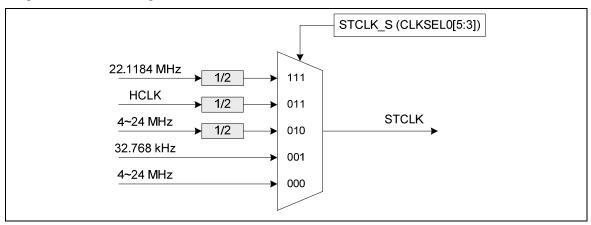

The clock source of SysTick in Cortex-M0 core can use CPU clock or external clock (SYST\_CSR[2]). If using external clock, the SysTick clock (STCLK) has 5 clock sources. The clock source switch depends on the setting of the register STCLK\_S (CLKSEL0[5:3]). The block diagram is showed in Figure 5-6.

Figure 5-6 SysTick Clock Control Block Diagram

### 5.4 General Purpose I/O (GPIO)

#### 5.4.1 Overview

NuMicro<sup>™</sup> NUC100/NUC120 Medium Density has up to 80 General Purpose I/O pins can be shared with other function pins; it depends on the chip configuration. These 80 pins are arranged in 5 ports named with GPIOA, GPIOB, GPIOC, GPIOD and GPIOE. Each port equips maximum 16 pins. Each one of the 80 pins is independent and has the corresponding register bits to control the pin mode function and data.

NuMicro<sup>™</sup> NUC100/NUC120 Low Density has up to 65 General Purpose I/O pins can be shared with other function pins; it depends on the chip configuration and package. These 65 pins are arranged in 4 ports named with GPIOA, GPIOB, GPIOC and GPIOD with each port equips maximum 16 pins and another port named GPIOE with 1 pins PE.5.

The I/O type of each of I/O pins can be configured by software individually as input, output, opendrain or quasi-bidirectional mode. After reset, the I/O type of all pins stay in quasi-bidirectional mode and port data register GPIOx\_DOUT[15:0] resets to 0x0000\_FFFF. Each I/O pin equips a very weakly individual pull-up resistor which is about 110K $\Omega$ ~300K $\Omega$  for V<sub>DD</sub> is from 5.0 V to 2.5 V.

#### 5.4.2 Features

- Four I/O modes:

- Quasi bi-direction

- Push-Pull output

- Open-Drain output

- Input only with high impendence

- TTL/Schmitt trigger input selectable

- I/O pin can be configured as interrupt source with edge/level setting

- High driver and high sink IO mode support

#### 5.5.2 Features

The I<sup>2</sup>C bus uses two wires (SDA and SCL) to transfer information between devices connected to the bus. The main features of the bus are:

- Master/Slave mode

- Bidirectional data transfer between masters and slaves

- Multi-master bus (no central master)

- Arbitration between simultaneously transmitting masters without corruption of serial data on the bus

- Serial clock synchronization allows devices with different bit rates to communicate via one serial bus

- Serial clock synchronization can be used as a handshake mechanism to suspend and resume serial transfer

- Built-in a 14-bit time-out counter will request the I<sup>2</sup>C interrupt if the I<sup>2</sup>C bus hangs up and timer-out counter overflows.

- External pull-up are needed for high output

- Programmable clocks allow versatile rate control

- Supports 7-bit addressing mode

- I<sup>2</sup>C-bus controllers support multiple address recognition (Four slave address with mask option)

the PWM counter 0/1/2/3 will be reload at this moment.

The maximum captured frequency that PWM can capture is confined by the capture interrupt latency. When capture interrupt occurred, software will do at least three steps, they are: Read PIIR to get interrupt source and Read CRLRx/CFLRx(x=0~3) to get capture value and finally write 1 to clear PIIR to zero. If interrupt latency will take time T0 to finish, the capture signal mustn't transition during this interval (T0). In this case, the maximum capture frequency will be 1/T0. For example:

HCLK = 50 MHz, PWM\_CLK = 25 MHz, Interrupt latency is 900 ns

So the maximum capture frequency will is 1/900ns  $\approx$  1000 kHz

#### 5.6.2 Features

5.6.2.1 PWM function features:

- PWM group has two PWM generators. Each PWM generator supports one 8-bit prescaler, one clock divider, two PWM-timers (down counter), one dead-zone generator and two PWM outputs.

- Up to 16-bit resolution

- PWM Interrupt request synchronized with PWM period

- One-shot or Auto-reload mode PWM

- Up to 2 PWM group (PWMA/PWMB) to support 8 PWM channels or 4 PWM paired channels (only 1 PWM group support for NuMicro™ NUC100/NUC120 Low Density)

- 5.6.2.2 Capture Function Features:

- Timing control logic shared with PWM Generators

- Support 8 Capture input channels shared with 8 PWM output channels (NuMicro™ NUC100/NUC120 Low Density only support 4 Capture input channels shared with 4 PWM output channels)

- Each channel supports one rising latch register (CRLR), one falling latch register (CFLR) and Capture interrupt flag (CAPIFx)

#### 5.10.2 Features

- 18-bit free running counter to avoid chip from Watchdog timer reset before the delay time expires.

- Selectable time-out interval (2<sup>4</sup> ~ 2<sup>18</sup>) and the time out interval is 104 ms ~ 26.3168 s (if WDT\_CLK = 10 kHz).

- Reset period = (1 / 10 kHz) \* 63, if WDT\_CLK = 10 kHz.

### 5.11 UART Interface Controller (UART)

NuMicro<sup>™</sup> NUC100/NUC120 Medium Density provides up to three channels of Universal Asynchronous Receiver/Transmitters (UART). UART0 supports High Speed UART and UART1~2 perform Normal Speed UART, besides, only UART0 and UART1 support flow control function. NuMicro<sup>™</sup> NUC100/NUC120 Low Density only supports UART0 and UART1.

#### 5.11.1 Overview

The Universal Asynchronous Receiver/Transmitter (UART) performs a serial-to-parallel conversion on data received from the peripheral, and a parallel-to-serial conversion on data transmitted from the CPU. The UART controller also supports IrDA SIR Function and RS-485 mode functions. Each UART channel supports seven types of interrupts including transmitter FIFO empty interrupt (INT\_THRE), receiver threshold level reaching interrupt (INT\_RDA), line status interrupt (parity error or framing error or break interrupt) (INT\_RLS), receiver buffer time out interrupt (INT\_TOUT), MODEM/Wake-up status interrupt (INT\_MODEM) and Buffer error interrupt (INT\_BUF\_ERR). Interrupts of UART0 and UART2 share the interrupt number 12 (vector number is 28); Interrupt number 13 (vector number is 29) only supports UART1 interrupt. Refer to Nested Vectored Interrupt Controller chapter for System Interrupt Map.

The UART0 is built-in with a 64-byte transmitter FIFO (TX\_FIFO) and a 64-byte receiver FIFO (RX\_FIFO) that reduces the number of interrupts presented to the CPU and the UART1~2 are equipped 16-byte transmitter FIFO (TX\_FIFO) and 16-byte receiver FIFO (RX\_FIFO). The CPU can read the status of the UART at any time during the operation. The reported status information includes the type and condition of the transfer operations being performed by the UART, as well as 4 error conditions (parity error, framing error, break interrupt and buffer error) probably occur while receiving data. The UART includes a programmable baud rate generator that is capable of dividing clock input by divisors to produce the serial clock that transmitter and receiver need. The baud rate equation is Baud Rate = UART\_CLK / M \* [BRD + 2], where M and BRD are defined in Baud Rate Divider Register (UA\_BAUD). Table 5-6 lists the equations in the various conditions and Table 5-7 list the UART baud rate setting table.

| Mode | DIV_X_EN | DIV_X_ONE | Divider X  | BRD | Baud rate equation                       |  |  |  |  |  |

|------|----------|-----------|------------|-----|------------------------------------------|--|--|--|--|--|

| 0    | 0        | 0         | В          | А   | UART_CLK / [16 * (A+2)]                  |  |  |  |  |  |

| 1    | 1        | 0         | В          | А   | UART_CLK / [(B+1) * (A+2)] , B must >= 8 |  |  |  |  |  |

| 2    | 1        | 1         | Don't care | А   | UART_CLK / (A+2), A must >=3             |  |  |  |  |  |

Table 5-6 UART Baud Rate Equation

|           | Syst      | em clock = Inter | nal 22.1184 MI                        | Hz high speed os                          | cillator  |             |  |  |

|-----------|-----------|------------------|---------------------------------------|-------------------------------------------|-----------|-------------|--|--|

| Baud rate | М         | ode0             | М                                     | ode1                                      | Mode2     |             |  |  |

| Daud Tale | Parameter | Register         | Parameter                             | Register                                  | Parameter | Register    |  |  |

| 921600    | x         | х                | A=0,B=11                              | 0x2B00_0000                               | A=22      | 0x3000_0016 |  |  |

| 460800    | A=1       | 0x0000_0001      | A=1,B=15<br>A=2,B=11                  | 0x2F00_0001<br>0x2B00_0002                | A=46      | 0x3000_002E |  |  |

| 230400    | A=4       | 0x0000_0004      | A=4,B=15<br>A=6,B=11                  | 0x2F00_0004<br>0x2B00_0006                | A=94      | 0x3000_005E |  |  |

| 115200    | A=10      | 0x0000_000A      | A=10,B=15<br>A=14,B=11                | 0x2F00_000A<br>0x2B00_000E                | A=190     | 0x3000_00BE |  |  |

| 57600     | A=22      | 0x0000_0016      | A=22,B=15<br>A=30,B=11                | 0x2F00_0016<br>0x2B00_001E                | A=382     | 0x3000_017E |  |  |

| 38400     | A=34      | 0x0000_0022      | A=62,B=8<br>A=46,B=11<br>A=34,B=15    | 0x2800_003E<br>0x2B00_002E<br>0x2F00_0022 | A=574     | 0x3000_023E |  |  |

| 19200     | A=70      | 0x0000_0046      | A=126,B=8<br>A=94,B=11<br>A=70,B=15   | 0x2800_007E<br>0x2B00_005E<br>0x2F00_0046 | A=1150    | 0x3000_047E |  |  |

| 9600      | A=142     | 0x0000_008E      | A=254,B=8<br>A=190,B=11<br>A=142,B=15 | 0x2800_00FE<br>0x2B00_00BE<br>0x2F00_008E | A=2302    | 0x3000_08FE |  |  |

| 4800      | A=286     | 0x0000_011E      | A=510,B=8<br>A=382,B=11<br>A=286,B=15 | 0x2800_01FE<br>0x2B00_017E<br>0x2F00_011E | A=4606    | 0x3000_11FE |  |  |

Table 5-7 UART Baud Rate Setting Table

The UART0 and UART1 controllers support auto-flow control function that uses two low-level signals, /CTS (clear-to-send) and /RTS (request-to-send), to control the flow of data transfer between the UART and external devices (ex: Modem). When auto-flow is enabled, the UART is not allowed to receive data until the UART asserts /RTS to external device. When the number of bytes in the RX FIFO equals the value of RTS\_TRI\_LEV (UA\_FCR [19:16]), the /RTS is deasserted. The UART sends data out when UART controller detects /CTS is asserted from external device. If a valid asserted /CTS is not detected the UART controller will not send data out.

The UART controllers also provides Serial IrDA (SIR, Serial Infrared) function (User must set IrDA\_EN (UA\_FUN\_SEL [1]) to enable IrDA function). The SIR specification defines a short-range infrared asynchronous serial transmission mode with one start bit, 8 data bits, and 1 stop bit. The maximum data rate is 115.2 Kbps (half duplex). The IrDA SIR block contains an IrDA SIR Protocol encoder/decoder. The IrDA SIR protocol is half-duplex only. So it cannot transmit and receive data at the same time. The IrDA SIR physical layer specifies a minimum 10ms transfer delay between transmission and reception. This delay feature must be implemented by software.

For NuMicro<sup>™</sup> NUC100/NUC120 Low Density, another alternate function of UART controllers is RS-485 9-bit mode function, and direction control provided by RTS pin or can program GPIO (PB.2 for RTS0 and PB.6 for RTS1) to implement the function by software. The RS-485 mode is selected by setting the UA\_FUN\_SEL register to select RS-485 function. The RS-485 driver control is implemented using the RTS control signal from an asynchronous serial port to enable the RS-485 driver. In RS-485 mode, many characteristics of the RX and TX are same as UART.

## 5.13 I<sup>2</sup>S Controller (I<sup>2</sup>S)

#### 5.13.1 Overview

The I<sup>2</sup>S controller consists of IIS protocol to interface with external audio CODEC. Two 8 word deep FIFO for read path and write path respectively and is capable of handling 8  $\sim$  32 bit word sizes. DMA controller handles the data movement between FIFO and memory.

#### 5.13.2 Features

- I<sup>2</sup>S can operate as either master or slave

- Capable of handling 8-, 16-, 24- and 32-bit word sizes

- Mono and stereo audio data supported

- I<sup>2</sup>S and MSB justified data format supported

- Two 8 word FIFO data buffers are provided, one for transmit and one for receive

- Generates interrupt requests when buffer levels cross a programmable boundary

- Two DMA requests, one for transmit and one for receive

### 7.2 DC Electrical Characteristics

#### 7.2.1 NuMicro™ NUC100/NUC120 Medium Density DC Electrical Characteristics

(V<sub>DD</sub>-V<sub>SS</sub>=3.3 V, TA = 25°C, FOSC = 50 MHz unless otherwise specified.)

| PARAMETER                            | SYM.                                | S    | SPECIFIC | CATION           |      | TEST CONDITIONS                                |

|--------------------------------------|-------------------------------------|------|----------|------------------|------|------------------------------------------------|

|                                      | 0110.                               | MIN. | TYP.     | MAX.             | UNIT |                                                |

| Operation voltage                    | V <sub>DD</sub>                     | 2.5  |          | 5.5              | v    | V <sub>DD</sub> =2.5 V ~ 5.5 V up to 50 MHz    |

| Power Ground                         | V <sub>SS</sub><br>AV <sub>SS</sub> | -0.3 |          |                  | v    |                                                |

| LDO Output Voltage                   | $V_{LDO}$                           | -10% | 2.5      | +10%             | V    | V <sub>DD</sub> > 2.7 V                        |

| Analog Operating Voltage             | $AV_{DD}$                           | 0    |          | V <sub>DD</sub>  | v    |                                                |

| Analog Reference Voltage             | Vref                                | 0    |          | AV <sub>DD</sub> | V    |                                                |

|                                      |                                     |      |          |                  |      | V <sub>DD</sub> = 5.5 V@50 MHz,                |

|                                      | I <sub>DD1</sub>                    |      | 54       |                  | mA   | enable all IP and PLL, XTAL=12<br>MHz          |

|                                      |                                     |      |          |                  |      | V <sub>DD</sub> = 5.5 V@ 50 MHz,               |

| Operating Current<br>Normal Run Mode | I <sub>DD2</sub>                    |      | 31       |                  | mA   | disable all IP and enable PLL,<br>XTAL=12 MHz  |

| @ 50 MHz                             |                                     |      |          |                  |      | V <sub>DD</sub> = 3 V@50 MHz,                  |

|                                      | I <sub>DD3</sub>                    |      | 51       |                  | mA   | enable all IP and PLL, XTAL=12<br>MHz          |

|                                      |                                     |      |          |                  |      | V <sub>DD</sub> = 3 V@50 MHz,                  |

|                                      | I <sub>DD4</sub>                    |      | 28       |                  | mA   | disable all IP and enable PLL,<br>XTAL=12 MHz  |

| Operating Current                    |                                     |      |          |                  |      | V <sub>DD</sub> = 5.5 V@12 MHz,                |

| Normal Run Mode<br>@ 12 MHz          | I <sub>DD5</sub>                    |      | 22       |                  | mA   | enable all IP and disable PLL,<br>XTAL=12 MHz  |

|                                      |                                     |      |          |                  |      | V <sub>DD</sub> = 5.5 V@12 MHz,                |

|                                      | I <sub>DD6</sub>                    |      | 14       |                  | mA   | disable all IP and disable PLL,<br>XTAL=12 MHz |

|                                      |                                     |      |          |                  |      | V <sub>DD</sub> = 3 V@12MHz,                   |

|                                      | I <sub>DD7</sub>                    |      | 20       |                  | mA   | enable all IP and disable PLL,<br>XTAL=12 MHz  |

| PARAMETER                                  | SYM.               | 5    | SPECIFIC | CATION |      | TEST CONDITIONS                                                                   |

|--------------------------------------------|--------------------|------|----------|--------|------|-----------------------------------------------------------------------------------|

| FARAIVIETER                                | 5111.              | MIN. | TYP.     | MAX.   | UNIT |                                                                                   |

|                                            | I <sub>DD8</sub>   |      | 12       |        | mA   | V <sub>DD</sub> = 3 V@12 MHz,<br>disable all IP and disable PLL,<br>XTAL=12 MHz   |

|                                            | I <sub>DD9</sub>   |      | 15       |        | mA   | V <sub>DD</sub> = 5 V@4 MHz,<br>enable all IP and disable PLL,<br>XTAL=4 MHz      |

| Operating Current<br>Normal Run Mode       | I <sub>DD10</sub>  |      | 11       |        | mA   | V <sub>DD</sub> = 5 V@4 MHz,<br>disable all IP and disable PLL,<br>XTAL=4 MHz     |

| @ 4 MHz                                    | I <sub>DD11</sub>  |      | 13       |        | mA   | V <sub>DD</sub> = 3 V@4 MHz,<br>enable all IP and disable PLL,<br>XTAL=4 MHz      |

|                                            | I <sub>DD12</sub>  |      | 9        |        | mA   | V <sub>DD</sub> = 3 V@4 MHz,<br>disable all IP and disable PLL,<br>XTAL=4 MHz     |

|                                            | I <sub>IDLE1</sub> |      | 38       |        | mA   | V <sub>DD</sub> = 5.5 V@50 MHz,<br>enable all IP and PLL, XTAL=12<br>MHz          |

| Operating Current<br>Idle Mode             | I <sub>IDLE2</sub> |      | 15       |        | mA   | VDD=5.5 V@50 MHz,<br>disable all IP and enable PLL,<br>XTAL=12 MHz                |

| @ 50 MHz                                   | I <sub>IDLE3</sub> |      | 35       |        | mA   | V <sub>DD</sub> = 3 V@50 MHz,<br>enable all IP and PLL, XTAL=12<br>MHz            |

|                                            | I <sub>IDLE4</sub> |      | 13       |        | mA   | V <sub>DD</sub> = 3 V@50 MHz,<br>disable all IP and enable PLL,<br>XTAL=12 MHz    |

| Operating Current<br>Idle Mode<br>@ 12 MHz | I <sub>IDLE5</sub> |      | 13       |        | mA   | V <sub>DD</sub> = 5.5 V@12 MHz,<br>enable all IP and disable PLL,<br>XTAL=12 MHz  |

|                                            | I <sub>IDLE6</sub> |      | 5.5      |        | mA   | V <sub>DD</sub> = 5.5 V@12 MHz,<br>disable all IP and disable PLL,<br>XTAL=12 MHz |

|                                            | I <sub>IDLE7</sub> |      | 12       |        | mA   | V <sub>DD</sub> = 3 V@12 MHz,<br>enable all IP and disable PLL,<br>XTAL=12 MHz    |

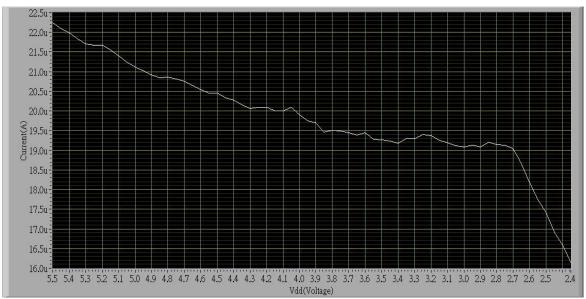

7.2.5 Power Down Current Curve

XTAL clock = 12 MHz, PLL Disable

Unit: mA