#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Last Time Buy                                                                           |  |  |  |  |

|----------------------------|-----------------------------------------------------------------------------------------|--|--|--|--|

| Core Processor             | ARM® Cortex®-M0                                                                         |  |  |  |  |

| Core Size                  | 32-Bit Single-Core                                                                      |  |  |  |  |

| Speed                      | 50MHz                                                                                   |  |  |  |  |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                                 |  |  |  |  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LVD, POR, PS2, PWM, WDT                  |  |  |  |  |

| Number of I/O              | 80                                                                                      |  |  |  |  |

| Program Memory Size        | 128KB (128K x 8)                                                                        |  |  |  |  |

| Program Memory Type        | FLASH                                                                                   |  |  |  |  |

| EEPROM Size                | -                                                                                       |  |  |  |  |

| RAM Size                   | 16K x 8                                                                                 |  |  |  |  |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                             |  |  |  |  |

| Data Converters            | A/D 8x12b                                                                               |  |  |  |  |

| Oscillator Type            | Internal                                                                                |  |  |  |  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                       |  |  |  |  |

| Mounting Type              | Surface Mount                                                                           |  |  |  |  |

| Package / Case             | 100-LQFP                                                                                |  |  |  |  |

| Supplier Device Package    | -                                                                                       |  |  |  |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/nuc100ve3an |  |  |  |  |

|                            |                                                                                         |  |  |  |  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

8

9

|                  | 7.3                | AC El | ectrical Characteristics                   | . 73 |  |  |  |

|------------------|--------------------|-------|--------------------------------------------|------|--|--|--|

|                  |                    | 7.3.1 | External 4~24 MHz High Speed Crystal       | 73   |  |  |  |

|                  |                    | 7.3.2 | External 32.768 kHz Low Speed Crystal      | 74   |  |  |  |

|                  |                    | 7.3.3 | Internal 22.1184 MHz High Speed Oscillator | 74   |  |  |  |

|                  |                    | 7.3.4 | Internal 10 kHz Low Speed Oscillator       | 74   |  |  |  |

|                  | 7.4                | Analo | g Characteristics                          | . 75 |  |  |  |

|                  |                    | 7.4.1 | Specification of 12-bit SARADC             | 75   |  |  |  |

|                  |                    | 7.4.2 | Specification of LDO and Power management  | 76   |  |  |  |

|                  |                    | 7.4.3 | Specification of Low Voltage Reset         | 77   |  |  |  |

|                  |                    | 7.4.4 | Specification of Brown-Out Detector        | 77   |  |  |  |

|                  |                    | 7.4.5 | Specification of Power-On Reset (5 V)      | 77   |  |  |  |

|                  |                    | 7.4.6 | Specification of Temperature Sensor        | 78   |  |  |  |

|                  |                    | 7.4.7 | Specification of Comparator                | 78   |  |  |  |

|                  | 7.5                | Flash | DC Electrical Characteristics              | . 79 |  |  |  |

|                  | 7.6                | SPI D | ynamic Characteristics                     | . 80 |  |  |  |

|                  | PACKAGE DIMENSIONS |       |                                            |      |  |  |  |

|                  | 8.1                | 100L  | LQFP (14x14x1.4 mm footprint 2.0mm)        | . 82 |  |  |  |

|                  | 8.2                | 64L L | QFP (10x10x1.4mm footprint 2.0 mm)         | . 83 |  |  |  |

|                  | 8.3                | 48L L | QFP (7x7x1.4mm footprint 2.0mm)            | . 84 |  |  |  |

| REVISION HISTORY |                    |       |                                            |      |  |  |  |

- Analog Comparator

- Up to two analog comparators

- External input or internal bandgap voltage selectable at negative node

- Interrupt when compare result change

- Power down wake-up

- $\bullet$  One built-in temperature sensor with 1  $^\circ\!\mathrm{C}$  resolution

- Brown-Out detector

- With 4 levels: 4.5 V/3.8 V/2.7 V/2.2 V

- Support Brown-Out Interrupt and Reset option

- Low Voltage Reset

- Threshold voltage levels: 2.0 V

- Operating Temperature: -40°C ~85°C

- Packages:

- All Green package (RoHS)

- LQFP 100-pin / 64-pin / 48-pin (100-pin for NuMicro<sup>™</sup> NUC100/NUC120 Medium Density Only)

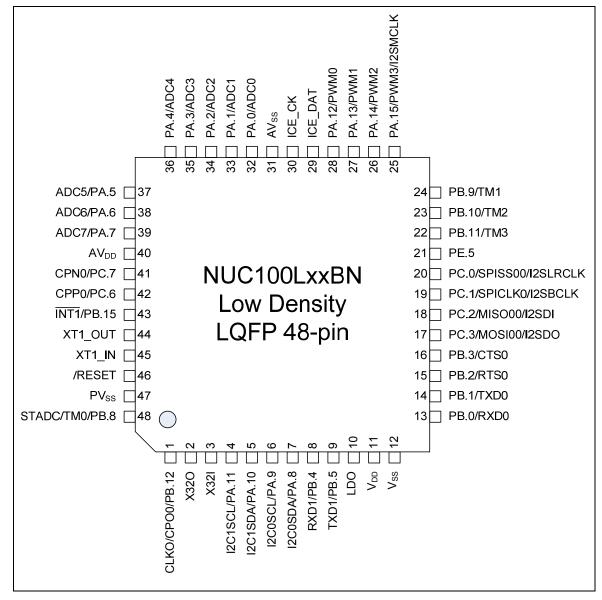

3.2.2.2 NuMicro™NUC100 Low Density LQFP 48 pin

Figure 3-5 NuMicro™ NUC100 Low Density LQFP 48-pin Pin Diagram

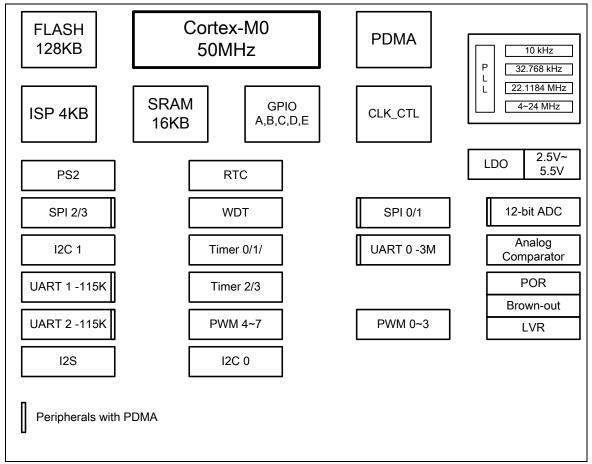

### 4 BLOCK DIAGRAM

### 4.1 NuMicro<sup>™</sup> NUC100 Medium Density Block Diagram

Figure 4-1 NuMicro™ NUC100 Medium Density Block Diagram

## **5 FUNCTIONAL DESCRIPTION**

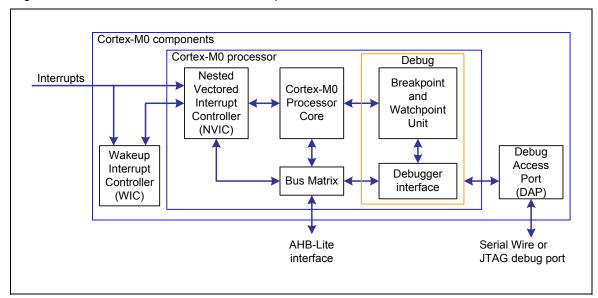

### 5.1 ARM<sup>®</sup> Cortex<sup>™</sup>-M0 Core

The Cortex<sup>™</sup>-M0 processor is a configurable, multistage, 32-bit RISC processor. It has an AMBA AHB-Lite interface and includes an NVIC component. It also has optional hardware debug functionality. The processor can execute Thumb code and is compatible with other Cortex-M profile processor. The profile supports two modes -Thread mode and Handler mode. Handler mode is entered as a result of an exception. An exception return can only be issued in Handler mode. Thread mode is entered on Reset, and can be entered as a result of an exception return. Figure 5-1 shows the functional controller of processor.

Figure 5-1 Functional Controller Diagram

The implemented device provides:

- A low gate count processor that features:

- The ARMv6-M Thumb® instruction set

- Thumb-2 technology

- ARMv6-M compliant 24-bit SysTick timer

- A 32-bit hardware multiplier

- The system interface supports little-endian data accesses

- The ability to have deterministic, fixed-latency, interrupt handling

- Load/store-multiples and multicycle-multiplies that can be abandoned and restarted to facilitate rapid interrupt handling

- C Application Binary Interface compliant exception model. This is the ARMv6-M, C Application Binary Interface (C-ABI) compliant exception model that enables the use of pure C functions as interrupt handlers

- Low power sleep mode entry using Wait For Interrupt (WFI), Wait For Event (WFE) instructions, or the return from interrupt sleep-on-exit feature

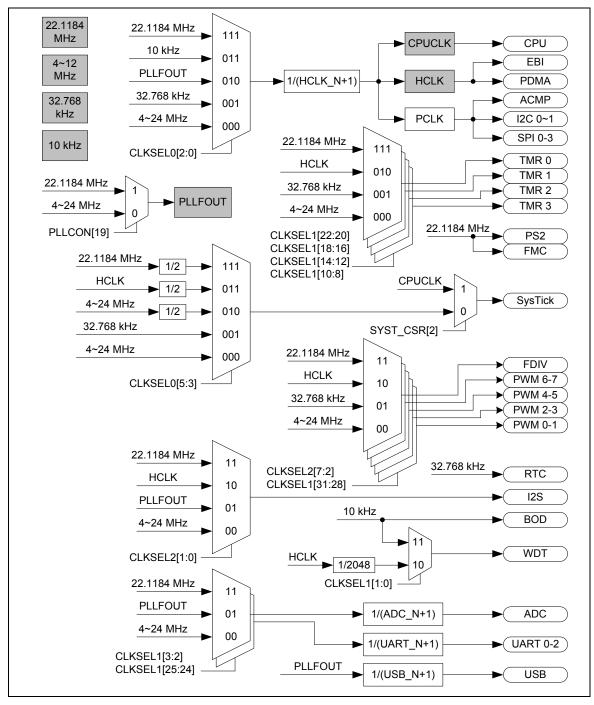

Figure 5-3 Clock generator global view diagram

#### 5.3.4 Peripherals Clock

The peripherals clock had different clock source switch setting which depends on the different peripheral. Please refer the CLKSEL1 and CLKSEL2 register description in 5.3.7.

#### 5.3.5 Power Down Mode Clock

When chip enters into power down mode, system clocks, some clock sources, and some peripheral clocks will be disabled. Some clock sources and peripherals clock are still active in power down mode.

For theses clocks which still keep active list below:

- Clock Generator

- Internal 10 kHz low speed oscillator clock

- External 32.768 kHz low speed crystal clock

- Peripherals Clock (When WDT adopt internal 10 kHz low speed oscillator as clock source and RTC adopt external 32.768 kHz low speed crystal as clock source)

#### 5.3.6 Frequency Divider Output

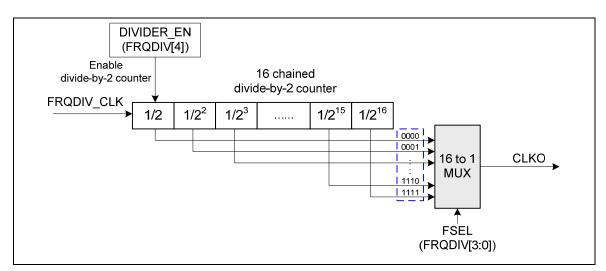

This device is equipped a power-of-2 frequency divider which is composed by16 chained divideby-2 shift registers. One of the 16 shift register outputs selected by a sixteen to one multiplexer is reflected to CLKO function pin. Therefore there are 16 options of power-of-2 divided clocks with the frequency from  $F_{in}/2^{16}$  where Fin is input clock frequency to the clock divider.

The output formula is  $F_{out} = F_{in}/2^{(N+1)}$ , where  $F_{in}$  is the input clock frequency,  $F_{out}$  is the clock divider output frequency and N is the 4-bit value in FSEL (FRQDIV[3:0]).

When write 1 to DIVIDER\_EN (FRQDIV[4]), the chained counter starts to count. When write 0 to DIVIDER\_EN (FRQDIV[4]), the chained counter continuously runs till divided clock reaches low state and stay in low state.

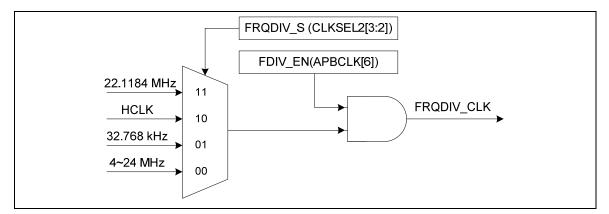

Figure 5-7 Clock Source of Frequency Divider

Figure 5-8 Block Diagram of Frequency Divider

### 5.5 I<sup>2</sup>C Serial Interface Controller (Master/Slave) (I<sup>2</sup>C)

#### 5.5.1 Overview

$I^2C$  is a two-wire, bi-directional serial bus that provides a simple and efficient method of data exchange between devices. The  $I^2C$  standard is a true multi-master bus including collision detection and arbitration that prevents data corruption if two or more masters attempt to control the bus simultaneously.

Data is transferred between a Master and a Slave synchronously to SCL on the SDA line on a byte-by-byte basis. Each data byte is 8-bit long. There is one SCL clock pulse for each data bit with the MSB being transmitted first. An acknowledge bit follows each transferred byte. Each bit is sampled during the high period of SCL; therefore, the SDA line may be changed only during the low period of SCL and must be held stable during the high period of SCL. A transition on the SDA line while SCL is high is interpreted as a command (START or STOP). Please refer to the Figure 5-9 for more detail I<sup>2</sup>C BUS Timing.

Figure 5-9 I<sup>2</sup>C Bus Timing

The device's on-chip I<sup>2</sup>C logic provides the serial interface that meets the I<sup>2</sup>C bus standard mode specification. The I<sup>2</sup>C port handles byte transfers autonomously. To enable this port, the bit ENS1 in I2CON should be set to '1'. The I<sup>2</sup>C H/W interfaces to the I<sup>2</sup>C bus via two pins: SDA and SCL. Pull up resistor is needed for I<sup>2</sup>C operation as these are open drain pins. When the I/O pins are used as I<sup>2</sup>C port, user must set the pins function to I<sup>2</sup>C in advance.

### 5.6 **PWM Generator and Capture Timer (PWM)**

#### 5.6.1 Overview

NuMicro<sup>™</sup> NUC100/NUC120 Medium Density has 2 sets of PWM group supports total 4 sets of PWM Generators which can be configured as 8 independent PWM outputs, PWM0~PWM7, or as 4 complementary PWM pairs, (PWM0, PWM1), (PWM2, PWM3), (PWM4, PWM5) and (PWM6, PWM7) with 4 programmable dead-zone generators. NuMicro<sup>™</sup> NUC100/NUC120 Low Density only support 1 set of PWM group supports total 2 sets of PWM Generators which can be configured as 4 independent PWM outputs, PWM0~PWM3, or as 2 complementary PWM pairs, (PWM0, PWM1) and (PWM2, PWM3) with 2 programmable dead-zone generators.

Each PWM Generator has one 8-bit prescaler, one clock divider with 5 divided frequencies (1, 1/2, 1/4, 1/8, 1/16), two PWM Timers including two clock selectors, two 16-bit PWM downcounters for PWM period control, two 16-bit comparators for PWM duty control and one deadzone generator. The 4 sets of PWM Generators provide eight independent PWM interrupt flags which are set by hardware when the corresponding PWM period down counter reaches zero. Each PWM interrupt source with its corresponding enable bit can cause CPU to request PWM interrupt. The PWM generators can be configured as one-shot mode to produce only one PWM cycle signal or auto-reload mode to output PWM waveform continuously.

When PCR.DZEN01 is set, PWM0 and PWM1 perform complementary PWM paired function; the paired PWM period, duty and dead-time are determined by PWM0 timer and Dead-zone generator 0. Similarly, the complementary PWM pairs of (PWM2, PWM3), (PWM4, PWM5) and (PWM6, PWM7) are controlled by PWM2, PWM4 and PWM6 timers and Dead-zone generator 2, 4 and 6, respectively.

To prevent PWM driving output pin with unsteady waveform, the 16-bit period down counter and 16-bit comparator are implemented with double buffer. When user writes data to counter/comparator buffer registers the updated value will be load into the 16-bit down counter/ comparator at the time down counter reaching zero. The double buffering feature avoids glitch at PWM outputs.

When the 16-bit period down counter reaches zero, the interrupt request is generated. If PWMtimer is set as auto-reload mode, when the down counter reaches zero, it is reloaded with PWM Counter Register (CNRx) automatically then start decreasing, repeatedly. If the PWM-timer is set as one-shot mode, the down counter will stop and generate one interrupt request when it reaches zero.

The value of PWM counter comparator is used for pulse high width modulation. The counter control logic changes the output to high level when down-counter value matches the value of compare register.

The alternate feature of the PWM-timer is digital input Capture function. If Capture function is enabled the PWM output pin is switched as capture input mode. The Capture0 and PWM0 share one timer which is included in PWM0 and the Capture1 and PWM1 share PWM1 timer, and etc. Therefore user must setup the PWM-timer before enable Capture feature. After capture feature is enabled, the capture always latched PWM-counter to Capture Rising Latch Register (CRLR) when input channel has a rising transition and latched PWM-counter to Capture Falling Latch Register (CFLR) when input channel has a falling transition. Capture channel 0 interrupt is programmable by setting CCR0.CRL\_IE0[1] (Rising latch Interrupt enable) and CCR0.CFL\_IE0[2]] (Falling latch Interrupt enable) to decide the condition of interrupt occur. Capture channel 1 has the same feature by setting CCR0.CRL\_IE1[17] and CCR0.CFL\_IE1[18]. And capture channel 2 to channel 3 on each group have the same feature by setting the corresponding control bits in CCR2. For each group, whenever Capture issues Interrupt 0/1/2/3,

### 5.7 Real Time Clock (RTC)

#### 5.7.1 Overview

Real Time Clock (RTC) controller provides user the real time and calendar message. The clock source of RTC is from an external 32.768 kHz low speed crystal connected at pins X321 and X32O (reference to pin descriptions) or from an external 32.768 kHz low speed oscillator output fed at pin X321. The RTC controller provides the time message (second, minute, hour) in Time Loading Register (TLR) as well as calendar message (day, month, year) in Calendar Loading Register (CLR). The data message is expressed in BCD format. It also offers alarm function that user can preset the alarm time in Time Alarm Register (TAR) and alarm calendar in Calendar Alarm Register (CAR).

The RTC controller supports periodic Time Tick and Alarm Match interrupts. The periodic interrupt has 8 period options 1/128, 1/64, 1/32, 1/16, 1/8, 1/4, 1/2 and 1 second which are selected by TTR (TTR[2:0]). When RTC counter in TLR and CLR is equal to alarm setting time registers TAR and CAR, the alarm interrupt flag (RIIR.AIF) is set and the alarm interrupt is requested if the alarm interrupt is enabled (RIER.AIER=1). Both RTC Time Tick and Alarm Match can cause chip wake-up from power down mode if wake-up function is enabled (TWKE (TTR[3])=1).

#### 5.7.2 Features

- There is a time counter (second, minute, hour) and calendar counter (day, month, year) for user to check the time

- Alarm register (second, minute, hour, day, month, year)

- 12-hour or 24-hour mode is selectable

- Leap year compensation automatically

- Day of week counter

- Frequency compensate register (FCR)

- All time and calendar message is expressed in BCD code

- Support periodic time tick interrupt with 8 period options 1/128, 1/64, 1/32, 1/16, 1/8, 1/4, 1/2 and 1 second

- Support RTC Time Tick and Alarm Match interrupt

- Support wake-up chip from power down mode

### 5.9 Timer Controller (TMR)

#### 5.9.1 Overview

The timer controller includes four 32-bit timers, TIMER0~TIMER3, which allows user to easily implement a timer control for applications. The timer can perform functions like frequency measurement, event counting, interval measurement, clock generation, delay timing, and so on. The timer can generates an interrupt signal upon timeout, or provide the current value during operation. Note: toggle mode, continuous counting mode and event counting function only support in NuMicro™ NUC100/NUC120 Low Density.

#### 5.9.2 Features

- 4 sets of 32-bit timers with 24-bit up-timer and one 8-bit pre-scale counter

- Independent clock source for each timer

- Provides one-shot, periodic, toggle and continuous counting operation modes (NuMicro™ NUC100/NUC120 Medium Density only support one-shot and periodic mode)

- Time out period = (Period of timer clock input) \* (8-bit pre-scale counter + 1) \* (24-bit TCMP)

- Maximum counting cycle time = (1 / T MHz) \* (2<sup>8</sup>) \* (2<sup>24</sup>), T is the period of timer clock

- 24-bit timer value is readable through TDR (Timer Data Register)

- Support event counting function to count the event from external pin (NuMicro™ NUC100/NUC120 Low Density only)

## 5.13 I<sup>2</sup>S Controller (I<sup>2</sup>S)

#### 5.13.1 Overview

The I<sup>2</sup>S controller consists of IIS protocol to interface with external audio CODEC. Two 8 word deep FIFO for read path and write path respectively and is capable of handling 8  $\sim$  32 bit word sizes. DMA controller handles the data movement between FIFO and memory.

#### 5.13.2 Features

- I<sup>2</sup>S can operate as either master or slave

- Capable of handling 8-, 16-, 24- and 32-bit word sizes

- Mono and stereo audio data supported

- I<sup>2</sup>S and MSB justified data format supported

- Two 8 word FIFO data buffers are provided, one for transmit and one for receive

- Generates interrupt requests when buffer levels cross a programmable boundary

- Two DMA requests, one for transmit and one for receive

### 5.15 Analog Comparator (CMP)

#### 5.15.1 Overview

NuMicro<sup>™</sup> NUC100 Series contains two comparators. The comparators can be used in a number of different configurations. The comparator output is a logical one when positive input greater than negative input, otherwise the output is a zero. Each comparator can be configured to cause an interrupt when the comparator output value changes. The block diagram is shown in **Error! Reference source not found.**

#### 5.15.2 Features

- Analog input voltage range: 0~5.0 V

- Hysteresis function supported

- Two analog comparators with optional internal reference voltage input at negative end

- One interrupt vector for both comparators

### 5.16 PDMA Controller (PDMA)

#### 5.16.1 Overview

NuMicro<sup>™</sup> NUC100/NUC120 Medium Density contains a peripheral direct memory access (PDMA) controller that transfers data to and from memory or transfer data to and from APB devices. The PDMA has nine channels of DMA (Peripheral-to-Memory or Memory-to-Peripheral or Memory-to-Memory). For each PDMA channel (PDMA CH0~CH8), there is one word buffer as transfer buffer between the Peripherals APB devices and Memory.

Software can stop the PDMA operation by disable PDMA [PDMACEN]. The CPU can recognize the completion of a PDMA operation by software polling or when it receives an internal PDMA interrupt. The PDMA controller can increase source or destination address or fixed them as well.

Notice: NuMicro™ NUC100/NUC120 Low Density only has 1 PDMA channel (channel 0).

#### 5.16.2 Features

- Up to nine DMA channels. Each channel can support a unidirectional transfer (NuMicro™ NUC100/NUC120 Low Density only has 1 PDMA channel)

- AMBA AHB master/slave interface compatible, for data transfer and register read/write

- Support source and destination address increased mode or fixed mode

- Hardware channel priority. DMA channel 0 has the highest priority and channel 8 has the lowest priority

### 5.17 External Bus Interface (EBI)

#### 5.17.1 Overview

The NuMicro™ NUC100/NUC120 Low Density LQFP-64 package equips an external bus interface (EBI) for external device used.

To save the connections between external device and this chip, EBI support address bus and data bus multiplex mode. And, address latch enable (ALE) signal supported differentiate the address and data cycle.

#### 5.17.2 Features

External Bus Interface has the following functions:

- External devices with max. 64K-byte size (8-bit data width)/128K-byte (16-bit data width) supported

- Variable external bus base clock (MCLK) supported

- 8-bit or 16-bit data width supported

- Variable data access time (tACC), address latch enable time (tALE) and address hold time (tAHD) supported

- Address bus and data bus multiplex mode supported to save the address pins

- Configurable idle cycle supported for different access condition: Write command finish (W2X), Read-to-Read (R2R)

## 6 FLASH MEMORY CONTROLLER (FMC)

#### 6.1 Overview

NuMicro<sup>™</sup> NUC100 Series equips with 128/64/32K bytes on chip embedded Flash for application program memory (APROM) that can be updated through ISP procedure. In System Programming (ISP) function enables user to update program memory when chip is soldered on PCB. After chip power on, Cortex-M0 CPU fetches code from APROM or LDROM decided by boot select (CBS) in Config0. By the way, NuMicro<sup>™</sup> NUC100 Series also provides additional DATA Flash for user, to store some application dependent data before chip power off. For 128K bytes APROM device, the data flash is shared with original 128K program memory and its start address is configurable and defined by user application request in Config1. For 64K/32K bytes APROM device, the data flash is fixed at 4K.

#### 6.2 Features

- Run up to 50 MHz with zero wait state for continuous address read access

- 128/64/32KB application program memory (APROM) (NuMicro<sup>™</sup> NUC100/NUC120 Low Density only support up to 64KB size)

- 4KB in system programming (ISP) loader program memory (LDROM)

- Configurable or fixed 4KB data flash with 512 bytes page erase unit

- Programmable data flash start address for 128K APROM device

- In System Program (ISP) to update on chip Flash

| PARAMETER                                  | SYM.               | SPECIFICATION |      |      |      | TEST CONDITIONS                                                                  |

|--------------------------------------------|--------------------|---------------|------|------|------|----------------------------------------------------------------------------------|

| FARAMETER                                  |                    | MIN.          | TYP. | MAX. | UNIT | TEST CONDITIONS                                                                  |

|                                            | I <sub>DD8</sub>   |               | 11.5 |      | mA   | $V_{DD}$ = 3 V@12 MHz,<br>disable all IP and disable PLL,<br>XTAL=12 MHz         |

|                                            | I <sub>DD9</sub>   |               | 13.5 |      | mA   | V <sub>DD</sub> = 5 V@4 MHz,<br>enable all IP and disable PLL,<br>XTAL=4 MHz     |

| Operating Current<br>Normal Run Mode       | I <sub>DD10</sub>  |               | 10   |      | mA   | V <sub>DD</sub> = 5 V@4 MHz,<br>disable all IP and disable PLL,<br>XTAL=4 MHz    |

| @ 4 MHz                                    | I <sub>DD11</sub>  |               | 12   |      | mA   | V <sub>DD</sub> = 3 V@4 MHz,<br>enable all IP and disable PLL,<br>XTAL=4 MHz     |

|                                            | I <sub>DD12</sub>  |               | 8    |      | mA   | V <sub>DD</sub> = 3 V@4 MHz,<br>disable all IP and disable PLL,<br>XTAL=4 MHz    |

|                                            | I <sub>IDLE1</sub> |               | 30   |      | mA   | V <sub>DD</sub> = 5.5 V@50 MHz,<br>enable all IP and PLL, XTAL=12<br>MHz         |

| Operating Current<br>Idle Mode             | I <sub>IDLE2</sub> |               | 13   |      | mA   | VDD=5.5 V@50 MHz,<br>disable all IP and enable PLL,<br>XTAL=12 MHz               |

| @ 50 MHz                                   | I <sub>IDLE3</sub> |               | 28   |      | mA   | V <sub>DD</sub> = 3 V@50 MHz,<br>enable all IP and PLL, XTAL=12<br>MHz           |

|                                            | I <sub>IDLE4</sub> |               | 12   |      |      | V <sub>DD</sub> = 3 V@50 MHz,<br>disable all IP and enable PLL,<br>XTAL=12 MHz   |

| Operating Current<br>Idle Mode<br>@ 12 MHz | I <sub>IDLE5</sub> |               | 11   |      | mA   | V <sub>DD</sub> = 5.5 V@12 MHz,<br>enable all IP and disable PLL,<br>XTAL=12 MHz |

|                                            | I <sub>IDLE6</sub> |               | 5    |      | mA   | $V_{DD}$ = 5.5 V@12 MHz,<br>disable all IP and disable PLL,<br>XTAL=12 MHz       |

|                                            | I <sub>IDLE7</sub> |               | 10   |      | mA   | $V_{DD}$ = 3 V@12 MHz,<br>enable all IP and disable PLL,<br>XTAL=12 MHz          |

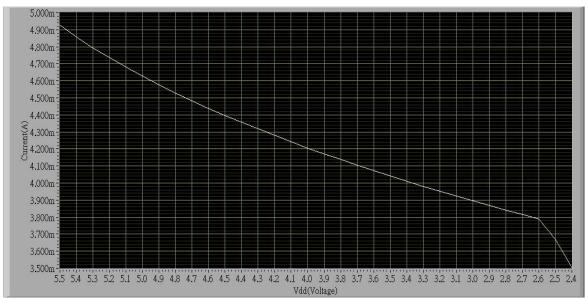

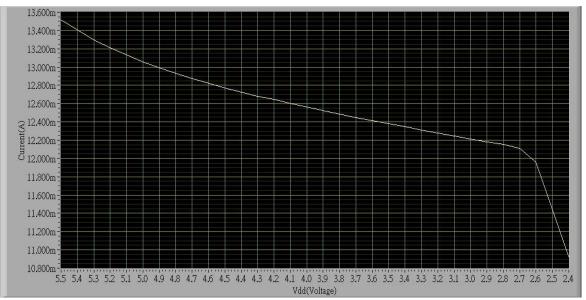

#### 7.2.4 Idle Current Curve

1. XTAL clock = 12 MHz, PLL disable, all-IP disable

Unit: mA

2. XTAL clock = 12 MHz, PLL disable, all-IP enable

Unit: mA

#### **Important Notice**

Nuvoton Products are neither intended nor warranted for usage in systems or equipment, any malfunction or failure of which may cause loss of human life, bodily injury or severe property damage. Such applications are deemed, "Insecure Usage".

Insecure usage includes, but is not limited to: equipment for surgical implementation, atomic energy control instruments, airplane or spaceship instruments, the control or operation of dynamic, brake or safety systems designed for vehicular use, traffic signal instruments, all types of safety devices, and other applications intended to support or sustain life.

All Insecure Usage shall be made at customer's risk, and in the event that third parties lay claims to Nuvoton as a result of customer's Insecure Usage, customer shall indemnify the damages and liabilities thus incurred by Nuvoton.

Please note that all data and specifications are subject to change without notice. All the trademarks of products and companies mentioned in this datasheet belong to their respective owners.