#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Active                                                                    |

|---------------------------------|---------------------------------------------------------------------------|

| Core Processor                  | ARM1136JF-S                                                               |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                            |

| Speed                           | 400MHz                                                                    |

| Co-Processors/DSP               | Multimedia; GPU, IPU, MPEG-4, VFP                                         |

| RAM Controllers                 | DDR                                                                       |

| Graphics Acceleration           | Yes                                                                       |

| Display & Interface Controllers | Keyboard, Keypad, LCD                                                     |

| Ethernet                        |                                                                           |

| SATA                            | -                                                                         |

| USB                             | USB 2.0 (3)                                                               |

| Voltage - I/O                   | 1.8V, 2.0V, 2.5V, 2.7V, 3.0V                                              |

| Operating Temperature           | -40°C ~ 85°C (TA)                                                         |

| Security Features               | Random Number Generator, RTIC, Secure Fusebox, Secure JTAG, Secure Memory |

| Package / Case                  | 473-LFBGA                                                                 |

| Supplier Device Package         | 473-MAPBGA (19x19)                                                        |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mcimx31cjmn4cr2              |

|                                 |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **3** Signal Descriptions

Signal descriptions are in the reference manual. Special signal considerations are listed following this paragraph. The BGA ball assignment is in Section 5, "Package Information and Pinout," on page 99.

Special Signal Considerations:

## • Tamper detect (GPIO1\_6)

Tamper detect logic is used to issue a security violation. This logic is activated if the tamper detect input is asserted.

The tamper detect logic is disabled after reset. After enabling the logic, it is impossible to disable it until the next reset. The GPR[16] bit functions as the tamper detect enable bit.

GPIO1\_6 functions similarly to other I/O with GPIO capabilities regardless of the status of the tamper detect enable bit. (For example, the GPIO1\_6 can function as an input with GPIO capabilities, such as sampling through PSR or generating interrupts.)

## • Power ready (GPIO1\_5)

The power ready input, GPIO1\_5, should be connected to an external power management IC power ready output signal. If not used, GPIO1\_5 must either be (a) externally pulled-up to NVCC1 or (b) a no connect, internally pulled-up by enabling the on-chip pull-up resistor. GPIO1\_5 is a dedicated input and cannot be used as a general-purpose input/output.

## • SJC\_MOD

SJC\_MOD must be externally connected to GND for normal operation. Termination to GND through an external pull-down resistor (such as 1 k $\Omega$ ) is allowed, but the value should be much smaller than the on-chip 100 k $\Omega$  pull-up.

## • CE\_CONTROL

CE\_CONTROL is a reserved input and must be externally tied to GND through a 1 k $\Omega$  resistor.

## • M\_REQUEST and M\_GRANT

These two signals are not utilized internally. The user should make no connection to these signals.

## • Clock Source Select (CLKSS)

The CLKSS is the input that selects the default reference clock source providing input to the DPLL. To select CKIH, tie CLKSS to NVCC1. To select CKIL, tie CLKSS to ground. After initialization, the reference clock source can be changed (initial setting is overwritten) by programming the PRCS bits in the CCMR.

# 4 Electrical Characteristics

This section provides the device-level and module-level electrical characteristics for the MCIMX31C.

## 4.1 Chip-Level Conditions

This section provides the device-level electrical characteristics for the IC. See Table 4 for a quick reference to the individual tables and sections.

- <sup>1</sup> In read mode, FUSE\_VDD should be floated or grounded.

- <sup>2</sup> Fuses might be inadvertently blown if written to while the voltage is below the minimum.

Table 9 provides information for interface frequency limits. For more details about clocks characteristics, see Section 4.3.8, "DPLL Electrical Specifications" on page 31 and Section 4.3.3, "Clock Amplifier Module (CAMP) Electrical Characteristics" on page 19.

| ID | Parameter                   | Symbol            | Min | Тур    | Max  | Units |

|----|-----------------------------|-------------------|-----|--------|------|-------|

| 1  | JTAG TCK Frequency          | f <sub>JTAG</sub> | DC  | 5      | 10   | MHz   |

| 2  | CKIL Frequency <sup>1</sup> | f <sub>CKIL</sub> | 32  | 32.768 | 38.4 | kHz   |

| 3  | CKIH Frequency <sup>2</sup> | f <sub>CKIH</sub> | 15  | 26     | 75   | MHz   |

#### Table 9. Interface Frequency

<sup>1</sup> CKIL must be driven by an external clock source to ensure proper start-up and operation of the device. CKIL is needed to clock the internal reset synchronizer, the watchdog, and the real-time clock.

<sup>2</sup> DPTC functionality, specifically the voltage/frequency relation table, is dependent on CKIH frequency. At the time of publication, standard tables used by Freescale OSs provided for a CKIH frequency of 26 MHz only. Any deviation from this frequency requires an update to the OS. For more details, refer to the particular OS user's guide documentation. DPTC/DVFS are not supported for fARM ≤ 400MHz.

#### Table 10 shows the fusebox supply current parameters.

#### **Table 10. Fusebox Supply Current Parameters**

| Ref. Num | Description                                                                               | Symbol   | Minimum | Typical | Maximum | Units |

|----------|-------------------------------------------------------------------------------------------|----------|---------|---------|---------|-------|

|          | eFuse Program Current. <sup>1</sup><br>Current to program one eFuse bit: efuse_pgm = 3.0V | Iprogram | —       | 35      | 60      | mA    |

|          | $Current to program one er use bit. eluse_pgin = 3.0V$                                    |          |         |         |         |       |

<sup>1</sup> The current I<sub>program</sub> is during program time (t<sub>program</sub>).

#### Notes:

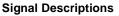

- <sup>1</sup> The board design must guarantee that supplies reach 90% level before transition to the next state, using Power Management IC or other means.

- <sup>2</sup> The NVCC1 supply must not precede IOQVDD by more than 0.2 V until IOQVDD has reached 1.5 V. If IOQVDD is powered up first, there are no restrictions.

- <sup>3</sup> Raising NVCC2, NVCC21, and NVCC22 at the same time as IOQVDD does not produce the slight increase in current drain on IOQVDD (as described in Figure 2, Note 5).

- <sup>4</sup> FUSE\_VDD should not be driven on power-up for Silicon Revision2.0 and 2.0.1. This supply is dedicated for fuse burning (programming), and should not be driven upon boot-up.

Figure 3. Option 2 Power-Up Sequence (Silicon Revision 2.0 and 2.0.1)

## 4.2.2 **Powering Down**

The power-down sequence should be completed as follows:

- 1. Lower the FUSE\_VDD supply (when in write mode).

- 2. Lower the remaining supplies.

## 4.3 Module-Level Electrical Specifications

This section contains the MCIMX31C electrical information including timing specifications, arranged in alphabetical order by module name.

## 4.3.1 I/O Pad (PADIO) Electrical Specifications

This section specifies the AC/DC characterization of functional I/O of the MCIMX31C. There are two main types of I/O: regular and DDR. In this document, the "Regular" type is referred to as GPIO.

## 4.3.1.1 DC Electrical Characteristics

The MCIMX31C I/O parameters appear in Table 12 for GPIO. See Table 7, "Operating Ranges," on page 12 for temperature and supply voltage ranges.

| Parameter                   | Min                       | Тур | Мах | Units |

|-----------------------------|---------------------------|-----|-----|-------|

| Input Frequency             | 15                        | _   | 75  | MHz   |

| VIL (for square wave input) | 0                         | _   | 0.3 | V     |

| VIH (for square wave input) | (VDD <sup>1</sup> - 0.25) | _   | 3   | V     |

| Sinusoidal Input Amplitude  | 0.4 <sup>2</sup>          | _   | VDD | Vp-p  |

| Duty Cycle                  | 45                        | 50  | 55  | %     |

Table 17. Clock Amplifier Electrical Characteristics for CKIH Input

<sup>1</sup> VDD is the supply voltage of CAMP. See reference manual.

<sup>2</sup> This value of the sinusoidal input will be measured through characterization.

## 4.3.4 1-Wire Electrical Specifications

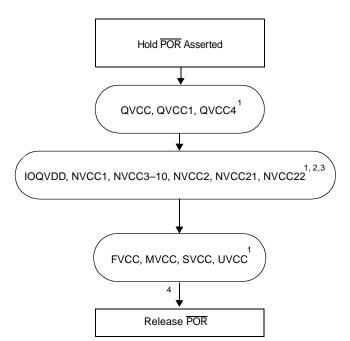

Figure 6 depicts the RPP timing, and Table 18 lists the RPP timing parameters.

Figure 6. Reset and Presence Pulses (RPP) Timing Diagram

| ID  | Parameters           | Symbol            | Min | Тур | Max | Units |

|-----|----------------------|-------------------|-----|-----|-----|-------|

| OW1 | Reset Time Low       | t <sub>RSTL</sub> | 480 | 511 | _   | μs    |

| OW2 | Presence Detect High | t <sub>PDH</sub>  | 15  | _   | 60  | μs    |

| OW3 | Presence Detect Low  | t <sub>PDL</sub>  | 60  | _   | 240 | μs    |

| OW4 | Reset Time High      | t <sub>RSTH</sub> | 480 | 512 |     | μs    |

Table 18. RPP Sequence Delay Comparisons Timing Parameters

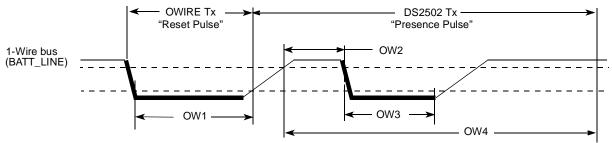

Figure 7 depicts Write 0 Sequence timing, and Table 19 lists the timing parameters.

## 4.3.6 AUDMUX Electrical Specifications

The AUDMUX provides a programmable interconnect logic for voice, audio and data routing between internal serial interfaces (SSI) and external serial interfaces (audio and voice codecs). The AC timing of AUDMUX external pins is hence governed by the SSI module. Please refer to their respective electrical specifications.

## 4.3.7 CSPI Electrical Specifications

This section describes the electrical information of the CSPI.

## 4.3.7.1 CSPI Timing

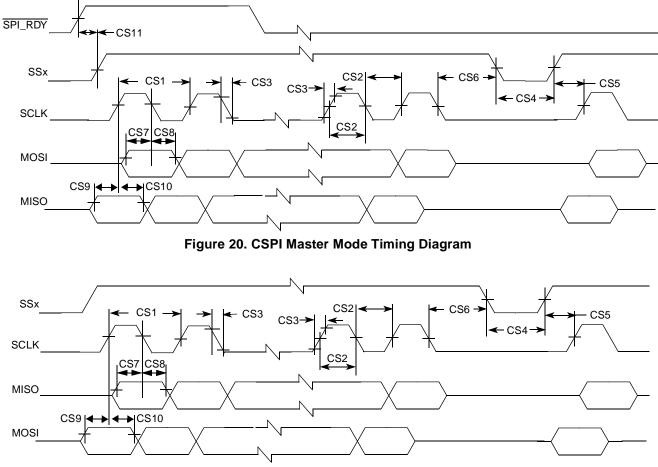

Figure 20 and Figure 21 depict the master mode and slave mode timings of CSPI, and Table 27 lists the timing parameters.

Figure 21. CSPI Slave Mode Timing Diagram

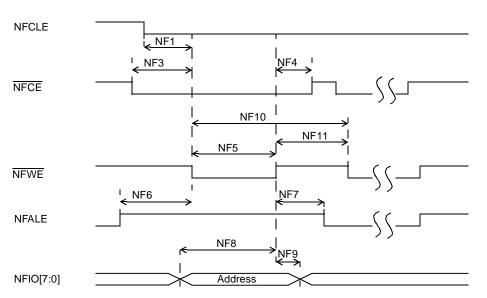

Figure 24. Write Data Latch Cycle Timing Dlagram

| ID               | Parameter                | Min                 | Max | Unit |

|------------------|--------------------------|---------------------|-----|------|

| T <sub>cyc</sub> | Clock period             | Frequency dependent |     | ns   |

| T <sub>wl</sub>  | Low pulse width          | 2                   | _   | ns   |

| T <sub>wh</sub>  | High pulse width         | 2                   | _   | ns   |

| Tr               | Clock and data rise time | _                   | 3   | ns   |

| Τ <sub>f</sub>   | Clock and data fall time | _                   | 3   | ns   |

#### Table 37. ETM TRACECLK Timing Parameters

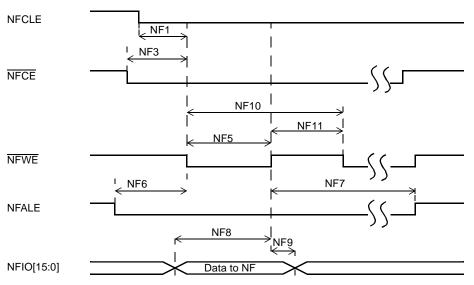

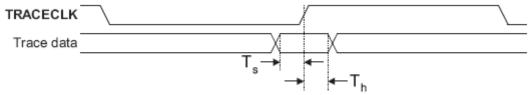

Figure 40 depicts the setup and hold requirements of the trace data pins with respect to TRACECLK, and Table 38 lists the timing parameters.

Figure 40. Trace Data Timing Diagram

Table 38. ETM Trace Data Timing Parameters

| ID             | Parameter  | Min | Max | Unit |

|----------------|------------|-----|-----|------|

| Τ <sub>s</sub> | Data setup | 2   | _   | ns   |

| T <sub>h</sub> | Data hold  | 1   |     | ns   |

### 4.3.10.1 Half-Rate Clocking Mode

When half-rate clocking is used, the trace data signals are sampled by the TPA on both the rising and falling edges of TRACECLK, where TRACECLK is half the frequency of the clock shown in Figure 40.

## 4.3.11 FIR Electrical Specifications

FIR implements asynchronous infrared protocols (FIR, MIR) that are defined by IrDA<sup>®</sup> (Infrared Data Association). Refer to http://www.IrDA.org for details on FIR and MIR protocols.

## 4.3.12 Fusebox Electrical Specifications

| Ref. Num | Description                         | Symbol               | Minimum | Typical | Maximum | Units |

|----------|-------------------------------------|----------------------|---------|---------|---------|-------|

| 1        | Program time for eFuse <sup>1</sup> | t <sub>program</sub> | 125     | _       | —       | μs    |

### **Table 39. Fusebox Timing Characteristics**

<sup>1</sup> The program length is defined by the value defined in the epm\_pgm\_length[2:0] bits of the IIM module. The value to program is based on a 32 kHz clock source (4 \* 1/32 kHz = 125 μs)

## 4.3.14 IPU—Sensor Interfaces

## 4.3.14.1 Supported Camera Sensors

Table 41 lists the known supported camera sensors at the time of publication.

| Vendor                 | Model                                                                                                                         |  |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------|--|

| Conexant               | CX11646, CX20490 <sup>2</sup> , CX20450 <sup>2</sup>                                                                          |  |

| Agilant                | HDCP-2010, ADCS-1021 <sup>2</sup> , ADCS-1021 <sup>2</sup>                                                                    |  |

| Toshiba                | TC90A70                                                                                                                       |  |

| ICMedia                | ICM202A, ICM102 <sup>2</sup>                                                                                                  |  |

| iMagic                 | IM8801                                                                                                                        |  |

| Transchip              | TC5600, TC5600J, TC5640, TC5700, TC6000                                                                                       |  |

| Fujitsu                | MB86S02A                                                                                                                      |  |

| Micron                 | MI-SOC-0133                                                                                                                   |  |

| Matsushita             | MN39980                                                                                                                       |  |

| STMicro                | W6411, W6500, W6501 <sup>2</sup> , W6600 <sup>2</sup> , W6552 <sup>2</sup> , STV0974 <sup>2</sup>                             |  |

| OmniVision             | OV7620, OV6630                                                                                                                |  |

| Sharp                  | LZ0P3714 (CCD)                                                                                                                |  |

| Motorola               | MC30300 (Python) <sup>2</sup> , SCM20014 <sup>2</sup> , SCM20114 <sup>2</sup> , SCM22114 <sup>2</sup> , SCM20027 <sup>2</sup> |  |

| National Semiconductor | LM9618 <sup>2</sup>                                                                                                           |  |

| Table 41. | Supported             | Camera   | Sensors <sup>1</sup> |

|-----------|-----------------------|----------|----------------------|

| 14010 111 | • • • • • • • • • • • | • aniona |                      |

<sup>1</sup> Freescale Semiconductor does not recommend one supplier over another and in no way suggests that these are the only camera suppliers.

<sup>2</sup> These sensors not validated at time of publication.

## 4.3.14.2 Functional Description

There are three timing modes supported by the IPU.

## 4.3.14.2.1 Pseudo BT.656 Video Mode

Smart camera sensors, which include imaging processing, usually support video mode transfer. They use an embedded timing syntax to replace the SENSB\_VSYNC and SENSB\_HSYNC signals. The timing syntax is defined by the BT.656 standard.

This operation mode follows the recommendations of ITU BT.656 specifications. The only control signal used is SENSB\_PIX\_CLK. Start-of-frame and active-line signals are embedded in the data stream. An active line starts with a SAV code and ends with a EAV code. In some cases, digital blanking is inserted in between EAV and SAV code. The CSI decodes and filters out the timing-coding from the data stream, thus recovering SENSB\_VSYNC and SENSB\_HSYNC signals for internal use.

| Туре                          | Vendor                                                      | Model                                                                                                                                                                                                                |

|-------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TFT displays<br>(memory-less) | Sharp (HR-TFT Super<br>Mobile LCD family)                   | LQ035Q7 DB02, LM019LC1Sxx                                                                                                                                                                                            |

|                               | Samsung (QCIF and<br>QVGA TFT modules for<br>mobile phones) | LTS180S1-HF1, LTS180S3-HF1, LTS350Q1-PE1,<br>LTS350Q1-PD1, LTS220Q1-HE1 <sup>2</sup>                                                                                                                                 |

|                               | Toshiba (LTM series)                                        | LTM022P806 <sup>2</sup> , LTM04C380K <sup>2</sup> ,<br>LTM018A02A <sup>2</sup> , LTM020P332 <sup>2</sup> , LTM021P337 <sup>2</sup> , LTM019P334 <sup>2</sup> ,<br>LTM022A783 <sup>2</sup> , LTM022A05ZZ <sup>2</sup> |

|                               | NEC                                                         | NL6448BC20-08E, NL8060BC31-27                                                                                                                                                                                        |

| Display controllers           | Epson                                                       | S1D15xxx series, S1D19xxx series, S1D13713, S1D13715                                                                                                                                                                 |

|                               | Solomon Systech                                             | SSD1301 (OLED), SSD1828 (LDCD)                                                                                                                                                                                       |

|                               | Hitachi                                                     | HD66766, HD66772                                                                                                                                                                                                     |

|                               | ATI                                                         | W2300                                                                                                                                                                                                                |

| Smart display modules         | Epson                                                       | L1F10043 T <sup>2</sup> , L1F10044 T <sup>2</sup> , L1F10045 T <sup>2</sup> , L2D22002 <sup>2</sup> , L2D20014 <sup>2</sup> , L2F50032 <sup>2</sup> , L2D25001 T <sup>2</sup>                                        |

|                               | Hitachi                                                     | 120 160 65K/4096 C-STN (#3284 LTD-1398-2) based on HD 66766 controller                                                                                                                                               |

|                               | Densitron Europe LTD                                        | All displays with MPU 80/68K series interface and serial peripheral interface                                                                                                                                        |

|                               | Sharp                                                       | LM019LC1Sxx                                                                                                                                                                                                          |

|                               | Sony                                                        | ACX506AKM                                                                                                                                                                                                            |

| Digital video encoders        | Analog Devices                                              | ADV7174/7179                                                                                                                                                                                                         |

| (for TV)                      | Crystal (Cirrus Logic)                                      | CS49xx series                                                                                                                                                                                                        |

|                               | Focus                                                       | FS453/4                                                                                                                                                                                                              |

<sup>1</sup> Freescale Semiconductor does not recommend one supplier over another and in no way suggests that these are the only display component suppliers.

<sup>2</sup> These display components not validated at time of publication.

## 4.3.15.2 Synchronous Interfaces

### 4.3.15.2.1 Interface to Active Matrix TFT LCD Panels, Functional Description

Figure 45 depicts the LCD interface timing for a generic active matrix color TFT panel. In this figure signals are shown with negative polarity. The sequence of events for active matrix interface timing is:

- DISPB\_D3\_CLK latches data into the panel on its negative edge (when positive polarity is selected). In active mode, DISPB\_D3\_CLK runs continuously.

- DISPB\_D3\_HSYNC causes the panel to start a new line.

- DISPB\_D3\_VSYNC causes the panel to start a new frame. It always encompasses at least one HSYNC pulse.

### MCIMX31C/MCIMX31LC Technical Data, Rev. 4.3

<sup>3</sup> Display interface clock up time

$Tdicu = \frac{1}{2}T_{HSP\_CLK} \cdot ceil \left[\frac{2 \cdot DISP3\_IF\_CLK\_UP\_WR}{HSP\_CLK\_PERIOD}\right]$

where CEIL(X) rounds the elements of X to the nearest integers towards infinity.

## 4.3.15.3 Interface to Sharp HR-TFT Panels

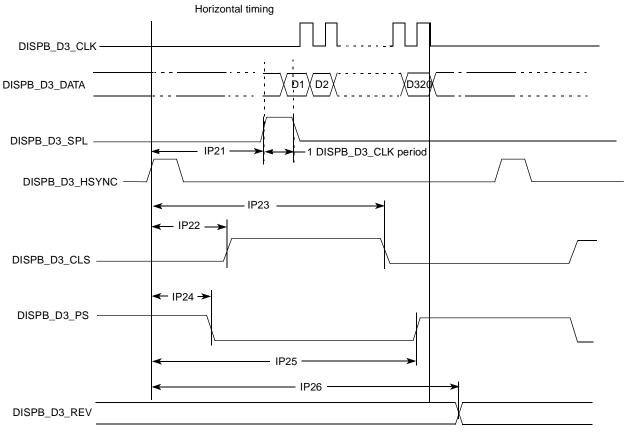

Figure 49 depicts the Sharp HR-TFT panel interface timing, and Table 46 lists the timing parameters. The CLS\_RISE\_DELAY, CLS\_FALL\_DELAY, PS\_FALL\_DELAY, PS\_RISE\_DELAY, REV\_TOGGLE\_DELAY parameters are defined in the SDC\_SHARP\_CONF\_1 and SDC\_SHARP\_CONF\_2 registers. For other Sharp interface timing characteristics, refer to Section 4.3.15.2.2, "Interface to Active Matrix TFT LCD Panels, Electrical Characteristics," on page 55. The timing images correspond to straight polarity of the Sharp signals.

Example is drawn with FW+1=320 pixel/line, FH+1=240 lines. SPL pulse width is fixed and aligned to the first data of the line. REV toggles every HSYNC period.

MCIMX31C/MCIMX31LC Technical Data, Rev. 4.3

## 4.3.15.5.2 Parallel Interfaces, Electrical Characteristics

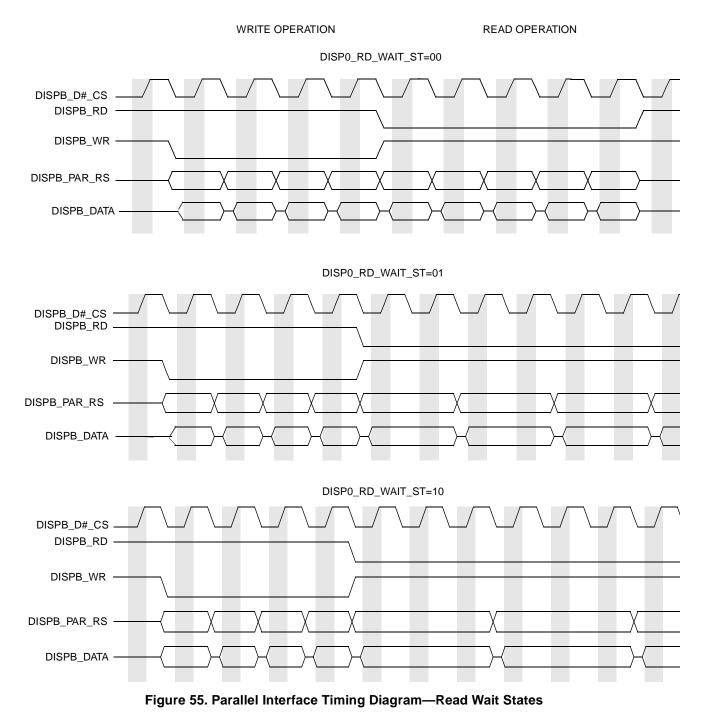

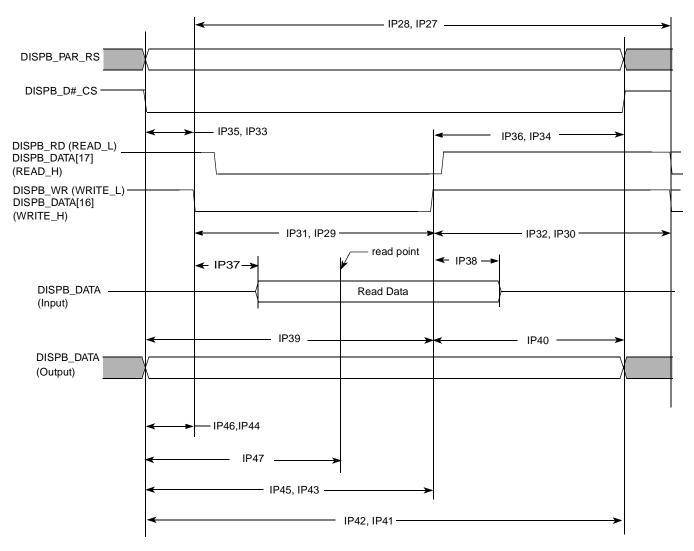

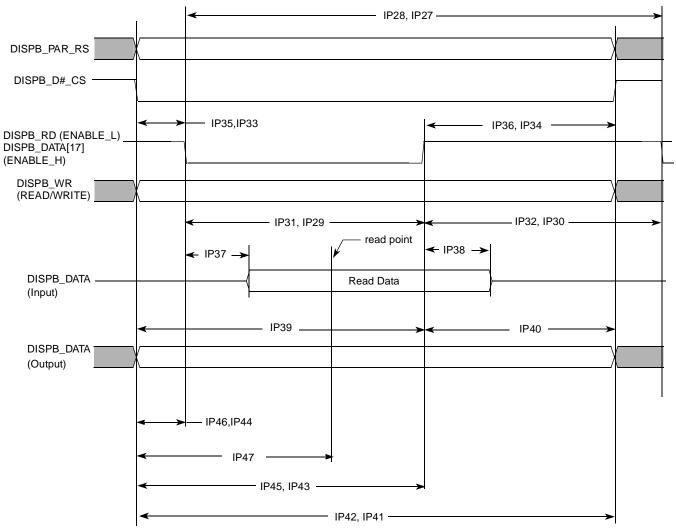

Figure 56, Figure 58, Figure 57, and Figure 59 depict timing of asynchronous parallel interfaces based on the system 80 and system 68k interfaces. Table 47 lists the timing parameters at display access level. All timing images are based on active low control signals (signals polarity is controlled via the DI\_DISP\_SIG\_POL Register).

Figure 57. Asynchronous Parallel System 80 Interface (Type 2) Timing Diagram

| Table 47. Asynchronous Parallel Interfac | e Timing Parameters—Access Level |

|------------------------------------------|----------------------------------|

|------------------------------------------|----------------------------------|

| ID   | Parameter                     | Symbol | Min.                         | Typ. <sup>1</sup>                        | Max.                         | Units |

|------|-------------------------------|--------|------------------------------|------------------------------------------|------------------------------|-------|

| IP27 | Read system cycle time        | Tcycr  | Tdicpr-1.5                   | Tdicpr <sup>2</sup>                      | Tdicpr+1.5                   | ns    |

| IP28 | Write system cycle time       | Tcycw  | Tdicpw-1.5                   | Tdicpw <sup>3</sup>                      | Tdicpw+1.5                   | ns    |

| IP29 | Read low pulse width          | Trl    | Tdicdr-Tdicur-1.5            | Tdicdr <sup>4</sup> –Tdicur <sup>5</sup> | Tdicdr-Tdicur+1.5            | ns    |

| IP30 | Read high pulse width         | Trh    | Tdicpr-Tdicdr+Tdicur-1.5     | Tdicpr–Tdicdr+<br>Tdicur                 | Tdicpr-Tdicdr+Tdicur+1.5     | ns    |

| IP31 | Write low pulse width         | Twl    | Tdicdw-Tdicuw-1.5            | Tdicdw <sup>6</sup> –Tdicuw <sup>7</sup> | Tdicdw-Tdicuw+1.5            | ns    |

| IP32 | Write high pulse width        | Twh    | Tdicpw–Tdicdw+<br>Tdicuw–1.5 | Tdicpw–Tdicdw+<br>Tdicuw                 | Tdicpw–Tdicdw+<br>Tdicuw+1.5 | ns    |

| IP33 | Controls setup time for read  | Tdcsr  | Tdicur-1.5                   | Tdicur                                   | —                            | ns    |

| IP34 | Controls hold time for read   | Tdchr  | Tdicpr-Tdicdr-1.5            | Tdicpr–Tdicdr                            | —                            | ns    |

| IP35 | Controls setup time for write | Tdcsw  | Tdicuw–1.5                   | Tdicuw                                   | —                            | ns    |

### MCIMX31C/MCIMX31LC Technical Data, Rev. 4.3

| ID   | Parameter                                | Symbol | Min.                 | Typ. <sup>1</sup> | Max.                                              | Units |

|------|------------------------------------------|--------|----------------------|-------------------|---------------------------------------------------|-------|

| IP36 | Controls hold time for write             | Tdchw  | Tdicpw-Tdicdw-1.5    | Tdicpw–Tdicdw     | —                                                 | ns    |

| IP37 | Slave device data delay <sup>8</sup>     | Tracc  | 0                    | —                 | Tdrp <sup>9</sup> –Tlbd <sup>10</sup> –Tdicur–1.5 | ns    |

| IP38 | Slave device data hold time <sup>8</sup> | Troh   | Tdrp-Tlbd-Tdicdr+1.5 | —                 | Tdicpr-Tdicdr-1.5                                 | ns    |

| IP39 | Write data setup time                    | Tds    | Tdicdw-1.5           | Tdicdw            | —                                                 | ns    |

| IP40 | Write data hold time                     | Tdh    | Tdicpw-Tdicdw-1.5    | Tdicpw–Tdicdw     | —                                                 | ns    |

| IP41 | Read period <sup>2</sup>                 | Tdicpr | Tdicpr-1.5           | Tdicpr            | Tdicpr+1.5                                        | ns    |

| IP42 | Write period <sup>3</sup>                | Tdicpw | Tdicpw-1.5           | Tdicpw            | Tdicpw+1.5                                        | ns    |

| IP43 | Read down time <sup>4</sup>              | Tdicdr | Tdicdr-1.5           | Tdicdr            | Tdicdr+1.5                                        | ns    |

| IP44 | Read up time <sup>5</sup>                | Tdicur | Tdicur-1.5           | Tdicur            | Tdicur+1.5                                        | ns    |

| IP45 | Write down time <sup>6</sup>             | Tdicdw | Tdicdw-1.5           | Tdicdw            | Tdicdw+1.5                                        | ns    |

| IP46 | Write up time <sup>7</sup>               | Tdicuw | Tdicuw-1.5           | Tdicuw            | Tdicuw+1.5                                        | ns    |

| IP47 | Read time point <sup>9</sup>             | Tdrp   | Tdrp–1.5             | Tdrp              | Tdrp+1.5                                          | ns    |

#### Table 47. Asynchronous Parallel Interface Timing Parameters—Access Level (continued)

<sup>1</sup>The exact conditions have not been finalized, but will likely match the current customer requirement for their specific display. These conditions may be device specific.

<sup>2</sup> Display interface clock period value for read:

Tdicpr = T<sub>HSP\_CLK</sub> ceil <u>DISP#\_IF\_CLK\_PER\_RD</u> HSP\_CLK\_PERIOD

$[dicpw = T_{HSP_CLK} \cdot ceil \left[ \frac{DISP\#_IF_CLK_PER_WR}{HSP_CLK_PERIOD} \right]$

4 Display interface clock down time for read: cail[2 · DISP#\_IF\_CLK\_DOWN\_RD]  $\Gamma$ dicdr =  $\frac{1}{T}$ T

$$= \frac{1}{2}$$

<sup>T</sup>HSP\_CLK · cell HSP\_CLK\_PERIOD

- Display interface clock up time for read:  $\Gamma dicur = \frac{1}{2}T_{HSP\_CLK} \cdot ceil \left[\frac{2 \cdot DISP\#\_IF\_CLK\_UP\_RD}{HSP\_CLK\_PERIOD}\right]$ 5

- <sup>6</sup> Display interface clock down time for write:  $Tdicdw = \frac{1}{2}T_{HSP_CLK} \cdot ceil \left[\frac{2 \cdot DISP\#_IF_CLK_DOWN_WR}{HSP_CLK_PERIOD}\right]$

- <sup>7</sup> Display interface clock up time for write:

$\label{eq:clcuw} \ensuremath{\texttt{I}}\xspace{-1pt} dicuw = \frac{1}{2}\ensuremath{\texttt{T}}\xspace{-1pt} HSP\_CLK \cdot ceil \left[ \frac{2 \cdot DISP\#\_IF\_CLK\_UP\_WR}{HSP\_CLK\_PERIOD} \right]$

<sup>8</sup> This parameter is a requirement to the display connected to the IPU

9 Data read point

$\Gamma drp = T_{HSP\_CLK} \cdot ceil \left[ \frac{DISP\#\_READ\_EN}{HSP\_CLK\_PERIOD} \right]$

<sup>10</sup> Loopback delay Tlbd is the cumulative propagation delay of read controls and read data. It includes an IPU output delay, a device-level output delay, board delays, a device-level input delay, an IPU input delay. This value is device specific.

<sup>&</sup>lt;sup>3</sup> Display interface clock period value for write:

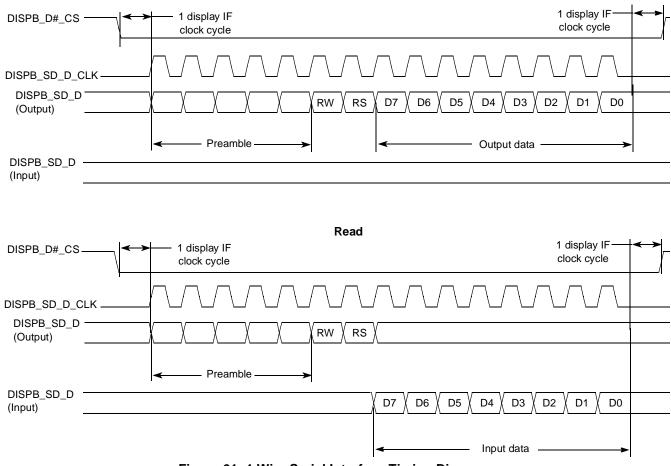

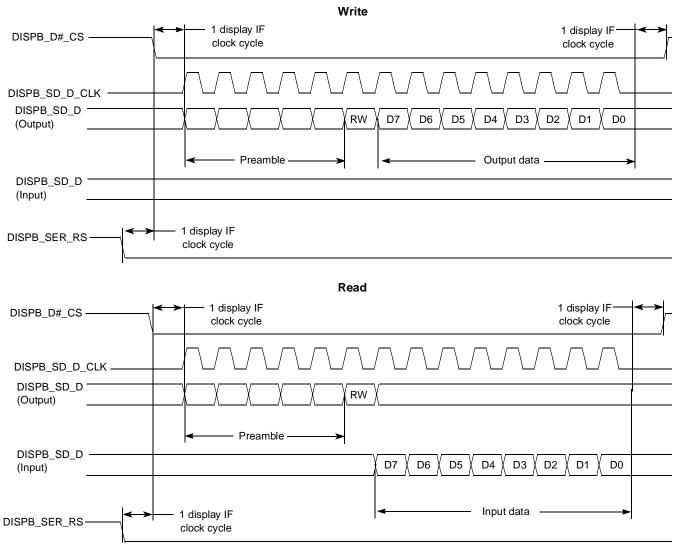

Figure 61. 4-Wire Serial Interface Timing Diagram

Figure 62 depicts timing of the 5-wire serial interface (Type 1). For this interface, a separate RS line is added. When a burst is transmitted within single active chip select interval, the RS can be changed at boundaries of words.

Figure 63 depicts timing of the 5-wire serial interface (Type 2). For this interface, a separate RS line is added. When a burst is transmitted within single active chip select interval, the RS can be changed at boundaries of words.

Figure 63. 5-Wire Serial Interface (Type 2) Timing Diagram

| ID   | Parameter                                | Symbol | Min.                 | Typ. <sup>1</sup> | Max.                                              | Units |

|------|------------------------------------------|--------|----------------------|-------------------|---------------------------------------------------|-------|

| IP56 | Controls setup time for write            | Tdcsw  | Tdicuw-1.5           | Tdicuw            | —                                                 | ns    |

| IP57 | Controls hold time for write             | Tdchw  | Tdicpw-Tdicdw-1.5    | Tdicpw–Tdicdw     | —                                                 | ns    |

| IP58 | Slave device data delay <sup>8</sup>     | Tracc  | 0                    | —                 | Tdrp <sup>9</sup> –Tlbd <sup>10</sup> –Tdicur–1.5 | ns    |

| IP59 | Slave device data hold time <sup>8</sup> | Troh   | Tdrp-Tlbd-Tdicdr+1.5 | —                 | Tdicpr-Tdicdr-1.5                                 | ns    |

| IP60 | Write data setup time                    | Tds    | Tdicdw-1.5           | Tdicdw            | —                                                 | ns    |

| IP61 | Write data hold time                     | Tdh    | Tdicpw-Tdicdw-1.5    | Tdicpw-Tdicdw     | —                                                 | ns    |

| IP62 | Read period <sup>2</sup>                 | Tdicpr | Tdicpr-1.5           | Tdicpr            | Tdicpr+1.5                                        | ns    |

| IP63 | Write period <sup>3</sup>                | Tdicpw | Tdicpw–1.5           | Tdicpw            | Tdicpw+1.5                                        | ns    |

| IP64 | Read down time <sup>4</sup>              | Tdicdr | Tdicdr-1.5           | Tdicdr            | Tdicdr+1.5                                        | ns    |

| IP65 | Read up time <sup>5</sup>                | Tdicur | Tdicur-1.5           | Tdicur            | Tdicur+1.5                                        | ns    |

| IP66 | Write down time <sup>6</sup>             | Tdicdw | Tdicdw-1.5           | Tdicdw            | Tdicdw+1.5                                        | ns    |

| IP67 | Write up time <sup>7</sup>               | Tdicuw | Tdicuw-1.5           | Tdicuw            | Tdicuw+1.5                                        | ns    |

| IP68 | Read time point <sup>9</sup>             | Tdrp   | Tdrp–1.5             | Tdrp              | Tdrp+1.5                                          | ns    |

#### Table 48. Asynchronous Serial Interface Timing Parameters—Access Level (continued)

<sup>1</sup> The exact conditions have not been finalized, but will likely match the current customer requirement for their specific display. These conditions may be device specific.

<sup>2</sup> Display interface clock period value for read:

$Tdicpr = T_{HSP\_CLK} \cdot ceil \left[ \frac{DISP\#\_IF\_CLK\_PER\_RD}{HSP\_CLK\_PERIOD} \right]$

<sup>3</sup> Display interface clock period value for write:

$Tdicpw = T_{HSP\_CLK} \cdot ceil \left[ \frac{DISP\#\_IF\_CLK\_PER\_WR}{HSP\_CLK\_PERIOD} \right]$

<sup>4</sup> Display interface clock down time for read:

$Tdicdr = \frac{1}{2}T_{HSP\_CLK} \cdot ceil \left[\frac{2 \cdot DISP\#\_IF\_CLK\_DOWN\_RD}{HSP\_CLK\_PERIOD}\right]$

<sup>5</sup> Display interface clock up time for read:

$Tdicur = \frac{1}{2}T_{HSP\_CLK} \cdot ceil \left[\frac{2 \cdot DISP\#\_IF\_CLK\_UP\_RD}{HSP\_CLK\_PERIOD}\right]$

<sup>6</sup> Display interface clock down time for write:

$$\label{eq:clcdw} \ensuremath{\mathsf{Fdicdw}} = \frac{1}{2} \ensuremath{\mathsf{T}}_{\ensuremath{\mathsf{HSP}}\xspace{\mathsf{CLK}}} \ensuremath{\mathsf{ceil}} \ensuremath{\mathsf{ERIOD}} \ensuremath{\mathsf{I}} \ensuremath{\mathsf{SPCLK}}\xspace{\mathsf{PERIOD}} \ensuremath{\mathsf{I}} \ensuremath{\mathsf{SPCLK}}\xspace{\mathsf{PERIOD}} \ensuremath{\mathsf{I}} \ensuremath{\mathsf{SPCLK}}\xspace{\mathsf{PERIOD}} \ensuremath{\mathsf{I}} \ensuremath{\mathsf{SPCLK}}\xspace{\mathsf{PERIOD}} \ensuremath{\mathsf{I}} \ensuremath{\mathsf{SPCLK}}\xspace{\mathsf{PERIOD}} \ensuremath{\mathsf{I}} \ensuremath{\mathsf{SPCLK}}\xspace{\mathsf{PERIOD}} \ensuremath{\mathsf{SPCLK}}\xspace{\mathsf{PERIOD}} \ensuremath{\mathsf{I}} \ensuremath{\mathsf{SPCLK}}\xspace{\mathsf{PERIOD}} \ensuremath{\mathsf{I}} \ensuremath{\mathsf{SPCLK}}\xspace{\mathsf{I}} \ensuremath{\mathsf{SPCLK}}\xspace{\mathsf{I}} \ensuremath{\mathsf{SPCLK}}\xspace{\mathsf{I}} \ensuremath{\mathsf{SPCLK}}\xspace{\mathsf{I}} \ensuremath{\mathsf{SPCLK}}\xspace{\mathsf{I}} \ensuremath{\mathsf{SPCLK}}\xspace{\mathsf{I}} \ensuremath{\mathsf{SPCLK}}\xspace{\mathsf{I}} \ensuremath{\mathsf{I}}\xspace{\mathsf{I}} \ensuremath{\mathsf{SPCLK}}\xspace{\mathsf{I}} \$$

<sup>7</sup> Display interface clock up time for write:

$$\label{eq:clk_up_kr} \begin{split} \mathbb{I} dicuw \ = \ \frac{1}{2} T_{\mbox{HSP\_CLK}} \cdot ceil \bigg[ \frac{2 \cdot D \mbox{ISP\#\_F\_CLK\_UP\_WR}}{\mbox{HSP\_CLK\_PERIOD}} \bigg] \end{split}$$

- <sup>8</sup> This parameter is a requirement to the display connected to the IPU.

- <sup>9</sup> Data read point:

$drp = T_{HSP_CLK} \cdot ceil \left[ \frac{DISP\#_READ_EN}{HSP_CLK_PERIOD} \right]$

<sup>10</sup> Loopback delay Tlbd is the cumulative propagation delay of read controls and read data. It includes an IPU output delay, a device-level output delay, board delays, a device-level input delay, an IPU input delay. This value is device specific.

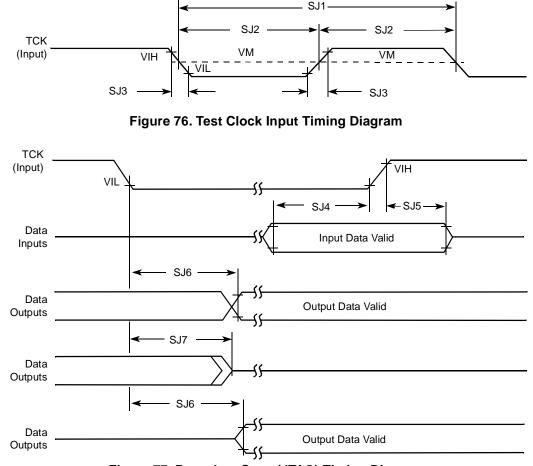

## 4.3.21 SJC Electrical Specifications

This section details the electrical characteristics for the SJC module. Figure 76 depicts the SJC test clock input timing. Figure 77 depicts the SJC boundary scan timing, Figure 78 depicts the SJC test access port, Figure 79 depicts the SJC TRST timing, and Table 56 lists the SJC timing parameters.

Figure 77. Boundary Scan (JTAG) Timing Diagram

| Signal | Ball Location |

|--------|---------------|

| NC     | N7            |

| NC     | P7            |

| NC     | U21           |

| Table 63. | 19 x 19 | <b>BGA No</b> | Connects <sup>1</sup> |

|-----------|---------|---------------|-----------------------|

|-----------|---------|---------------|-----------------------|

<sup>1</sup> These contacts are not used and must be floated by the user.

## 5.1.3.2 BGA Signal ID by Ball Grid Location—19 x 19 0.8 mm

Table 64. 19 x 19 BGA Signal ID by Ball Grid Location

| Signal ID  | Ball Location |

|------------|---------------|

| A0         | Y6            |

| A1         | AC5           |

| A10        | V15           |

| A11        | AB3           |

| A12        | AA3           |

| A13        | Y3            |

| A14        | Y15           |

| A15        | Y14           |

| A16        | V14           |

| A17        | Y13           |

| A18        | V13           |

| A19        | Y12           |

| A2         | AB5           |

| A20        | V12           |

| A21        | Y11           |

| A22        | V11           |

| A23        | Y10           |

| A24        | Y9            |

| A25        | Y8            |

| A3         | AA5           |

| A4         | Y5            |

| A5         | AC4           |

| A6         | AB4           |

| A7         | AA4           |

| A8         | Y4            |

| A9         | AC3           |

| ATA_CS0    | E1            |

| ATA_CS1    | G4            |

| ATA_DIOR   | E3            |

| ATA_DIOW   | H6            |

| ATA_DMACK  | E2            |

| ATA_RESET  | F3            |

| BATT_LINE  | F6            |

| BCLK       | W20           |

| BOOT_MODE0 | F17           |

| BOOT_MODE1 | C21           |

| Signal ID     | Ball Location |

|---------------|---------------|

| CKIL          | E21           |

| CLKO          | C20           |

| CLKSS         | H17           |

| COMPARE       | A20           |

| CONTRAST      | N21           |

| CS0           | U17           |

| CS1           | Y22           |

| CS2           | Y18           |

| CS3           | Y19           |

| CS4           | Y20           |

| CS5           | AA21          |

| CSI_D10       | K21           |

| CSI_D11       | K22           |

| CSI_D12       | K23           |

| CSI_D13       | L20           |

| CSI_D14       | L18           |

| CSI_D15       | L21           |

| CSI_D4        | J20           |

| CSI_D5        | J21           |

| CSI_D6        | L17           |

| CSI_D7        | J22           |

| CSI_D8        | J23           |

| CSI_D9        | K20           |

| CSI_HSYNC     | H22           |

| CSI_MCLK      | H20           |

| CSI_PIXCLK    | H23           |

| CSI_VSYNC     | H21           |

| CSPI1_MISO    | N2            |

| CSPI1_MOSI    | N1            |

| CSPI1_SCLK    | M4            |

| CSPI1_SPI_RDY | M1            |

| CSPI1_SS0     | M2            |

| CSPI1_SS1     | N6            |

| CSPI1_SS2     | M3            |

| CSPI2_MISO    | B4            |

| CSPI2_MOSI    | D5            |

MCIMX31C/MCIMX31LC Technical Data, Rev. 4.3

• *MCIMX31 Chip Errata* (order number MCIMX31CE)

The Freescale manuals are available on the Freescale Semiconductors Web site at http://www.freescale.com/imx. These documents may be downloaded directly from the Freescale Web site, or printed versions may be ordered. ARM Ltd. documentation is available from http://www.arm.com.

# 7 Revision History

Table 65 summarizes revisions to the MCIMX31C/MCIMX31LC Data Sheet since the release of Rev. 3.

| Table 65. Revision History | y of the MCIMX31C/MCIMX31LC Data Sheet |

|----------------------------|----------------------------------------|

|                            |                                        |

| Rev | Location                                                             | Change                                                                  |

|-----|----------------------------------------------------------------------|-------------------------------------------------------------------------|

| 4   | Table 7, "Operating Ranges," on page 12                              | Operating Junction Temperature Range Max: changed from 100 to 105.      |

| 4.1 | Table 1, "MCIMX31C and MCIMX31LC Ordering<br>Information," on page 3 | Added new part numbers MCIMX31CVMN4D and MCIMX31LCVMN4D.                |

| 4.1 | Section 1.2.1, "Feature Differences Between TO2.0 and TO 2.0.1       | Added new section describing differences between silicon revisions.     |

| 4.2 | Table 1, "MCIMX31C and MCIMX31LC Ordering<br>Information," on page 3 | Added new part numbers MCIMX31CJMN4C and MCIMX31LCJMN4D and a footnote. |

| 4.3 | Table 1, "MCIMX31C and MCIMX31LC Ordering<br>Information," on page 3 | Added new part number MCIMX31CJMN4D.                                    |