Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                   |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 30/20MHz                                                                |

| Connectivity               | UART/USART                                                              |

| Peripherals                | POR                                                                     |

| Number of I/O              | 32                                                                      |

| Program Memory Size        | ·                                                                       |

| Program Memory Type        | ROMIess                                                                 |

| EEPROM Size                | ·                                                                       |

| RAM Size                   | 128 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | ·                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-QFP                                                                  |

| Supplier Device Package    | 44-VQFP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/ts80c31x2-lce |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

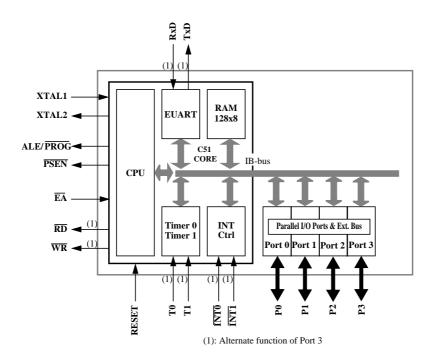

# 3. Block Diagram

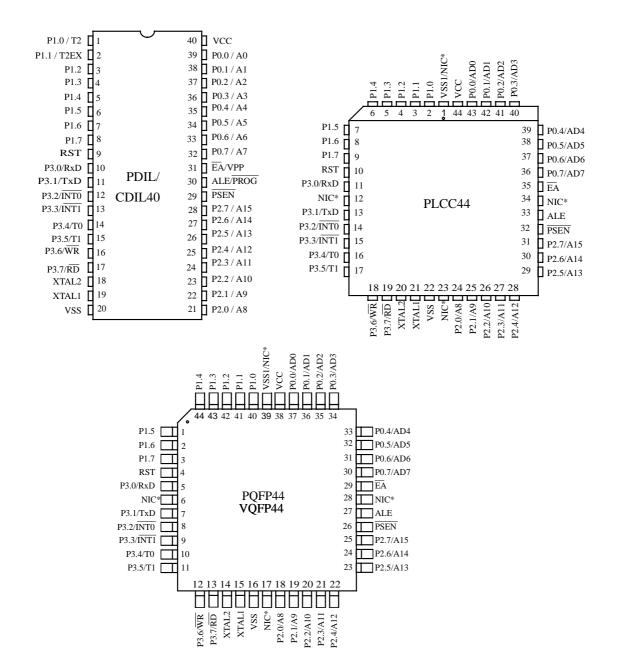

## 5. Pin Configuration

\*NIC: No Internal Connection

## 6. TS80C31X2 Enhanced Features

In comparison to the original 80C31, the TS80C31X2 implements some new features, which are:

- The X2 option.

- The Dual Data Pointer.

- The 4 level interrupt priority system.

- The power-off flag.

- The ONCE mode.

- Enhanced UART

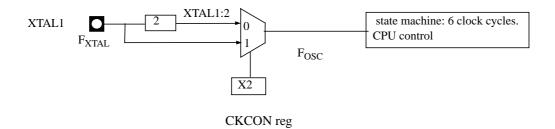

### 6.1 X2 Feature

The TS80C31X2 core needs only 6 clock periods per machine cycle. This feature called "X2" provides the following advantages:

- Divide frequency crystals by 2 (cheaper crystals) while keeping same CPU power.

- Save power consumption while keeping same CPU power (oscillator power saving).

- Save power consumption by dividing dynamically operating frequency by 2 in operating and idle modes.

- Increase CPU power by 2 while keeping same crystal frequency.

In order to keep the original C51 compatibility, a divider by 2 is inserted between the XTAL1 signal and the main clock input of the core (phase generator). This divider may be disabled by software.

### 6.1.1 Description

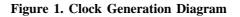

The clock for the whole circuit and peripheral is first divided by two before being used by the CPU core and peripherals. This allows any cyclic ratio to be accepted on XTAL1 input. In X2 mode, as this divider is bypassed, the signals on XTAL1 must have a cyclic ratio between 40 to 60%. Figure 1. shows the clock generation block diagram. X2 bit is validated on XTAL1+2 rising edge to avoid glitches when switching from X2 to STD mode. Figure 2. shows the mode switching waveforms.

### Table 3. CKCON Register

#### CKCON - Clock Control Register (8Fh)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0  |

|---|---|---|---|---|---|---|----|

| - | - | - | - | - | - | - | X2 |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                     |

|---------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7             | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                 |

| 6             | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                 |

| 5             | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                 |

| 4             | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                 |

| 3             | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                 |

| 2             | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                 |

| 1             | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                 |

| 0             | X2              | <b>CPU and peripheral clock bit</b><br>Clear to select 12 clock periods per machine cycle (STD mode, $F_{OSC}=F_{XTAL}/2$ ).<br>Set to select 6 clock periods per machine cycle (X2 mode, $F_{OSC}=F_{XTAL}$ ). |

Reset Value = XXXX XXX0b Not bit addressable

For further details on the X2 feature, please refer to ANM072 available on the web (http://www.atmel-wm.com)

## 6.3 TS80C31X2 Serial I/O Port

The serial I/O port in the TS80C31X2 is compatible with the serial I/O port in the 80C31.

It provides both synchronous and asynchronous communication modes. It operates as an Universal Asynchronous Receiver and Transmitter (UART) in three full-duplex modes (Modes 1, 2 and 3). Asynchronous transmission and reception can occur simultaneously and at different baud rates

Serial I/O port includes the following enhancements:

- Framing error detection

- Automatic address recognition

### 6.3.1 Framing Error Detection

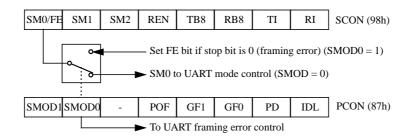

Framing bit error detection is provided for the three asynchronous modes (modes 1, 2 and 3). To enable the framing bit error detection feature, set SMOD0 bit in PCON register (See Figure 4).

#### Figure 4. Framing Error Block Diagram

When this feature is enabled, the receiver checks each incoming data frame for a valid stop bit. An invalid stop bit may result from noise on the serial lines or from simultaneous transmission by two CPUs. If a valid stop bit is not found, the Framing Error bit (FE) in SCON register (See Table 5.) bit is set.

#### 6.3.5 Reset Addresses

On reset, the SADDR and SADEN registers are initialized to 00h, i.e. the given and broadcast addresses are XXXX (all don't-care bits). This ensures that the serial port will reply to any address, and so, that it is backwards compatible with the 80C51 microcontrollers that do not support automatic address recognition.

#### SADEN - Slave Address Mask Register (B9h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = 0000 0000b Not bit addressable

#### SADDR - Slave Address Register (A9h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = 0000 0000b Not bit addressable

### 6.4 Interrupt System

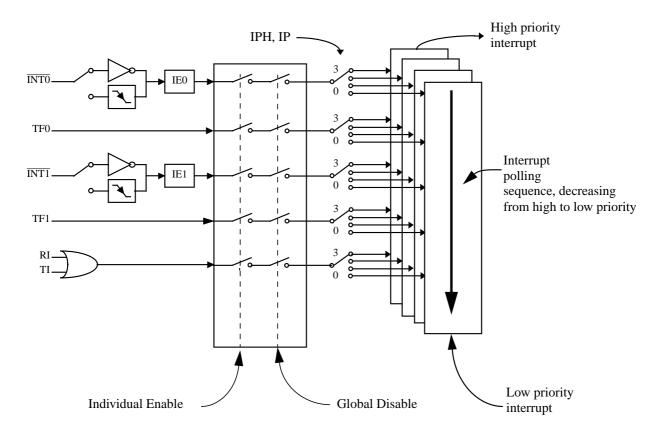

The TS80C31X2 has a total of 5 interrupt vectors: two external interrupts ( $\overline{INT0}$  and  $\overline{INT1}$ ), two timer interrupts (timers 0 and 1) and the serial port interrupt. These interrupts are shown in Figure 7.

#### Figure 7. Interrupt Control System

Each of the interrupt sources can be individually enabled or disabled by setting or clearing a bit in the Interrupt Enable register (See Table 8.). This register also contains a global disable bit, which must be cleared to disable all interrupts at once.

Each interrupt source can also be individually programmed to one out of four priority levels by setting or clearing a bit in the Interrupt Priority register (See Table 9.) and in the Interrupt Priority High register (See Table 10.). shows the bit values and priority levels associated with each combination.

#### Table 7. Priority Level Bit Values

| IPH.x | IP.x | Interrupt Level Priority |

|-------|------|--------------------------|

| 0     | 0    | 0 (Lowest)               |

| 0     | 1    | 1                        |

| 1     | 0    | 2                        |

| 1     | 1    | 3 (Highest)              |

A low-priority interrupt can be interrupted by a high priority interrupt, but not by another low-priority interrupt. A high-priority interrupt can't be interrupted by any other interrupt source.

If two interrupt requests of different priority levels are received simultaneously, the request of higher priority level is serviced. If interrupt requests of the same priority level are received simultaneously, an internal polling sequence determines which request is serviced. Thus within each priority level there is a second priority structure determined by the polling sequence.

## Table 8. IE Register

| IE - Interrupt Enable Register (A8h) |   |   |    |     |     |     |     |  |  |

|--------------------------------------|---|---|----|-----|-----|-----|-----|--|--|

| 7                                    | 6 | 5 | 4  | 3   | 2   | 1   | 0   |  |  |

| EA                                   | - | - | ES | ET1 | EX1 | ЕТО | EX0 |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                 |

|---------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7             | EA              | Enable All interrupt bit<br>Clear to disable all interrupts.<br>Set to enable all interrupts.<br>If EA=1, each interrupt source is individually enabled or disabled by setting or clearing its own interrupt<br>enable bit. |

| 6             | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                             |

| 5             | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                             |

| 4             | ES              | Serial port Enable bit<br>Clear to disable serial port interrupt.<br>Set to enable serial port interrupt.                                                                                                                   |

| 3             | ET1             | Timer 1 overflow interrupt Enable bit           Clear to disable timer 1 overflow interrupt.           Set to enable timer 1 overflow interrupt.                                                                            |

| 2             | EX1             | External interrupt 1 Enable bit<br>Clear to disable external interrupt 1.<br>Set to enable external interrupt 1.                                                                                                            |

| 1             | ET0             | <b>Timer 0 overflow interrupt Enable bit</b><br>Clear to disable timer 0 overflow interrupt.<br>Set to enable timer 0 overflow interrupt.                                                                                   |

| 0             | EX0             | External interrupt 0 Enable bit<br>Clear to disable external interrupt 0.<br>Set to enable external interrupt 0.                                                                                                            |

Reset Value = 0XX0 0000b Bit addressable

#### IP - Interrupt Priority Register (B8h)

| 7             | 6               | 5                                                                      | 4                                                                                   | 3   | 2   | 1   | 0   |  |  |

|---------------|-----------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----|-----|-----|-----|--|--|

| -             | -               | -                                                                      | PS                                                                                  | PT1 | PX1 | РТО | PX0 |  |  |

| Bit<br>Number | Bit<br>Mnemonic |                                                                        | Description                                                                         |     |     |     |     |  |  |

| 7             | -               | Reserved<br>The value read t                                           | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.     |     |     |     |     |  |  |

| 6             | -               | Reserved<br>The value read t                                           | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.     |     |     |     |     |  |  |

| 5             | -               | Reserved<br>The value read t                                           | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.     |     |     |     |     |  |  |

| 4             | PS              |                                                                        | Serial port Priority bit<br>Refer to PSH for priority level.                        |     |     |     |     |  |  |

| 3             | PT1             |                                                                        | Timer 1 overflow interrupt Priority bit           Refer to PT1H for priority level. |     |     |     |     |  |  |

| 2             | PX1             |                                                                        | External interrupt 1 Priority bit<br>Refer to PX1H for priority level.              |     |     |     |     |  |  |

| 1             | PT0             |                                                                        | Timer 0 overflow interrupt Priority bit<br>Refer to PT0H for priority level.        |     |     |     |     |  |  |

| 0             | PX0             | External interrupt 0 Priority bit<br>Refer to PX0H for priority level. |                                                                                     |     |     |     |     |  |  |

Reset Value = XXX0 0000b Bit addressable

# 6.7 ONCE<sup>TM</sup> Mode (ON Chip Emulation)

The ONCE mode facilitates testing and debugging of systems using TS80C31X2 without removing the circuit from the board. The ONCE mode is invoked by driving certain pins of the TS80C31X2; the following sequence must be exercised:

- Pull ALE low while the device is in reset (RST high) and  $\overline{\text{PSEN}}$  is high.

- Hold ALE low as RST is deactivated.

While the TS80C31X2 is in ONCE mode, an emulator or test CPU can be used to drive the circuit Table 26. shows the status of the port pins during ONCE mode.

Normal operation is restored when normal reset is applied.

#### Table 12. External Pin Status during ONCE Mode

| ALE          | PSEN         | Port 0 | Port 1       | Port 2       | Port 3       | XTAL1/2 |

|--------------|--------------|--------|--------------|--------------|--------------|---------|

| Weak pull-up | Weak pull-up | Float  | Weak pull-up | Weak pull-up | Weak pull-up | Active  |

# 7. Electrical Characteristics

## 7.1 Absolute Maximum Ratings <sup>(1)</sup>

| Ambiant Temperature Under Bias:               |                                    |

|-----------------------------------------------|------------------------------------|

| C = commercial                                | 0°C to 70°C                        |

| I = industrial                                | -40°C to 85°C                      |

| Storage Temperature                           | $-65^{\circ}C$ to $+ 150^{\circ}C$ |

| Voltage on V <sub>CC</sub> to V <sub>SS</sub> | -0.5 V to + 7 V                    |

| Voltage on $V_{PP}$ to $V_{SS}$               | -0.5 V to + 13 V                   |

| Voltage on Any Pin to V <sub>SS</sub>         | -0.5 V to $V_{CC}$ + 0.5 V         |

| Power Dissipation                             | $1 W^{(2)}$                        |

|                                               |                                    |

NOTES

1. Stresses at or above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

2. This value is based on the maximum allowable die temperature and the thermal resistance of the package.

### 7.2 Power consumption measurement

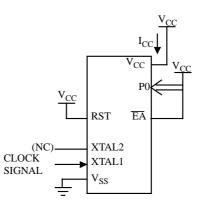

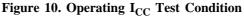

Since the introduction of the first C51 devices, every manufacturer made operating Icc measurements under reset, which made sense for the designs were the CPU was running under reset. In Atmel Wireless & Microcontrollers new devices, the CPU is no more active during reset, so the power consumption is very low but is not really representative of what will happen in the customer system. That's why, while keeping measurements under Reset, Atmel Wireless & Microcontrollers presents a new way to measure the operating Icc:

Using an internal test ROM, the following code is executed:

Label: SJMP Label (80 FE)

Ports 1, 2, 3 are disconnected, Port 0 is tied to FFh, EA = Vcc, RST = Vss, XTAL2 is not connected and XTAL1 is driven by the clock.

This is much more representative of the real operating Icc.

### 7.3 DC Parameters for Standard Voltage

$\begin{array}{l} TA = 0^{\circ}C \mbox{ to } +70^{\circ}C; \mbox{ } V_{SS} = 0 \mbox{ } V; \mbox{ } V_{CC} = 5 \mbox{ } V \pm 10\%; \mbox{ } F = 0 \mbox{ to } 40 \mbox{ } MHz. \\ TA = -40^{\circ}C \mbox{ to } +85^{\circ}C; \mbox{ } V_{SS} = 0 \mbox{ } V; \mbox{ } V_{CC} = 5 \mbox{ } V \pm 10\%; \mbox{ } F = 0 \mbox{ to } 40 \mbox{ } MHz. \\ \end{array}$

| Table 14. | DC | <b>Parameters</b> | in | Standard | Voltage |

|-----------|----|-------------------|----|----------|---------|

|-----------|----|-------------------|----|----------|---------|

| Symbol                            | Parameter                                                    | Min                                                                     | Тур               | Max                                               | Unit        | Test Conditions                                                                                                                    |

|-----------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------|-------------------|---------------------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>IL</sub>                   | Input Low Voltage                                            | -0.5                                                                    |                   | 0.2 V <sub>CC</sub> - 0.1                         | v           |                                                                                                                                    |

| V <sub>IH</sub>                   | Input High Voltage except XTAL1, RST                         | 0.2 V <sub>CC</sub> + 0.9                                               |                   | V <sub>CC</sub> + 0.5                             | v           |                                                                                                                                    |

| V <sub>IH1</sub>                  | Input High Voltage, XTAL1, RST                               | 0.7 V <sub>CC</sub>                                                     |                   | V <sub>CC</sub> + 0.5                             | v           |                                                                                                                                    |

| V <sub>OL</sub>                   | Output Low Voltage, ports 1, 2, 3 <sup>(6)</sup>             |                                                                         |                   | 0.3<br>0.45<br>1.0                                | V<br>V<br>V | $I_{OL} = 100 \ \mu A^{(4)}$ $I_{OL} = 1.6 \ m A^{(4)}$ $I_{OL} = 3.5 \ m A^{(4)}$                                                 |

| V <sub>OL1</sub>                  | Output Low Voltage, port 0 <sup>(6)</sup>                    |                                                                         |                   | 0.3<br>0.45<br>1.0                                | V<br>V<br>V | $I_{OL} = 200 \ \mu A^{(4)}$ $I_{OL} = 3.2 \ m A^{(4)}$ $I_{OL} = 7.0 \ m A^{(4)}$                                                 |

| V <sub>OL2</sub>                  | Output Low Voltage, ALE, PSEN                                |                                                                         |                   | 0.3<br>0.45<br>1.0                                | V<br>V<br>V | $I_{OL} = 100 \ \mu A^{(4)}$ $I_{OL} = 1.6 \ m A^{(4)}$ $I_{OL} = 3.5 \ m A^{(4)}$                                                 |

| V <sub>OH</sub>                   | Output High Voltage, ports 1, 2, 3                           | $V_{CC} - 0.3$<br>$V_{CC} - 0.7$<br>$V_{CC} - 1.5$                      |                   |                                                   | V<br>V<br>V | $I_{OH} = -10 \ \mu A$ $I_{OH} = -30 \ \mu A$ $I_{OH} = -60 \ \mu A$ $V_{CC} = 5 \ V \pm 10\%$                                     |

| V <sub>OH1</sub>                  | Output High Voltage, port 0                                  | V <sub>CC</sub> - 0.3<br>V <sub>CC</sub> - 0.7<br>V <sub>CC</sub> - 1.5 |                   |                                                   | V<br>V<br>V | $\begin{split} I_{OH} &= -200 \; \mu A \\ I_{OH} &= -3.2 \; m A \\ I_{OH} &= -7.0 \; m A \\ V_{CC} &= 5 \; V \pm 10\% \end{split}$ |

| V <sub>OH2</sub>                  | Output High Voltage, ALE, PSEN                               | V <sub>CC</sub> - 0.3<br>V <sub>CC</sub> - 0.7<br>V <sub>CC</sub> - 1.5 |                   |                                                   | V<br>V<br>V | $\begin{split} I_{OH} &= -100 \; \mu A \\ I_{OH} &= -1.6 \; m A \\ I_{OH} &= -3.5 \; m A \\ V_{CC} &= 5 \; V \pm 10\% \end{split}$ |

| R <sub>RST</sub>                  | RST Pulldown Resistor                                        | 50                                                                      | 90 <sup>(5)</sup> | 200                                               | kΩ          |                                                                                                                                    |

| I <sub>IL</sub>                   | Logical 0 Input Current ports 1, 2 and 3                     |                                                                         |                   | -50                                               | μΑ          | Vin = 0.45 V                                                                                                                       |

| I <sub>LI</sub>                   | Input Leakage Current                                        |                                                                         |                   | ±10                                               | μΑ          | 0.45 V < Vin < V <sub>CC</sub>                                                                                                     |

| I <sub>TL</sub>                   | Logical 1 to 0 Transition Current, ports 1, 2, 3             |                                                                         |                   | -650                                              | μΑ          | Vin = 2.0 V                                                                                                                        |

| C <sub>IO</sub>                   | Capacitance of I/O Buffer                                    |                                                                         |                   | 10                                                | pF          | $Fc = 1 MHz$ $TA = 25^{\circ}C$                                                                                                    |

| I <sub>PD</sub>                   | Power Down Current                                           |                                                                         | 20 <sup>(5)</sup> | 50                                                | μΑ          | $2.0 \text{ V} < \text{V}_{\text{CC}} < 5.5 \text{ V}^{(3)}$                                                                       |

| I <sub>CC</sub><br>under<br>RESET | Power Supply Current Maximum values, X1 mode: <sup>(7)</sup> |                                                                         |                   | 1 + 0.4 Freq<br>(MHz)<br>@12MHz 5.8<br>@16MHz 7.4 | mA          | $V_{CC} = 5.5 V^{(1)}$                                                                                                             |

| Symbol                       | Parameter                                                    | Min | Тур | Max                                                 | Unit | Test Conditions              |

|------------------------------|--------------------------------------------------------------|-----|-----|-----------------------------------------------------|------|------------------------------|

| I <sub>CC</sub><br>operating | Power Supply Current Maximum values, X1 mode: <sup>(7)</sup> |     |     | 3 + 0.6 Freq<br>(MHz)<br>@12MHz 10.2<br>@16MHz 12.6 | mA   | $V_{\rm CC} = 5.5 \ V^{(8)}$ |

| I <sub>CC</sub><br>idle      | Power Supply Current Maximum values, X1 mode: <sup>(7)</sup> |     |     | 0.25+0.3Freq<br>(MHz)<br>@12MHz 3.9<br>@16MHz 5.1   | mA   | $V_{CC} = 5.5 V^{(2)}$       |

## 7.4 DC Parameters for Low Voltage

TA = 0°C to +70°C; V<sub>SS</sub> = 0 V; V<sub>CC</sub> = 2.7 V to 5.5 V  $\pm$  10%; F = 0 to 30 MHz. TA = -40°C to +85°C; V<sub>SS</sub> = 0 V; V<sub>CC</sub> = 2.7 V to 5.5 V  $\pm$  10%; F = 0 to 30 MHz.

Table 15. DC Parameters for Low Voltage

| Symbol                            | Parameter                                                    | Min                 | Тур                                    | Max                                               | Unit | Test Conditions                                                                                      |

|-----------------------------------|--------------------------------------------------------------|---------------------|----------------------------------------|---------------------------------------------------|------|------------------------------------------------------------------------------------------------------|

| V <sub>IL</sub>                   | Input Low Voltage                                            | -0.5                |                                        | 0.2 V <sub>CC</sub> - 0.1                         | V    |                                                                                                      |

| V <sub>IH</sub>                   | Input High Voltage except XTAL1, RST                         | $0.2 V_{CC} + 0.9$  |                                        | V <sub>CC</sub> + 0.5                             | V    |                                                                                                      |

| V <sub>IH1</sub>                  | Input High Voltage, XTAL1, RST                               | 0.7 V <sub>CC</sub> |                                        | V <sub>CC</sub> + 0.5                             | V    |                                                                                                      |

| V <sub>OL</sub>                   | Output Low Voltage, ports 1, 2, 3 <sup>(6)</sup>             |                     |                                        | 0.45                                              | v    | $I_{OL} = 0.8 \text{ mA}^{(4)}$                                                                      |

| V <sub>OL1</sub>                  | Output Low Voltage, port 0, ALE, PSEN <sup>(6)</sup>         |                     |                                        | 0.45                                              | v    | $I_{OL} = 1.6 \text{ mA}^{(4)}$                                                                      |

| V <sub>OH</sub>                   | Output High Voltage, ports 1, 2, 3                           | 0.9 V <sub>CC</sub> |                                        |                                                   | V    | $I_{OH} = -10 \ \mu A$                                                                               |

| V <sub>OH1</sub>                  | Output High Voltage, port 0, ALE, PSEN                       | 0.9 V <sub>CC</sub> |                                        |                                                   | V    | $I_{OH} = -40 \ \mu A$                                                                               |

| I <sub>IL</sub>                   | Logical 0 Input Current ports 1, 2 and 3                     |                     |                                        | -50                                               | μΑ   | Vin = 0.45 V                                                                                         |

| $I_{LI}$                          | Input Leakage Current                                        |                     |                                        | ±10                                               | μΑ   | 0.45 V < Vin < V <sub>CC</sub>                                                                       |

| I <sub>TL</sub>                   | Logical 1 to 0 Transition Current, ports 1, 2, 3             |                     |                                        | -650                                              | μΑ   | Vin = 2.0 V                                                                                          |

| R <sub>RST</sub>                  | RST Pulldown Resistor                                        | 50                  | 90 <sup>(5)</sup>                      | 200                                               | kΩ   |                                                                                                      |

| CIO                               | Capacitance of I/O Buffer                                    |                     |                                        | 10                                                | pF   | $Fc = 1 MHz$ $TA = 25^{\circ}C$                                                                      |

| I <sub>PD</sub>                   | Power Down Current                                           |                     | 20 <sup>(5)</sup><br>10 <sup>(5)</sup> | 50<br>30                                          | μΑ   | $V_{CC} = 2.0 \text{ V to } 5.5 \text{ V}^{(3)}$<br>$V_{CC} = 2.0 \text{ V to } 3.3 \text{ V}^{(3)}$ |

| I <sub>CC</sub><br>under<br>RESET | Power Supply Current Maximum values, X1 mode: <sup>(7)</sup> |                     |                                        | 1 + 0.2 Freq<br>(MHz)<br>@12MHz 3.4<br>@16MHz 4.2 | mA   | $V_{CC} = 3.3 V^{(1)}$                                                                               |

| I <sub>CC</sub><br>operating      | Power Supply Current Maximum values, X1 mode: <sup>(7)</sup> |                     |                                        | 1 + 0.3 Freq<br>(MHz)<br>@12MHz 4.6<br>@16MHz 5.8 | mA   | $V_{CC} = 3.3 V^{(8)}$                                                                               |

| Symbol                  | Parameter                                                    | Min | Тур | Max                                                | Unit | Test Conditions        |

|-------------------------|--------------------------------------------------------------|-----|-----|----------------------------------------------------|------|------------------------|

| I <sub>CC</sub><br>idle | Power Supply Current Maximum values, X1 mode: <sup>(7)</sup> |     |     | 0.15 Freq<br>(MHz) + 0.2<br>@12MHz 2<br>@16MHz 2.6 | mA   | $V_{CC} = 3.3 V^{(2)}$ |

NOTES

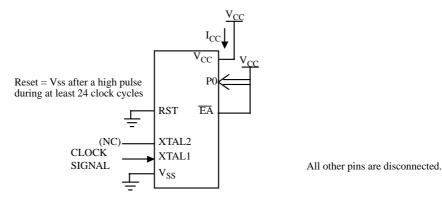

1.  $I_{CC}$  under reset is measured with all output pins disconnected; XTAL1 driven with  $T_{CLCH}$ ,  $T_{CHCL} = 5$  ns (see Figure 13.),  $V_{IL} = V_{SS} + 0.5$  V,  $V_{IH} = V_{CC} - 0.5$ V; XTAL2 N.C.;  $\overline{EA} = RST = Port 0 = V_{CC}$ .  $I_{CC}$  would be slightly higher if a crystal oscillator used.

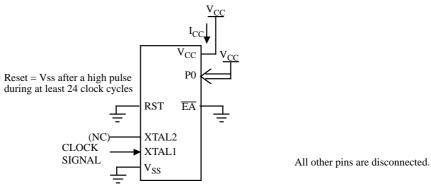

2. Idle  $I_{CC}$  is measured with all output pins disconnected; XTAL1 driven with  $T_{CLCH}$ ,  $T_{CHCL} = 5$  ns,  $V_{IL} = V_{SS} + 0.5$  V,  $V_{IH} = V_{CC} - 0.5$  V; XTAL2 N.C; Port  $0 = V_{CC}$ ;  $\overline{EA} = RST = V_{SS}$  (see Figure 11.).

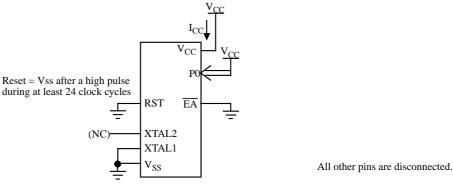

3. Power Down  $I_{CC}$  is measured with all output pins disconnected;  $\overline{EA} = V_{SS}$ , PORT  $0 = V_{CC}$ ; XTAL2 NC.; RST =  $V_{SS}$  (see Figure 12.).

4. Capacitance loading on Ports 0 and 2 may cause spurious noise pulses to be superimposed on the  $V_{OL}$ s of ALE and Ports 1 and 3. The noise is due to external bus capacitance discharging into the Port 0 and Port 2 pins when these pins make 1 to 0 transitions during bus operation. In the worst cases (capacitive loading 100pF), the noise pulse on the ALE line may exceed 0.45V with maxi  $V_{OL}$  peak 0.6V. A Schmitt Trigger use is not necessary.

5. Typicals are based on a limited number of samples and are not guaranteed. The values listed are at room temperature and 5V.

6. Under steady state (non-transient) conditions, I<sub>OL</sub> must be externally limited as follows:

Maximum I<sub>OL</sub> per port pin: 10 mA Maximum I<sub>OL</sub> per 8-bit port:

Port 0: 26 mA

Ports 1, 2 and 3: 15 mA Maximum total I<sub>OL</sub> for all output pins: 71 mA

If  $I_{OL}$  exceeds the test condition,  $V_{OL}$  may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions. 7. For other values, please contact your sales office.

8. Operating  $I_{CC}$  is measured with all output pins disconnected; XTAL1 driven with  $T_{CLCH}$ ,  $T_{CHCL} = 5$  ns (see Figure 13.),  $V_{IL} = V_{SS} + 0.5$  V,

$V_{IH} = V_{CC} - 0.5V$ ; XTAL2 N.C.;  $\overline{EA} = Port \ 0 = V_{CC}$ ; RST =  $V_{SS}$ . The internal ROM runs the code 80 FE (label: SJMP label).  $I_{CC}$  would be slightly higher if a crystal oscillator is used. Measurements are made with OTP products when possible, which is the worst case.

All other pins are disconnected.

Figure 9. I<sub>CC</sub> Test Condition, under reset

Figure 11.  $I_{CC}$  Test Condition, Idle Mode

Figure 12. I<sub>CC</sub> Test Condition, Power-Down Mode

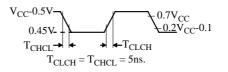

Figure 13. Clock Signal Waveform for  $I_{\mbox{\scriptsize CC}}$  Tests in Active and Idle Modes

# 7.5.4 External Data Memory Characteristics

## Table 21. Symbol Description

| Symbol            | Parameter                   |

|-------------------|-----------------------------|

| T <sub>RLRH</sub> | RD Pulse Width              |

| T <sub>WLWH</sub> | WR Pulse Width              |

| T <sub>RLDV</sub> | RD to Valid Data In         |

| T <sub>RHDX</sub> | Data Hold After RD          |

| T <sub>RHDZ</sub> | Data Float After RD         |

| T <sub>LLDV</sub> | ALE to Valid Data In        |

| T <sub>AVDV</sub> | Address to Valid Data In    |

| T <sub>LLWL</sub> | ALE to WR or RD             |

| T <sub>AVWL</sub> | Address to WR or RD         |

| T <sub>QVWX</sub> | Data Valid to WR Transition |

| T <sub>QVWH</sub> | Data set-up to WR High      |

| T <sub>WHQX</sub> | Data Hold After WR          |

| T <sub>RLAZ</sub> | RD Low to Address Float     |

| T <sub>WHLH</sub> | RD or WR High to ALE high   |

| Speed             | SpeedM<br>40 MHz |     | -V<br>X2 mode<br>30 MHz<br>60 MHz equiv. |     | -V<br>standard mode<br>40 MHz |     | -L<br>X2 mode<br>20 MHz<br>40 MHz equiv. |     | -L<br>standard mode<br>30 MHz |     | Units |

|-------------------|------------------|-----|------------------------------------------|-----|-------------------------------|-----|------------------------------------------|-----|-------------------------------|-----|-------|

| Symbol            | Min              | Max | Min                                      | Max | Min                           | Max | Min                                      | Max | Min                           | Max |       |

| T <sub>RLRH</sub> | 130              |     | 85                                       |     | 135                           |     | 125                                      |     | 175                           |     | ns    |

| T <sub>WLWH</sub> | 130              |     | 85                                       |     | 135                           |     | 125                                      |     | 175                           |     | ns    |

| T <sub>RLDV</sub> |                  | 100 |                                          | 60  |                               | 102 |                                          | 95  |                               | 137 | ns    |

| T <sub>RHDX</sub> | 0                |     | 0                                        |     | 0                             |     | 0                                        |     | 0                             |     | ns    |

| T <sub>RHDZ</sub> |                  | 30  |                                          | 18  |                               | 35  |                                          | 25  |                               | 42  | ns    |

| T <sub>LLDV</sub> |                  | 160 |                                          | 98  |                               | 165 |                                          | 155 |                               | 222 | ns    |

| T <sub>AVDV</sub> |                  | 165 |                                          | 100 |                               | 175 |                                          | 160 |                               | 235 | ns    |

| T <sub>LLWL</sub> | 50               | 100 | 30                                       | 70  | 55                            | 95  | 45                                       | 105 | 70                            | 130 | ns    |

| T <sub>AVWL</sub> | 75               |     | 47                                       |     | 80                            |     | 70                                       |     | 103                           |     | ns    |

| T <sub>QVWX</sub> | 10               |     | 7                                        |     | 15                            |     | 5                                        |     | 13                            |     | ns    |

| T <sub>QVWH</sub> | 160              |     | 107                                      |     | 165                           |     | 155                                      |     | 213                           |     | ns    |

| T <sub>WHQX</sub> | 15               |     | 9                                        |     | 17                            |     | 10                                       |     | 18                            |     | ns    |

| T <sub>RLAZ</sub> |                  | 0   |                                          | 0   |                               | 0   |                                          | 0   |                               | 0   | ns    |

| T <sub>WHLH</sub> | 10               | 40  | 7                                        | 27  | 15                            | 35  | 5                                        | 45  | 13                            | 53  | ns    |

Table 22. AC Parameters for a Fix Clock

| Symbol            | Туре | Standard<br>Clock | X2 Clock  | -M | -V | -L | Units |

|-------------------|------|-------------------|-----------|----|----|----|-------|

| T <sub>RLRH</sub> | Min  | 6 T - x           | 3 T - x   | 20 | 15 | 25 | ns    |

| T <sub>WLWH</sub> | Min  | 6 T - x           | 3 T - x   | 20 | 15 | 25 | ns    |

| T <sub>RLDV</sub> | Max  | 5 T - x           | 2.5 T - x | 25 | 23 | 30 | ns    |

| T <sub>RHDX</sub> | Min  | x                 | х         | 0  | 0  | 0  | ns    |

| T <sub>RHDZ</sub> | Max  | 2 T - x           | T - x     | 20 | 15 | 25 | ns    |

| T <sub>LLDV</sub> | Max  | 8 T - x           | 4T -x     | 40 | 35 | 45 | ns    |

| T <sub>AVDV</sub> | Max  | 9 T - x           | 4.5 T - x | 60 | 50 | 65 | ns    |

| T <sub>LLWL</sub> | Min  | 3 T - x           | 1.5 T - x | 25 | 20 | 30 | ns    |

| T <sub>LLWL</sub> | Max  | 3 T + x           | 1.5 T + x | 25 | 20 | 30 | ns    |

| T <sub>AVWL</sub> | Min  | 4 T - x           | 2 T - x   | 25 | 20 | 30 | ns    |

| T <sub>QVWX</sub> | Min  | T - x             | 0.5 T - x | 15 | 10 | 20 | ns    |

| T <sub>QVWH</sub> | Min  | 7 T - x           | 3.5 T - x | 15 | 10 | 20 | ns    |

| T <sub>WHQX</sub> | Min  | T - x             | 0.5 T - x | 10 | 8  | 15 | ns    |

| T <sub>RLAZ</sub> | Max  | x                 | х         | 0  | 0  | 0  | ns    |

| T <sub>WHLH</sub> | Min  | T - x             | 0.5 T - x | 15 | 10 | 20 | ns    |

| T <sub>WHLH</sub> | Max  | T + x             | 0.5 T + x | 15 | 10 | 20 | ns    |

Table 23. AC Parameters for a Variable Clock: derating formula

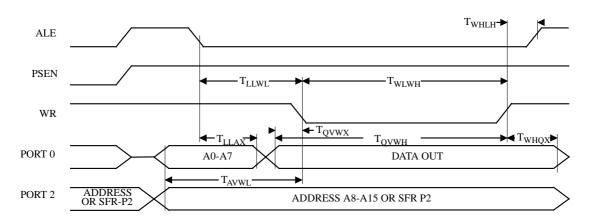

## 7.5.5 External Data Memory Write Cycle

Figure 15. External Data Memory Write Cycle

For timing purposes a port pin is no longer floating when a 100 mV change from load voltage occurs and begins to float when a 100 mV change from the loaded  $V_{OH}/V_{OL}$  level occurs.  $I_{OL}/I_{OH} \ge \pm 20$ mA.

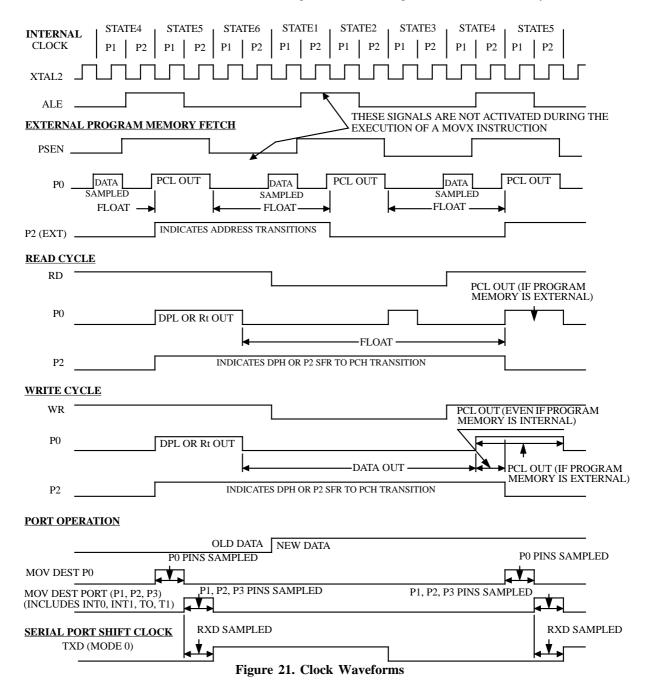

#### 7.5.13 Clock Waveforms

Valid in normal clock mode. In X2 mode XTAL2 signal must be changed to XTAL2 divided by two.

This diagram indicates when signals are clocked internally. The time it takes the signals to propagate to the pins, however, ranges from 25 to 125 ns. This propagation delay is dependent on variables such as temperature and pin loading. Propagation also varies from output to output and component. Typically though ( $T_A=25^{\circ}C$  fully loaded) RD and WR propagation delays are approximately 50ns. The other signals are typically 85 ns. Propagation delays are incorporated in the AC specifications.

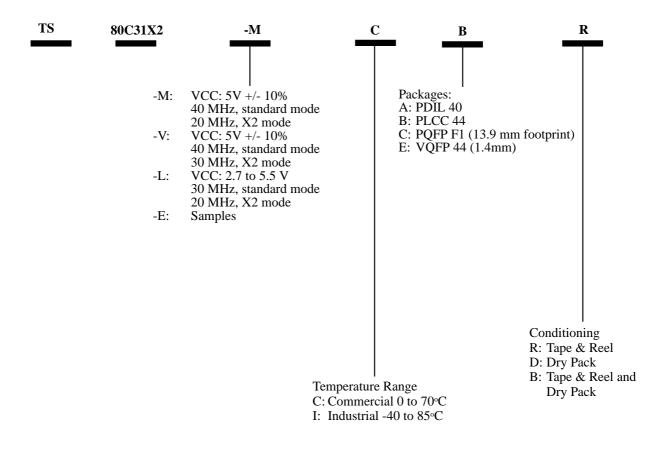

## 8. Ordering Information

Table 28. Maximum Clock Frequency

| Code                                   | -M | -V        | -L        | Unit |

|----------------------------------------|----|-----------|-----------|------|

| Standard Mode, oscillator frequency    | 40 | 40        | 30        | MHz  |

| Standard Mode, internal frequency      | 40 | 40        | 30        |      |

| X2 Mode, oscillator frequency          | 20 | 30        | 20        | MHz  |

| X2 Mode, internal equivalent frequency | 40 | <b>60</b> | <b>40</b> |      |