Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                   |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 30/20MHz                                                                |

| Connectivity               | UART/USART                                                              |

| Peripherals                | POR                                                                     |

| Number of I/O              | 32                                                                      |

| Program Memory Size        | -                                                                       |

| Program Memory Type        | ROMIess                                                                 |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 128 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                |

| Supplier Device Package    | 40-PDIL                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/ts80c31x2-lia |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TS80C31X2

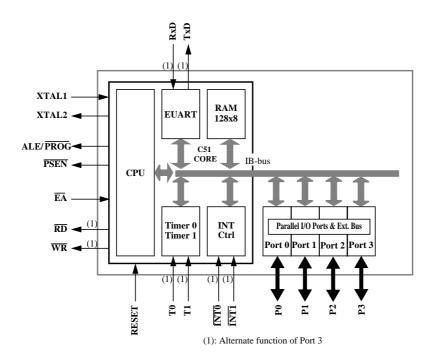

# 3. Block Diagram

| Table 2. | Pin | Description | for | 40/44 | pin | packages |

|----------|-----|-------------|-----|-------|-----|----------|

|----------|-----|-------------|-----|-------|-----|----------|

|                 | PIN NUMBER |              |              |       | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|-----------------|------------|--------------|--------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MNEMONIC        | DIL        | LCC          | VQFP 1.4     | TYPE  | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| V <sub>SS</sub> | 20         | 22           | 16           | I     | Ground: 0V reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Vss1            |            | 1            | 39           | Ι     | Optional Ground: Contact the Sales Office for ground connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| V <sub>CC</sub> | 40         | 44           | 38           | Ι     | <b>Power Supply:</b> This is the power supply voltage for normal, idle and power-<br>down operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| P0.0-P0.7       | 39-32      | 43-36        | 37-30        | I/O   | <b>Port 0</b> : Port 0 is an open-drain, bidirectional I/O port. Port 0 pins that have 1s written to them float and can be used as high impedance inputs. Port 0 pins must be polarized to Vcc or Vss in order to prevent any parasitic current consumption. Port 0 is also the multiplexed low-order address and data bus during access to external program and data memory. In this application, it uses strong internal pull-up when emitting 1s.                                                                                                                                                                                                                        |  |  |  |

| P1.0-P1.7       | 1-8        | 2-9          | 40-44<br>1-3 | I/O   | <b>Port 1:</b> Port 1 is an 8-bit bidirectional I/O port with internal pull-ups. Port 1 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 1 pins that are externally pulled low will source current because of the internal pull-ups.                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| P2.0-P2.7       | 21-28      | 24-31        | 18-25        | I/O   | <b>Port 2</b> : Port 2 is an 8-bit bidirectional I/O port with internal pull-ups. Port 2 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 2 pins that are externally pulled low will source current because of the internal pull-ups. Port 2 emits the high-order address byte during fetches from external program memory and during accesses to external data memory that use 16-bit addresses (MOVX @DPTR).In this application, it uses strong internal pull-ups emitting 1s. During accesses to external data memory that use 8-bit addresses (MOVX @Ri), port 2 emits the contents of the P2 SFR. |  |  |  |

| P3.0-P3.7       | 10-17      | 11,<br>13-19 | 5,<br>7-13   | I/O   | <b>Port 3:</b> Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 3 pins that are externally pulled low will source current because of the internal pull-ups. Port 3 also serves the special features of the 80C51 family, as listed below.                                                                                                                                                                                                                                                                                     |  |  |  |

|                 | 10         | 11           | 5            | I     | RXD (P3.0): Serial input port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                 | 11         | 13           | 7            | 0     | TXD (P3.1): Serial output port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|                 | 12         | 14           | 8            | I     | <b>INTO</b> (P3.2): External interrupt 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                 | 13         | 15           | 9            | I     | <b>INT1</b> (P3.3): External interrupt 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                 | 14         | 16           | 10           | I     | T0 (P3.4): Timer 0 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|                 | 15         | 17           | 11           | I     | T1 (P3.5): Timer 1 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|                 | 16         | 18           | 12           | 0     | WR (P3.6): External data memory write strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                 | 17         | 19           | 13           | 0     | <b>RD</b> (P3.7): External data memory read strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| Reset           | 9          | 10           | 4            | Ι     | <b>Reset:</b> A high on this pin for two machine cycles while the oscillator is running, resets the device. An internal diffused resistor to $V_{SS}$ permits a power-on reset using only an external capacitor to $V_{CC}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| ALE             | 30         | 33           | 27           | (I) O | Address Latch Enable: Output pulse for latching the low byte of the address during an access to external memory. In normal operation, ALE is emitted at a constant rate of 1/6 (1/3 in X2 mode) the oscillator frequency, and can be used for external timing or clocking. Note that one ALE pulse is skipped during each access to external data memory.                                                                                                                                                                                                                                                                                                                   |  |  |  |

| PSEN            | 29         | 32           | 26           | 0     | <b>Program Store ENable:</b> The read strobe to external program memory. When executing code from the external program memory, <b>PSEN</b> is activated twice each machine cycle, except that two <b>PSEN</b> activations are skipped during each access to external data memory. <b>PSEN</b> is not activated during fetches from internal program memory.                                                                                                                                                                                                                                                                                                                 |  |  |  |

| ĒĀ              | 31         | 35           | 29           | Ι     | <b>External Access Enable:</b> $\overline{EA}$ must be externally held low to enable the device to fetch code from external program memory locations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| XTAL1           | 19         | 21           | 15           | I     | <b>Crystal 1:</b> Input to the inverting oscillator amplifier and input to the internal clock generator circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| XTAL2           | 18         | 20           | 14           | 0     | Crystal 2: Output from the inverting oscillator amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

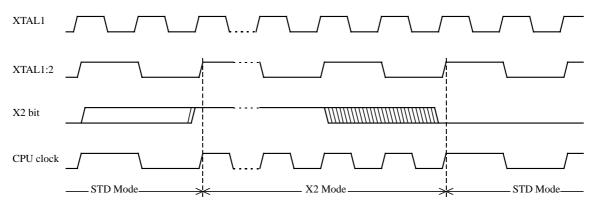

Figure 2. Mode Switching Waveforms

The X2 bit in the CKCON register (See Table 3.) allows to switch from 12 clock cycles per instruction to 6 clock cycles and vice versa. At reset, the standard speed is activated (STD mode). Setting this bit activates the X2 feature (X2 mode).

#### CAUTION

In order to prevent any incorrect operation while operating in X2 mode, user must be aware that all peripherals using clock frequency as time reference (UART, timers) will have their time reference divided by two. For example a free running timer generating an interrupt every 20 ms will then generate an interrupt every 10 ms. UART with 4800 baud rate will have 9600 baud rate.

# **TS80C31X2**

## Table 4. AUXR1: Auxiliary Register 1

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|---|---|---|---|---|---|---|-----|

| - | - | - | - | - | - | - | DPS |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                     |

|---------------|-----------------|---------------------------------------------------------------------------------|

| 7             | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |

| 6             | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |

| 5             | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |

| 4             | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |

| 3             | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |

| 2             | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |

| 1             | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |

| 0             | DPS             | Data Pointer Selection<br>Clear to select DPTR0.<br>Set to select DPTR1.        |

Reset Value = XXXX XXX0 Not bit addressable

## Application

Software can take advantage of the additional data pointers to both increase speed and reduce code size, for example, block operations (copy, compare, search ...) are well served by using one data pointer as a 'source' pointer and the other one as a "destination" pointer.

### ASSEMBLY LANGUAGE

; Block move using dual data pointers ; Destroys DPTR0, DPTR1, A and PSW ; note: DPS exits opposite of entry state ; unless an extra INC AUXR1 is added

00A2 AUXR1 EQU 0A2H 0000 909000MOV DPTR,#SOURCE : address of SOURCE 0003 05A2 INC AUXR1 ; switch data pointers 0005 90A000 MOV DPTR,#DEST ; address of DEST 0008 LOOP: 0008 05A2 INC AUXR1 ; switch data pointers ; get a byte from SOURCE 000A E0 MOVX A, @DPTR INC DPTR ; increment SOURCE address 000B A3 ; switch data pointers 000C 05A2 INC AUXR1 000E F0 MOVX @DPTR,A ; write the byte to DEST 000F A3 INC DPTR : increment DEST address 0010 70F6 JNZ LOOP ; check for 0 terminator 0012 05A2 INC AUXR1 ; (optional) restore DPS

INC is a short (2 bytes) and fast (12 clocks) way to manipulate the DPS bit in the AUXR1 SFR. However, note that the INC instruction does not directly force the DPS bit to a particular state, but simply toggles it. In simple routines, such as the block move example, only the fact that DPS is toggled in the proper sequence matters, not its actual value. In other words, the block move routine works the same whether DPS is '0' or '1' on entry. Observe that without the last instruction (INC AUXR1), the routine will exit with DPS in the opposite state.

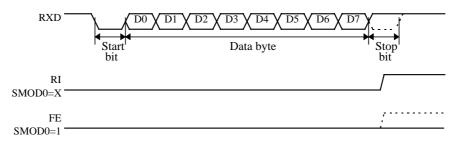

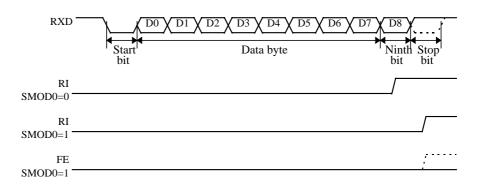

Software may examine FE bit after each reception to check for data errors. Once set, only software or a reset can clear FE bit. Subsequently received frames with valid stop bits cannot clear FE bit. When FE feature is enabled, RI rises on stop bit instead of the last data bit (See Figure 5. and Figure 6.).

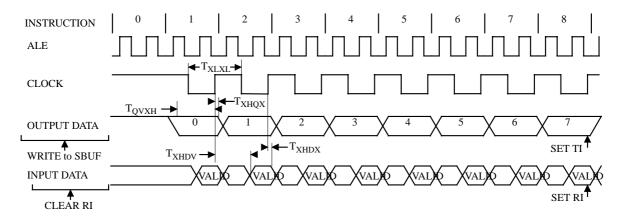

Figure 6. UART Timings in Modes 2 and 3

#### 6.3.2 Automatic Address Recognition

The automatic address recognition feature is enabled when the multiprocessor communication feature is enabled (SM2 bit in SCON register is set).

Implemented in hardware, automatic address recognition enhances the multiprocessor communication feature by allowing the serial port to examine the address of each incoming command frame. Only when the serial port recognizes its own address, the receiver sets RI bit in SCON register to generate an interrupt. This ensures that the CPU is not interrupted by command frames addressed to other devices.

If desired, you may enable the automatic address recognition feature in mode 1. In this configuration, the stop bit takes the place of the ninth data bit. Bit RI is set only when the received command frame address matches the device's address and is terminated by a valid stop bit.

To support automatic address recognition, a device is identified by a given address and a broadcast address.

NOTE: The multiprocessor communication and automatic address recognition features cannot be enabled in mode 0 (i.e. setting SM2 bit in SCON register in mode 0 has no effect).

#### 6.3.5 Reset Addresses

On reset, the SADDR and SADEN registers are initialized to 00h, i.e. the given and broadcast addresses are XXXX (all don't-care bits). This ensures that the serial port will reply to any address, and so, that it is backwards compatible with the 80C51 microcontrollers that do not support automatic address recognition.

#### SADEN - Slave Address Mask Register (B9h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = 0000 0000b Not bit addressable

#### SADDR - Slave Address Register (A9h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = 0000 0000b Not bit addressable

# TS80C31X2

## Table 5. SCON Register

#### SCON - Serial Control Register (98h)

| 7             | 6               | 5                                                 |                             | 4                                                              | 3                                                                            | 2                                                                 | 1                                                                | 0                  |

|---------------|-----------------|---------------------------------------------------|-----------------------------|----------------------------------------------------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------------------------------------|--------------------|

| FE/SM0        | SM1             | SM                                                | 2                           | REN                                                            | TB8                                                                          | RB8                                                               | TI                                                               | RI                 |

| Bit<br>Number | Bit<br>Mnemonic |                                                   |                             |                                                                | Descrip                                                                      | otion                                                             |                                                                  |                    |

| 7             | FE              | Set by ha                                         | reset the err<br>rdware whe | or state, not cle<br>en an invalid st                          | eared by a valid sto<br>op bit is detected.<br>ss to the FE bit              | op bit.                                                           |                                                                  |                    |

|               | SM0             |                                                   | SM1 for ser                 | ial port mode a ared to enable                                 | selection.<br>access to the SM0                                              | bit                                                               |                                                                  |                    |

|               |                 | Serial port M                                     | fode bit 1<br>SM1           | Mada                                                           | Decorinti                                                                    | on Baud Rat                                                       |                                                                  |                    |

| 6             | SM1             | 0<br>0<br>1<br>1                                  | 0<br>1<br>0<br>1            | <u>Mode</u><br>0<br>1<br>2<br>3                                | Descripti<br>Shift Reg<br>8-bit UA<br>9-bit UA<br>9-bit UA                   | ister F <sub>XTAL</sub> /<br>RT Variabl<br>RT F <sub>XTAL</sub> / | –<br>12 (/6 in X2 mode)<br>e<br>64 or F <sub>XTAL</sub> /32 (/32 |                    |

| 5             | SM2             | Clear to o<br>Set to ena                          | disable mult                | tiprocessor con<br>ocessor comm                                | cessor Communic<br>nmunication featur<br>unication feature in                | re.                                                               | d eventually mode                                                | 1. This bit should |

| 4             | REN             |                                                   |                             | al reception.                                                  |                                                                              |                                                                   |                                                                  |                    |

| 3             | TB8             | Clear to t                                        | ransmit a lo                | <b>h bit to trans</b><br>ogic 0 in the 9t<br>ic 1 in the 9th l | <b>mit in modes 2 an</b><br>h bit.<br>pit.                                   | d 3.                                                              |                                                                  |                    |

| 2             | RB8             | Cleared b<br>Set by ha                            | y hardware<br>rdware if 9   | if 9th bit receith bit receith                                 | modes 2 and 3<br>ived is a logic 0.<br>is a logic 1.<br>received stop bit. I | n mode 0 RB8 is 1                                                 | not used.                                                        |                    |

| 1             | TI              | Transmit Int<br>Clear to a<br>Set by ha<br>modes. | acknowledg                  | e interrupt.                                                   | th bit time in mode                                                          | e 0 or at the begin                                               | ning of the stop bit                                             | in the other       |

| 0             | RI              |                                                   | acknowledg                  |                                                                | th bit time in mode                                                          | e 0, see Figure 5.                                                | and Figure 6. in the                                             | e other modes.     |

Reset Value = 0000 0000b Bit addressable

#### Table 6. PCON Register

#### PCON - Power Control Register (87h)

| 7             | 6               | 5                                                      | 4                                                                               | 3                   | 2                    | 1                 | 0   |  |  |

|---------------|-----------------|--------------------------------------------------------|---------------------------------------------------------------------------------|---------------------|----------------------|-------------------|-----|--|--|

| SMOD1         | SMOD            | -                                                      | POF                                                                             | GF1                 | GF0                  | PD                | IDL |  |  |

| Bit<br>Number | Bit<br>Mnemonic |                                                        |                                                                                 | Descrip             | otion                |                   |     |  |  |

| 7             | SMOD1           | Serial port Mode bi<br>Set to select do                | <b>t 1</b><br>Ible baud rate in n                                               | node 1, 2 or 3.     |                      |                   |     |  |  |

| 6             | SMOD0           |                                                        | <b>t 0</b><br>M0 bit in SCON r<br>E bit in SCON reş                             |                     |                      |                   |     |  |  |

| 5             | -               | Reserved<br>The value read f                           | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                     |                      |                   |     |  |  |

| 4             | POF             |                                                        | ze next reset type.<br>when VCC rises f                                         | from 0 to its nomin | al voltage. Can also | be set by softwar | e.  |  |  |

| 3             | GF1             |                                                        | <b>ag</b><br>for general purpos<br>eneral purpose usa                           |                     |                      |                   |     |  |  |

| 2             | GF0             |                                                        | <b>ag</b><br>for general purpos<br>eneral purpose usa                           |                     |                      |                   |     |  |  |

| 1             | PD              | Power-Down mode<br>Cleared by hard<br>Set to enter pow | ware when reset of                                                              | ccurs.              |                      |                   |     |  |  |

| 0             | IDL             | Idle mode bit<br>Clear by hardwa<br>Set to enter idle  | re when interrupt mode.                                                         | or reset occurs.    |                      |                   |     |  |  |

Reset Value = 00X1 0000b Not bit addressable

Power-off flag reset value will be 1 only after a power on (cold reset). A warm reset doesn't affect the value of this bit.

## 6.4 Interrupt System

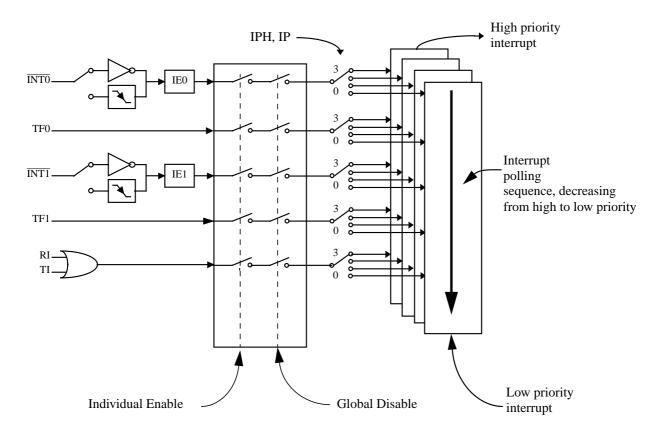

The TS80C31X2 has a total of 5 interrupt vectors: two external interrupts ( $\overline{INT0}$  and  $\overline{INT1}$ ), two timer interrupts (timers 0 and 1) and the serial port interrupt. These interrupts are shown in Figure 7.

#### Figure 7. Interrupt Control System

Each of the interrupt sources can be individually enabled or disabled by setting or clearing a bit in the Interrupt Enable register (See Table 8.). This register also contains a global disable bit, which must be cleared to disable all interrupts at once.

Each interrupt source can also be individually programmed to one out of four priority levels by setting or clearing a bit in the Interrupt Priority register (See Table 9.) and in the Interrupt Priority High register (See Table 10.). shows the bit values and priority levels associated with each combination.

# 6.7 ONCE<sup>TM</sup> Mode (ON Chip Emulation)

The ONCE mode facilitates testing and debugging of systems using TS80C31X2 without removing the circuit from the board. The ONCE mode is invoked by driving certain pins of the TS80C31X2; the following sequence must be exercised:

- Pull ALE low while the device is in reset (RST high) and  $\overline{\text{PSEN}}$  is high.

- Hold ALE low as RST is deactivated.

While the TS80C31X2 is in ONCE mode, an emulator or test CPU can be used to drive the circuit Table 26. shows the status of the port pins during ONCE mode.

Normal operation is restored when normal reset is applied.

#### Table 12. External Pin Status during ONCE Mode

| ALE          | PSEN         | Port 0 | Port 1       | Port 2       | Port 3       | XTAL1/2 |

|--------------|--------------|--------|--------------|--------------|--------------|---------|

| Weak pull-up | Weak pull-up | Float  | Weak pull-up | Weak pull-up | Weak pull-up | Active  |

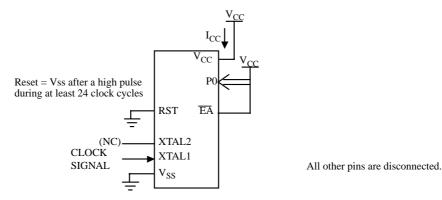

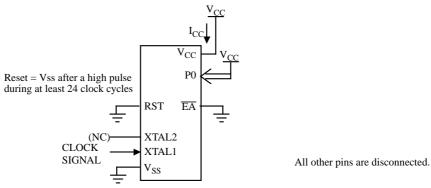

Figure 11.  $I_{CC}$  Test Condition, Idle Mode

Figure 12. I<sub>CC</sub> Test Condition, Power-Down Mode

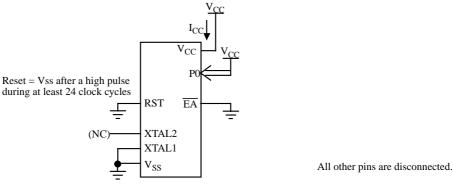

Figure 13. Clock Signal Waveform for  $I_{\mbox{\scriptsize CC}}$  Tests in Active and Idle Modes

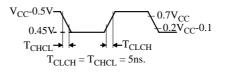

# 7.5 AC Parameters

### 7.5.1 Explanation of the AC Symbols

Each timing symbol has 5 characters. The first character is always a "T" (stands for time). The other characters, depending on their positions, stand for the name of a signal or the logical status of that signal. The following is a list of all the characters and what they stand for.

Example:  $T_{AVLL}$  = Time for Address Valid to ALE Low. T<sub>LLPL</sub> = Time for ALE Low to PSEN Low.

TA = 0 to +70°C (commercial temperature range);  $V_{SS} = 0$  V;  $V_{CC} = 5$  V ± 10%; -M and -V ranges. TA = -40°C to +85°C (industrial temperature range);  $V_{SS} = 0$  V;  $V_{CC} = 5$  V ± 10%; -M and -V ranges. TA = 0 to +70°C (commercial temperature range);  $V_{SS} = 0$  V; 2.7 V <  $V_{CC} < 5.5$  V; -L range. TA = -40°C to +85°C (industrial temperature range);  $V_{SS} = 0$  V; 2.7 V <  $V_{CC} < 5.5$  V; -L range.

Table 16. gives the maximum applicable load capacitance for Port 0, Port 1, 2 and 3, and ALE and  $\overline{\text{PSEN}}$  signals. Timings will be guaranteed if these capacitances are respected. Higher capacitance values can be used, but timings will then be degraded.

|              | -M  | -V | -L  |

|--------------|-----|----|-----|

| Port 0       | 100 | 50 | 100 |

| Port 1, 2, 3 | 80  | 50 | 80  |

| ALE / PSEN   | 100 | 30 | 100 |

| Table 16. | Load | Capacitance            | versus  | speed  | range. | in | рF |

|-----------|------|------------------------|---------|--------|--------|----|----|

|           |      | Capacita in the second | 1010000 | Spece. |        |    | r- |

Table 18., Table 21. and Table 24. give the description of each AC symbols.

Table 19., Table 22. and Table 25. give for each range the AC parameter.

Table 20., Table 23. and Table 26. give the frequency derating formula of the AC parameter. To calculate each AC symbols, take the x value corresponding to the speed grade you need (-M, -V or -L) and replace this value in the formula. Values of the frequency must be limited to the corresponding speed grade:

Table 17. Max frequency for derating formula regarding the speed grade

|            | -M X1 mode | -M X2 mode | -V X1 mode | -V X2 mode | -L X1 mode | -L X2 mode |

|------------|------------|------------|------------|------------|------------|------------|

| Freq (MHz) | 40         | 20         | 40         | 30         | 30         | 20         |

| T (ns)     | 25         | 50         | 25         | 33.3       | 33.3       | 50         |

Example:

$T_{LLIV}$  in X2 mode for a -V part at 20 MHz (T =  $1/20^{E6}$  = 50 ns):

x= 25 (Table 20.)

T = 50 ns

$T_{LLIV} = 2T - x = 2 \times 50 - 25 = 75$ ns

# 7.5.2 External Program Memory Characteristics

| Symbol            | Parameter                         |

|-------------------|-----------------------------------|

| Т                 | Oscillator clock period           |

| T <sub>LHLL</sub> | ALE pulse width                   |

| T <sub>AVLL</sub> | Address Valid to ALE              |

| T <sub>LLAX</sub> | Address Hold After ALE            |

| T <sub>LLIV</sub> | ALE to Valid Instruction In       |

| T <sub>LLPL</sub> | ALE to PSEN                       |

| T <sub>PLPH</sub> | PSEN Pulse Width                  |

| T <sub>PLIV</sub> | PSEN to Valid Instruction In      |

| T <sub>PXIX</sub> | Input Instruction Hold After PSEN |

| T <sub>PXIZ</sub> | Input Instruction FloatAfter PSEN |

| T <sub>PXAV</sub> | PSEN to Address Valid             |

| T <sub>AVIV</sub> | Address to Valid Instruction In   |

| T <sub>PLAZ</sub> | PSEN Low to Address Float         |

| Table 19. AC Parameters for F | Fix Clock |

|-------------------------------|-----------|

|-------------------------------|-----------|

| Speed             |     | M<br>MHz | X2 n<br>30 N | -V -V<br>X2 mode<br>30 MHz<br>60 MHz equiv. |     | -L-LX2 modestandard mode20 MHz30 MHz40 MHz equiv |     | Units |     |     |    |

|-------------------|-----|----------|--------------|---------------------------------------------|-----|--------------------------------------------------|-----|-------|-----|-----|----|

| Symbol            | Min | Max      | Min          | Max                                         | Min | Max                                              | Min | Max   | Min | Max |    |

| Т                 | 25  |          | 33           |                                             | 25  |                                                  | 50  |       | 33  |     | ns |

| T <sub>LHLL</sub> | 40  |          | 25           |                                             | 42  |                                                  | 35  |       | 52  |     | ns |

| T <sub>AVLL</sub> | 10  |          | 4            |                                             | 12  |                                                  | 5   |       | 13  |     | ns |

| T <sub>LLAX</sub> | 10  |          | 4            |                                             | 12  |                                                  | 5   |       | 13  |     | ns |

| T <sub>LLIV</sub> |     | 70       |              | 45                                          |     | 78                                               |     | 65    |     | 98  | ns |

| T <sub>LLPL</sub> | 15  |          | 9            |                                             | 17  |                                                  | 10  |       | 18  |     | ns |

| T <sub>PLPH</sub> | 55  |          | 35           |                                             | 60  |                                                  | 50  |       | 75  |     | ns |

| T <sub>PLIV</sub> |     | 35       |              | 25                                          |     | 50                                               |     | 30    |     | 55  | ns |

| T <sub>PXIX</sub> | 0   |          | 0            |                                             | 0   |                                                  | 0   |       | 0   |     | ns |

| T <sub>PXIZ</sub> |     | 18       |              | 12                                          |     | 20                                               |     | 10    |     | 18  | ns |

| T <sub>AVIV</sub> |     | 85       |              | 53                                          |     | 95                                               |     | 80    |     | 122 | ns |

| T <sub>PLAZ</sub> |     | 10       |              | 10                                          |     | 10                                               |     | 10    |     | 10  | ns |

| Symbol            | Туре | Standard<br>Clock | X2 Clock  | -M | -V | -L | Units |

|-------------------|------|-------------------|-----------|----|----|----|-------|

| T <sub>LHLL</sub> | Min  | 2 T - x           | T - x     | 10 | 8  | 15 | ns    |

| T <sub>AVLL</sub> | Min  | T - x             | 0.5 T - x | 15 | 13 | 20 | ns    |

| T <sub>LLAX</sub> | Min  | T - x             | 0.5 T - x | 15 | 13 | 20 | ns    |

| T <sub>LLIV</sub> | Max  | 4 T - x           | 2 T - x   | 30 | 22 | 35 | ns    |

| T <sub>LLPL</sub> | Min  | T - x             | 0.5 T - x | 10 | 8  | 15 | ns    |

| T <sub>PLPH</sub> | Min  | 3 T - x           | 1.5 T - x | 20 | 15 | 25 | ns    |

| T <sub>PLIV</sub> | Max  | 3 T - x           | 1.5 T - x | 40 | 25 | 45 | ns    |

| T <sub>PXIX</sub> | Min  | x                 | х         | 0  | 0  | 0  | ns    |

| T <sub>PXIZ</sub> | Max  | T - x             | 0.5 T - x | 7  | 5  | 15 | ns    |

| T <sub>AVIV</sub> | Max  | 5 T - x           | 2.5 T - x | 40 | 30 | 45 | ns    |

| T <sub>PLAZ</sub> | Max  | x                 | х         | 10 | 10 | 10 | ns    |

# 7.5.3 External Program Memory Read Cycle

Figure 14. External Program Memory Read Cycle

# 7.5.4 External Data Memory Characteristics

# Table 21. Symbol Description

| Symbol            | Parameter                   |

|-------------------|-----------------------------|

| T <sub>RLRH</sub> | RD Pulse Width              |

| T <sub>WLWH</sub> | WR Pulse Width              |

| T <sub>RLDV</sub> | RD to Valid Data In         |

| T <sub>RHDX</sub> | Data Hold After RD          |

| T <sub>RHDZ</sub> | Data Float After RD         |

| T <sub>LLDV</sub> | ALE to Valid Data In        |

| T <sub>AVDV</sub> | Address to Valid Data In    |

| T <sub>LLWL</sub> | ALE to WR or RD             |

| T <sub>AVWL</sub> | Address to WR or RD         |

| T <sub>QVWX</sub> | Data Valid to WR Transition |

| T <sub>QVWH</sub> | Data set-up to WR High      |

| T <sub>WHQX</sub> | Data Hold After WR          |

| T <sub>RLAZ</sub> | RD Low to Address Float     |

| T <sub>WHLH</sub> | RD or WR High to ALE high   |

| Speed             |     | M<br>MHz | -V<br>X2 mode<br>30 MHz<br>60 MHz equiv. |     | -V<br>standard mode<br>40 MHz |     | -L<br>X2 mode<br>20 MHz<br>40 MHz equiv. |     | -L<br>standard mode<br>30 MHz |     | Units |

|-------------------|-----|----------|------------------------------------------|-----|-------------------------------|-----|------------------------------------------|-----|-------------------------------|-----|-------|

| Symbol            | Min | Max      | Min                                      | Max | Min                           | Max | Min                                      | Max | Min                           | Max |       |

| T <sub>RLRH</sub> | 130 |          | 85                                       |     | 135                           |     | 125                                      |     | 175                           |     | ns    |

| T <sub>WLWH</sub> | 130 |          | 85                                       |     | 135                           |     | 125                                      |     | 175                           |     | ns    |

| T <sub>RLDV</sub> |     | 100      |                                          | 60  |                               | 102 |                                          | 95  |                               | 137 | ns    |

| T <sub>RHDX</sub> | 0   |          | 0                                        |     | 0                             |     | 0                                        |     | 0                             |     | ns    |

| T <sub>RHDZ</sub> |     | 30       |                                          | 18  |                               | 35  |                                          | 25  |                               | 42  | ns    |

| T <sub>LLDV</sub> |     | 160      |                                          | 98  |                               | 165 |                                          | 155 |                               | 222 | ns    |

| T <sub>AVDV</sub> |     | 165      |                                          | 100 |                               | 175 |                                          | 160 |                               | 235 | ns    |

| T <sub>LLWL</sub> | 50  | 100      | 30                                       | 70  | 55                            | 95  | 45                                       | 105 | 70                            | 130 | ns    |

| T <sub>AVWL</sub> | 75  |          | 47                                       |     | 80                            |     | 70                                       |     | 103                           |     | ns    |

| T <sub>QVWX</sub> | 10  |          | 7                                        |     | 15                            |     | 5                                        |     | 13                            |     | ns    |

| T <sub>QVWH</sub> | 160 |          | 107                                      |     | 165                           |     | 155                                      |     | 213                           |     | ns    |

| T <sub>WHQX</sub> | 15  |          | 9                                        |     | 17                            |     | 10                                       |     | 18                            |     | ns    |

| T <sub>RLAZ</sub> |     | 0        |                                          | 0   |                               | 0   |                                          | 0   |                               | 0   | ns    |

| T <sub>WHLH</sub> | 10  | 40       | 7                                        | 27  | 15                            | 35  | 5                                        | 45  | 13                            | 53  | ns    |

Table 22. AC Parameters for a Fix Clock

| Symbol            | Туре | Standard<br>Clock | X2 Clock  | -M | -V | -L | Units |

|-------------------|------|-------------------|-----------|----|----|----|-------|

| T <sub>RLRH</sub> | Min  | 6 T - x           | 3 T - x   | 20 | 15 | 25 | ns    |

| T <sub>WLWH</sub> | Min  | 6 T - x           | 3 T - x   | 20 | 15 | 25 | ns    |

| T <sub>RLDV</sub> | Max  | 5 T - x           | 2.5 T - x | 25 | 23 | 30 | ns    |

| T <sub>RHDX</sub> | Min  | x                 | х         | 0  | 0  | 0  | ns    |

| T <sub>RHDZ</sub> | Max  | 2 T - x           | T - x     | 20 | 15 | 25 | ns    |

| T <sub>LLDV</sub> | Max  | 8 T - x           | 4T -x     | 40 | 35 | 45 | ns    |

| T <sub>AVDV</sub> | Max  | 9 T - x           | 4.5 T - x | 60 | 50 | 65 | ns    |

| T <sub>LLWL</sub> | Min  | 3 T - x           | 1.5 T - x | 25 | 20 | 30 | ns    |

| T <sub>LLWL</sub> | Max  | 3 T + x           | 1.5 T + x | 25 | 20 | 30 | ns    |

| T <sub>AVWL</sub> | Min  | 4 T - x           | 2 T - x   | 25 | 20 | 30 | ns    |

| T <sub>QVWX</sub> | Min  | T - x             | 0.5 T - x | 15 | 10 | 20 | ns    |

| T <sub>QVWH</sub> | Min  | 7 T - x           | 3.5 T - x | 15 | 10 | 20 | ns    |

| T <sub>WHQX</sub> | Min  | T - x             | 0.5 T - x | 10 | 8  | 15 | ns    |

| T <sub>RLAZ</sub> | Max  | x                 | х         | 0  | 0  | 0  | ns    |

| T <sub>WHLH</sub> | Min  | T - x             | 0.5 T - x | 15 | 10 | 20 | ns    |

| T <sub>WHLH</sub> | Max  | T + x             | 0.5 T + x | 15 | 10 | 20 | ns    |

Table 23. AC Parameters for a Variable Clock: derating formula

# 7.5.5 External Data Memory Write Cycle

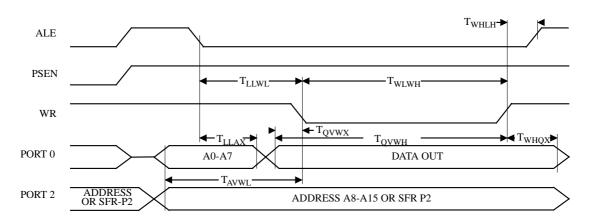

Figure 15. External Data Memory Write Cycle

| Symbol            | Туре | Standard<br>Clock | X2 Clock | -М  | -V  | -L  | Units |

|-------------------|------|-------------------|----------|-----|-----|-----|-------|

| T <sub>XLXL</sub> | Min  | 12 T              | 6 T      |     |     |     | ns    |

| T <sub>QVHX</sub> | Min  | 10 T - x          | 5 T - x  | 50  | 50  | 50  | ns    |

| T <sub>XHQX</sub> | Min  | 2 T - x           | T - x    | 20  | 20  | 20  | ns    |

| T <sub>XHDX</sub> | Min  | х                 | х        | 0   | 0   | 0   | ns    |

| T <sub>XHDV</sub> | Max  | 10 T - x          | 5 T- x   | 133 | 133 | 133 | ns    |

Table 26. AC Parameters for a Variable Clock: derating formula

# 7.5.8 Shift Register Timing Waveforms

Figure 17. Shift Register Timing Waveforms

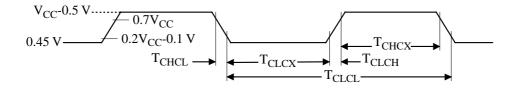

## 7.5.9 External Clock Drive Characteristics (XTAL1)

| Table | 27. | AC | Parameters |

|-------|-----|----|------------|

|-------|-----|----|------------|

| Symbol                               | Parameter               | Min | Max | Units |

|--------------------------------------|-------------------------|-----|-----|-------|

| T <sub>CLCL</sub>                    | Oscillator Period       | 25  |     | ns    |

| T <sub>CHCX</sub>                    | High Time               | 5   |     | ns    |

| T <sub>CLCX</sub>                    | Low Time                | 5   |     | ns    |

| T <sub>CLCH</sub>                    | Rise Time               |     | 5   | ns    |

| T <sub>CHCL</sub>                    | Fall Time               |     | 5   | ns    |

| T <sub>CHCX</sub> /T <sub>CLCX</sub> | Cyclic ratio in X2 mode | 40  | 60  | %     |

### 7.5.10 External Clock Drive Waveforms

#### Figure 18. External Clock Drive Waveforms

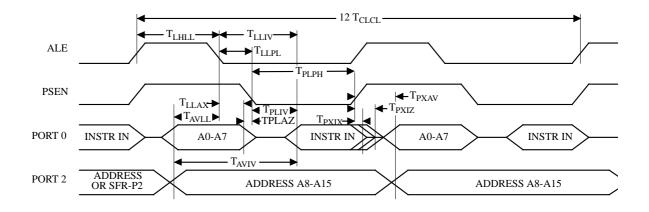

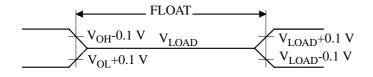

### 7.5.11 AC Testing Input/Output Waveforms

Figure 19. AC Testing Input/Output Waveforms

AC inputs during testing are driven at  $V_{CC}$  - 0.5 for a logic "1" and 0.45V for a logic "0". Timing measurement are made at  $V_{IH}$  min for a logic "1" and  $V_{IL}$  max for a logic "0".

#### 7.5.12 Float Waveforms

Figure 20. Float Waveforms