Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Obsolete                                                              |

| Core Processor             | 56800E                                                                |

| Core Size                  | 16-Bit                                                                |

| Speed                      | 60MHz                                                                 |

| Connectivity               | CANbus, EBI/EMI, SCI, SPI                                             |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                            |

| Number of I/O              | 76                                                                    |

| Program Memory Size        | 128KB (64K x 16)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 6K x 16                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.25V ~ 3.6V                                                          |

| Data Converters            | A/D 16x12b                                                            |

| Oscillator Type            | External                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 160-LQFP                                                              |

| Supplier Device Package    | 160-LQFP (24x24)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc56f8347vpye |

#### **1.1.3 Memory**

**Note:** Features in italics are NOT available in the 56F8147 device.

- Harvard architecture permits as many as three simultaneous accesses to program and data memory

- Flash security protection feature

- On-chip memory, including a low-cost, high-volume Flash solution

- 128KB of Program Flash

- 4KB of Program RAM

- 8KB of Data Flash

- 8KB of Data RAM

- 8KB of Boot Flash

- Off-chip memory expansion capabilities provide a simple method for interfacing additional external memory and/or peripheral devices

- Access up to 4MB of external program memory or 32MB of external data memory

- External accesses supported at up to 60MHz (zero wait states)

- EEPROM emulation capability

### 1.1.4 Peripheral Circuits

**Note:** Features in italics are NOT available in the 56F8147 device.

- Pulse Width Modulator:

- In the 56F8347, two Pulse Width Modulator modules, each with six PWM outputs, three Current Sense inputs, and three Fault inputs; fault-tolerant design with dead time insertion; supports both center-aligned and edge-aligned modes

- In the 56F8147, one Pulse Width Modulator module, with six PWM outputs, three Current Sense inputs, and three Fault inputs; fault-tolerant design with dead time insertion; supports both center-aligned and edge-aligned modes

- Four 12-bit, Analog-to-Digital Converters (ADCs), which support four simultaneous conversions with quad, 4-pin multiplexed inputs; ADC and PWM modules can be synchronized through Timer C, channels 2 and 3

- Quadrature Decoder:

- In the 56F8347, two four-input Quadrature Decoders or two additional Quad Timers

- In the 56F8147, one four-input Quadrature Decoder, which works in conjunction with Quad Timer A

- Temperature Sensor diode can be connected, on the board, to any of the ADC inputs to monitor the on-chip temperature

- Quad Timer:

- In the 56F8347, four dedicated general-purpose Quad Timers totaling six dedicated pins: Timer C with two pins and Timer D with four pins

- In the 56F8147, two general-purpose Quad Timers; Timer A works in conjunction with Quadrature Decoder 0 or GPIO and Timer C works in conjunction with GPIO

- FlexCAN (CAN Version 2.0 B-compliant) module with 2-pin port for transmit and receive

#### **To/From IPBus Bridge** Interrupt **CLKGEN** Controller (OSC/PLL) Low-Voltage Interrupt Timer A POR & LVI System POR Quadrature Decoder 0 RESET SIM Timer D COP Reset Timer B COP **FlexCAN** Quadrature Decoder 1 SPI 1 **PWMA** SYNC Output **GPIOA PWMB GPIOB** SYNC Output **GPIOC** ch3i ch2i Timer C **GPIOD** ch3o ch2o **GPIOE GPIOF ADCB** SPI0 **ADCA** SCI0 TEMP\_SENSE SCI1 Note: ADCA and ADCB use the same voltage reference circuit with $\rm V_{REFH}, \ V_{REFP}$ $\rm V_{REFMID}, \ V_{REFN}, \ and \ V_{REFLO} \ pins.$ NOT available on the 56F8147 device. **IPBus**

Figure 1-2 Peripheral Subsystem

Table 2-2 Signal and Package Information for the 160-Pin LQFP and MBGA (Continued)

| Signal Name         | Pin<br>No. | Ball<br>No. | Туре                     | State<br>During<br>Reset                                      | Signal Description                                                                                                                           |

|---------------------|------------|-------------|--------------------------|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| ISB0                | 61         | N8          | Schmitt<br>Input         | Input,<br>pull-up<br>enabled                                  | ISB0 - 2 — These three input current status pins are used for top/bottom pulse width correction in complementary channel operation for PWMB. |

| (GPIOD10)           |            |             | Schmitt                  |                                                               | Port D GPIO — These GPIO pins can be individually                                                                                            |

| ISB1<br>(GPIOD11)   | 63         | L8          | Output                   |                                                               | At reset, these pins default to ISB functionality.                                                                                           |

| ISB2<br>(GPIOD12)   | 64         | P8          |                          |                                                               | To deactivate the internal pull-up resistor, clear the appropriate bit of the GPIOD_PUR register. For details, see Part 6.5.8.               |

| FAULTB0             | 67         | N9          | Schmitt                  | Input,                                                        | FAULTB0 - 3 — These four fault input pins are used for                                                                                       |

| FAULTB1             | 68         | L9          | Input pull-up<br>enabled |                                                               | disabling selected PWMB outputs in cases where fault conditions originate off-chip.                                                          |

| FAULTB2             | 69         | L10         |                          | To deactivate the internal pull-up resistor, set the PWMB bit |                                                                                                                                              |

| FAULTB3             | 72         | P11         |                          |                                                               | in the SIM_PUDR register. For details, see Part 6.5.8.                                                                                       |

| ANA0                | 100        | G13         | Input                    | Analog                                                        | ANA0 - 3 — Analog inputs to ADC A, channel 0                                                                                                 |

| ANA1                | 101        | H13         |                          | Input                                                         |                                                                                                                                              |

| ANA2                | 102        | G12         |                          |                                                               |                                                                                                                                              |

| ANA3                | 103        | F13         |                          |                                                               |                                                                                                                                              |

| ANA4                | 104        | F12         | Input                    | Analog                                                        | ANA4 - 7 — Analog inputs to ADC A, channel 1                                                                                                 |

| ANA5                | 105        | H14         |                          | Input                                                         |                                                                                                                                              |

| ANA6                | 106        | G14         |                          |                                                               |                                                                                                                                              |

| ANA7                | 107        | E13         |                          |                                                               |                                                                                                                                              |

| V <sub>REFH</sub>   | 113        | D14         | Input                    | Analog<br>Input                                               | <b>V</b> <sub>REFH</sub> — Analog Reference Voltage High. V <sub>REFH</sub> must be less than or equal to V <sub>DDA_ADC</sub> .             |

| V <sub>REFP</sub>   | 112        | D13         | Input/                   | Input/ Analog<br>Output Input/<br>Output                      | V <sub>REFP</sub> , V <sub>REFMID</sub> & V <sub>REFN</sub> — Internal pins for voltage                                                      |

| V <sub>REFMID</sub> | 111        | E14         | Output                   |                                                               | reference which are brought off-chip so they can be bypassed. Connect to a 0.1μF low ESR capacitor.                                          |

| V <sub>REFN</sub>   | 110        | F14         |                          |                                                               |                                                                                                                                              |

| V <sub>REFLO</sub>  | 109        | E12         | Input                    | Analog<br>Input                                               | V <sub>REFLO</sub> — Analog Reference Voltage Low. This should normally be connected to a low-noise V <sub>SS</sub> .                        |

| Table 4-5 Interrupt Vector Table Contents <sup>1</sup> (Continued | Table 4-5 Interru | pt Vector Table | Contents <sup>1</sup> | (Continued |

|-------------------------------------------------------------------|-------------------|-----------------|-----------------------|------------|

|-------------------------------------------------------------------|-------------------|-----------------|-----------------------|------------|

| Peripheral | Vector<br>Number | Priority<br>Level | Vector Base<br>Address + | Interrupt Function                      |

|------------|------------------|-------------------|--------------------------|-----------------------------------------|

| SCI0       | 68               | 0-2               | P:\$88                   | SCI 0 Transmitter Empty                 |

| SCI0       | 69               | 0-2               | P:\$8A                   | SCI 0 Transmitter Idle                  |

|            |                  |                   |                          | Reserved                                |

| SCI0       | 71               | 0-2               | P:\$8E                   | SCI 0 Receiver Error                    |

| SCI0       | 72               | 0-2               | P:\$90                   | SCI 0 Receiver Full                     |

| ADCB       | 73               | 0-2               | P:\$92                   | ADC B Conversion Compete / End of Scan  |

| ADCA       | 74               | 0-2               | P:\$94                   | ADC A Conversion Complete / End of Scan |

| ADCB       | 75               | 0-2               | P:\$96                   | ADC B Zero Crossing or Limit Error      |

| ADCA       | 76               | 0-2               | P:\$98                   | ADC A Zero Crossing or Limit Error      |

| PWMB       | 77               | 0-2               | P:\$9A                   | Reload PWM B                            |

| PWMA       | 78               | 0-2               | P:\$9C                   | Reload PWM A                            |

| PWMB       | 79               | 0-2               | P:\$9E                   | PWM B Fault                             |

| PWMA       | 80               | 0-2               | P:\$A0                   | PWM A Fault                             |

| core       | 81               | - 1               | P:\$A2                   | SW Interrupt LP                         |

<sup>1.</sup> Two words are allocated for each entry in the vector table. This does not allow the full address range to be referenced from the vector table, providing only 19 bits of address.

## 4.4 Data Map

**Note:** Data Flash is NOT available on the 56F8147 device.

## Table 4-6 Data Memory Map<sup>1</sup>

| Begin/End<br>Address       | EX = 0 <sup>2</sup>                             | EX = 1                                          |

|----------------------------|-------------------------------------------------|-------------------------------------------------|

| X:\$FF FFFF<br>X:\$FF 0000 | EOnCE<br>256 locations allocated                | EOnCE<br>256 locations allocated                |

| X:\$FF FEFF<br>X:\$01 0000 | External Memory                                 | External Memory                                 |

| X:\$00 FFFF<br>X:\$00 F000 | On-Chip Peripherals<br>4096 locations allocated | On-Chip Peripherals<br>4096 locations allocated |

| X:\$00 EFFF<br>X:\$00 2000 | External Memory                                 | External Memory                                 |

| X:\$00 1FFF<br>X:\$00 1000 | On-Chip Data Flash<br>8KB                       |                                                 |

| X:\$00 0FFF<br>X:\$00 0000 | On-Chip Data RAM<br>8KB <sup>3</sup>            |                                                 |

<sup>1.</sup> All addresses are 16-bit Word addresses, not byte addresses.

#### 56F8347 Technical Data, Rev.11

<sup>2.</sup> If the VBA is set to 0200 (or VBA = 0000 for Mode 1, EMI\_MODE = 0), the first two locations of the vector table are the chip reset addresses; therefore, these locations are not interrupt vectors.

<sup>2.</sup> In the Operating Mode Register (OMR).

<sup>3.</sup> The Data RAM is organized as a 2K x 32-bit memory to allow single-cycle long-word operations.

## Table 4-14 Quad Timer D Registers Address Map (Continued) (TMRD\_BASE = \$00 F100) Quad Timer D is NOT available in the 56F8147 device

| Register Acronym | Address Offset | Register Description                   |

|------------------|----------------|----------------------------------------|

| TMRD2_CMPLD1     | \$28           | Comparator Load Register 1             |

| TMRD2_CMPLD2     | \$29           | Comparator Load Register 2             |

| TMRD2_COMSCR     | \$2A           | Comparator Status and Control Register |

|                  |                | Reserved                               |

| TMRD3_CMP1       | \$30           | Compare Register 1                     |

| TMRD3_CMP2       | \$31           | Compare Register 2                     |

| TMRD3_CAP        | \$32           | Capture Register                       |

| TMRD3_LOAD       | \$33           | Load Register                          |

| TMRD3_HOLD       | \$34           | Hold Register                          |

| TMRD3_CNTR       | \$35           | Counter Register                       |

| TMRD3_CTRL       | \$36           | Control Register                       |

| TMRD3_SCR        | \$37           | Status and Control Register            |

| TMRD3_CMPLD1     | \$38           | Comparator Load Register 1             |

| TMRD3_CMPLD2     | \$39           | Comparator Load Register 2             |

| TMRD3_COMSCR     | \$3A           | Comparator Status and Control Register |

## Table 4-15 Pulse Width Modulator A Registers Address Map (PWMA\_BASE = \$00 F140) PWMA is NOT available in the 56F8147 device

| Register Acronym | Address Offset | Register Description              |

|------------------|----------------|-----------------------------------|

| PWMA_PMCTL       | \$0            | Control Register                  |

| PWMA_PMFCTL      | \$1            | Fault Control Register            |

| PWMA_PMFSA       | \$2            | Fault Status Acknowledge Register |

| PWMA_PMOUT       | \$3            | Output Control Register           |

| PWMA_PMCNT       | \$4            | Counter Register                  |

| PWMA_PWMCM       | \$5            | Counter Modulo Register           |

| PWMA_PWMVAL0     | \$6            | Value Register 0                  |

| PWMA_PWMVAL1     | \$7            | Value Register 1                  |

| PWMA_PWMVAL2     | \$8            | Value Register 2                  |

| PWMA_PWMVAL3     | \$9            | Value Register 3                  |

| PWMA_PWMVAL4     | \$A            | Value Register 4                  |

| PWMA_PWMVAL5     | \$B            | Value Register 5                  |

| PWMA_PMDEADTM    | \$C            | Dead Time Register                |

Table 4-20 Analog-to-Digital Converter Registers Address Map (Continued) (ADCA\_BASE = \$00 F200)

| Register Acronym | Address Offset | Register Description     |

|------------------|----------------|--------------------------|

| ADCA_OFS 5       | \$26           | Offset Register 5        |

| ADCA_OFS 6       | \$27           | Offset Register 6        |

| ADCA_OFS 7       | \$28           | Offset Register 7        |

| ADCA_POWER       | \$29           | Power Control Register   |

| ADCA_CAL         | \$2A           | ADC Calibration Register |

Table 4-21 Analog-to-Digital Converter Registers Address Map (ADCB\_BASE = \$00 F240)

| Register Acronym | Address Offset | Register Description           |

|------------------|----------------|--------------------------------|

| ADCB_CR 1        | \$0            | Control Register 1             |

| ADCB_CR 2        | \$1            | Control Register 2             |

| ADCB_ZCC         | \$2            | Zero Crossing Control Register |

| ADCB_LST 1       | \$3            | Channel List Register 1        |

| ADCB_LST 2       | \$4            | Channel List Register 2        |

| ADCB_SDIS        | \$5            | Sample Disable Register        |

| ADCB_STAT        | \$6            | Status Register                |

| ADCB_LSTAT       | \$7            | Limit Status Register          |

| ADCB_ZCSTAT      | \$8            | Zero Crossing Status Register  |

| ADCB_RSLT 0      | \$9            | Result Register 0              |

| ADCB_RSLT 1      | \$A            | Result Register 1              |

| ADCB_RSLT 2      | \$B            | Result Register 2              |

| ADCB_RSLT 3      | \$C            | Result Register 3              |

| ADCB_RSLT 4      | \$D            | Result Register 4              |

| ADCB_RSLT 5      | \$E            | Result Register 5              |

| ADCB_RSLT 6      | \$F            | Result Register 6              |

| ADCB_RSLT 7      | \$10           | Result Register 7              |

| ADCB_LLMT 0      | \$11           | Low Limit Register 0           |

| ADCB_LLMT 1      | \$12           | Low Limit Register 1           |

| ADCB_LLMT 2      | \$13           | Low Limit Register 2           |

| ADCB_LLMT 3      | \$14           | Low Limit Register 3           |

| ADCB_LLMT 4      | \$15           | Low Limit Register 4           |

| ADCB_LLMT 5      | \$16           | Low Limit Register 5           |

| ADCB_LLMT 6      | \$17           | Low Limit Register 6           |

| ADCB_LLMT 7      | \$18           | Low Limit Register 7           |

| ADCB_HLMT 0      | \$19           | High Limit Register 0          |

56F8347 Technical Data, Rev.11

Table 4-21 Analog-to-Digital Converter Registers Address Map (Continued) (ADCB\_BASE = \$00 F240)

| Register Acronym | Address Offset | Register Description     |

|------------------|----------------|--------------------------|

| ADCB_HLMT 1      | \$1A           | High Limit Register 1    |

| ADCB_HLMT 2      | \$1B           | High Limit Register 2    |

| ADCB_HLMT 3      | \$1C           | High Limit Register 3    |

| ADCB_HLMT 4      | \$1D           | High Limit Register 4    |

| ADCB_HLMT 5      | \$1E           | High Limit Register 5    |

| ADCB_HLMT 6      | \$1F           | High Limit Register 6    |

| ADCB_HLMT 7      | \$20           | High Limit Register 7    |

| ADCB_OFS 0       | \$21           | Offset Register 0        |

| ADCB_OFS 1       | \$22           | Offset Register 1        |

| ADCB_OFS 2       | \$23           | Offset Register 2        |

| ADCB_OFS 3       | \$24           | Offset Register 3        |

| ADCB_OFS 4       | \$25           | Offset Register 4        |

| ADCB_OFS 5       | \$26           | Offset Register 5        |

| ADCB_OFS 6       | \$27           | Offset Register 6        |

| ADCB_OFS 7       | \$28           | Offset Register 7        |

| ADCB_POWER       | \$29           | Power Control Register   |

| ADCB_CAL         | \$2A           | ADC Calibration Register |

### Table 4-22 Temperature Sensor Register Address Map (TSENSOR\_BASE = \$00 F270) Temperature Sensor is NOT available in the 56F8147 device

| Register Acronym | Address Offset | Register Description |

|------------------|----------------|----------------------|

| TSENSOR_CNTL     | \$0            | Control Register     |

## Table 4-23 Serial Communication Interface 0 Registers Address Map (SCI0\_BASE = \$00 F280)

| Register Acronym | Address Offset | Register Description |

|------------------|----------------|----------------------|

| SCI0_SCIBR       | \$0            | Baud Rate Register   |

| SCI0_SCICR       | \$1            | Control Register     |

|                  |                | Reserved             |

| SCI0_SCISR       | \$3            | Status Register      |

| SCI0_SCIDR       | \$4            | Data Register        |

# Table 4-38 FlexCAN Registers Address Map (Continued) (FC\_BASE = \$00 F800) FlexCAN is NOT available in the 56F8147 device

| Register Acronym | Address Offset | Register Description                       |

|------------------|----------------|--------------------------------------------|

| FCMB5_DATA       | \$6B           | Message Buffer 5 Data Register             |

| FCMB5_DATA       | \$6C           | Message Buffer 5 Data Register             |

| FCMB5_DATA       | \$6D           | Message Buffer 5 Data Register             |

| FCMB5_DATA       | \$6E           | Message Buffer 5 Data Register             |

|                  |                | Reserved                                   |

| FCMB6_CONTROL    | \$70           | Message Buffer 6 Control / Status Register |

| FCMB6_ID_HIGH    | \$71           | Message Buffer 6 ID High Register          |

| FCMB6_ID_LOW     | \$72           | Message Buffer 6 ID Low Register           |

| FCMB6_DATA       | \$73           | Message Buffer 6 Data Register             |

| FCMB6_DATA       | \$74           | Message Buffer 6 Data Register             |

| FCMB6_DATA       | \$75           | Message Buffer 6 Data Register             |

| FCMB6_DATA       | \$76           | Message Buffer 6 Data Register             |

|                  |                | Reserved                                   |

| FCMB7_CONTROL    | \$78           | Message Buffer 7 Control / Status Register |

| FCMB7_ID_HIGH    | \$79           | Message Buffer 7 ID High Register          |

| FCMB7_ID_LOW     | \$7A           | Message Buffer 7 ID Low Register           |

| FCMB7_DATA       | \$7B           | Message Buffer 7 Data Register             |

| FCMB7_DATA       | \$7C           | Message Buffer 7 Data Register             |

| FCMB7_DATA       | \$7D           | Message Buffer 7 Data Register             |

| FCMB7_DATA       | \$7E           | Message Buffer 7 Data Register             |

|                  |                | Reserved                                   |

| FCMB8_CONTROL    | \$80           | Message Buffer 8 Control / Status Register |

| FCMB8_ID_HIGH    | \$81           | Message Buffer 8 ID High Register          |

| FCMB8_ID_LOW     | \$82           | Message Buffer 8 ID Low Register           |

| FCMB8_DATA       | \$83           | Message Buffer 8 Data Register             |

| FCMB8_DATA       | \$84           | Message Buffer 8 Data Register             |

| FCMB8_DATA       | \$85           | Message Buffer 8 Data Register             |

| FCMB8_DATA       | \$86           | Message Buffer 8 Data Register             |

|                  |                | Reserved                                   |

| FCMB9_CONTROL    | \$88           | Message Buffer 9 Control / Status Register |

| FCMB9_ID_HIGH    | \$89           | Message Buffer 9 ID High Register          |

| FCMB9_ID_LOW     | \$8A           | Message Buffer 9 ID Low Register           |

|                              |                                     | •                                     |  |  |  |

|------------------------------|-------------------------------------|---------------------------------------|--|--|--|

| IPIC_LEVEL[1:0] <sup>1</sup> | Current Interrupt Priority<br>Level | Required Nested<br>Exception Priority |  |  |  |

| 00                           | No Interrupt or SWILP               | Priorities 0, 1, 2, 3                 |  |  |  |

| 01                           | Priority 0                          | Priorities 1, 2, 3                    |  |  |  |

| 01                           | Priority 1                          | Priorities 2, 3                       |  |  |  |

| 11                           | Priorities 2 or 3                   | Priority 3                            |  |  |  |

**Table 5-2. Interrupt Priority Encoding**

### 5.3.3 Fast Interrupt Handling

Fast interrupts are described in the **DSP56800E Reference Manual**. The interrupt controller recognizes fast interrupts before the core does.

A fast interrupt is defined (to the ITCN) by:

- 1. Setting the priority of the interrupt as level 2, with the appropriate field in the IPR registers

- 2. Setting the FIMn register to the appropriate vector number

- 3. Setting the FIVALn and FIVAHn registers with the address of the code for the fast interrupt

When an interrupt occurs, its vector number is compared with the FIM0 and FIM1 register values. If a match occurs, and it is a level 2 interrupt, the ITCN handles it as a fast interrupt. The ITCN takes the vector address from the appropriate FIVALn and FIVAHn registers, instead of generating an address that is an offset from the VBA

The core then fetches the instruction from the indicated vector adddress and if it is not a JSR, the core starts its fast interrupt handling.

<sup>1.</sup> See IPIC field definition in Part 5.6.30.2

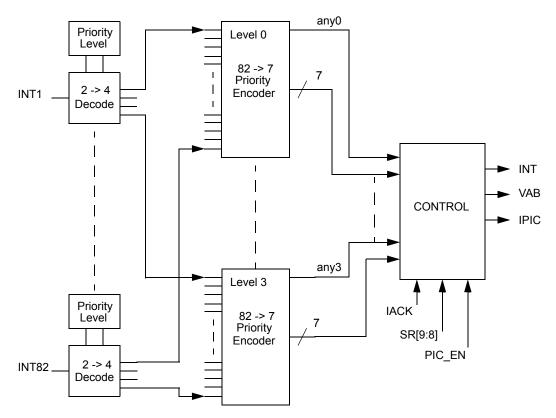

## 5.4 Block Diagram

Figure 5-1 Interrupt Controller Block Diagram

## 5.5 Operating Modes

The ITCN module design contains two major modes of operation:

#### Functional Mode

The ITCN is in this mode by default.

#### Wait and Stop Modes

During Wait and Stop modes, the system clocks and the 56800E core are turned off. The ITCN will signal a pending IRQ to the System Integration Module (SIM) to restart the clocks and service the IRQ. An IRQ can only wake up the core if the IRQ is enabled prior to entering the Wait or Stop mode. Also, the IRQA and IRQB signals automatically become low-level sensitive in these modes even if the control register bits are set to make them falling-edge sensitive. This is because there is no clock available to detect the falling edge.

A peripheral which requires a clock to generate interrupts will not be able to generate interrupts during Stop mode. The FlexCAN module can wake the device from Stop mode, and a reset will do just that, or IRQA and IRQB can wake it up.

#### 5.6.17.1 Reserved—Bits 15-5

This bit field is reserved or not implemented. It is read as 0 and cannot be modified by writing.

#### 5.6.17.2 Fast Interrupt 1 Vector Address High (FIVAH1)—Bits 4–0

The upper five bits of the vector address are used for Fast Interrupt 1. This register is combined with FIVAL1 to form the 21-bit vector address for Fast Interrupt 1 defined in the FIM1 register.

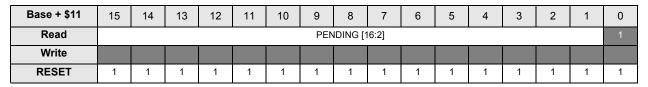

## 5.6.18 IRQ Pending 0 Register (IRQP0)

Figure 5-20 IRQ Pending 0 Register (IRQP0)

#### 5.6.18.1 IRQ Pending (PENDING)—Bits 16-2

This register combines with the other five to represent the pending IRQs for interrupt vector numbers 2 through 81.

- 0 = IRQ pending for this vector number

- 1 = No IRQ pending for this vector number

#### 5.6.18.2 Reserved—Bit 0

This bit is reserved or not implemented. It is read as 1 and cannot be modified by writing.

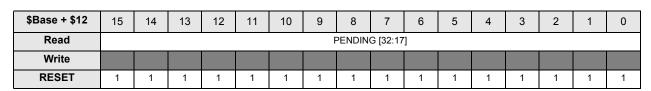

## 5.6.19 IRQ Pending 1 Register (IRQP1)

Figure 5-21 IRQ Pending 1 Register (IRQP1)

## 5.6.19.1 IRQ Pending (PENDING)—Bits 32–17

This register combines with the other five to represent the pending IRQs for interrupt vector numbers 2 through 81.

- 0 = IRQ pending for this vector number

- 1 = No IRQ pending for this vector number

## 6.3 Operating Modes

Since the SIM is responsible for distributing clocks and resets across the chip, it must understand the various chip operating modes and take appropriate action. These are:

- **Reset Mode,** which has two submodes:

- POR and RESET operation

The 56800E core and all peripherals are reset. This occurs when the internal POR is asserted or the RESET pin is asserted.

- COP reset and software reset operation

The 56800E core and all peripherals are reset. The MA bit within the OMR is not changed. This allows the software to determine the boot mode (internal or external boot) to be used on the next reset.

#### Run Mode

This is the primary mode of operation for this device. In this mode, the 56800E controls chip operation.

#### Debug Mode

The 56800E is controlled via JTAG/EOnCE when in debug mode. All peripherals, except the COP and PWMs, continue to run. COP is disabled and PWM outputs are optionally switched off to disable any motor from being driven; see the PWM chapter in the **56F8300 Peripheral User Manual** for details.

#### Wait Mode

In Wait mode, the core clock and memory clocks are disabled. Optionally, the COP can be stopped. Similarly, it is an option to switch off PWM outputs to disable any motor from being driven. All other peripherals continue to run.

#### Stop Mode

When in Stop mode, the 56800E core, memory, and most peripheral clocks are shut down. Optionally, the COP and CAN can be stopped. For lowest power consumption in Stop mode, the PLL can be shut down. This must be done explicitly before entering Stop mode, since there is no automatic mechanism for this. The CAN (along with any non-gated interrupt) is capable of waking the chip up from Stop mode, but is not fully functional in Stop mode.

## 6.4 Operating Mode Register

| Bit   | 15  | 14 | 13 | 12 | 11 | 10 | 9 | 8   | 7   | 6   | 5   | 4   | 3   | 2 | 1   | 0   |

|-------|-----|----|----|----|----|----|---|-----|-----|-----|-----|-----|-----|---|-----|-----|

|       | NL  |    |    |    |    |    |   | CM  | XP  | SD  | R   | SA  | EX  | 0 | MB  | MA  |

| Type  | R/W |    |    |    |    |    |   | R/W | R/W | R/W | R/W | R/W | R/W |   | R/W | R/W |

| RESET | 0   | 0  | 0  | 0  | 0  | 0  | 0 | 0   | 0   | 0   | 0   | 0   | 0   | 0 | Х   | Х   |

Figure 6-1 OMR

The reset state for MB and MA will depend on the Flash secured state. See Part 4.2 and Part 7 for detailed information on how the Operating Mode Register (OMR) MA and MB bits operate in this device. For all other bits, see the **DSP56800E Reference Manual**.

**Note:** The OMR is not a Memory Map register; it is directly accessible in code through the acronym OMR.

#### 6.5.1.2 EMI MODE (EMI MODE)—Bit 6

This bit reflects the current (non-clocked) state of the EMI\_MODE pin. During reset, this bit, coupled with the EXTBOOT signal, is used to initialize address bits [19:16] either as GPIO or as address. These settings can be explicitly overwritten using the appropriate GPIO peripheral enable register at any time after reset. In addition, this pin can be used as a general purpose input pin after reset.

- 0 = External address bits [19:16] are initially programmed as GPIO

- 1 = When booted with EXTBOOT = 1, A[19:16] are initially programmed as address. If EXTBOOT is 0, they are initialized as GPIO.

#### 6.5.1.3 OnCE Enable (OnCE EBL)—Bit 5

- 0 = OnCE clock to 56800E core enabled when core TAP is enabled

- 1 = OnCE clock to 56800E core is always enabled

#### 6.5.1.4 Software Reset (SW RST)—Bit 4

This bit is always read as 0. Writing a 1 to this bit will cause the part to reset.

#### 6.5.1.5 Stop Disable (STOP\_DISABLE)—Bits 3–2

- 00 Stop mode will be entered when the 56800E core executes a STOP instruction

- 01 The 56800E STOP instruction will not cause entry into Stop mode; STOP\_DISABLE can be reprogrammed in the future

- 10 The 56800E STOP instruction will not cause entry into Stop mode; STOP\_DISABLE can then only be changed by resetting the device

- 11 Same operation as 10

## 6.5.1.6 Wait Disable (WAIT\_DISABLE)—Bits 1–0

- 00 Wait mode will be entered when the 56800E core executes a WAIT instruction

- 01 The 56800E WAIT instruction will not cause entry into Wait mode; WAIT\_DISABLE can be reprogrammed in the future

- 10 The 56800E WAIT instruction will not cause entry into Wait mode; WAIT\_DISABLE can then only be changed by resetting the device

- 11 Same operation as 10

## 6.5.2 SIM Reset Status Register (SIM\_RSTSTS)

Bits in this register are set upon any system reset and are initialized only by a Power-On Reset (POR). A reset (other than POR) will only set bits in the register; bits are not cleared. Only software should only clear this register.

| Base + \$1 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5   | 4      | 3     | 2     | 1   | 0 |   |

|------------|----|----|----|----|----|----|---|---|---|---|-----|--------|-------|-------|-----|---|---|

| Read       | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | SWR | R COPR | COPP  | EXTR  | POR | 0 | 0 |

| Write      |    |    |    |    |    |    |   |   |   |   |     |        | LXIIX | 1 OIX |     |   |   |

| RESET      | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 |     |        |       |       | 0   | 0 |   |

Figure 6-4 SIM Reset Status Register (SIM RSTSTS)

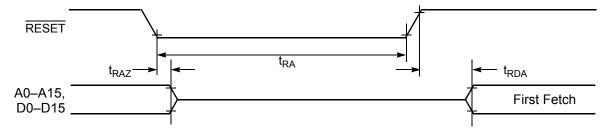

## 10.9 Reset, Stop, Wait, Mode Select, and Interrupt Timing

Table 10-17 Reset, Stop, Wait, Mode Select, and Interrupt Timing 1,2

| Characteristic                                                                                     | Symbol                  | Typical<br>Min | Typical<br>Max | Unit | See Figure |

|----------------------------------------------------------------------------------------------------|-------------------------|----------------|----------------|------|------------|

| RESET Assertion to Address, Data and Control Signals High Impedance                                | t <sub>RAZ</sub>        | _              | 21             | ns   | 10-5       |

| Minimum RESET Assertion Duration                                                                   | t <sub>RA</sub>         | 16T            | _              | ns   | 10-5       |

| RESET Deassertion to First External Address Output <sup>3</sup>                                    | t <sub>RDA</sub>        | 63T            | 64T            | ns   | 10-5       |

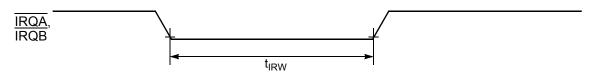

| Edge-sensitive Interrupt Request Width                                                             | t <sub>IRW</sub>        | 1.5T           | _              | ns   | 10-6       |

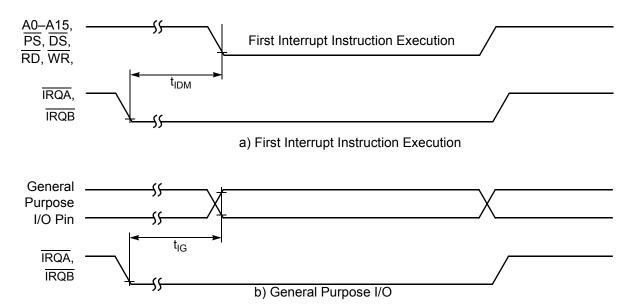

| IRQA, IRQB Assertion to External Data Memory Access Out Valid, caused by first instruction         | t <sub>IDM</sub>        | 18T            | _              | ns   | 10-7       |

| execution in the interrupt service routine                                                         | t <sub>IDM - FAST</sub> | 14T            | _              |      |            |

| IRQA, IRQB Assertion to General Purpose Output Valid, caused by first instruction execution in the | t <sub>IG</sub>         | 18T            | _              | ns   | 10-7       |

| interrupt service routine                                                                          | t <sub>IG - FAST</sub>  | 14T            | _              |      |            |

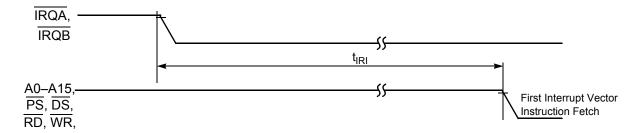

| Delay from IRQA Assertion (exiting Wait) to External Data Memory Access <sup>4</sup>               | t <sub>IRI</sub>        | 22T            | _              | ns   | 10-8       |

| External Data Memory Access                                                                        | t <sub>IRI -FAST</sub>  | 18T            | _              |      |            |

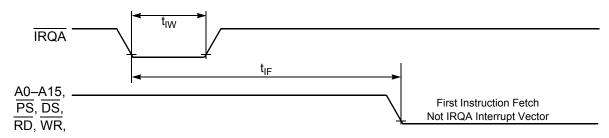

| Delay from IRQA Assertion to External Data Memory Access (exiting Stop)                            | t <sub>IF</sub>         | 22T            | _              | ns   | 10-9       |

|                                                                                                    | t <sub>IF - FAST</sub>  | 18T            | _              |      |            |

| IRQA Width Assertion to Recover from Stop<br>State <sup>5</sup>                                    | t <sub>IW</sub>         | 1.5T           | _              | ns   | 10-9       |

<sup>1.</sup> In the formulas, T = clock cycle. For an operating frequency of 60MHz, T = 16.67ns. At 8MHz (used during Reset and Stop modes), T = 125ns.

<sup>2.</sup> Parameters listed are guaranteed by design.

<sup>3.</sup> During Power-On Reset, it is possible to use the device's internal reset stretching circuitry to extend this period to  $2^{21}T$ .

<sup>4.</sup> The minimum is specified for the duration of <u>an edge</u>-sensitive <u>IRQA</u> interrupt required to recover from the Stop state. This is not the minimum required so that the <u>IRQA</u> interrupt is accepted.

<sup>5.</sup> The interrupt instruction fetch is visible on the pins only in Mode 3.

Figure 10-5 Asynchronous Reset Timing

Figure 10-6 External Interrupt Timing (Negative-Edge Sensitive)

Figure 10-7 External Level-Sensitive Interrupt Timing

Figure 10-8 Interrupt from Wait State Timing

Figure 10-9 Recovery from Stop State Using Asynchronous Interrupt Timing

## 10.10 Serial Peripheral Interface (SPI) Timing

Table 10-18 SPI Timing<sup>1</sup>

| Characteristic                           | Symbol           | Min        | Max    | Unit     | See Figure                    |

|------------------------------------------|------------------|------------|--------|----------|-------------------------------|

| Cycle time<br>Master<br>Slave            | t <sub>C</sub>   | 50<br>50   | _      | ns<br>ns | 10-10, 10-11,<br>10-12, 10-13 |

| Enable lead time<br>Master<br>Slave      | t <sub>ELD</sub> | <br>25     |        | ns<br>ns | 10-13                         |

| Enable lag time<br>Master<br>Slave       | t <sub>ELG</sub> | <br>100    | _      | ns<br>ns | 10-13                         |

| Clock (SCK) high time<br>Master<br>Slave | t <sub>CH</sub>  | 17.6<br>25 | _<br>_ | ns<br>ns | 10-10, 10-11,<br>10-12, 10-13 |

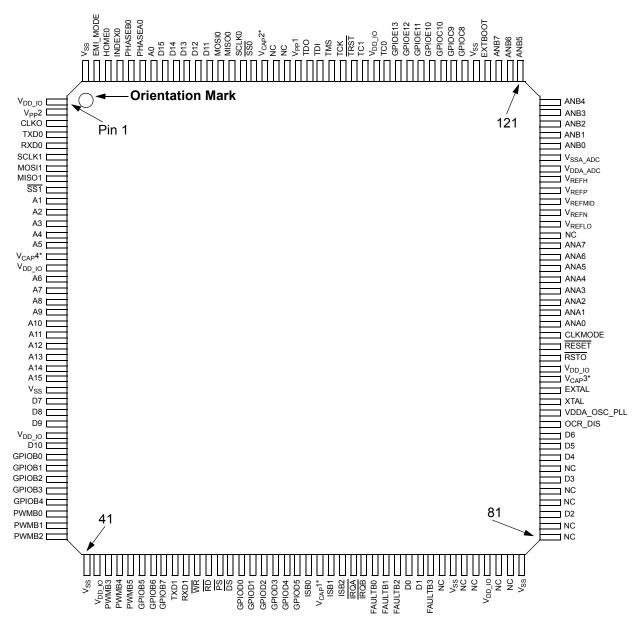

Table 11-1 56F8347 160-Pin LQFP Package Identification by Pin Number

| Pin No.   | Signal<br>Name                                                                               | Pin No. | Signal Name         | Pin No. | Signal Name              | Pin No. | Signal Name         |  |  |  |

|-----------|----------------------------------------------------------------------------------------------|---------|---------------------|---------|--------------------------|---------|---------------------|--|--|--|

| 1         | V <sub>DD_IO</sub>                                                                           | 41      | V <sub>SS</sub>     | 81      | PWMA5                    | 121     | ANB5                |  |  |  |

| 2         | V <sub>PP</sub> 2                                                                            | 42      | V <sub>DD_IO</sub>  | 82      | FAULTA0                  | 122     | ANB6                |  |  |  |

| 3         | CLKO                                                                                         | 43      | PWMB3               | 83      | D2                       | 123     | ANB7                |  |  |  |

| 4         | TXD0                                                                                         | 44      | PWMB4               | 84      | FAULTA1                  | 124     | EXTBOOT             |  |  |  |

| 5         | RXD0                                                                                         | 45      | PWMB5               | 85      | FAULTA2                  | 125     | V <sub>SS</sub>     |  |  |  |

| 6         | PHASEA1                                                                                      | 46      | GPIOB5              | 86      | D3                       | 126     | ISA0                |  |  |  |

| 7         | PHASEB1                                                                                      | 47      | GPIOB6              | 87      | FAULTA3                  | 127     | ISA1                |  |  |  |

| 8         | INDEX1                                                                                       | 48      | GPIOB7              | 88      | D4                       | 128     | ISA2                |  |  |  |

| 9         | HOME1                                                                                        | 49      | TXD1                | 89      | D5                       | 129     | TD0                 |  |  |  |

| 10        | A1                                                                                           | 50      | RXD1                | 90      | D6                       | 130     | TD1                 |  |  |  |

| 11        | A2                                                                                           | 51      | WR                  | 91      | OCR_DIS                  | 131     | TD2                 |  |  |  |

| 12        | А3                                                                                           | 52      | RD                  | 92      | V <sub>DDA_OSC_PLL</sub> | 132     | TD3                 |  |  |  |

| 13        | A4                                                                                           | 53      | PS                  | 93      | XTAL                     | 133     | TC0                 |  |  |  |

| 14        | A5                                                                                           | 54      | DS                  | 94      | EXTAL                    | 134     | V <sub>DD_IO</sub>  |  |  |  |

| 15        | V <sub>CAP</sub> 4*                                                                          | 55      | GPIOD0              | 95      | V <sub>CAP</sub> 3*      | 135     | TC1                 |  |  |  |

| 16        | V <sub>DD_IO</sub>                                                                           | 56      | GPIOD1              | 96      | V <sub>DD_IO</sub>       | 136     | TRST                |  |  |  |

| 17        | A6                                                                                           | 57      | GPIOD2              | 97      | RSTO                     | 137     | TCK                 |  |  |  |

| 18        | A7                                                                                           | 58      | GPIOD3              | 98      | RESET                    | 138     | TMS                 |  |  |  |

| 19        | A8                                                                                           | 59      | GPIOD4              | 99      | CLKMODE                  | 139     | TDI                 |  |  |  |

| 20        | A9                                                                                           | 60      | GPIOD5              | 100     | ANA0                     | 140     | TDO                 |  |  |  |

| 21        | A10                                                                                          | 61      | ISB0                | 101     | ANA1                     | 141     | V <sub>PP</sub> 1   |  |  |  |

| 22        | A11                                                                                          | 62      | V <sub>CAP</sub> 1* | 102     | ANA2                     | 142     | CAN_TX              |  |  |  |

| 23        | A12                                                                                          | 63      | ISB1                | 103     | ANA3                     | 143     | CAN_RX              |  |  |  |

| 24        | A13                                                                                          | 64      | ISB2                | 104     | ANA4                     | 144     | V <sub>CAP</sub> 2* |  |  |  |

| 25        | A14                                                                                          | 65      | ĪRQA                | 105     | ANA5                     | 145     | SS0                 |  |  |  |

| * When th | * When the on-chip regulator is disabled, these four pins become 2.5V V <sub>DD CORE</sub> . |         |                     |         |                          |         |                     |  |  |  |

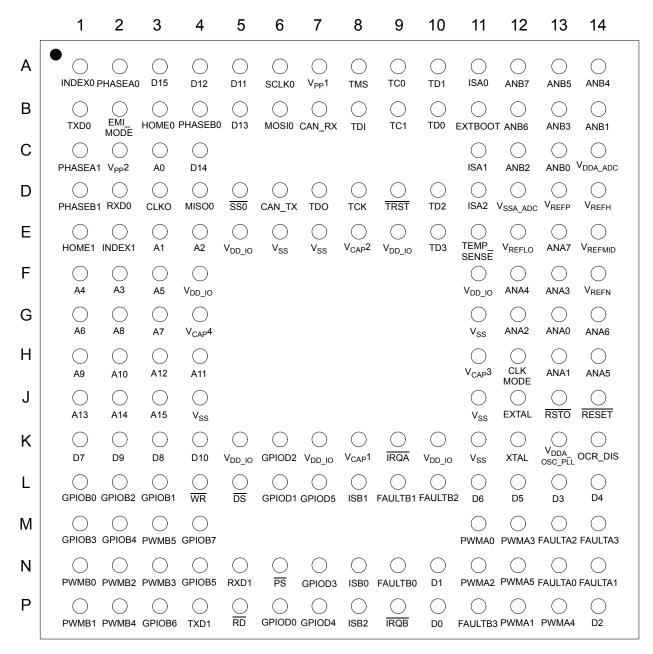

Figure 11-2 Top View, 56F8347 160-Pin MAPBGA Package

Table 11-2 56F8347 -160 MAPBGA Package Identification by Pin Number

| Ball<br>No. | Signal Name         | Ball<br>No. | Signal Name         | Ball<br>No. | Signal Name              | Ball<br>No. | Signal Name         |

|-------------|---------------------|-------------|---------------------|-------------|--------------------------|-------------|---------------------|

| F4          | V <sub>DD_IO</sub>  | K11         | V <sub>SS</sub>     | N12         | PWMA5                    | A13         | ANB5                |

| C2          | V <sub>PP</sub> 2   | K7          | V <sub>DD_IO</sub>  | N13         | FAULTA0                  | B12         | ANB6                |

| D3          | CLKO                | N3          | PWMB3               | P14         | D2                       | A12         | ANB7                |

| B1          | TXD0                | P2          | PWMB4               | N14         | FAULTA1                  | B11         | EXTBOOT             |

| D2          | RXD0                | МЗ          | PWMB5               | M13         | FAULTA2                  | J11         | V <sub>SS</sub>     |

| C1          | PHASEA1             | N4          | GPIOB5              | L13         | D3                       | A11         | ISA0                |

| D1          | PHASEB1             | P3          | GPIOB6              | M14         | FAULTA3                  | C11         | ISA1                |

| E2          | INDEX1              | M4          | GPIOB7              | L14         | D4                       | D11         | ISA2                |

| E1          | HOME1               | P4          | TXD1                | L12         | D5                       | B10         | TD0                 |

| E3          | A1                  | N5          | RXD1                | L11         | D6                       | A10         | TD1                 |

| E4          | A2                  | L4          | WR                  | K14         | OCR_DIS                  | D10         | TD2                 |

| F2          | A3                  | P5          | RD                  | K13         | V <sub>DDA_OSC_PLL</sub> | E10         | TD3                 |

| F1          | A4                  | N6          | PS                  | K12         | XTAL                     | A9          | TC0                 |

| F3          | A5                  | L5          | DS                  | J12         | EXTAL                    | F11         | V <sub>DD_IO</sub>  |

| G4          | V <sub>CAP</sub> 4* | P6          | GPIOD0              | H11         | V <sub>CAP</sub> 3*      | В9          | TC1                 |

| K5          | V <sub>DD_IO</sub>  | L6          | GPIOD1              | K10         | V <sub>DD_IO</sub>       | D9          | TRST                |

| G1          | A6                  | K6          | GPIOD2              | J13         | RSTO                     | D8          | тск                 |

| G3          | A7                  | N7          | GPIOD3              | J14         | RESET                    | A8          | TMS                 |

| G2          | A8                  | P7          | GPIOD4              | H12         | CLKMODE                  | В8          | TDI                 |

| H1          | A9                  | L7          | GPIOD5              | G13         | ANA0                     | D7          | TDO                 |

| H2          | A10                 | N8          | ISB0                | H13         | ANA1                     | A7          | V <sub>PP</sub> 1   |

| H4          | A11                 | K8          | V <sub>CAP</sub> 1* | G12         | ANA2                     | D6          | CAN_TX              |

| НЗ          | A12                 | L8          | ISB1                | F13         | ANA3                     | В7          | CAN_RX              |

| J1          | A13                 | P8          | ISB2                | F12         | ANA4                     | E8          | V <sub>CAP</sub> 2* |

| J2          | A14                 | K9          | ĪRQA                | H14         | ANA5                     | D5          | SS0                 |

$<sup>^{\</sup>star}$  When the on-chip regulator is disabled, these four pins become 2.5V  $\rm V_{DD\_CORE}.$

## 11.2 56F8147 Package and Pin-Out Information

This section contains package and pin-out information for the 56F8147. This device comes in a 160-pin Low-profile Quad Flat Pack (LQFP). **Figure 11-4** shows the package outline for the 160-pin LQFP, **Figure 11-5** shows the mechanical parameters for this package, and **Table 11-1** lists the pin-out for the 160-pin LQFP.

$<sup>^{\</sup>star}$  When the on-chip regulator is disabled, these four pins become 2.5V V<sub>DD CORE</sub>

Figure 11-4 Top View, 56F8147 160-Pin LQFP Package