# E·XFL

Welcome to E-XFL.COM

Embedded - Microcontrollers - Application Specific: Tailored Solutions for Precision and Performance

#### Embedded - Microcontrollers - Application Specific

represents a category of microcontrollers designed with unique features and capabilities tailored to specific application needs. Unlike general-purpose microcontrollers, application-specific microcontrollers are optimized for particular tasks, offering enhanced performance, efficiency, and functionality to meet the demands of specialized applications.

#### What Are <u>Embedded - Microcontrollers -</u> <u>Application Specific</u>?

Application enacific microcontrollars are angineered to

#### Details

| 2 0 0 0 0 0             |                                                                      |

|-------------------------|----------------------------------------------------------------------|

| Product Status          | Obsolete                                                             |

| Applications            | Automotive                                                           |

| Core Processor          | XC800                                                                |

| Program Memory Type     | FLASH (64kB)                                                         |

| Controller Series       | - ·                                                                  |

| RAM Size                | 3.25K x 8                                                            |

| Interface               | LIN, SSI, UART                                                       |

| Number of I/O           | 11                                                                   |

| Voltage - Supply        | 3V ~ 27V                                                             |

| Operating Temperature   | -40°C ~ 150°C (TJ)                                                   |

| Mounting Type           | Surface Mount                                                        |

| Package / Case          | 48-VFQFN Exposed Pad                                                 |

| Supplier Device Package | PG-VQFN-48-29                                                        |

| Purchase URL            | https://www.e-xfl.com/product-detail/infineon-technologies/tle9835qx |

|                         |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Summary of Features**

## 1.1 Device Types / Ordering Information

The TLE983x product family features devices with different peripheral modules, configurations and program memory sizes to offer cost-effective solutions for different application requirements. Table 1 describes the TLE9835QX device configuration.

#### Table 1Device Configuration

| Device Name | Max Clock<br>Frequency | High Side<br>Switches | High Voltage<br>Monitor<br>Inputs | Flash Size |    | Operational<br>Amplifier |

|-------------|------------------------|-----------------------|-----------------------------------|------------|----|--------------------------|

| TLE9835QX   | 40 MHz                 | 2                     | 5                                 | 64 kByte   | 11 | yes                      |

## TLE9835QX

**Summary of Features**

| Table 2 Acronyms |                                             |

|------------------|---------------------------------------------|

| Acronyms         | Name                                        |

| ROM              | Read Only Memory                            |

| SCK              | SSC Clock                                   |

| SFR              | Special Function Register                   |

| SOW              | Short Open Window (for WDT1)                |

| SPI              | Serial Peripheral Interface                 |

| SSC              | Synchronous Serial Channel                  |

| SSU              | System Status Unit                          |

| TMS              | Test Mode Select                            |

| UART             | Universal Asynchronous Receiver Transmitter |

| UDIG             | Universal Digital Controller for ADC1       |

| VBG              | Voltage reference Band Gap                  |

| WDT              | Watchdog timer                              |

| WMU              | Wake-up Management Unit                     |

| XRAM             | On-Chip eXternal Data Memory                |

| XSFR             | On-Chip eXternal Special Function Register  |

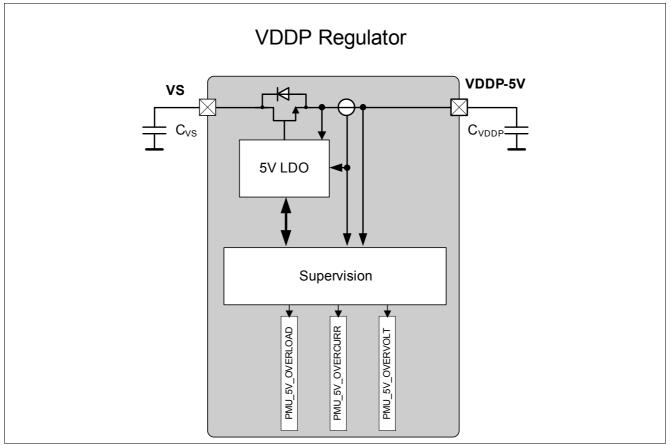

## 3.1.1 Voltage Regulator 5.0V (VDDP)

This module represents the 5 V voltage regulator, which serves as pad supply for the parallel port pins and other 5 V analog functions.

#### Features

- 5 V low-drop voltage regulator

- Current limitation

- Overcurrent monitoring and shutdown with MCU signalling (Interrupt)

- Overvoltage monitoring with MCU signalling (Interrupt)

- Undervoltage overload monitoring with MCU signalling (Interrupt)

- Preregulator for VDDC regulator

- GPIO supply

- Pull-down current source at the output for Sleep Mode (100 μA)

The output capacitor  $C_{VDDP}$  is mandatory to ensure a proper regulator functionality.

Figure 6 Module Block Diagram of VDDP Voltage Regulator

## 3.5 Flash Memory

The Flash memory provides an embedded user-programmable non-volatile memory, allowing fast and reliable storage of user code and data. It is operated from a single 1.5V supply (VDDC) from the internal voltage regulator and does not require additional programming or erasing voltage.

## Features

- · In-System Programming via LIN (Flash mode) and DAP

- Error Correction Code (ECC) for dynamic correction of single Bit errors and signalling for double Bit failures

- Support for aborting erase operation

- Program width of 128 Byte (page)

- Minimum erase width of 128 Byte (page)

- 4 Byte read access

- Read access time: 75 ns

- Program time for 1 page: 3 ms

- Page erase time: 4 ms

## 3.6 Watchdog Timer 1 (WDT1)

## Features

- Windowed Watchdog Timer with programmable timing in Active Mode

- Long open window (80ms) after power-up, reset, wake-up

- Short open window (30ms) to facilitate Flash programming

- Disabled during debugging

- Safety shutdown to Sleep Mode after 5 missed WDT1 services

There are two watchdog timers in the system. The Watchdog Timer (WDT) within the microcontroller (see **Chapter 3.7**) and the Watchdog Timer 1 (WDT1), which is described in this section.

In Active Mode, the WDT1 acts as a windowed watchdog timer, which provides a highly reliable and safe way to recover from software or hardware failures.

The WDT1 is always enabled in Active Mode. In Sleep Mode, Stop Mode and OCDS mode the WDT1 is disabled.

The behavior of the Watchdog Timer 1 in Active Mode is depicted in Figure 12.

## **TLE9835QX**

#### **Functional Description**

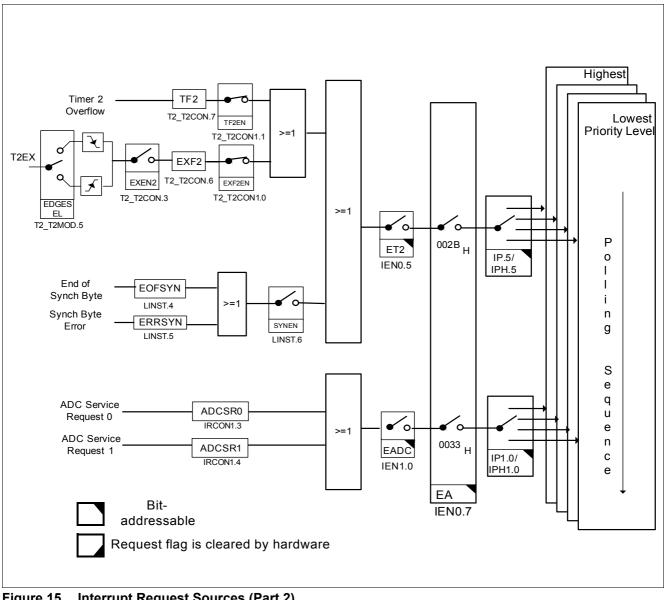

Figure 15 Interrupt Request Sources (Part 2)

## 3.13 Timer 3

Timer 3 can function as timer or counter. When functioning as a timer, Timer 3 is incremented in periods based on the system clock. When functioning as a counter, Timer 3 is incremented in response to a 1-to-0 transition (falling edge) at its respective input. Timer 3 can be configured in four different operating modes to use in a variety of applications, see Table 8.

| Mode | Sub-Mode | Operation                                                                                                                                                                                                                                                                                         |

|------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | -        | <b>13-Bit Timer</b><br>The timer is essentially an 8-Bit counter with a divide-by-32 prescaler. This mode is included solely for compatibility with Intel 8048 devices.                                                                                                                           |

| 1    | а        | <b>16-Bit Timer</b><br>The timer registers, TLx and THx, are concatenated to form a 16-Bit counter.                                                                                                                                                                                               |

| 1    | b        | <b>16-Bit Timer</b><br>The timer registers, TLx and THx, are concatenated to form a 16-Bit counter, which is triggered by the PWM Unit to enable a single shot measurement on a preset channel with the measurement unit.                                                                         |

| 1    | C        | <b>16-Bit Timer</b><br>The timer registers, TLx and THx, are concatenated to form a 16-Bit counter, which is triggered by the PWM Unit to enable the LIN Baudrate Measurement.                                                                                                                    |

| 2    | -        | <b>8-Bit Timer with Auto-reload</b><br>The timer register TLx is reloaded with a user-defined 8-Bit value in THx upon overflow.                                                                                                                                                                   |

| 3    | а        | <b>Timer 3 operates as Two 8-Bit Timers</b><br>The timer registers, TL3 and TH3, operate as two separate 8-Bit counters.                                                                                                                                                                          |

| 3    | b        | <b>Timer 3 operates as Two 8-Bit Timers</b><br>The timer registers, TL3 and TH3, operate as two separate 8-Bit counters. In this mode the 100 kHz Low Power Clock can be measured. TL3 acts as an edge counter for the clock edges and TH3 as an counter which counts the time between the edges. |

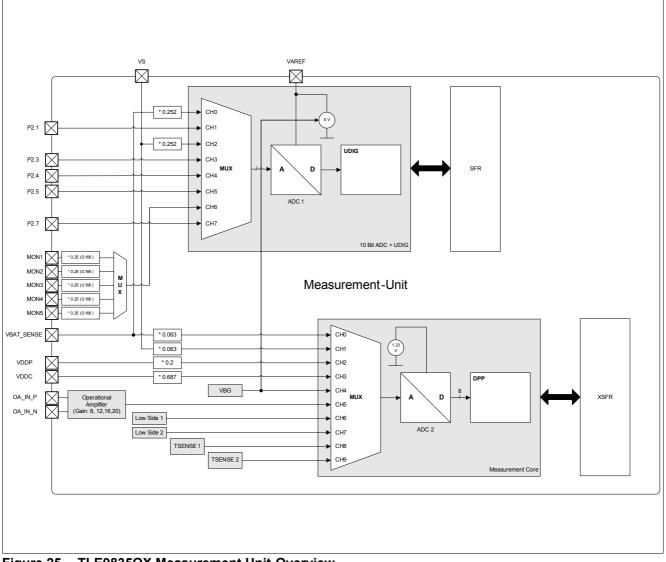

## 3.18 Measurement Unit

The measurement unit is a functional unit that comprises the following associated sub-modules:

- 1 x 8 Bit ADC (ADC2) with 10 inputs. 5 are for single ended input signals and 5 are for differential input signals.

- Monitoring inputs voltage attenuators with two selectable attenuation settings: divide by 4 and divide by 6

- Supply voltage attenuators with attenuation of VBAT\_SENSE, VS, VDDP and VDDC.

- VBG monitoring of 8-Bit ADC (ADC2) to guarantee functional safety requirements.

- Low Side Switch current sensing of LS1 and LS2. Allows a scalable overcurrent pre warning.

- Temperature sensor for monitoring the chip temperature and Low Side Switches temperature.

- Supplement block with reference voltage generation, bias current generation, voltage buffer for Flash reference voltage, voltage buffer for analog module reference voltage and test interface.

| Module<br>Name                                                       | Modules                                                                              | Functions                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Central Functions<br>Unit                                            | Bandgap reference circuit                                                            | <ul> <li>The bandgap-reference sub-module provides two reference voltages</li> <li>1. a trimmable reference voltage for the 8-Bit ADC. A local dedicated bandgap circuit is implemented to avoid deterioration of the reference voltage arising e.g. from crosstalk or ground voltage shift.</li> <li>2. the reference voltage for the Flash module</li> </ul> |

| 8-Bit ADC (ADC2)                                                     | 8-Bit ADC module with 10 multiplexed inputs                                          | <ol> <li>5 single-ended inputs 0 1.23V</li> <li>5 differential inputs 0 1.23V</li> <li>(allocation see following overview figure)</li> </ol>                                                                                                                                                                                                                   |

| 10-Bit ADC<br>(ADC1)                                                 | 10-Bit ADC module including analog<br>test bus interface - part of µC<br>subsystem   | <ol> <li>VBAT_SENSE measurement on channel 0 of ADC1.</li> <li>VS measurement on channel 2 of ADC1.</li> <li>MONx measurement on channel 6 of ADC1.</li> <li>5 additional (5V) analog inputs from Port 2.</li> </ol>                                                                                                                                           |

| Supply Voltage<br>Attenuator                                         | Resistive supply voltage attenuator                                                  | Scales down the supply voltages of the system to the input voltage range of ADC1 and ADC2.                                                                                                                                                                                                                                                                     |

| Monitoring Input<br>Attenuator                                       | Resistive attenuator for (HV)                                                        | Scales down 5 monitoring input voltages to the input voltage range of the ADC1.                                                                                                                                                                                                                                                                                |

| Central<br>Temperature -<br>Low Side Switch<br>Temperature<br>Sensor | Temperature sensor readout with two multiplexed $\Delta V_{\rm be}$ sensing elements | Generates outputs voltage which is a linear function of the local chip (junction) temperature.                                                                                                                                                                                                                                                                 |

| Measurement<br>Core Module                                           | Digital signal processing and ADC control unit                                       | <ol> <li>Generates the control signal for the 8-Bit ADC2 and the<br/>synchronous clock for the switched capacitor circuits,</li> <li>Performs digital signal processing functions and<br/>provides status outputs for interrupt generation.</li> </ol>                                                                                                         |

#### Table 10 Measurement functions and associated modules

The structure of the measurement functions module is shown in Figure 25.

## TLE9835QX

#### **Functional Description**

Figure 25 TLE9835QX Measurement Unit-Overview

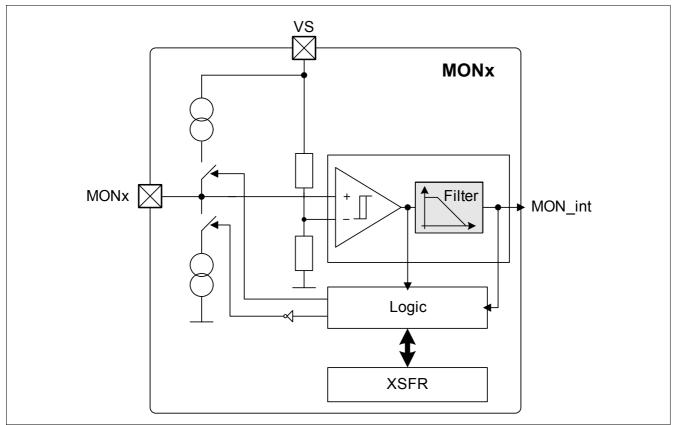

## 3.21 High Voltage Monitor Input

This module is dedicated to monitor external voltage levels above or below a specified threshold or it can be used to detect a wake-up event at each high-voltage MON\_IN pin in low-power mode. Each input is sensitive to an input level monitoring. It is available when the module is switched to Active Mode via the MON\_int (internal signal name) output with a small filter delay of typical 2 µs.

## Features

- High-voltage input with  $V_S/2$  threshold voltage

- Edge sensitive wake capability for power saving modes

- · Level sensitive wake-up feature configurable for transitions from low to high, high to low or both directions

- MON inputs can also be evaluated with ADC1 in Active Mode, using adjustable threshold values (see also Chapter 3.20).

Figure 27 Monitoring Input Block Diagram

## 4 Application Information

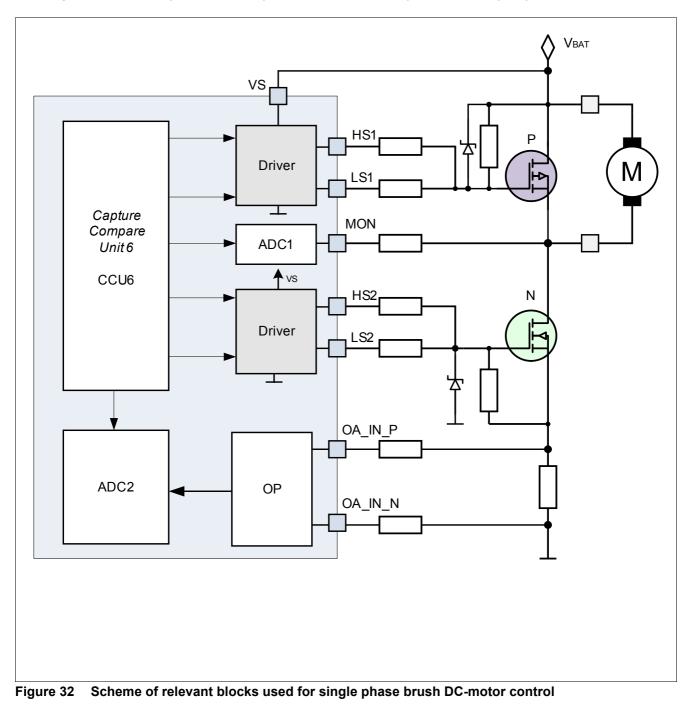

## 4.1 Motor Drive with p/n-channel MOSFET Power Half Bridge

## Note: The following information is given as a hint for the implementation of the device only and shall not be regarded as a description or warranty of a certain functionality, condition or quality of the device.

#### **Application Information**

## 4.1.1.3 MOSFET protection

For overload protection of the power MOSFET's two different options are provided by TLE9835QX:

- Current measurement by using the Operational Amplifier module<sup>1)</sup>.

- · Output voltage measurement by using the Monitor Inputs

Assuming one terminal of the motor is connected to battery the protection against short circuit to battery of the power half bridge is possible by synchronous measurment of the active current over the shunt resistor. If the current exceeds the internally selected overcurrent threshold an interrupt will be generated which can be used to disable the respective gate driver stage of the n-channel MOSFET. Furthermore it is recommended to implement a software algorithm for detection of a motor stall condition based on the measured motor current. In case of a stall condition the power half bridge has to be disabled to avoid overheating of the MOSFET's. If a Hall sensor is available the signals of the sensor can be used in the software to detect a stall condition.

## 4.1.2 Application hints

In **Figure 34** a simplified application diagram for brush-DC motor with terminal connected to battery is shown. Beside the above described functions it further includes an option to perform an output voltage monitoring using MON1 and LS2 in combination with  $R_{m2_v}$  and  $R_{m2_h}$  for pre-drive<sup>2)</sup> output monitoring. The following diagnosis functions can be executed:

- Motor connection interrupted: LS2 activated => V<sub>M</sub>~0V instead of V<sub>Bat</sub>

- Motor shorted to ground: LS2 off =>  $V_{M-}$ ~0V instead of  $V_{Bat}$

To ensure stable supply voltage condition during PWM operation a buffer capacity  $C_1$  in combination with  $C_0$  is mandatory. Both capacitors need to be placed as close as possible to the power half bridge.  $C_1$  should be dimensioned with respect to the PWM frequency as well as the allowed current and supply voltage ripple. To reduce the emission over the battery line a filter build up with an inductance  $L_1$  and  $C_2$  is required. The value of  $C_2$  should be selected roughly in the region of 10% of the  $C_1$  capacity. It is recommended to define the filter frequency of  $L_1$  and  $C_2$  to 50% of the PWM frequency. For reverse polarity protection a p-channel MOSFET provides a feasible solution.

<sup>1)</sup> This works only for shunt resistors to ground.

<sup>2)</sup> This means outputs HSx/LSx are switched off and will be enabled in a specific way for pre-drive check before starting normal operation.

## 5.2.3 VDDEXT Voltage Regulator 5.0V

## Table 21 Electrical Characteristics

$V_{\rm S}$  = 5.5 V to 27 V,  $T_{\rm j}$  = -40° C to +150 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                   | Symbol                        | Values |      |      | Unit | Note /                                                    | Number   |  |

|---------------------------------------------|-------------------------------|--------|------|------|------|-----------------------------------------------------------|----------|--|

|                                             |                               | Min.   | Тур. | Max. |      | Test Condition                                            |          |  |

| Output Current                              | I <sub>VDDEXT</sub>           | 0      | -    | 20   | mA   | 1)                                                        | P_5.2.20 |  |

| Output Capacitance                          | C <sub>VDDEXT</sub>           | 10     | -    | 1000 | nF   | <sup>1)</sup> ESR < 1 Ω                                   | P_5.2.21 |  |

| Output Voltage including line regulation    | V <sub>DDEXT</sub>            | 4.9    | 5.0  | 5.1  | V    | $I_{\rm load}$ < 20mA;Vs > 5.5V                           | P_5.2.22 |  |

| Output Drop                                 | $V_{\rm s}$ - $V_{\rm DDEXT}$ |        | -    | +400 | mV   | <sup>1)</sup> $I_{load}$ < 20mA;<br>3V < $V_{s}$ < 5.5V   | P_5.2.23 |  |

| Dynamic Load Regulation                     | V <sub>DDEXTLOR</sub>         | -50    | -    | 50   | mV   | <sup>1)</sup> 2 20mA;<br>C=10nF;<br>dl/dt=10mA/μs         | P_5.2.24 |  |

| Dynamic Line Regulation                     | V <sub>VDDEXTLIR</sub>        | -25    | -    | 25   | mV   | V <sub>s</sub> = 5.5 20V;<br>dV/dt=5V/μs                  | P_5.2.25 |  |

| Power Supply Ripple Rejection <sup>1)</sup> | P <sub>SSRVDDEXT</sub>        | 50     | -    | -    | dB   | V <sub>s</sub> = 13.5V; f=0<br>1KHz; V <sub>r</sub> =2Vpp | P_5.2.26 |  |

| Over Voltage Detection                      | V <sub>VDDEXTOV</sub>         | 5.05   | -    | 5.4  | V    | V <sub>s</sub> > 5.5V                                     | P_5.2.27 |  |

| Under Voltage Detection                     | V <sub>VDDEXTUV</sub>         | 2.6    | -    | 2.9  | V    | $^{2)}V_{\rm s}$ > 3.0V                                   | P_5.2.28 |  |

| Over Current Diagnostic                     | I <sub>VDDEXTOC</sub>         | 25     | -    | 70   | mA   | -                                                         | P_5.2.29 |  |

1) Not subject to production test, specified by design

2) When the condition is met, the Bit VDDEXT\_CTRL.VDDEXT\_SHORT will be set

## 5.3 System Clocks

## 5.3.1 Oscillators and PLL

#### Table 22 Electrical Characteristics

$V_{\rm S}$  = 5.5 V to 27 V,  $T_{\rm j}$  = -40° C to +150 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                        | Symbol                |            | Values | 6       | Unit | Note / Test Condition                                                     | Number   |  |

|----------------------------------|-----------------------|------------|--------|---------|------|---------------------------------------------------------------------------|----------|--|

|                                  |                       | Min.       | Тур.   | Max.    | 1    |                                                                           |          |  |

| PMU Oscillators (Powe            | er Manager            | nent Unit) |        |         |      |                                                                           |          |  |

| Frequency of LP_CLK              | flp_clk1              | 14         | 18     | 22      | MHz  | this clock is used at startup<br>and can be used in case the<br>PLL fails | P_5.3.1  |  |

| Frequency of LP_CLK2             | $f_{\rm LP\_CLK2}$    | 70         | 100    | 130     | kHz  | this clock is used for cyclic wake and cyclic sense                       | P_5.3.2  |  |

| CGU Oscillator (Clock            | Generatio             | n Unit Mic | rocont | roller) |      |                                                                           |          |  |

| Oscillator frequency             | $f_{\rm INTOSC}$      |            | 5      |         | MHz  |                                                                           | P_5.3.42 |  |

| Short term frequency deviation   | <i>f</i> trimst       | -0.5%      |        | +0.5%   |      | <sup>1)</sup> for duration < 5ms                                          | P_5.3.43 |  |

| Short term frequency deviation   | <i>f</i> trimst       | -1.5%      |        | +1.5%   |      | <sup>1)</sup> for duration >=5ms and<br><100ms                            | P_5.3.3  |  |

| Long term frequency deviation    | $f_{TRIMLT}$          | -3.0%      |        | +3.0%   |      | <sup>2)</sup> over lifetime and temperature                               | P_5.3.4  |  |

| CGU-OSC Start-up<br>time         | T <sub>OSC</sub>      | -          | -      | 10      | μs   | startup time OSC from Sleep<br>Mode and Stop Mode, power<br>supply stable | P_5.3.5  |  |

| PLL (Clock Generation            | Unit Micro            | ocontrolle | r)     |         | 1    |                                                                           | 1        |  |

| VCO frequency range<br>Mode 0    | fvco-0                | 48         | -      | 112     | MHz  | VCOSEL ="0"                                                               | P_5.3.6  |  |

| VCO frequency range<br>Mode 1    | f <sub>vco-1</sub>    | 96         | -      | 160     | MHz  | VCOSEL ="1"                                                               | P_5.3.7  |  |

| Input frequency range            | fosc                  | 4          | -      | 16      | MHz  | -                                                                         | P_5.3.8  |  |

| XTAL1 input freq. range          | fosc                  | 4          | -      | 16      | MHz  | -                                                                         | P_5.3.9  |  |

| Output freq. range               | $f_{PLL}$             | 0.04687    | -      | 80      | MHz  | -                                                                         | P_5.3.10 |  |

| Free-running frequency<br>Mode 0 | $f_{\rm VCOfree_0}$   | -          | -      | 38      | MHz  | VCOSEL ="0"                                                               | P_5.3.11 |  |

| Free-running frequency<br>Mode 1 | $f_{\rm VCOfree_1}$   | -          | -      | 76      | MHz  | VCOSEL ="1"                                                               | P_5.3.12 |  |

| Input clock high/low<br>time     | t <sub>high/low</sub> | 10         | -      | -       | ns   | -                                                                         | P_5.3.13 |  |

| Peak period jitter               | t <sub>jp</sub>       | -500       | _      | 500     | ps   | for K=1                                                                   | P_5.3.14 |  |

#### Table 22 Electrical Characteristics

$V_{\rm S}$  = 5.5 V to 27 V,  $T_{\rm j}$  = -40° C to +150 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter          | Symbol |      | Values | 3    | Unit | Note / Test Condition | Number   |

|--------------------|--------|------|--------|------|------|-----------------------|----------|

|                    |        | Min. | Тур.   | Max. |      |                       |          |

| Accumulated jitter | jacc   | _    | _      | 5    | ns   | for K=1               | P_5.3.15 |

| lock-in time       | TL     | -    | -      | 200  | μs   | _                     | P_5.3.16 |

1)  $V_{\text{DDC}} = 1.5 \text{ V}, T_{\text{j}} = 25^{\circ}\text{C}$

2) including short term frequency deviation

## 5.3.2 External Clock Parameters XTAL1, XTAL2

#### Table 23 Functional Range

$V_{\rm S}$  = 5.5 V to 27 V,  $T_{\rm j}$  = -40° C to +150 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                      | Symbol                |                         | Values |      | Unit | Note /                                | Number   |

|------------------------------------------------|-----------------------|-------------------------|--------|------|------|---------------------------------------|----------|

|                                                |                       | Min.                    | Тур.   | Max. |      | Test Condition                        |          |

| Input voltage range limits for signal on XTAL1 | V <sub>IX1_SR</sub>   | -1.7 + V <sub>DDC</sub> | -      | 1.7  | V    | 1)                                    | P_5.3.17 |

| Input voltage (amplitude) on XTAL1             | V <sub>AX1_SR</sub>   | 0.3 x V <sub>DDP</sub>  | -      | -    | V    | <sup>2)</sup> Peak-to-peak<br>voltage | P_5.3.18 |

| XTAL1 input current                            | I <sub>IL</sub>       | -                       | -      | ±20  | μA   | $0 V < V_{IN} < V_{DDC}$              | P_5.3.19 |

| Oscillator frequency                           | $f_{\rm OSC}$         | 4                       | -      | 24   | MHz  | Clock signal                          | P_5.3.20 |

| Oscillator frequency                           | fosc                  | 4                       | -      | 16   | MHz  | Crystal or<br>Resonator               | P_5.3.21 |

| High time                                      | <i>t</i> <sub>1</sub> | 6                       | -      | -    | ns   | -                                     | P_5.3.22 |

| Low time                                       | t <sub>2</sub>        | 6                       | -      | _    | ns   | -                                     | P_5.3.23 |

| Rise time                                      | t <sub>3</sub>        | -                       | 8      | 8    | ns   | -                                     | P_5.3.24 |

| Fall time                                      | <i>t</i> <sub>4</sub> | -                       | 8      | 8    | ns   | -                                     | P_5.3.25 |

1) Overload conditions must not occur on pin XTAL1.

2) The amplitude voltage  $V_{AX1}$  refers to the offset voltage  $V_{OFF}$ . This offset voltage must be stable during the operation and the resulting voltage peaks must remain within the limits defined by  $V_{IX1}$ .

## 5.4 Flash Parameters

This chapter includes the parameters for the 64 kByte embedded flash module.

## Table 24 Flash Characteristics <sup>1)</sup>

$V_{\rm S}$  = 5.5 V to 27 V,  $T_{\rm j}$  = -40° C to +150 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                              | Symbol           | Values |                 |      | Unit    | Note /                          | Number  |  |

|----------------------------------------|------------------|--------|-----------------|------|---------|---------------------------------|---------|--|

|                                        |                  | Min.   | Тур.            | Max. | _       | Test Condition                  |         |  |

| Programming time per 128 Byte page     | t <sub>PR</sub>  | _      | <sup>2)</sup> 3 | 3.5  | ms      | -                               | P_5.4.1 |  |

| Erase time per sector/page             | t <sub>ER</sub>  | _      | <sup>2)</sup> 4 | 4.5  | ms      | -                               | P_5.4.2 |  |

| Data retention time                    | t <sub>RET</sub> | 20     | -               | -    | years   | 1,000 erase /<br>program cycles | P_5.4.3 |  |

| Flash erase endurance for user sectors | $N_{ER}$         | 30     | -               | -    | kcycles | Data retention<br>time 5 years  | P_5.4.4 |  |

1) Not subject for production test, specified by design

2) Programming and erase times depend on the internal Flash clock source. The control state machine needs a few system clock cycles. This requirement is only relevant for extremely low system frequencies.

## 5.5 Parallel Ports (GPIO)

## 5.5.1 Functional Range

#### Table 25Functional Range

$V_{\rm S}$  = 5.5 V to 27 V,  $T_{\rm j}$  = -40° C to +150 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                        | Symbol                      |      | Values |      | Values |                | Values  |  | Unit | Note / | Number |

|----------------------------------|-----------------------------|------|--------|------|--------|----------------|---------|--|------|--------|--------|

|                                  |                             | Min. | Тур.   | Max. |        | Test Condition |         |  |      |        |        |

| Output current on any pin        | $I_{\rm OH}$ , $I_{\rm OL}$ | -    | -      | 20   | mA     | 1) 2)          | P_5.5.1 |  |      |        |        |

| Max output current for all GPIOs | I <sub>max</sub>            | -    | -      | 60   | mA     | 1) 2)          | P_5.5.2 |  |      |        |        |

1) One of these limits must be kept.

2) Not subject to production test, specified by design

## 5.5.2 DC Parameters

These parameters apply to the IO voltage range, 4.5 V  $\leq V_{\text{DDP}} \leq$  5.5 V.

Note: Operating Conditions apply.

Keeping signal levels within the limits specified in this table ensures operation without overload conditions. For signal levels outside these specifications, also refer to the specification of the overload current  $I_{ov}$ .

## Table 26 DC Characteristics

$V_{\rm S}$  = 5.5 V to 27 V,  $T_{\rm j}$  = -40° C to +150 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                       | Symbol           |                         | Values | Unit                   | Note / | Number                                                                         |          |

|-------------------------------------------------|------------------|-------------------------|--------|------------------------|--------|--------------------------------------------------------------------------------|----------|

|                                                 |                  | Min.                    | Тур.   | Max.                   |        | <b>Test Condition</b>                                                          |          |

| Input low voltage<br>(all except XTAL1)         | V <sub>IL</sub>  | -0.3                    | -      | 0.3 x V <sub>DDP</sub> | V      | -                                                                              | P_5.5.3  |

| Input high voltage<br>(all except XTAL1)        | V <sub>IH</sub>  | 0.7 x V <sub>DDP</sub>  | -      | V <sub>DDP</sub> + 0.3 | V      | -                                                                              | P_5.5.4  |

| Input Hysteresis <sup>1)</sup>                  | HYS              | 0.11 x V <sub>DDP</sub> | -      | -                      | V      | Series resistance = $0 \Omega$                                                 | P_5.5.5  |

| Output low voltage                              | V <sub>OL</sub>  | -                       | -      | 1.0                    | V      | <sup>2)</sup> $I_{OL} \leq I_{OLmax}$                                          | P_5.5.6  |

| Output low voltage                              | V <sub>OL</sub>  | -                       | -      | 0.4                    | V      | <sup>2)</sup> $I_{OL} \leq {}^{3)} I_{OLnom}$                                  | P_5.5.7  |

| Output high voltage <sup>4)</sup>               | V <sub>OH</sub>  | V <sub>DDP</sub> - 1.0  | -      | -                      | V      | <sup>2)</sup> $I_{OH} \ge I_{OHmax}$                                           | P_5.5.8  |

| Output high voltage                             | V <sub>OH</sub>  | V <sub>DDP</sub> - 0.4  | -      | -                      | V      | <sup>2)3)</sup> $I_{OH} \ge I_{OHnom}$                                         | P_5.5.9  |

| Input leakage current<br>(Port 2)               | I <sub>OZ1</sub> | -400                    | -      | +400                   | nA     | $T_{\rm J} \le 85^{\circ}{ m C},$<br>0 V < $V_{\rm IN} < V_{\rm DDP}$          | P_5.5.10 |

| Input leakage current (all other) <sup>5)</sup> | I <sub>OZ2</sub> | -5                      | -      | +5                     | μA     | $T_{\rm J} \le 85^{\circ}{\rm C},$<br>0.45 V < $V_{\rm IN}$<br>< $V_{\rm DDP}$ | P_5.5.11 |

## Table 28 Electrical Characteristics (cont'd) LIN Transceiver

$V_s$  = 5.5V - 18V,  $T_j$  = -40° C to +150 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                                                               | Symbol               |       | Value | es    | Unit | Note / Test Condition                                                                                                                                                                                 | Number   |

|-----------------------------------------------------------------------------------------|----------------------|-------|-------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                                                                         |                      | Min.  | Тур.  | Max.  |      |                                                                                                                                                                                                       |          |

| Propagation delay<br>bus recessive to RxD HIGH                                          | $t_{\rm d(H),R}$     | 0.1   | 0.5   | 6     | μs   | -                                                                                                                                                                                                     | P_5.6.32 |

| Receiver delay symmetry                                                                 | t <sub>sym,R</sub>   | -1.0  | -     | 1.0   | μs   | $t_{\rm sym,R} = t_{\rm d(L),R} - t_{\rm d(H),R};$                                                                                                                                                    | P_5.6.33 |

| Duty cycle D7<br>(for worst case at 115 kBit/s)<br>for +1 µs Receiver delay<br>symmetry | t <sub>duty1</sub>   | 0.399 | -     | -     |      | <sup>8)</sup> duty cycle D7<br>$TH_{Rec}(max) =$<br>$0.744 \times V_S;$<br>$TH_{Dom}(max) =$<br>$0.581 \times V_S; V_S = 13.5 V;$<br>$t_{bit} = 8.7 \ \mu s;$<br>$D7 = t_{bus\_rec(min)}/2 t_{bit};$  | P_5.6.34 |

| Duty cycle D8<br>(for worst case at 115 kBit/s)<br>for +1 µs Receiver delay<br>symmetry | t <sub>duty2</sub>   | -     | -     | 0.578 |      | <sup>6)</sup> duty cycle 8<br>$TH_{Rec}(max) =$<br>$0.422 \times V_S;$<br>$TH_{Dom}(max) =$<br>$0.284 \times V_S; V_S = 13.5 V;$<br>$t_{bit} = 8.7 \ \mu s;$<br>$D8 = t_{bus\_rec}(max)/2 \ t_{bit};$ | P_5.6.35 |

| TxD dominant time out                                                                   | t <sub>timeout</sub> | 6     | 12    | 20    | ms   | <sup>8)</sup> $V_{\text{TxD}} = 0 \text{ V}$                                                                                                                                                          | P_5.6.36 |

1) Maximum limit specified by design.

2)  $V_{\text{BUS}\_\text{CNT}} = (V_{\text{th}\_\text{dom}} + V_{\text{th} \text{ rec}})/2$

3)  $V_{\text{HYS}} = V_{\text{BUSrec}} - V_{\text{BUSdom}}$

4) This parameter is not subject to production test

5) Bus load concerning LIN Spec 2.1: Load 1 = 1 nF / 1 k $\Omega$  =  $C_{\text{BUS}}$  /  $R_{\text{BUS}}$ Load 2 = 6.8 nF / 660  $\Omega$  =  $C_{\text{BUS}}$  /  $R_{\text{BUS}}$ Load 3 = 10 nF / 500  $\Omega$  =  $C_{\text{BUS}}$  /  $R_{\text{BUS}}$

- 6) Bus loads: Load 1 = 1 nF / 1 k $\Omega$  =  $C_{BUS}$  /  $R_{BUS}$ 7) Bus load concerning LNL Space 2.1:

- 7) Bus load concerning LIN Spec 2.1: Load 1 = 1 nF / 1 k $\Omega$  =  $C_{\text{BUS}}$  /  $R_{\text{BUS}}$ Load 2 = 6.8 nF / 660  $\Omega$  =  $C_{\text{BUS}}$  /  $R_{\text{BUS}}$ Load 3 = 10 nF / 500  $\Omega$  =  $C_{\text{BUS}}$  /  $R_{\text{BUS}}$

- 8) Timeout can be disabled optional

## 5.9.2 Analog/Digital Converter Parameters

These parameters describe the conditions for optimum ADC performance. *Note: Operating Conditions apply.*

## Table 36 A/D Converter Characteristics

$V_{\rm S}$  = 5.5 V to 27 V,  $T_{\rm j}$  = -40° C to +150 °C; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                        | Symbol                  |                                                   | Values                                                                    |                                                             | Unit | Note /                                        | Number   |

|--------------------------------------------------|-------------------------|---------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------|------|-----------------------------------------------|----------|

|                                                  |                         | Min.                                              | Тур.                                                                      | Max.                                                        |      | Test Condition                                |          |

| Analog reference supply                          | V <sub>AREFSR</sub>     | V <sub>AGND</sub><br>+ 1.0                        | -                                                                         | V <sub>DDPA</sub><br>+ 0.05                                 | V    | 1)                                            | P_5.9.7  |

| Analog reference ground                          | V <sub>AGNDSR</sub>     | <i>GND</i><br>- 0.05                              | -                                                                         | 1.5                                                         | V    | 2)                                            | P_5.9.8  |

| Analog input voltage range                       | V <sub>AIN</sub>        | $V_{AGND}$                                        | -                                                                         | $V_{AREF}$                                                  | V    | 3)                                            | P_5.9.9  |

| Analog clock frequency                           | $f_{\rm ADCI}$          | 0.5                                               | -                                                                         | 20                                                          | MHz  | 4)                                            | P_5.9.10 |

| Conversion time for 10-bit result <sup>5)</sup>  | <i>t</i> <sub>C10</sub> | (13 + STC)<br>× $t_{ADCI}$<br>+ 2 x $t_{SYS}$     | (13 + STC)<br>× <i>t</i> <sub>ADCI</sub><br>+ 2 x <i>t</i> <sub>SYS</sub> | (13 + STC)<br>× t <sub>ADCI</sub><br>+ 2 x t <sub>SYS</sub> | _    | 6)                                            | P_5.9.11 |

| Conversion time for 8-bit result                 | t <sub>C8</sub>         | $(11 + STC)  \times t_{ADCI}  + 2 \times t_{SYS}$ | (11 + STC)<br>× $t_{ADCI}$<br>+ 2 × $t_{SYS}$                             | $(11 + STC) \times t_{ADCI} + 2 \times t_{SYS}$             | -    | 6)                                            | P_5.9.12 |

| Wake-up time from analog<br>Stop Mode, fast mode | t <sub>WAF</sub>        | -                                                 | -                                                                         | 4                                                           | μs   | 7)                                            | P_5.9.13 |

| Wake-up time from analog<br>Stop Mode, slow mode | t <sub>WAS</sub>        | -                                                 | -                                                                         | 15                                                          | μs   | 7)                                            | P_5.9.14 |

| Total unadjusted error <sup>8)</sup>             | TUE                     | -15                                               | -                                                                         | + 15                                                        | LSB  | <sup>1)</sup> V <sub>AREF</sub> =<br>5.0 V±1% | P_5.9.15 |

| DNL error                                        | EA <sub>DNL</sub> EA    | -2                                                | -                                                                         | + 2                                                         | LSB  | -                                             | P_5.9.16 |

| INL error                                        | EA <sub>INL</sub> EA    | -5                                                | -                                                                         | + 5                                                         | LSB  | -                                             | P_5.9.17 |

| Gain error                                       | $EA_GAINEA$             | -10                                               | _                                                                         | + 10                                                        | LSB  | -                                             | P_5.9.18 |

| Offset error                                     | EA <sub>OFF</sub> EA    | -2                                                | -                                                                         | + 2                                                         | LSB  | -                                             | P_5.9.19 |

| Total capacitance of an analog input             | $C_{AINT}$              | _                                                 | -                                                                         | 10                                                          | pF   | 7)9)                                          | P_5.9.20 |

| Switched capacitance of an analog input          | C <sub>AINS</sub>       | -                                                 | -                                                                         | 4                                                           | pF   | 7)9)                                          | P_5.9.21 |

| Resistance of the analog input path              | R <sub>AIN</sub>        | -                                                 | -                                                                         | 2                                                           | kΩ   | 7)9)                                          | P_5.9.22 |

| Total capacitance<br>of the reference input      | $C_{AREFT}$             | -                                                 | -                                                                         | 15                                                          | pF   | 7)9)                                          | P_5.9.23 |

| Switched capacitance of the reference input      | $C_{AREFS}$             | -                                                 | -                                                                         | 7                                                           | pF   | 7)9)                                          | P_5.9.24 |

| Resistance of the reference input path           | R <sub>AREF</sub>       | -                                                 | _                                                                         | 2                                                           | kΩ   | 7)9)                                          | P_5.9.25 |

## Table 41 Electrical Characteristics (cont'd)

$V_{\rm S}$  = 5.5 V to 27 V,  $T_{\rm j}$  = -40° C to +150 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                              | Symbol                 | ymbol Values |      |      | Unit | Note / Test Condition                                                                         | Number    |  |

|--------------------------------------------------------|------------------------|--------------|------|------|------|-----------------------------------------------------------------------------------------------|-----------|--|

|                                                        |                        | Min.         | Тур. | Max. |      |                                                                                               |           |  |

| Turn OFF Delay time, PWM mode                          | t <sub>dOff,f-LS</sub> | -            | -    | 2    | μs   | LS_ON=0 to 0.1*Vs<br>$V_{\rm S}$ =13.5V, $R_{\rm L}$ =270 $\Omega$                            | P_5.12.12 |  |

| Turn OFF Rise time, PWM mode                           | t <sub>OFFR,PWM</sub>  | -            | 1    | 1.25 | μs   | $V_{\rm LS}$ 0.1*Vs to 0.9*Vs;<br>$V_{\rm S}$ =13.5V, $R_{\rm L}$ =270Ω                       | P_5.12.13 |  |

| Turn OFF Rise time, slow mode                          | t <sub>OFFR,Slow</sub> | -            | 100  | 150  | μs   | <sup>1)</sup> $V_{\rm LS}$ 0.9*Vs to 0.9*Vs;<br>$V_{\rm S}$ =13.5V, $R_{\rm L}$ =270 $\Omega$ | P_5.12.14 |  |

| Minimum Duty Cycle Pulse Width variation               | ton <sub>MIN</sub>     | 1.5          | 2    | 3.5  | μs   | $ton(dig) = 2\mu s^{2}$                                                                       | P_5.12.15 |  |

| Typical (systematic) Pulse Width increase LS_ON to VLS | d ton <sub>TYP</sub>   | -            | 1.25 | -    | μs   | $ton(dig) = 2\mu s^{2}$                                                                       | P_5.12.16 |  |

| Zener Clamp Voltage                                    | V <sub>AZ</sub>        | -            | 50   | -    | V    | values are valid at $T_{\rm i}$ = 25°C                                                        | P_5.12.17 |  |

| Clamping Energy (repetitive)                           | $E_{clamp}$            | -            | -    | 2    | mJ   | <sup>2)</sup> 1.000.000 cycles                                                                | P_5.12.18 |  |

| Clamping Energy                                        | E <sub>clamp</sub>     | -            | -    | 14   | mJ   | <sup>2)</sup> <i>T</i> start = 25°C                                                           | P_5.12.19 |  |

| Clamping Energy (single), hot                          | E <sub>clamp</sub>     | -            | -    | 7    | mJ   | <sup>2)</sup> 10 cycles, <i>T</i> start = $85^{\circ}$ C                                      | P_5.12.20 |  |

1) Static ON mode (no PWM)

2) Not subject to production test, specified by design

**Revision History**

## 7 Revision History

| Revision | Date       | Changes          |

|----------|------------|------------------|

| 1.0      | 2012-06-27 | Initial revision |

|          |            |                  |

|          |            |                  |

|          |            |                  |

## Trademarks of Infineon Technologies AG

AURIX<sup>™</sup>, C166<sup>™</sup>, CanPAK<sup>™</sup>, CIPOS<sup>™</sup>, CIPURSE<sup>™</sup>, EconoPACK<sup>™</sup>, CoolMOS<sup>™</sup>, CoolSET<sup>™</sup>, CORECONTROL<sup>™</sup>, CROSSAVE<sup>™</sup>, DAVE<sup>™</sup>, EasyPIM<sup>™</sup>, EconoBRIDGE<sup>™</sup>, EconoDUAL<sup>™</sup>, EconoPIM<sup>™</sup>, EiceDRIVER<sup>™</sup>, eupec<sup>™</sup>, FCOS<sup>™</sup>, HITFET<sup>™</sup>, HybridPACK<sup>™</sup>, I<sup>2</sup>RF<sup>™</sup>, ISOFACE<sup>™</sup>, IsoPACK<sup>™</sup>, MIPAQ<sup>™</sup>, ModSTACK<sup>™</sup>, my-d<sup>™</sup>, NovalithIC<sup>™</sup>, OptiMOS<sup>™</sup>, ORIGA<sup>™</sup>, PRIMARION<sup>™</sup>, PrimePACK<sup>™</sup>, PrimeSTACK<sup>™</sup>, PRO-SIL<sup>™</sup>, PROFET<sup>™</sup>, RASIC<sup>™</sup>, ReverSave<sup>™</sup>, SatRIC<sup>™</sup>, SIEGET<sup>™</sup>, SINDRION<sup>™</sup>, SIPMOS<sup>™</sup>, SmartLEWIS<sup>™</sup>, SOLID FLASH<sup>™</sup>, TEMPFET<sup>™</sup>, thinQ!<sup>™</sup>, TRENCHSTOP<sup>™</sup>, TriCore<sup>™</sup>.

#### Other Trademarks

Advance Design System<sup>™</sup> (ADS) of Agilent Technologies, AMBA<sup>™</sup>, ARM<sup>™</sup>, MULTI-ICE<sup>™</sup>, KEIL<sup>™</sup>, PRIMECELL<sup>™</sup>, REALVIEW<sup>™</sup>, THUMB<sup>™</sup>, µVision<sup>™</sup> of ARM Limited, UK. AUTOSAR<sup>™</sup> is licensed by AUTOSAR development partnership. Bluetooth™ of Bluetooth SIG Inc. CAT-iq™ of DECT Forum. COLOSSUS™, FirstGPS™ of Trimble Navigation Ltd. EMV™ of EMVCo, LLC (Visa Holdings Inc.). EPCOS™ of Epcos AG. FLEXGO™ of Microsoft Corporation. FlexRay™ is licensed by FlexRay Consortium. HYPERTERMINAL™ of Hilgraeve Incorporated. IEC<sup>™</sup> of Commission Electrotechnique Internationale. IrDA<sup>™</sup> of Infrared Data Association Corporation. ISO™ of INTERNATIONAL ORGANIZATION FOR STANDARDIZATION. MATLAB™ of MathWorks, Inc. MAXIM™ of Maxim Integrated Products, Inc. MICROTEC™, NUCLEUS™ of Mentor Graphics Corporation. Mifare™ of NXP. MIPI™ of MIPI Alliance, Inc. MIPS™ of MIPS Technologies, Inc., USA. muRata™ of MURATA MANUFACTURING CO., MICROWAVE OFFICE™ (MWO) of Applied Wave Research Inc., OmniVision<sup>™</sup> of OmniVision Technologies, Inc. Openwave<sup>™</sup> Openwave Systems Inc. RED HAT<sup>™</sup> Red Hat, Inc. RFMD<sup>™</sup> RF Micro Devices, Inc. SIRIUS<sup>™</sup> of Sirius Satellite Radio Inc. SOLARIS<sup>™</sup> of Sun Microsystems, Inc. SPANSION™ of Spansion LLC Ltd. Symbian™ of Symbian Software Limited. TAIYO YUDEN™ of Taiyo Yuden Co. TEAKLITE™ of CEVA, Inc. TEKTRONIX™ of Tektronix Inc. TOKO™ of TOKO KABUSHIKI KAISHA TA. UNIX™ of X/Open Company Limited. VERILOG™, PALLADIUM™ of Cadence Design Systems, Inc. VLYNQ™ of Texas Instruments Incorporated. VXWORKS™, WIND RIVER™ of WIND RIVER SYSTEMS, INC. ZETEX™ of Diodes Zetex Limited.

Last Trademarks Update 2011-02-24