Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                       |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | e200z4                                                       |

| Core Size                  | 32-Bit Single-Core                                           |

| Speed                      | 150MHz                                                       |

| Connectivity               | CANbus, EBI/EMI, LINbus, SCI, SPI                            |

| Peripherals                | DMA, POR, PWM, WDT                                           |

| Number of I/O              | 84                                                           |

| Program Memory Size        | 2MB (2M x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | •                                                            |

| RAM Size                   | 128K × 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.14V ~ 5.25V                                                |

| Data Converters            | A/D 40x12b                                                   |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                           |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 176-LQFP                                                     |

| Supplier Device Package    | 176-LQFP (24x24)                                             |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=spc5642af2mlu1r |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Introduction

• Calibration support allowing an external tool to modify address mapping

# 1.5.2 Crossbar switch (XBAR)

The XBAR multiport crossbar switch supports simultaneous connections between four master ports and four slave ports. The crossbar supports a 32-bit address bus width and a 64-bit data bus width.

The crossbar allows three concurrent transactions to occur from the master ports to any slave port but each master must access a different slave. If a slave port is simultaneously requested by more than one master port, arbitration logic selects the higher priority master and grants it ownership of the slave port. All other masters requesting that slave port are stalled until the higher priority master completes its transactions. Requesting masters are treated with equal priority and are granted access to a slave port in round-robin fashion, based upon the ID of the last master to be granted access. The crossbar provides the following features:

- 4 master ports

- CPU instruction bus

- CPU data bus

- eDMA

- FlexRay

- 4 slave ports

- Flash

- Calibration bus interface

- SRAM

- Peripheral bridge

- 32-bit internal address, 64-bit internal data paths

# 1.5.3 Enhanced direct memory access (eDMA)

The enhanced direct memory access (eDMA) controller is a second-generation module capable of performing complex data movements via 64 programmable channels, with minimal intervention from the host processor. The hardware micro-architecture includes a DMA engine which performs source and destination address calculations, and the actual data movement operations, along with an SRAM-based memory containing the transfer control descriptors (TCD) for the channels. This implementation minimizes overall block size. The eDMA module provides the following features:

- All data movement via dual-address transfers: read from source, write to destination

- Programmable source and destination addresses, transfer size, plus support for enhanced addressing modes

- Transfer control descriptor organized to support two-deep, nested transfer operations

- An inner data transfer loop defined by a "minor" byte transfer count

- An outer data transfer loop defined by a "major" iteration count

- Channel activation via one of three methods:

- Explicit software initiation

- Initiation via a channel-to-channel linking mechanism for continuous transfers

- Peripheral-paced hardware requests (one per channel)

- Support for fixed-priority and round-robin channel arbitration

- Channel completion reported via optional interrupt requests

- 1 interrupt per channel, optionally asserted at completion of major iteration count

- Error termination interrupts optionally enabled

- Support for scatter/gather DMA processing

- Ability to suspend channel transfers by a higher priority channel

Introduction

- Second time base counter can work as a continuous angle counter, enabling angle based applications to match angle instead of time

- Both time bases can be exported to the eMIOS timer module

- Both time bases visible from the host

- Event-triggered microengine:

- Fixed-length instruction execution in two-system-clock microcycle

- 14 KB of code memory (SCM)

- 3 KB of parameter (data) RAM (SPRAM)

- Parallel execution of data memory, ALU, channel control and flow control sub-instructions in selected combinations

- 32-bit microengine registers and 24-bit wide ALU, with 1 microcycle addition and subtraction, absolute value, bitwise logical operations on 24-bit, 16-bit, or byte operands, single-bit manipulation, shift operations, sign extension and conditional execution

- Additional 24-bit Multiply/MAC/Divide unit which supports all signed/unsigned Multiply/MAC combinations, and unsigned 24-bit divide. The MAC/Divide unit works in parallel with the regular microcode commands.

- Resource sharing features support channel use of common channel registers, memory and microengine time:

- Hardware scheduler works as a "task management" unit, dispatching event service routines by predefined, host-configured priority

- Automatic channel context switch when a "task switch" occurs, that is, one function thread ends and another begins to service a request from other channel: channel-specific registers, flags and parameter base address are automatically loaded for the next serviced channel

- SPRAM shared between host CPU and eTPU2, supporting communication either between channels and host or inter-channel

- Hardware implementation of 4 semaphores support coherent parameter sharing between both eTPU engines

- Dual-parameter coherency hardware support allows atomic access to 2 parameters by host

- Test and development support features:

- Nexus Class 1 debug, supporting single-step execution, arbitrary microinstruction execution, hardware breakpoints and watchpoints on several conditions

- Software breakpoints

- SCM continuous signature-check built-in self test MISC (multiple input signature calculator), runs concurrently with eTPU2 normal operation

# 1.5.13 Reaction module (REACM)

The REACM provides the ability to modulate output signals to manage closed loop control without CPU assistance. It works in conjunction with the eQADC and eTPU2 to increase system performance by removing the CPU from the current control loop.

The REACM has the following features:

- 6 reaction channels with peak and hold control blocks

- Each channel output is a bus of 3 signals, providing ability to control 3 inputs.

- Each channel can implement a peak and hold waveform, making it possible to implement up to six independent peak and hold control channels

Target applications include solenoid control for direct injection systems and valve control in automatic transmissions.

#### Pinout and signal description

| VSS     | VSS    | VSS      |         |         |         |         | VRC33    | NC       | NC       | VDDEH6AB | м  |

|---------|--------|----------|---------|---------|---------|---------|----------|----------|----------|----------|----|

| VSS     | VSS    | VSS      |         |         |         |         | NC       | SCI_A_TX | VSS      | NC       | Ν  |

| VSS     | VSS    | VSS      |         |         |         |         | CAN_C_TX | SCI_A_RX | RSTOUT   | RSTCFG   | Р  |

|         |        |          |         |         |         |         | NC       | NC       | NC       | RESET    | R  |

|         |        |          |         |         |         |         | VSS      | BOOTCFG0 | VSS      | VSS      | т  |

|         |        |          |         |         |         |         | VDDEH6AB | PLLCFG1  | BOOTCFG1 | EXTAL    | U  |

|         |        |          |         |         |         |         | SCI_C_RX | CAN_C_RX | PLLREF   | XTAL     | v  |

| ETPUA1  | EMIOS1 | VDDEH4AB | EMIOS8  | EMIOS15 | EMIOS16 | EMIOS23 | SCI_C_TX | VDD      | CAN_B_RX | VDDPLL   | w  |

| ETPUA0  | EMIOS2 | EMIOS5   | EMIOS9  | EMIOS14 | EMIOS17 | EMIOS22 | CAN_A_RX | VSS      | VDD      | CAN_B_TX | Y  |

| EMIOS0  | EMIOS3 | EMIOS6   | EMIOS10 | EMIOS13 | EMIOS18 | EMIOS21 | VDDEH4AB | WKPCFG   | VSS      | VDD      | AA |

| TCRCLKA | EMIOS4 | EMIOS7   | EMIOS11 | EMIOS12 | EMIOS19 | EMIOS20 | CAN_A_TX | SCI_B_RX | SCI_B_TX | VSS      | AB |

| 12      | 13     | 14       | 15      | 16      | 17      | 18      | 19       | 20       | 21       | 22       |    |

Figure 7. 324-pin TEPBGA package ballmap (southeast, viewed from above)

30

# 2.4 Signal summary

## Table 3. MPC5642A signal properties

| Name <sup>1</sup>                                           | Function <sup>2</sup>                                                             | P/A/G <sup>3</sup> | PCR<br>PA                | PCR <sup>5</sup>  | I/O              | Voltage <sup>6</sup> /         | Sta           | ntus <sup>8</sup> | Pa  | ickage pin N | lo. |

|-------------------------------------------------------------|-----------------------------------------------------------------------------------|--------------------|--------------------------|-------------------|------------------|--------------------------------|---------------|-------------------|-----|--------------|-----|

| Name                                                        | Function                                                                          | P/A/G              | field <sup>4</sup>       | PCR               | type             | Pad type <sup>7</sup>          | During reset  | After reset       | 176 | 208          | 324 |

|                                                             |                                                                                   | I                  |                          |                   | GPIO             | I                              |               |                   |     | 1            |     |

| FR_A_TX<br>GPIO[12]                                         | FlexRay transmit data channel A GPIO                                              | A1<br>G            | 010<br>000               | 12                | 0<br>I/O         | VDDE-EH /<br>Medium            | — / Up        | — / Up            | —   | —            | P3  |

| FR_A_TX_EN<br>GPIO[13]                                      | FlexRay ch. A tx data enable GPIO                                                 | A1<br>G            | 010<br>000               | 13                | 0<br>I/O         | VDDE-EH /<br>Medium            | — / Up        | — / Up            | —   | —            | P4  |

| FR_A_RX<br>GPIO[14]                                         | FlexRay receive data ch. A<br>GPIO                                                | A1<br>G            | 010<br>000               | 14                | I<br>I/O         | VDDE-EH /<br>Medium            | — / Up        | — / Up            | —   | —            | R1  |

| FR_B_TX<br>GPIO[15]                                         | FlexRay transmit data ch. B<br>GPIO                                               | A1<br>G            | 010<br>000               | 15                | 0<br>I/O         | VDDE-EH /<br>Medium            | — / Up        | — / Up            | —   | _            | R2  |

| FR_B_TX_EN<br>GPIO[16]                                      | FlexRay tx data enable for ch. B<br>GPIO                                          | A1<br>G            | 010<br>000               | 16                | 0<br>I/O         | VDDE-EH /<br>Medium            | — / Up        | — / Up            | —   | —            | R4  |

| FR_B_RX<br>GPIO[17]                                         | FlexRay receive data channel B<br>GPIO                                            | A1<br>G            | 010<br>000               | 17                | I<br>I/O         | VDDE-EH /<br>Medium            | — / Up        | — / Up            | —   | —            | T1  |

| GPIO[206] ETRIGO                                            | GPIO / eQADC Trigger Input                                                        | G                  | 00                       | 206               | I/O <sup>9</sup> | VDDEH7 /<br>Slow <sup>10</sup> | — / Up        | — / Up            | 143 | R4           | C14 |

| GPIO[207] ETRIG1                                            | GPIO / eQADC Trigger Input                                                        | G                  | 00                       | 207               | I/O <sup>9</sup> | VDDEH7 /<br>Slow               | — / Up        | — / Up            | 144 | P5           | B14 |

| GPIO[219]                                                   | GPIO                                                                              | G                  | 000                      | 219 <sup>11</sup> | I/O              | VDDEH7 /<br>MultV              | — / Up        | — / Up            | 122 | Т6           | _   |

|                                                             |                                                                                   |                    | R                        | Reset / (         | Configur         | ation                          | 1             |                   |     | 1            |     |

| RESET                                                       | External Reset Input                                                              | Р                  | _                        | —                 | I                | VDDEH6 /<br>Slow               | RESET / Up    | RESET / Up        | 97  | L16          | R22 |

| RSTOUT                                                      | External Reset Output                                                             | Р                  | 01                       | 230               | 0                | VDDEH6 /<br>Slow               | RSTOUT / Down | RSTOUT / Down     | 102 | K15          | P21 |

| PLLREF<br>IRQ[4]<br>ETRIG2<br>GPIO[208]                     | FMPLL Mode Selection<br>External Interrupt Request<br>eQADC Trigger Input<br>GPIO | P<br>A1<br>A2<br>G | 001<br>010<br>100<br>000 | 208               | <br> <br> /0     | VDDEH6 /<br>Slow               | — / Up        | PLLREF / Up       | 83  | M14          | V21 |

| PLLCFG1 <sup>12</sup><br>IRQ[5]<br>DSPI_D_SOUT<br>GPIO[209] | —<br>External interrupt request<br>DSPI D data output<br>GPIO                     | —<br>A1<br>A2<br>G | <br>010<br>100<br>000    | 209               | <br> <br> /0     | VDDEH6 /<br>Medium             | — / Up        | — / Up            | —   | _            | U20 |

| RSTCFG<br>GPIO[210]                                         | RSTCFG<br>GPIO                                                                    | P<br>G             | 01<br>00                 | 210               | I<br>I/O         | VDDEH6 /<br>Slow               | — / Down      | _                 | —   | —            | P22 |

Pinout and signal description

| Name <sup>1</sup> | Function <sup>2</sup>                              | P / A / G <sup>3</sup> | PCR<br>PA          | PCR <sup>5</sup> | I/O    | Voltage <sup>6</sup> /<br>Pad type <sup>7</sup> | St           | atus <sup>8</sup> | Package pin No. |     |     |

|-------------------|----------------------------------------------------|------------------------|--------------------|------------------|--------|-------------------------------------------------|--------------|-------------------|-----------------|-----|-----|

| Name <sup>1</sup> | Function-                                          | P/A/G°                 | field <sup>4</sup> | PCR°             | type   | Pad type <sup>7</sup>                           | During reset | After reset       | 176             | 208 | 324 |

| CAL_DATA[10]      | Calibration data bus                               | Р                      | 01                 | 341              | I/O    | VDDE12 /<br>Fast                                | — / Up       | — / Up            | _               | -   | -   |

| CAL_DATA[11]      | Calibration data bus                               | Р                      | 01                 | 341              | I/O    | VDDE12 /<br>Fast                                | — / Up       | — / Up            | _               | -   | -   |

| CAL_DATA[12]      | Calibration data bus                               | Р                      | 01                 | 341              | I/O    | VDDE12 /<br>Fast                                | — / Up       | — / Up            | _               | -   | -   |

| CAL_DATA[13]      | Calibration data bus                               | Р                      | 01                 | 341              | I/O    | VDDE12 /<br>Fast                                | — / Up       | — / Up            | _               | -   | -   |

| CAL_DATA[14]      | Calibration data bus                               | Р                      | 01                 | 341              | I/O    | VDDE12 /<br>Fast                                | — / Up       | — / Up            | _               | -   | -   |

| CAL_DATA[15]      | Calibration data bus                               | Р                      | 01                 | 341              | I/O    | VDDE12 /<br>Fast                                | — / Up       | — / Up            | _               | -   |     |

| CAL_RD_WR         | Calibration data bus                               | Р                      | 01                 | 342              | 0      | VDDE12 /<br>Fast                                |              | _/_               | _               | -   | -   |

| CAL_WE[0]         | Calibration write enable                           | Р                      | 01                 | 342              | 0      | VDDE12 /<br>Fast                                |              | _/_               | _               | -   | -   |

| CAL_WE[1]         | Calibration write enable                           | Р                      | 01                 | 342              | 0      | VDDE12 /<br>Fast                                |              | _/_               | _               | -   |     |

| CAL_OE            | Calibration output enable                          | Р                      | 01                 | 342              | 0      | VDDE12 /<br>Fast                                |              | _/_               | _               | -   | -   |

| CAL_TS<br>CAL_ALE | Calibration transfer start<br>Address Latch Enable | P<br>A1                | 01<br>10           | 343              | 0<br>0 | VDDE12 /<br>Fast                                |              | _/_               | _               | -   | -   |

| CAL_MDO[4]        | Calibration Nexus Message Data Out                 | Р                      | 01                 | -                | 0      | VDDE12 /<br>Fast                                | -            | CAL_MDO[4]/       | _               | -   | —   |

| CAL_MDO[5]        | Calibration Nexus Message Data Out                 | Р                      | 01                 | -                | 0      | VDDE12 /<br>Fast                                | -            | CAL_MDO[5]/       | _               | -   | -   |

| CAL_MDO[6]        | Calibration Nexus Message Data Out                 | Р                      | 01                 | —                | 0      | VDDE12 /<br>Fast                                | -            | CAL_MDO[6]/       | _               | -   |     |

| CAL_MDO[7]        | Calibration Nexus Message Data Out                 | Р                      | 01                 | _                | 0      | VDDE12 /<br>Fast                                | -            | CAL_MDO[7]/       | _               | -   | -   |

| CAL_MDO[8]        | Calibration Nexus Message Data Out                 | Р                      | 01                 | —                | 0      | VDDE12 /<br>Fast                                | -            | CAL_MDO[8]/       | _               | -   | -   |

| CAL_MDO[9]        | Calibration Nexus Message Data Out                 | Р                      | 01                 | —                | 0      | VDDE12 /<br>Fast                                | -            | CAL_MDO[9]/       | _               | -   | -   |

| CAL_MDO[10]       | Calibration Nexus Message Data Out                 | Р                      | 01                 | —                | 0      | VDDE12 /<br>Fast                                | _            | CAL_MDO[10] /     | _               | -   | -   |

| CAL_MDO[11]       | Calibration Nexus Message Data Out                 | Р                      | 01                 | _                | 0      | VDDE12 /<br>Fast                                | _            | CAL_MDO[11]/      | _               | _   |     |

# Table 3. MPC5642A signal properties (continued)

Pinout and signal description

# Table 3. MPC5642A signal properties (continued)

Pinout and signal description

| Name <sup>1</sup>                | Function <sup>2</sup>                                              | P/A/G <sup>3</sup> | PCR                      | PCR <sup>5</sup>  | I/O                | Voltage <sup>6</sup> / | Sta          | itus <sup>8</sup> | Package pin No. |     |     |

|----------------------------------|--------------------------------------------------------------------|--------------------|--------------------------|-------------------|--------------------|------------------------|--------------|-------------------|-----------------|-----|-----|

| Name <sup>1</sup>                | Function-                                                          | P/A/G              | PA<br>field <sup>4</sup> | PCR°              | type               | Pad type <sup>7</sup>  | During reset | After reset       | 176             | 208 | 324 |

|                                  |                                                                    |                    |                          | N                 | EXUS <sup>13</sup> |                        |              |                   |                 |     |     |

| EVTI                             | Nexus event in                                                     | Р                  | 01                       | 231               | I                  | VDDEH7 /<br>MultiV     | — / Up       | EVTI / Up         | 116             | E15 | H20 |

| EVTO <sup>14</sup>               | Nexus event out                                                    | Р                  | 01                       | 227               | 0                  | VDDEH7 /<br>MultiV     | ABR/Up       | EVTO / —          | 120             | D15 | G20 |

| МСКО                             | Nexus message clock out                                            | Р                  | —                        | 219 <sup>11</sup> | 0                  | VRC33 /<br>Fast        | _            | МСКО / —          | 14              | F15 | F1  |

| MDO[0]                           | Nexus message data out                                             | Р                  | 01                       | 220               | 0                  | VRC33 /<br>Fast        | _            | MDO[0] / —        | 17              | A14 | F3  |

| MDO[1]                           | Nexus message data out                                             | Р                  | 01                       | 221               | 0                  | VRC33 /<br>Fast        | _            | MDO[1] /          | 18              | B14 | G2  |

| MDO[2]                           | Nexus message data out                                             | Р                  | 01                       | 222               | 0                  | VRC33 /<br>Fast        | _            | MDO[2] /          | 19              | A13 | G3  |

| MDO[3]                           | Nexus message data out                                             | Р                  | 01                       | 223               | 0                  | VRC33 /<br>Fast        | _            | MDO[3] / —        | 20              | B13 | G4  |

| MDO[4]<br>ETPUA2_O<br>GPIO[75]   | Nexus message data out<br>eTPU A channel (output only)<br>GPIO     | P<br>A1<br>G       | 01<br>10<br>00           | 75                | 0<br>0<br>I/0      | VDDEH7 /<br>MultiV     | —            | _/_               | 126             | P10 | B19 |

| MDO[5]<br>ETPUA4_O<br>GPIO[76]   | Nexus message data out<br>eTPU A channel (output only)<br>GPIO     | P<br>A1<br>G       | 01<br>10<br>00           | 76                | 0<br>0<br>I/0      | VDDEH7 /<br>MultiV     | —            | _/_               | 129             | T10 | B20 |

| MDO[6]<br>ETPUA13_0<br>GPIO[77]  | Nexus message data out<br>eTPU A channel (output only)<br>GPIO     | P<br>A1<br>G       | 01<br>10<br>00           | 77                | 0<br>0<br>I/O      | VDDEH7 /<br>MultiV     | —            | _/_               | 135             | T11 | C18 |

| MDO[7]<br>ETPUA19_O<br>GPIO[78]  | Nexus message data out<br>eTPU A channel (output only)<br>GPIO     | P<br>A1<br>G       | 01<br>10<br>00           | 78                | 0<br>0<br>I/O      | VDDEH7 /<br>MultiV     | —            | _/_               | 136             | N11 | B18 |

| MDO[8]<br>ETPUA21_O<br>GPIO[79]  | Nexus message data out<br>eTPU A channel (output only)<br>GPIO     | P<br>A1<br>G       | 01<br>10<br>00           | 79                | 0<br>0<br>I/0      | VDDEH7 /<br>MultiV     | —            | _/_               | 137             | P11 | A18 |

| MDO[9]<br>ETPUA25_O<br>PIO[80]   | Nexus message data out<br>eTPU A channel (output only)<br>GPIO     | P<br>A1<br>G       | 01<br>10<br>00           | 80                | 0<br>0<br>I/0      | VDDEH7 /<br>MultiV     | _            | _/_               | 139             | T7  | D18 |

| MDO[10]<br>ETPUA27_O<br>GPIO[81] | Nexus message data out<br>eTPU A channel (output only)<br>GPIO     | P<br>A1<br>G       | 01<br>10<br>00           | 81                | 0<br>0<br>I/0      | VDDEH7 /<br>MultiV     | _            | _/_               | 134             | R10 | A19 |

| MDO[11]<br>ETPUA29_0<br>GPIO[82] | Nexus message data out<br>eTPU A channel (output only)<br>GPIO[82] | P<br>A1<br>G       | 01<br>10<br>00           | 82                | 0<br>0<br>I/0      | VDDEH7 /<br>MultiV     | _            | _/_               | 124             | P9  | C19 |

# Table 3. MPC5642A signal properties (continued)

| Name <sup>1</sup>                  | Function <sup>2</sup>            | P / A / G <sup>3</sup> | PCR<br>PA          | PCR <sup>5</sup> | I/O        | Voltage <sup>6</sup> / | 1 type <sup>7</sup> |               | P   | ackage pin l   | No.         |

|------------------------------------|----------------------------------|------------------------|--------------------|------------------|------------|------------------------|---------------------|---------------|-----|----------------|-------------|

| Name                               | Function-                        | P/A/G°                 | field <sup>4</sup> | PCR°             | type       | Pad type <sup>7</sup>  | During reset        | After reset   | 176 | 208            | 324         |

| EMIOS20<br>GPIO[199]               | eMIOS channel<br>GPIO            | P<br>G                 | 01<br>00           | 199              | I/O<br>I/O | VDDEH4 /<br>Slow       | — /<br>WKPCFG       | — /<br>WKPCFG | _   | -              | AB18        |

| EMIOS21<br>GPIO[200]               |                                  |                        | 01<br>00           | 200              | I/O<br>I/O | VDDEH4 /<br>Slow       | — /<br>WKPCFG       | — /<br>WKPCFG | —   | -              | AA18        |

| EMIOS22<br>GPIO[201]               |                                  |                        | 01<br>00           | 201              | I/O<br>I/O | VDDEH4 /<br>Slow       | — / Down            | — / Down      | _   | _              | Y18         |

| EMIOS23<br>GPIO[202]               | eMIOS channel<br>GPIO            | P<br>G                 | 01<br>00           | 202              | I/O<br>I/O | VDDEH4 /<br>Slow       | — / Down            | — / Down      | 80  | R11            | W18         |

| EMIOS14 <sup>15</sup><br>GPIO[203] | eMIOS channel<br>GPIO            | P<br>G                 | 01<br>00           | 203              | 0<br>I/O   | VDDEH7 /<br>Slow       | — / Down            | — / Down      | _   | -              | A15         |

| EMIOS15 <sup>15</sup><br>GPIO[204] | eMIOS channel<br>GPIO            | P<br>G                 | 01<br>00           | 204              | 0<br>I/O   | VDDEH7 /<br>Slow       | — / Down            | — / Down      | -   | -              | D14         |

|                                    |                                  | L                      |                    | Clock            | Synthes    | izer                   |                     |               | 1   | -              | J           |

| XTAL                               | Crystal oscillator output        | Р                      | 01                 | —                | 0          | VDDEH6 /<br>Analog     | —                   | _             | 93  | P16            | V22         |

| EXTAL                              | Crystal oscillator input         | Р                      | 01                 | —                | I          | VDDEH6 /<br>Analog     | —                   | —             | 92  | N16            | U22         |

| CLKOUT                             | System clock output              | Р                      | 01                 | 229              | 0          | VDDE12 /<br>Fast       | —                   | CLKOUT        | _   | -              | AB9         |

| ENGCLK                             | Engineering clock output         | Р                      | 01                 | 214              | 0          | VDDE12 /<br>Fast       | —                   | ENGCLK        | _   | T14            | W10         |

|                                    |                                  | L                      |                    | Powe             | r / Grou   | nd                     |                     |               | 1   |                | J           |

| VDDREG                             | Voltage regulator supply         | —                      |                    | —                | I          | 5 V                    | I/—                 | VDDREG        | 10  | K16            | F4          |

| VRCCTL                             | Voltage regulator control output | —                      |                    | —                | 0          | _                      | 0/—                 | VRCCTL        | 11  | N14            | F2          |

| VRC33 <sup>17</sup>                | Internal regulator output        | —                      |                    | —                | 0          | 3.3 V                  | I/O / —             | VRC33         | 13  | A15,           | B1,         |

|                                    | Input for external 3.3 V supply  | —                      |                    | —                | I          | 3.3 V                  |                     |               |     | D1, N6,<br>N12 | M19,<br>P11 |

| VDDA                               | eQADC high reference voltage     | _                      |                    | —                | Ι          | 5 V                    | 1/—                 | VDDA          | 6   | A4, B11        | E3, A6      |

| VSSA eQADC ground/low reference v  |                                  | —                      |                    | —                | I          | _                      | I/—                 | VSSA          | 7   | A5, A11        | A7, E2      |

| VDDPLL                             | FMPLL supply voltage             | —                      |                    | —                | I          | 1.2 V                  | I/—                 | VDDPLL        | 91  | R16            | W22         |

| VSTBY                              | Power supply for standby RAM     | —                      |                    | —                | I          | 0.9 V – 6 V            | I/—                 | VSTBY         | 12  | C1             | E4          |

Freescale Semiconductor

MPC5642A Microcontroller Data Sheet, Rev. 3.1

Pinout and signal description

48

- <sup>7</sup> See Table 4 for details on pad types.

- <sup>8</sup> The Status During Reset pin is sampled after the internal POR is negated. Prior to exiting POR, the signal has a high impedance. Terminology is O (output), I (input), Up (weak pull up enabled), Down (weak pull down enabled), Low (output driven low), High (output driven high). A dash for the function in this column denotes that both the input and output buffer are turned off. The signal name to the left or right of the slash indicates the pin is enabled.

- <sup>9</sup> When used as ETRIG, this pin must be configured as an input. For GPIO it can be configured either as an input or output.

- <sup>10</sup> Maximum frequency is 50 kHz

- <sup>11</sup> PCR219 controls two different pins: MCKO and GPIO[219]. Please refer to Pad Configuration Register 219 section in SIU chapter of device reference manual for details.

- <sup>12</sup> On 176 LQFP and 208 MAPBGA packages, this pin is tied low internally.

- <sup>13</sup> These pins are selected by asserting JCOMP and configuring the NPC. SIU values have no effect on the function of this pin once enabled.

- <sup>14</sup> The BAM uses this pin to select if auto baud rate is on or off.

<sup>15</sup> Output only

- <sup>16</sup> This signal name is used to support legacy naming.

- <sup>17</sup> Do not use VRC33 to drive external circuits.

- <sup>18</sup> VDDEH1A, VDDEH1B and VDDEH1AB are shorted together in all production packages. The separation of the signal names is present to support legacy naming, however they should be considered as the same signal in this document.

- <sup>19</sup> VDDEH4, VDDEH4A, VDDEH4B and VDDEH4AB are shorted together in all production packages. The separation of the signal names is present to support legacy naming, however they should be considered as the same signal in this document.

- <sup>20</sup> VDDEH6, VDDEH6A, VDDEH6B and VDDEH6AB are shorted together in all production packages. The separation of the signal names is present to support legacy naming, however they should be considered as the same signal in this document.

- <sup>21</sup> VDDEH7, VDDEH7A and VDDE7B are shorted together in all production packages. The separation of the signal names is present to support legacy naming, however they should be considered as the same signal in this document.

| ID | Name       |                                                        | С | Parameter                                                                  |                    | Value     |                    | Unit |

|----|------------|--------------------------------------------------------|---|----------------------------------------------------------------------------|--------------------|-----------|--------------------|------|

| טו | Name       |                                                        | C | Parameter                                                                  | Min                | Тур       | Max                | Unit |

| 5d | ldd3p3     | СС                                                     | С | Voltage regulator 3.3 V maximum DC output current                          | 80                 | _         | —                  | mA   |

| 5e | Vdd33 ILim | СС                                                     | С | Voltage regulator 3.3 V DC current limit                                   | —                  | 130       | _                  | mA   |

| 6  | Lvi3p3     | СС                                                     | С | Nominal LVI for rising 3.3 V supply <sup>6</sup>                           | —                  | 3.090     | _                  | V    |

| 6a | _          | сс                                                     | С | Variation of LVI for rising 3.3 V supply at power-on reset <sup>7</sup>    | Lvi3p3<br>- 6%     | Lvi3p3    | Lvi3p3<br>+ 6%     | V    |

| 6b | _          | СС                                                     | С | Variation of LVI for rising 3.3 V supply after power-on reset <sup>7</sup> | Lvi3p3<br>– 3%     | Lvi3p3    | Lvi3p3<br>+ 3%     | V    |

| 6c | _          | СС                                                     | С | Trimming step LVI 3.3 V                                                    | —                  | 20        | _                  | mV   |

| 6d | Lvi3p3_h   | СС                                                     | С | LVI 3.3 V hysteresis                                                       | —                  | 60        | _                  | mV   |

| 7  | Por3.3V_r  | СС                                                     | С | Nominal POR for rising 3.3 V supply <sup>8</sup>                           | —                  | 2.07      | _                  | V    |

| 7a | _          | сс                                                     | С | Variation of POR for rising 3.3 V supply                                   | Por3.3V_r -<br>35% | Por3.3V_r | Por3.3V_r<br>+ 35% | V    |

| 7b | Por3.3V_f  | СС                                                     | С | Nominal POR for falling 3.3 V supply                                       |                    | 1.95      | _                  | V    |

| 7c | —          | сс                                                     | С | Variation of POR for falling 3.3 V supply                                  | Por3.3V_f<br>- 35% | Por3.3V_f | Por3.3V_f<br>+ 35% | V    |

| 8  | Lvi5p0     | СС                                                     | С | Nominal LVI for rising 5 V VDDREG supply                                   |                    | 4.290     | _                  | V    |

| 8a | —          | сс                                                     | С | Variation of LVI for rising 5 V VDDREG supply at power-on reset            | Lvi5p0<br>- 6%     | Lvi5p0    | Lvi5p0<br>+ 6%     | V    |

| 8b | —          | СС                                                     | С | Variation of LVI for rising 5 V VDDREG supply power-on reset               | Lvi5p0<br>- 3%     | Lvi5p0    | Lvi5p0<br>+ 3%     | V    |

| 8c | —          | СС                                                     | С | Trimming step LVI 5 V                                                      | —                  | 20        |                    | mV   |

| 8d | Lvi5p0_h   | СС                                                     | С | LVI 5 V hysteresis                                                         | —                  | 60        | —                  | mV   |

| 9  | Por5V_r    | СС                                                     | С | Nominal POR for rising 5 V VDDREG supply                                   | —                  | 2.67      | —                  | V    |

| 9a | _          | СС                                                     | С | Variation of POR for rising 5 V VDDREG supply                              | Por5V_r<br>- 35%   | Por5V_r   | Por5V_r<br>+ 35%   | V    |

| 9b | Por5V_f    | Por5V_f CC C Nominal POR for falling 5 V VDDREG supply |   |                                                                            | 2.47               | —         | V                  |      |

| 9c | _          | сс                                                     | С | Variation of POR for falling 5 V VDDREG supply                             | Por5V_f<br>- 35%   | Por5V_f   | Por5V_f<br>+ 35%   | V    |

<sup>1</sup> Using external ballast transistor.

<sup>2</sup> Min range is extended to 10% since Lvi1p2 is reprogrammed from 1.2 V to 1.16 V after power-on reset.

<sup>3</sup> LVI for falling supply is calculated as LVI rising – LVI hysteresis.

<sup>4</sup> Lvi1p2 tracks DC target variation of internal V<sub>DD</sub> regulator. Minimum and maximum Lvi1p2 correspond to minimum and maximum V<sub>DD</sub> DC target respectively.

<sup>5</sup> With internal load up to Idd3p3

$^{6}\,$  The Lvi3p3 specs are also valid for the V\_{\rm DDEH}\,\rm LVI

<sup>7</sup> Lvi3p3 tracks DC target variation of internal V<sub>DD33</sub> regulator. Minimum and maximum Lvi3p3 correspond to minimum and maximum V<sub>DD33</sub> DC target respectively.

- <sup>18</sup> Maximum leakage occurs at maximum operating temperature. Leakage current decreases by approximately one-half for each 8 to 12 °C, in the ambient temperature range of 50 to 125 °C. Applies to analog pads.

- <sup>19</sup> Applies to CLKOUT, external bus pins, and Nexus pins

- <sup>20</sup> Applies to the FCK, SDI, SDO, and SDS pins

- <sup>21</sup> This programmable option applies only to eQADC differential input channels and is used for biasing and sensor diagnostics.

# 3.9 I/O pad current specifications

The power consumption of an I/O segment depends on the usage of the pins on a particular segment. The power consumption is the sum of all output pin currents for a particular segment. The output pin current can be calculated from Table 21 based on the voltage, frequency, and load on the pin. Use linear scaling to calculate pin currents for voltage, frequency, and load parameters that fall outside the values given in Table 21.

| Pad type                   | Symbol                    |    | с | Period<br>(ns) | Load <sup>2</sup><br>(pF) | V <sub>DDE</sub><br>(V) | Drive/Slew rate select | I <sub>DDE</sub> Avg<br>(mA) <sup>3</sup> | I <sub>DDE</sub> RMS<br>(mA) |

|----------------------------|---------------------------|----|---|----------------|---------------------------|-------------------------|------------------------|-------------------------------------------|------------------------------|

| Slow                       | I <sub>DRV_SSR_HV</sub>   | СС | D | 37             | 50                        | 5.25                    | 11                     | 9                                         |                              |

|                            |                           | СС | D | 130            | 50                        | 5.25                    | 01                     | 2.5                                       | —                            |

|                            |                           | СС | D | 650            | 50                        | 5.25                    | 00                     | 0.5                                       | —                            |

|                            |                           | СС | D | 840            | 200                       | 5.25                    | 00                     | 1.5                                       | —                            |

| Medium                     | I <sub>DRV_MSR_HV</sub>   | СС | D | 24             | 50                        | 5.25                    | 11                     | 14                                        | —                            |

|                            |                           | СС | D | 62             | 50                        | 5.25                    | 01                     | 5.3                                       | —                            |

|                            |                           | СС | D | 317            | 50                        | 5.25                    | 00                     | 1.1                                       |                              |

|                            |                           | СС | D | 425            | 200                       | 5.25                    | 00                     | 3                                         | —                            |

| Fast                       | I <sub>DRV_FC</sub>       | СС | D | 10             | 50                        | 3.6                     | 11                     | 22.7                                      | 68.3                         |

|                            |                           | СС | D | 10             | 30                        | 3.6                     | 10                     | 12.1                                      | 41.1                         |

|                            |                           | СС | D | 10             | 20                        | 3.6                     | 01                     | 8.3                                       | 27.7                         |

|                            |                           | СС | D | 10             | 10                        | 3.6                     | 00                     | 4.44                                      | 14.3                         |

|                            |                           | СС | D | 10             | 50                        | 1.98                    | 11                     | 12.5                                      | 31                           |

|                            |                           | СС | D | 10             | 30                        | 1.98                    | 10                     | 7.3                                       | 18.6                         |

|                            |                           | СС | D | 10             | 20                        | 1.98                    | 01                     | 5.42                                      | 12.6                         |

|                            |                           | СС | D | 10             | 10                        | 1.98                    | 00                     | 2.84                                      | 6.4                          |

| MultiV                     | I <sub>DRV_MULTV_HV</sub> | СС | D | 20             | 50                        | 5.25                    | 11                     | 9                                         | —                            |

| (High swing mode)          |                           | СС | D | 30             | 50                        | 5.25                    | 01                     | 6.1                                       | —                            |

|                            |                           | СС | D | 117            | 50                        | 5.25                    | 00                     | 2.3                                       | —                            |

|                            |                           | СС | D | 212            | 200                       | 5.25                    | 00                     | 5.8                                       | —                            |

| MultiV<br>(Low swing mode) | IDRV_MULTV_HV             | СС | D | 30             | 30                        | 5.25                    | 11                     | 3.4                                       | —                            |

Table 21. I/O pad average I<sub>DDE</sub> specifications<sup>1</sup>

<sup>1</sup> Numbers from simulations at best case process, 150 °C

<sup>2</sup> All loads are lumped.

<sup>3</sup> Average current is for pad configured as output only

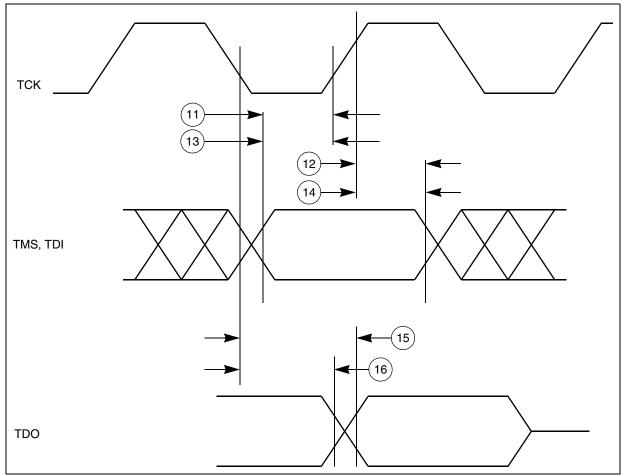

Figure 18. Nexus TDI, TMS, TDO timing

|                     |                                |                                  | I                           | Nexus Pin Usage          | 9                            | Max. Operating        |  |

|---------------------|--------------------------------|----------------------------------|-----------------------------|--------------------------|------------------------------|-----------------------|--|

| Package             | Nexus Width                    | Nexus Routing                    | MDO[0:3]                    | MDO[4:11]                | CAL_MDO[4:1<br>1]            | Frequency             |  |

| 176 LQFP<br>208 BGA | Reduced port mode <sup>1</sup> | Route to MDO <sup>2</sup>        | Nexus Data Out<br>[0:3]     | GPIO                     | GPIO                         | 40 MHz <sup>3</sup>   |  |

| 324 BGA             | Full port<br>mode <sup>4</sup> | Route to MDO <sup>2</sup>        | Nexus Data Out<br>[0:3]     | Nexus Data Out<br>[4:11] | GPIO                         | 40 MHz <sup>5,6</sup> |  |

| 496 CSP             | Reduced port mode <sup>1</sup> | Route to MDO <sup>2</sup>        | Nexus Data Out<br>[0:3]     | GPIO                     | GPIO                         | 40 MHz <sup>3</sup>   |  |

|                     | Full port<br>mode <sup>4</sup> | Route to MDO <sup>2</sup>        | Nexus Data Out<br>[0:3]     | Nexus Data Out<br>[4:11] | GPIO                         | 40 MHz <sup>5,6</sup> |  |

|                     |                                | Route to<br>CAL_MDO <sup>7</sup> | Cal Nexus Data<br>Out [0:3] | GPIO                     | Cal Nexus Data<br>Out [4:11] | 40 MHz <sup>3</sup>   |  |

| Table 39. Nexus | debug port | operating | frequency |

|-----------------|------------|-----------|-----------|

|-----------------|------------|-----------|-----------|

<sup>1</sup> NPC\_PCR[FPM] = 0 <sup>2</sup> NPC\_PCR[NEXCFG] = 0

# 3.17.4 Calibration bus interface timing

### Table 40. Calibration bus interface maximum operating frequency

| Port width | Multiplexed |                                | Pin usage                          |                                   |                     |  |  |  |  |  |

|------------|-------------|--------------------------------|------------------------------------|-----------------------------------|---------------------|--|--|--|--|--|

|            | mode        | CAL_ADDR[12:15]                | CAL_ADDR[16:30]                    | CAL_DATA[0:15]                    | frequency           |  |  |  |  |  |

| 16-bit     | Yes         | GPIO                           | GPIO                               | CAL_ADDR[12:30]<br>CAL_DATA[0:15] | 66 MHz <sup>1</sup> |  |  |  |  |  |

| 16-bit     | No          | CAL_ADDR[12:15]                | CAL_ADDR[16:30]                    | CAL_DATA[0:15]                    | 66 MHz <sup>1</sup> |  |  |  |  |  |

| 32-bit     | Yes         | CAL_WE/BE[2:3]<br>CAL_DATA[31] | CAL_ADDR[16:30]<br>CAL_DATA[16:30] | CAL_ADDR[0:15]<br>CAL_DATA[0:15]  | 66 MHz <sup>1</sup> |  |  |  |  |  |

<sup>1</sup> Set SIU\_ECCR[EBDF] to either divide by two or divide by four if the system frequency is greater than 66 MHz.

### Table 41. Calibration bus operation timing<sup>1</sup>

| #  | Symbol           |        | с | Characteristic                                                                                                                                                                                                                                                               |      | 66 MHz <sup>2</sup> |                |

|----|------------------|--------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------|----------------|

| #  | Sym              | symbol |   |                                                                                                                                                                                                                                                                              |      | Max                 | Unit           |

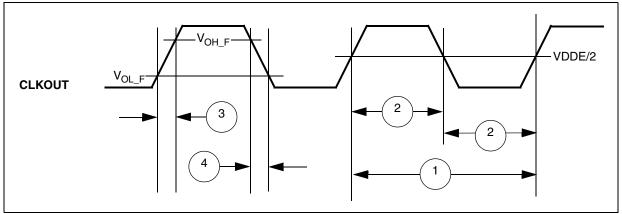

| 1  | T <sub>C</sub>   | CC     | Ρ | CLKOUT period <sup>3</sup>                                                                                                                                                                                                                                                   | 15.2 | _                   | ns             |

| 2  | t <sub>CDC</sub> | CC     | Т | CLKOUT duty cycle                                                                                                                                                                                                                                                            | 45%  | 55%                 | T <sub>C</sub> |

| 3  | t <sub>CRT</sub> | СС     | Т | CLKOUT rise time                                                                                                                                                                                                                                                             | _    | 4                   | ns             |

| 4  | t <sub>CFT</sub> | СС     | Т | CLKOUT fall time                                                                                                                                                                                                                                                             | —    | 4                   | ns             |

| 5  | t <sub>сон</sub> |        |   | CLKOUT Posedge to Output Signal Invalid or High Z (Hold Time)       1.3         CAL_ADDR[12:30]       1.3         CAL_CS[0], CAL_CS[2:3]       1.3         CAL_DATA[0:15]       1.3         CAL_RD_WR       1.3         CAL_TS       1.3         CAL_WE[0:3]/BE[0:3]       9 |      |                     |                |

|    |                  |        |   | CAL_ADDR[12:30]<br>CAL_CS[0], CAL_CS[2:3]<br>CAL_DATA[0:15]<br>CAL_OE<br>CAL_RD_WR<br>CAL_TS<br>CAL_WE[0:3]/BE[0:3]                                                                                                                                                          |      |                     |                |

| 7  | t <sub>CIS</sub> | CC     | Ρ | Input Signal Valid to CLKOUT Posedge (Setup Time)<br>DATA[0:31]                                                                                                                                                                                                              |      | —                   | ns             |

| 8  | t <sub>CIH</sub> | CC     | Ρ | CLKOUT Posedge to Input Signal Invalid (Hold Time) 1.0 —<br>DATA[0:31]                                                                                                                                                                                                       |      |                     | ns             |

| 9  | t <sub>APW</sub> | СС     | Ρ | ALE Pulse Width <sup>5</sup>                                                                                                                                                                                                                                                 | 6.5  | —                   | ns             |

| 10 | t <sub>AAI</sub> | СС     | Ρ | ALE Negated to Address Invalid <sup>5</sup> 1.5 <sup>6</sup> —                                                                                                                                                                                                               |      |                     |                |

- <sup>1</sup> Calibration bus timing specified at  $f_{SYS}$  = 150 MHz and 100 MHz,  $V_{DD}$  = 1.14 V to 1.32 V,  $V_{DDE}$  = 3 V to 3.6 V (unless stated otherwise),  $T_A$  =  $T_L$  to  $T_H$ , and  $C_L$  = 30 pF with DSC = 0b10.

- <sup>2</sup> The calibration bus is limited to half the speed of the internal bus. The maximum calibration bus frequency is 66 MHz. The bus division factor should be set accordingly based on the internal frequency being used.

- $^3\,$  Signals are measured at 50%  $V_{\text{DDE}}$

- <sup>4</sup> Refer to fast pad timing in Table 34 and Table 35 (different values for 1.8 V vs. 3.3 V).

- <sup>5</sup> Measured at 50% of ALE

- <sup>6</sup> When CAL\_TS pad is used for CAL\_ALE function the hold time is 1 ns instead of 1.5 ns.

Figure 19. CLKOUT timing

# 3.17.7 eMIOS timing

| Table 44. | eMIOS | timing <sup>1</sup> |

|-----------|-------|---------------------|

|-----------|-------|---------------------|

| #  | # Symbol               |  | с | Characteristic           | Va  | Unit |                  |

|----|------------------------|--|---|--------------------------|-----|------|------------------|

| 'n |                        |  | U |                          | Min | Max  | onit             |

| 1  | t <sub>MIPW</sub> CC D |  | D | eMIOS Input Pulse Width  | 4   |      | t <sub>CYC</sub> |

| 2  | t <sub>MOPW</sub> CC D |  | D | eMIOS Output Pulse Width | 1   | _    | t <sub>CYC</sub> |

<sup>1</sup> eMIOS timing specified at  $V_{DD}$  = 1.14 V to 1.32 V,  $V_{DDEH}$  = 4.75 V to 5.25 V,  $T_A$  =  $T_L$  to  $T_H$ , and  $C_L$  = 50 pF with SRC = 0b00.

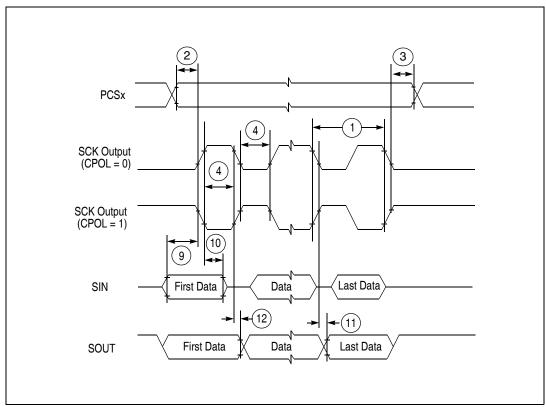

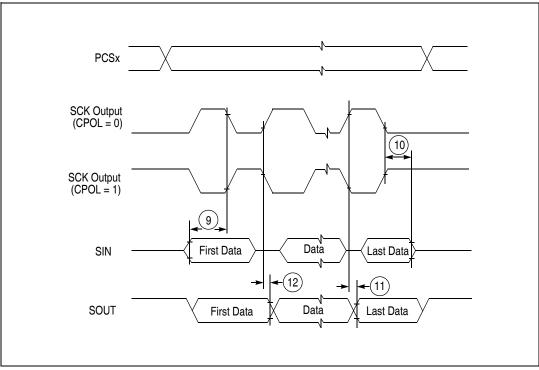

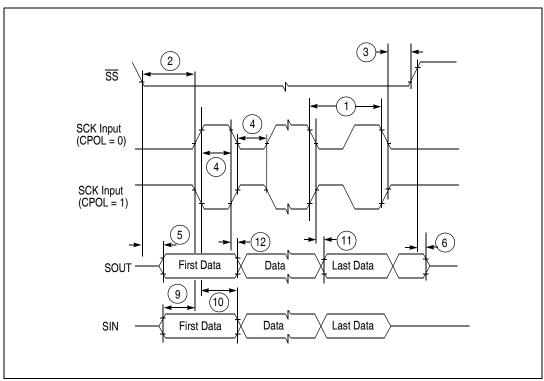

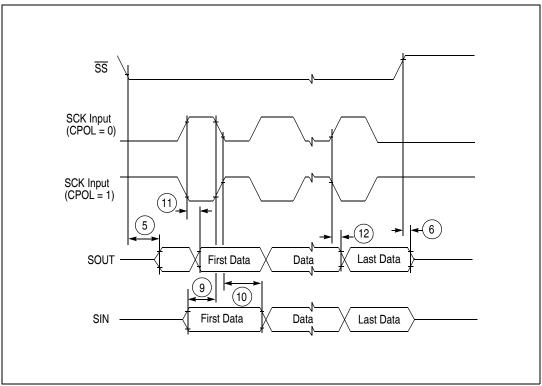

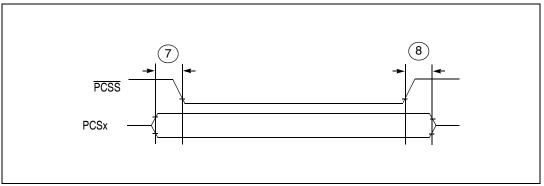

# 3.17.8 DSPI timing

DSPI channel frequency support for the MPC5642A MCU is shown in Table 45. Timing specifications are in Table 46.

| System clock<br>(MHz) | DSPI Use Mode | Maximum usable<br>frequency (MHz) | Notes                                                                                                                                                                       |  |  |

|-----------------------|---------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 150 LVDS 37.5         |               | 37.5                              | Use sysclock /4 divide ratio                                                                                                                                                |  |  |

|                       | Non-LVDS      | 18.75                             | Use sysclock /8 divide ratio                                                                                                                                                |  |  |

| 120                   | LVDS          | 40                                | Use sysclock /3 divide ratio. Gives 33/66 duty cycle. Use DSPI configuration DBR = 0b1 (double baud rate), BR = 0b0000 (scaler value 2) and PBR = 0b01 (prescaler value 3). |  |  |

|                       | Non-LVDS      | 20                                | Use sysclock /6 divide ratio                                                                                                                                                |  |  |

| 80                    | LVDS          | 40                                | Use sysclock /2 divide ratio                                                                                                                                                |  |  |

|                       | Non-LVDS      | 20                                | Use sysclock /4 divide ratio                                                                                                                                                |  |  |

Table 45. DSPI channel frequency support

## Table 46. DSPI timing<sup>1,2</sup>

| # | Symbol            |    | С | Characteristic                                                                | Condition | Min.                      | Max.                    | Unit |

|---|-------------------|----|---|-------------------------------------------------------------------------------|-----------|---------------------------|-------------------------|------|

| 1 | t <sub>SCK</sub>  | СС | D | SCK Cycle Time <sup>3,4,5</sup>                                               |           | 24.4 ns                   | 2.9 ms                  |      |

| 2 | t <sub>CSC</sub>  | СС | D | PCS to SCK Delay <sup>6</sup>                                                 |           | 22 <sup>7</sup>           | _                       | ns   |

| 3 | t <sub>ASC</sub>  | СС | D | After SCK Delay <sup>8</sup>                                                  |           | 21 <sup>9</sup>           | _                       | ns   |

| 4 | t <sub>SDC</sub>  | СС | D | SCK Duty Cycle                                                                |           | $(\frac{1}{2}t_{SC}) - 2$ | (½t <sub>SC</sub> ) + 2 | ns   |

| 5 | t <sub>A</sub>    | СС | D | Slave Access Time (SS active to SOUT driven)                                  |           | —                         | 25                      | ns   |

| 6 | t <sub>DIS</sub>  | СС | D | Slave SOUT Disable Time ( $\overline{SS}$ inactive to SOUT High-Z or invalid) |           | _                         | 25                      | ns   |

| 7 | t <sub>PCSC</sub> | СС | D | PCSx to PCSS time                                                             |           | 4 <sup>10</sup>           | _                       | ns   |

| 8 | t <sub>PASC</sub> | СС | D | PCSS to PCSx time                                                             |           | 5 <sup>11</sup>           | _                       | ns   |

# NP

### **Electrical characteristics**

- <sup>7</sup> Timing met when PCSSCK = 3 (01), and CSSCK = 2 (0000)

- <sup>8</sup> The maximum value is programmable in DSPI\_CTARx[PASC] and DSPI\_CTARx[ASC].

- <sup>9</sup> Timing met when ASC = 2 (0000), and PASC = 3 (01)

- $^{10}$  Timing met when PCSSCK = 3

- <sup>11</sup> Timing met when ASC = 3

<sup>12</sup> This number is calculated assuming the SMPL\_PT bitfield in DSPI\_MCR is set to 0b10.

Figure 24. DSPI classic SPI timing (master, CPHA = 0)

Figure 26. DSPI classic SPI timing (slave, CPHA = 0)

Figure 31. DSPI modified transfer format timing (slave, CPHA = 1)

Figure 32. DSPI PCS strobe (PCSS) timing

#### Packages

|                                                                                                                                                                                                                                                                                                                                                                                           | MECHANICAL OUTLINES                                                 | LOUTLINES                                         | DOCUMENT NO: 98ASS23840W |             |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------|--------------------------|-------------|--|--|

|                                                                                                                                                                                                                                                                                                                                                                                           | DICTIONARY                                                          |                                                   | PAGE:                    | 1158        |  |  |

| DIRECTALE SEMICINUCTOR, INC. ALL RIGHTS RESERVED.<br>ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED<br>DIRECTLY FROM THE DOCUMENT CONTROL REPOSITORY. PRINTED VERSIONS<br>ARE UNCONTROLLED EXCEPT WHEN STAMPED "CONTROLLED COPY" IN RED.                                                                                                                                       | DO NOT SCALE                                                        | THIS DRAWING                                      | REV:                     | D           |  |  |

| PREESCALE SEMICONDUCTOR, INC. ALL RICHTS RESERVED.<br>ELECTENCY FROM THE DOCUMENT CONTROL REPOSITORY. PRINTED VERSIONS<br>ARE UNCONTROLLED EXCEPT WHEN STAMPED CONTROLLED COPY IN RED.<br>NOTES:<br>1. ALL DIMENSIONS IN MILLIME<br>2. DIMENSIONING AND TOLERAI<br>3. MAXIMUM SOLDER BALL DIA<br>4. DATUM A, THE SEATING PL<br>SOLDER BALLS.<br>5. PARALLELISM MEASUREMENT<br>OF PACKAGE. | L<br>TERS.<br>NCING PER ASME<br>METER MEASURED<br>ANE, IS DETERMINI | Y14.5M—1994.<br>PARALLEL TO D/<br>ED BY THE SPHER | atum a.<br>Rical cr      | OWNS OF THE |  |  |

| TITLE: PBGA, 324<br>23 X 23 P                                                                                                                                                                                                                                                                                                                                                             | 1/0,<br>KG,                                                         | CASE NUMBER: 1<br>STANDARD: JEDE                  |                          |             |  |  |

| 1 MM PITCH (C                                                                                                                                                                                                                                                                                                                                                                             | MPAC)                                                               | PACKAGE CODE:                                     | 5241                     | SHEET: 2    |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                           |                                                                     |                                                   |                          |             |  |  |

## Figure 40. 324 BGA package mechanical drawing (part 2)

MPC5642A Microcontroller Data Sheet, Rev. 3.1

NP

**Document revision history**

| Date        | Revision      | Substantive changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 26 Mar 2012 | 2<br>(cont'd) | Merged "DSPI timing (V <sub>DDEH</sub> = 3.0 to 3.6 V)" and "DSPI timing (V <sub>DDEH</sub> = 4.5 to 5.5V)" tables into Table 46 (DSPI timing·) and changed all parameter classification to D<br>Table 47 (eQADC SSI timing characteristics (pads at 3.3 V or at 5.0 V)) changed all parameter classification to D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 04 May 2012 | 3             | <ul> <li>Minor editorial changes and improvements throughout.</li> <li>In Section 2.4, Signal summary, Table 3 (MPC5642A signal properties), updated the following properties for the Nexus" title for this pin group.</li> <li>Added a footnote to the "Name" entry for EVTO.</li> <li>Updated the "Status During reset" entry for EVTO.</li> <li>In Section 3.2, Maximum ratings, Table 8 (Absolute maximum ratings), removed the "TBD - To be defined" footnote.</li> <li>In Section 3.6, Power management control (PMC) and power on reset (POR) electrical specifications, removed the "Voltage regulator controller (VRC) electrical specifications, removed the "Voltage regulator controller (VRC) electrical specifications, removed the "TBD - To be defined" footnote.</li> <li>In Section 3.8, DC electrical specifications, Table 20 (DC electrical specifications), removed the "TBD - To be defined" footnote.</li> <li>In Section 3.9, I/O pad current specifications, Table 21 (I/O pad average I<sub>DDE</sub> specifications):</li> <li>Updated values and replaced TBDs with numerical data.</li> <li>Removed the "TBD - To be defined" footnote.</li> <li>In Section 3.9.1, I/O pad V<sub>RC33</sub> current specifications, Table 22 (I/O pad V<sub>RC33</sub> average I<sub>DDE</sub> specifications):</li> <li>Updated values and replaced TBDs with numerical data.</li> <li>Removed the "TBD - To be defined" footnote.</li> <li>In Section 3.14, Platform flash controller electrical characteristics, Table 31 (APC, RWSC, WWSC settings vs. frequency of operation), removed the "TBD - To be defined" footnote.</li> <li>In Section 5, Ordering information, Table 50 (Orderable part number summary):</li> <li>Changed "MPC5642AF0MMG1" to "SC667201MMG1".</li> <li>Changed "MPC5642AF0MMG1" to "SC667201MMG1".</li> <li>Changed "MPC5642AF0MMG3" to "SC667201MMG2".</li> <li>Changed "MPC5642AF0MMG3" to "SC667201MMG3".</li> <li>In Table 51 (Revision history), removed several erroneous items from the Revision 2 entry.</li> </ul> |

| 29 Jun 2012 | 3.1           | No content changes, technical or editorial, were made in this revision.<br>Removed the "preliminary" footers throughout.<br>Changed "Data Sheet: Advance Information" to "Data Sheet: Technical Data" on page 1.<br>Removed the "product under development" disclaimer on page 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

#### How to Reach Us:

Home Page: freescale.com