Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Active                                                                 |

| Core Processor             | e200z4                                                                 |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 80MHz                                                                  |

| Connectivity               | CANbus, EBI/EMI, LINbus, SCI, SPI                                      |

| Peripherals                | DMA, POR, PWM, WDT                                                     |

| Number of I/O              | 84                                                                     |

| Program Memory Size        | 2MB (2M x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 128K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.14V ~ 5.25V                                                          |

| Data Converters            | A/D 40x12b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 176-LQFP                                                               |

| Supplier Device Package    | 176-LQFP (24x24)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5642af2mlu3 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### How to Reach Us:

Home Page: freescale.com

Web Support: freescale.com/support Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document.

Freescale reserves the right to make changes without further notice to any products herein. Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address:freescale.com/SalesTermsandConditions.

Freescale, the Freescale logo, AltiVec, C-5, CodeTest, CodeWarrior, ColdFire, C-Ware, Energy Efficient Solutions logo, Kinetis, mobileGT, PowerQUICC, Processor Expert, QorlQ, Qorivva, StarCore, Symphony, and VortiQa are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. Airfast, BeeKit, BeeStack, ColdFire+, CoreNet, Flexis, MagniV, MXC, Platform in a Package, QorlQ Qonverge, QUICC Engine, Ready Play, SafeAssure, SMARTMOS, TurboLink, Vybrid, and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2014 Freescale Semiconductor, Inc.

Document Number: MPC5642A\_AD Rev. 1 12/2014

# 1 Introduction

## 1.1 Document overview

This document provides electrical specifications, pin assignments, and package diagrams for the MPC5642A series of microcontroller units (MCUs). It also describes the device features and highlights important electrical and physical characteristics. For functional characteristics, refer to the device reference manual.

# 1.2 Description

This microcontroller is a 32-bit system-on-chip (SoC) device intended for use in mid-range engine control and automotive transmission control applications.

It is compatible with devices in Freescale's MPC5600 family and offers performance and capabilities beyond the MPC5632M devices.

The microcontroller's e200z4 host processor core is built on the Power Architecture<sup>®</sup> technology and designed specifically for embedded applications. In addition to the Power Architecture technology, this core supports instructions for digital signal processing (DSP).

The device has two levels of memory hierarchy consisting of 8 KB of instruction cache, backed by a 128 KB on-chip SRAM and a 2 MB internal flash memory.

For development, the device includes a calibration bus that is accessible only when using the Freescale VertiCal Calibration System.

## 1.3 Device feature summary

Table 1 summarizes the MPC5642A features and compares them to those of the MPC5644A.

|     | Feature                      | MPC5642A    | MPC5644A        |  |  |  |

|-----|------------------------------|-------------|-----------------|--|--|--|

| Pro | ocess                        | 90          | nm              |  |  |  |

| Co  | re                           | e20         | )0z4            |  |  |  |

|     | SIMD                         | Y           | es              |  |  |  |

|     | VLE                          | Y           | es              |  |  |  |

|     | Cache                        | 8 KB in:    | struction       |  |  |  |

|     | Non-Maskable Interrupt (NMI) | NMI and Cri | tical Interrupt |  |  |  |

|     | MMU                          | 24-entry    |                 |  |  |  |

|     | MPU                          | 16-6        | entry           |  |  |  |

|     | Crossbar switch              | 4 × 4       | 5 × 4           |  |  |  |

|     | Core performance             | 0–150       | ) MHz           |  |  |  |

| Wi  | ndowing software watchdog    | Y           | es              |  |  |  |

| Co  | re Nexus                     | Clas        | ss 3+           |  |  |  |

| SF  | AM                           | 128 KB      | 192 KB          |  |  |  |

| Fla | sh                           | 2 MB        | 4 MB            |  |  |  |

| Fla | sh fetch accelerator         | 4 × 128-bit | 4 × 256-bit     |  |  |  |

### Table 1. MPC5642A device feature summary (continued)

| Feature         | MPC5642A                                                                                                  | MPC5644A                                                                                                  |

|-----------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| CRC             | Ye                                                                                                        | es                                                                                                        |

| FMPLL           | Ye                                                                                                        | es                                                                                                        |

| VRC             | Ye                                                                                                        | es                                                                                                        |

| Supplies        | 5 V, 3                                                                                                    | 9.3 V <sup>2</sup>                                                                                        |

| Low-power modes |                                                                                                           | mode<br>mode                                                                                              |

| Packages        | 176 LQFP <sup>3</sup><br>208 MAPBGA <sup>3,4</sup><br>324 TEPBGA <sup>5</sup><br>496-pin CSP <sup>6</sup> | 176 LQFP <sup>3</sup><br>208 MAPBGA <sup>3,4</sup><br>324 TEPBGA <sup>5</sup><br>496-pin CSP <sup>6</sup> |

<sup>1</sup> 197 interrupt vectors are reserved.

$^2\ 5$  V single supply only for 176 LQFP

<sup>3</sup> Pinout compatible with Freescale's MPC5634M devices

<sup>4</sup> Pinout compatible with Freescale's MPC5534

<sup>5</sup> Ballmap upwardly compatible with the standardized package ballmap used for various Freescale MPC563xM family members

<sup>6</sup> For Freescale VertiCal Calibration System only

## 1.4 Block diagram

Figure 1 shows a top-level block diagram of the MPC5642A series.

Introduction

- Second time base counter can work as a continuous angle counter, enabling angle based applications to match angle instead of time

- Both time bases can be exported to the eMIOS timer module

- Both time bases visible from the host

- Event-triggered microengine:

- Fixed-length instruction execution in two-system-clock microcycle

- 14 KB of code memory (SCM)

- 3 KB of parameter (data) RAM (SPRAM)

- Parallel execution of data memory, ALU, channel control and flow control sub-instructions in selected combinations

- 32-bit microengine registers and 24-bit wide ALU, with 1 microcycle addition and subtraction, absolute value, bitwise logical operations on 24-bit, 16-bit, or byte operands, single-bit manipulation, shift operations, sign extension and conditional execution

- Additional 24-bit Multiply/MAC/Divide unit which supports all signed/unsigned Multiply/MAC combinations, and unsigned 24-bit divide. The MAC/Divide unit works in parallel with the regular microcode commands.

- Resource sharing features support channel use of common channel registers, memory and microengine time:

- Hardware scheduler works as a "task management" unit, dispatching event service routines by predefined, host-configured priority

- Automatic channel context switch when a "task switch" occurs, that is, one function thread ends and another begins to service a request from other channel: channel-specific registers, flags and parameter base address are automatically loaded for the next serviced channel

- SPRAM shared between host CPU and eTPU2, supporting communication either between channels and host or inter-channel

- Hardware implementation of 4 semaphores support coherent parameter sharing between both eTPU engines

- Dual-parameter coherency hardware support allows atomic access to 2 parameters by host

- Test and development support features:

- Nexus Class 1 debug, supporting single-step execution, arbitrary microinstruction execution, hardware breakpoints and watchpoints on several conditions

- Software breakpoints

- SCM continuous signature-check built-in self test MISC (multiple input signature calculator), runs concurrently with eTPU2 normal operation

## 1.5.13 Reaction module (REACM)

The REACM provides the ability to modulate output signals to manage closed loop control without CPU assistance. It works in conjunction with the eQADC and eTPU2 to increase system performance by removing the CPU from the current control loop.

The REACM has the following features:

- 6 reaction channels with peak and hold control blocks

- Each channel output is a bus of 3 signals, providing ability to control 3 inputs.

- Each channel can implement a peak and hold waveform, making it possible to implement up to six independent peak and hold control channels

Target applications include solenoid control for direct injection systems and valve control in automatic transmissions.

### Pinout and signal description

| VSS     | VSS    | VSS      |         |         |         |         | VRC33    | NC       | NC       | VDDEH6AB | м  |

|---------|--------|----------|---------|---------|---------|---------|----------|----------|----------|----------|----|

| VSS     | VSS    | VSS      |         |         |         |         | NC       | SCI_A_TX | VSS      | NC       | N  |

| VSS     | VSS    | VSS      |         |         |         |         | CAN_C_TX | SCI_A_RX | RSTOUT   | RSTCFG   | Р  |

|         |        |          |         |         |         |         | NC       | NC       | NC       | RESET    | R  |

|         |        |          |         |         |         |         | VSS      | BOOTCFG0 | VSS      | VSS      | т  |

|         |        |          |         |         |         |         | VDDEH6AB | PLLCFG1  | BOOTCFG1 | EXTAL    | U  |

|         |        |          |         |         |         |         | SCI_C_RX | CAN_C_RX | PLLREF   | XTAL     | v  |

| ETPUA1  | EMIOS1 | VDDEH4AB | EMIOS8  | EMIOS15 | EMIOS16 | EMIOS23 | SCI_C_TX | VDD      | CAN_B_RX | VDDPLL   | w  |

| ETPUA0  | EMIOS2 | EMIOS5   | EMIOS9  | EMIOS14 | EMIOS17 | EMIOS22 | CAN_A_RX | VSS      | VDD      | CAN_B_TX | Y  |

| EMIOS0  | EMIOS3 | EMIOS6   | EMIOS10 | EMIOS13 | EMIOS18 | EMIOS21 | VDDEH4AB | WKPCFG   | VSS      | VDD      | AA |

| TCRCLKA | EMIOS4 | EMIOS7   | EMIOS11 | EMIOS12 | EMIOS19 | EMIOS20 | CAN_A_TX | SCI_B_RX | SCI_B_TX | VSS      | AB |

| 12      | 13     | 14       | 15      | 16      | 17      | 18      | 19       | 20       | 21       | 22       |    |

Figure 7. 324-pin TEPBGA package ballmap (southeast, viewed from above)

### Table 3. MPC5642A signal properties (continued)

Pinout and signal description

| Name <sup>1</sup>                | Function <sup>2</sup>                                              | P/A/G <sup>3</sup> | PCR                      | PCR <sup>5</sup>  | I/O                | Voltage <sup>6</sup> / | Sta          | Package pin No. |     |     |     |

|----------------------------------|--------------------------------------------------------------------|--------------------|--------------------------|-------------------|--------------------|------------------------|--------------|-----------------|-----|-----|-----|

| Name <sup>1</sup>                | Function-                                                          | P/A/G              | PA<br>field <sup>4</sup> | PCR°              | type               | Pad type <sup>7</sup>  | During reset | After reset     | 176 | 208 | 324 |

|                                  |                                                                    |                    |                          | N                 | EXUS <sup>13</sup> |                        |              |                 |     |     |     |

| EVTI                             | Nexus event in                                                     | Р                  | 01                       | 231               | I                  | VDDEH7 /<br>MultiV     | — / Up       | EVTI / Up       | 116 | E15 | H20 |

| EVTO <sup>14</sup>               | Nexus event out                                                    | Р                  | 01                       | 227               | 0                  | VDDEH7 /<br>MultiV     | ABR/Up       | EVTO / —        | 120 | D15 | G20 |

| МСКО                             | Nexus message clock out                                            | Р                  | —                        | 219 <sup>11</sup> | 0                  | VRC33 /<br>Fast        | _            | МСКО / —        | 14  | F15 | F1  |

| MDO[0]                           | Nexus message data out                                             | Р                  | 01                       | 220               | 0                  | VRC33 /<br>Fast        | _            | MDO[0] / —      | 17  | A14 | F3  |

| MDO[1]                           | Nexus message data out                                             | Р                  | 01                       | 221               | 0                  | VRC33 /<br>Fast        | _            | MDO[1] /        | 18  | B14 | G2  |

| MDO[2]                           | Nexus message data out                                             | Р                  | 01                       | 222               | 0                  | VRC33 /<br>Fast        | _            | MDO[2] /        | 19  | A13 | G3  |

| MDO[3]                           | Nexus message data out                                             | Р                  | 01                       | 223               | 0                  | VRC33 /<br>Fast        | _            | MDO[3] / —      | 20  | B13 | G4  |

| MDO[4]<br>ETPUA2_O<br>GPIO[75]   | Nexus message data out<br>eTPU A channel (output only)<br>GPIO     | P<br>A1<br>G       | 01<br>10<br>00           | 75                | 0<br>0<br>I/0      | VDDEH7 /<br>MultiV     | —            | _/_             | 126 | P10 | B19 |

| MDO[5]<br>ETPUA4_O<br>GPIO[76]   | Nexus message data out<br>eTPU A channel (output only)<br>GPIO     | P<br>A1<br>G       | 01<br>10<br>00           | 76                | 0<br>0<br>I/0      | VDDEH7 /<br>MultiV     | —            | _/_             | 129 | T10 | B20 |

| MDO[6]<br>ETPUA13_0<br>GPIO[77]  | Nexus message data out<br>eTPU A channel (output only)<br>GPIO     | P<br>A1<br>G       | 01<br>10<br>00           | 77                | 0<br>0<br>I/O      | VDDEH7 /<br>MultiV     | —            | _/_             | 135 | T11 | C18 |

| MDO[7]<br>ETPUA19_O<br>GPIO[78]  | Nexus message data out<br>eTPU A channel (output only)<br>GPIO     | P<br>A1<br>G       | 01<br>10<br>00           | 78                | 0<br>0<br>I/O      | VDDEH7 /<br>MultiV     | —            | _/_             | 136 | N11 | B18 |

| MDO[8]<br>ETPUA21_O<br>GPIO[79]  | Nexus message data out<br>eTPU A channel (output only)<br>GPIO     | P<br>A1<br>G       | 01<br>10<br>00           | 79                | 0<br>0<br>I/0      | VDDEH7 /<br>MultiV     | —            | _/_             | 137 | P11 | A18 |

| MDO[9]<br>ETPUA25_O<br>PIO[80]   | Nexus message data out<br>eTPU A channel (output only)<br>GPIO     | P<br>A1<br>G       | 01<br>10<br>00           | 80                | 0<br>0<br>I/0      | VDDEH7 /<br>MultiV     | _            | _/_             | 139 | T7  | D18 |

| MDO[10]<br>ETPUA27_O<br>GPIO[81] | Nexus message data out<br>eTPU A channel (output only)<br>GPIO     | P<br>A1<br>G       | 01<br>10<br>00           | 81                | 0<br>0<br>I/0      | VDDEH7 /<br>MultiV     | _            | _/_             | 134 | R10 | A19 |

| MDO[11]<br>ETPUA29_0<br>GPIO[82] | Nexus message data out<br>eTPU A channel (output only)<br>GPIO[82] | P<br>A1<br>G       | 01<br>10<br>00           | 82                | 0<br>0<br>I/0      | VDDEH7 /<br>MultiV     | _            | _/_             | 124 | P9  | C19 |

48

- <sup>7</sup> See Table 4 for details on pad types.

- <sup>8</sup> The Status During Reset pin is sampled after the internal POR is negated. Prior to exiting POR, the signal has a high impedance. Terminology is O (output), I (input), Up (weak pull up enabled), Down (weak pull down enabled), Low (output driven low), High (output driven high). A dash for the function in this column denotes that both the input and output buffer are turned off. The signal name to the left or right of the slash indicates the pin is enabled.

- <sup>9</sup> When used as ETRIG, this pin must be configured as an input. For GPIO it can be configured either as an input or output.

- <sup>10</sup> Maximum frequency is 50 kHz

- <sup>11</sup> PCR219 controls two different pins: MCKO and GPIO[219]. Please refer to Pad Configuration Register 219 section in SIU chapter of device reference manual for details.

- <sup>12</sup> On 176 LQFP and 208 MAPBGA packages, this pin is tied low internally.

- <sup>13</sup> These pins are selected by asserting JCOMP and configuring the NPC. SIU values have no effect on the function of this pin once enabled.

- <sup>14</sup> The BAM uses this pin to select if auto baud rate is on or off.

<sup>15</sup> Output only

- <sup>16</sup> This signal name is used to support legacy naming.

- <sup>17</sup> Do not use VRC33 to drive external circuits.

- <sup>18</sup> VDDEH1A, VDDEH1B and VDDEH1AB are shorted together in all production packages. The separation of the signal names is present to support legacy naming, however they should be considered as the same signal in this document.

- <sup>19</sup> VDDEH4, VDDEH4A, VDDEH4B and VDDEH4AB are shorted together in all production packages. The separation of the signal names is present to support legacy naming, however they should be considered as the same signal in this document.

- <sup>20</sup> VDDEH6, VDDEH6A, VDDEH6B and VDDEH6AB are shorted together in all production packages. The separation of the signal names is present to support legacy naming, however they should be considered as the same signal in this document.

- <sup>21</sup> VDDEH7, VDDEH7A and VDDE7B are shorted together in all production packages. The separation of the signal names is present to support legacy naming, however they should be considered as the same signal in this document.

This section contains detailed information on power considerations, DC/AC electrical characteristics, and AC timing specifications for the MPC5642A series of MCUs.

The electrical specifications are preliminary and are from previous designs, design simulations, or initial evaluation. These specifications may not be fully tested or guaranteed at this early stage of the product life cycle, however for production silicon these specifications will be met. Finalized specifications will be published after complete characterization and device qualifications have been completed.

In the tables where the device logic provides signals with their respective timing characteristics, the symbol "CC" for Controller Characteristics is included in the Symbol column.

In the tables where the external system must provide signals with their respective timing characteristics to the device, the symbol "SR" for System Requirement is included in the Symbol column.

## 3.1 Parameter classification

The electrical parameters shown in this supplement are guaranteed by various methods. To give the customer a better understanding, the classifications listed in Table 7 are used and the parameters are tagged accordingly in the tables where appropriate.

| Classification tag | Tag description                                                                                                                                                                                                        |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Р                  | Those parameters are guaranteed during production testing on each individual device.                                                                                                                                   |

| С                  | Those parameters are achieved by the design characterization by measuring a statistically relevant sample size across process variations.                                                                              |

| Т                  | Those parameters are achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted. All values shown in the typical column are within this category. |

| D                  | Those parameters are derived mainly from simulations.                                                                                                                                                                  |

### Table 7. Parameter classifications

### NOTE

The classification is shown in the column labeled "C" in the parameter tables where appropriate.

| ID | Name       |    | С | Parameter                                                                  |                    | Value     |                    | Unit |

|----|------------|----|---|----------------------------------------------------------------------------|--------------------|-----------|--------------------|------|

| טו | Name       |    | C | Parameter                                                                  | Min                | Тур       | Max                | Unit |

| 5d | ldd3p3     | СС | С | Voltage regulator 3.3 V maximum DC output current                          | 80                 | _         | —                  | mA   |

| 5e | Vdd33 ILim | СС | С | Voltage regulator 3.3 V DC current limit                                   | —                  | 130       | _                  | mA   |

| 6  | Lvi3p3     | СС | С | Nominal LVI for rising 3.3 V supply <sup>6</sup>                           | —                  | 3.090     | _                  | V    |

| 6a | _          | сс | С | Variation of LVI for rising 3.3 V supply at power-on reset <sup>7</sup>    | Lvi3p3<br>- 6%     | Lvi3p3    | Lvi3p3<br>+ 6%     | V    |

| 6b | _          | СС | С | Variation of LVI for rising 3.3 V supply after power-on reset <sup>7</sup> | Lvi3p3<br>– 3%     | Lvi3p3    | Lvi3p3<br>+ 3%     | V    |

| 6c | _          | СС | С | Trimming step LVI 3.3 V                                                    | —                  | 20        | _                  | mV   |

| 6d | Lvi3p3_h   | СС | С | LVI 3.3 V hysteresis                                                       | —                  | 60        | _                  | mV   |

| 7  | Por3.3V_r  | СС | С | Nominal POR for rising 3.3 V supply <sup>8</sup>                           | —                  | 2.07      | _                  | V    |

| 7a | _          | сс | С | Variation of POR for rising 3.3 V supply                                   | Por3.3V_r -<br>35% | Por3.3V_r | Por3.3V_r<br>+ 35% | V    |

| 7b | Por3.3V_f  | СС | С | Nominal POR for falling 3.3 V supply                                       | —                  | 1.95      | _                  | V    |

| 7c | —          | сс | С | Variation of POR for falling 3.3 V supply                                  | Por3.3V_f<br>- 35% | Por3.3V_f | Por3.3V_f<br>+ 35% | V    |

| 8  | Lvi5p0     | СС | С | Nominal LVI for rising 5 V VDDREG supply                                   |                    | 4.290     | _                  | V    |

| 8a | —          | сс | С | Variation of LVI for rising 5 V VDDREG supply at power-on reset            | Lvi5p0<br>- 6%     | Lvi5p0    | Lvi5p0<br>+ 6%     | V    |

| 8b | —          | СС | С | Variation of LVI for rising 5 V VDDREG supply power-on reset               | Lvi5p0<br>- 3%     | Lvi5p0    | Lvi5p0<br>+ 3%     | V    |

| 8c | —          | СС | С | Trimming step LVI 5 V                                                      | —                  | 20        | _                  | mV   |

| 8d | Lvi5p0_h   | СС | С | LVI 5 V hysteresis                                                         | —                  | 60        | —                  | mV   |

| 9  | Por5V_r    | СС | С | Nominal POR for rising 5 V VDDREG supply                                   | —                  | 2.67      | —                  | V    |

| 9a | _          | СС | С | Variation of POR for rising 5 V VDDREG supply                              | Por5V_r<br>- 35%   | Por5V_r   | Por5V_r<br>+ 35%   | V    |

| 9b | Por5V_f    | сс | С | Nominal POR for falling 5 V VDDREG supply                                  |                    | 2.47      | —                  | V    |

| 9c | _          | сс | С | Variation of POR for falling 5 V VDDREG supply                             | Por5V_f<br>- 35%   | Por5V_f   | Por5V_f<br>+ 35%   | V    |

<sup>1</sup> Using external ballast transistor.

<sup>2</sup> Min range is extended to 10% since Lvi1p2 is reprogrammed from 1.2 V to 1.16 V after power-on reset.

<sup>3</sup> LVI for falling supply is calculated as LVI rising – LVI hysteresis.

<sup>4</sup> Lvi1p2 tracks DC target variation of internal V<sub>DD</sub> regulator. Minimum and maximum Lvi1p2 correspond to minimum and maximum V<sub>DD</sub> DC target respectively.

<sup>5</sup> With internal load up to Idd3p3

$^{6}\,$  The Lvi3p3 specs are also valid for the V\_{\rm DDEH}\,\rm LVI

<sup>7</sup> Lvi3p3 tracks DC target variation of internal V<sub>DD33</sub> regulator. Minimum and maximum Lvi3p3 correspond to minimum and maximum V<sub>DD33</sub> DC target respectively.

$^{8}\,$  The 3.3V POR specs are also valid for the  $V_{\text{DDEH}}\,\text{POR}$

### 3.6.1 Regulator example

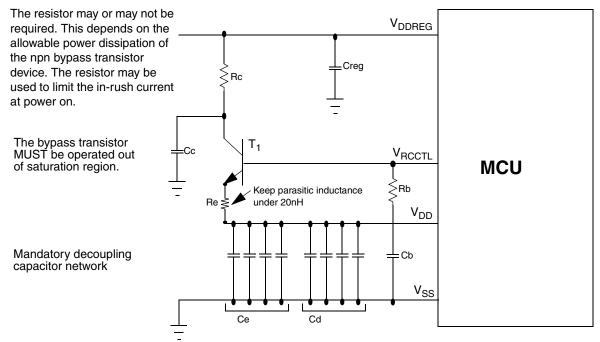

In designs where the MPC5642A microcontroller's internal regulators are used, a ballast is required for generation of the 1.2 V internal supply. No ballast is required when an external 1.2 V supply is used.

VRCCTL capacitor and resistor is required

Figure 8. Core voltage regulator controller external components preferred configuration

Table 16. MPC5642A External network specification

| External Network<br>Parameter      | Min          | Тур          | Max             | Comment                  |

|------------------------------------|--------------|--------------|-----------------|--------------------------|

| Τ1                                 | _            | _            | _               | NJD2873 or BCP68<br>only |

| Cb                                 | 1.1 μF       | 2.2μF        | 2.97μF          | X7R,-50%/+35%            |

| Се                                 | 3*2.35μF+5μF | 3*4.7μF+10μF | 3*6.35μF+13.5μF | X7R, -50%/+35%           |

| Equivalent ESR of<br>Ce capacitors | 5mΩ          | _            | 50mΩ            | —                        |

| Cd                                 | 4*50nF       | 4*100nF      | 4*135nF         | X7R, -50%/+35%           |

| Rb                                 | 9Ω           | 10Ω          | 11Ω             | +/-10%                   |

| Cumb al                                |                                              | ~                                       | Devenueter                                       | Conditions                                             |      | Value    |                        | Unit |

|----------------------------------------|----------------------------------------------|-----------------------------------------|--------------------------------------------------|--------------------------------------------------------|------|----------|------------------------|------|

| Symbol                                 |                                              | С                                       | Parameter                                        | Conditions _                                           | Min  | Тур      | Max                    | Unit |

| I <sub>DD</sub> +I <sub>DDPLL</sub>    | CC                                           | Ρ                                       | Operating current 1.2 V supplies                 | V <sub>DD</sub> @1.32 V<br>@ 80 MHz                    | —    | _        | 300                    | mA   |

|                                        |                                              | Ρ                                       |                                                  | V <sub>DD</sub> @ 1.32 V<br>@ 120 MHz                  | —    | _        | 360                    | mA   |

|                                        |                                              | Ρ                                       |                                                  | V <sub>DD</sub> @ 1.32 V<br>@ 150 MHz                  | —    | _        | 400                    | mA   |

| I <sub>DDSTBY</sub> Co                 | сс                                           | Т                                       | Operating current<br>0.95-1.2 V                  | V <sub>STBY</sub> at 55 °C                             | _    | 35       | 100                    | μA   |

|                                        |                                              | Т                                       | Operating current<br>2–5.5 V                     | V <sub>STBY</sub> at 55 °C                             | —    | 45       | 110                    | μA   |

| I <sub>DDSTBY27</sub>                  | CC                                           | Ρ                                       | Operating current<br>0.95-1.2 V                  | V <sub>STBY</sub> 27 °C                                | —    | 25       | 90                     | μA   |

|                                        |                                              | Ρ                                       | Operating current<br>2-5.5 V                     | V <sub>STBY</sub> 27 °C                                | _    | 35       | 100                    | μA   |

| I <sub>DDSTBY150</sub>                 | 0.95-1.2 V<br>P Operating current<br>2–5.5 V |                                         | V <sub>STBY</sub> 150 °C                         | _                                                      | 790  | 2000     | μA                     |      |

|                                        |                                              | V <sub>STBY</sub> at 150 <sup>o</sup> C | _                                                | 760                                                    | 2000 | μA       |                        |      |

| I <sub>DDPLL</sub>                     | СС                                           | Ρ                                       | Operating current 1.2 V<br>supplies              | V <sub>DDPLL</sub> , 80 MHz,<br>V <sub>DD</sub> =1.2 V | _    | _        | 15                     | mA   |

| IDDSLOW                                | CC                                           | С                                       | V <sub>DD</sub> low-power mode                   | Slow mode <sup>12</sup>                                | _    | _        | 191                    | mA   |

| DDSTOP                                 |                                              | С                                       | operating current @ 1.32 V                       | Stop mode <sup>13</sup>                                | _    | —        | 190                    |      |

| I <sub>DD33</sub>                      | CC                                           | Р                                       | Operating current 3.3 V supplies                 | V <sub>RC33</sub> <sup>2</sup>                         | _    | -        | 60                     | mA   |

| I <sub>DDA</sub>                       | CC                                           | Ρ                                       | Operating current 5.0 V                          | V <sub>DDA</sub>                                       | _    | -        | 30.0                   | mA   |

| I <sub>REF</sub><br>I <sub>DDREG</sub> |                                              | Ρ                                       | supplies                                         | Analog reference<br>supply current<br>(transient)      | _    | _        | 1.0                    |      |

|                                        |                                              | Р                                       |                                                  | V <sub>DDREG</sub>                                     | _    | _        | 70 <sup>14</sup>       |      |

| I <sub>DDH1</sub>                      | CC                                           | Р                                       | Operating current V <sub>DDE</sub> <sup>15</sup> | V <sub>DDEH1</sub>                                     | _    | _        | See note <sup>15</sup> | mA   |

| I <sub>DDH4</sub>                      |                                              | Р                                       | supplies                                         | V <sub>DDEH4</sub>                                     | _    | _        | 1                      |      |

| I <sub>DDH6</sub><br>I <sub>DDH7</sub> |                                              | Ρ                                       |                                                  | V <sub>DDEH6</sub>                                     | _    | -        | 1                      |      |

| I <sub>DD7</sub><br>I <sub>DDH9</sub>  |                                              | Ρ                                       |                                                  | V <sub>DDEH7</sub>                                     |      | -        | 1                      |      |

| I <sub>DD12</sub>                      |                                              | Ρ                                       |                                                  | V <sub>DDE7</sub>                                      | _    | -        | 1                      |      |

|                                        |                                              | Ρ                                       |                                                  | V <sub>DDEH9</sub>                                     |      | -        | 1                      |      |

|                                        |                                              | Р                                       |                                                  | V <sub>DDE12</sub>                                     | _    | <u> </u> | 1                      |      |

| Symbol                                             |    | с | Parameter                                                          | Conditions                                                                         |       | Value   |       | Unit |

|----------------------------------------------------|----|---|--------------------------------------------------------------------|------------------------------------------------------------------------------------|-------|---------|-------|------|

| Symbol                                             |    |   | Falameter                                                          | Conditions                                                                         | Min   | Тур Мах |       | Onit |

| R <sub>PUPD100K</sub>                              | SR | С | Weak pull-up/down resistance <sup>21</sup> , 100 k $\Omega$ option | —                                                                                  | 65    | _       | 140   | kΩ   |

| R <sub>PUPD5K</sub>                                | SR | С | Weak pull-up/down                                                  | 5 V ± 10% supply                                                                   | 1.4   | _       | 5.2   | kΩ   |

|                                                    |    | С | resistance <sup>21</sup> , 5 k $\Omega$ option                     | 3.3 V ± 10% supply                                                                 | 1.7   | _       | 7.7   |      |

| R <sub>PUPD5K</sub>                                | SR | С | Weak Pull-Up/Down<br>Resistance <sup>21</sup> ,<br>5 kΩ Option     | 5 V $\pm$ 5% supply                                                                | 1.4   | _       | 7.5   | kΩ   |

| R <sub>PUPDMTCH</sub>                              | CC | С | Pull-up/Down<br>Resistance matching<br>ratios (100K/200K)          | Pull-up and<br>pull-down<br>resistances both<br>enabled and<br>settings are equal. | -2.5  | _       | 2.5   | %    |

| T <sub>A</sub> (T <sub>L</sub> to T <sub>H</sub> ) | SR | Ρ | Operating temperature<br>range - ambient<br>(packaged)             | _                                                                                  | -40.0 |         | 125.0 | °C   |

| _                                                  | SR | D | Slew rate on power supply pins                                     | —                                                                                  |       | _       | 25    | V/ms |

| Table 20. DC electrica | l specifications <sup>1</sup> | (continued) |

|------------------------|-------------------------------|-------------|

|------------------------|-------------------------------|-------------|

<sup>1</sup> These specifications are design targets and subject to change per device characterization.

<sup>2</sup> These specifications apply when V<sub>RC33</sub> is supplied externally, after disabling the internal regulator (V<sub>DDREG</sub> = 0).

<sup>3</sup> ADC is functional with 4 V  $\leq$  V<sub>DDA</sub>  $\leq$  4.75 V but with derated accuracy. This means the ADC will continue to function at full speed with no undesirable behavior, but the accuracy will be degraded.

- <sup>4</sup> The V<sub>DDF</sub> supply is connected to V<sub>DD</sub> in the package substrate. This specification applies to calibration package devices only.

- $^{5}$  V<sub>FLASH</sub> is available in the calibration package only.

- <sup>6</sup> Regulator is functional, with derated performance, with supply voltage down to 4.0 V

- <sup>7</sup> Multi-voltage power supply cannot be below 4.5 V when in low-swing mode

- <sup>8</sup> The slew rate (SRC) setting must be 0b11 when in low-swing mode.

- <sup>9</sup> While in low-swing mode there are no restrictions in transitioning to high-swing mode.

- <sup>10</sup> Pin in low-swing mode can accept a 5 V input

- $^{11}$  All V<sub>OI</sub> /V<sub>OH</sub> values 100% tested with  $\pm$  2 mA load except where otherwise noted

- <sup>12</sup> Bypass mode, system clock @ 1 MHz (using system clock divider), PLL shut down, CPU running simple executive code, 4 x ADC conversion every 10 ms, 2 x PWM channels @ 1 kHz, all other modules stopped.

- <sup>13</sup> Bypass mode, system clock @ 1 MHz (using system clock divider), CPU stopped, PIT running, all other modules stopped

- <sup>14</sup> If 1.2V and 3.3V internal regulators are on,then iddreg=70mA

If supply is external that is 3.3V internal regulator is off, then iddreg=15mA

- <sup>15</sup> Power requirements for each I/O segment are dependent on the frequency of operation and load of the I/O pins on a particular I/O segment, and the voltage of the I/O segment. See Table 21 for values to calculate power dissipation for specific operation. The total power consumption of an I/O segment is the sum of the individual power consumptions for each pin on the segment.

- $^{16}$  Absolute value of current, measured at  $V_{IL}$  and  $V_{IH}$

- <sup>17</sup> Weak pull-up/down inactive. Measured at  $V_{DDE} = 3.6$  V and  $V_{DDEH} = 5.25$  V. Applies to all digital pad types.

## 3.9.1 I/O pad V<sub>RC33</sub> current specifications

The power consumption of the  $V_{RC33}$  supply is dependent on the usage of the pins on all I/O segments. The power consumption is the sum of all input and output pin  $V_{RC33}$  currents for all I/O segments. The output pin  $V_{RC33}$  current can be calculated from Table 22 based on the voltage, frequency, and load on all fast pins. The input pin  $V_{RC33}$  current can be calculated from Table 22 based on the voltage, frequency, and load on all medium pins. Use linear scaling to calculate pin currents for voltage, frequency, and load on all medium pins. Use linear scaling to calculate pin currents for voltage, frequency, and load on all medium pins.

| Pad type                                | Symbol                    |    | с | Period<br>(ns) | Load <sup>2</sup><br>(pF) | Drive<br>select | I <sub>DD33</sub> Avg<br>(μA) | I <sub>DD33</sub> RMS<br>(μΑ) |

|-----------------------------------------|---------------------------|----|---|----------------|---------------------------|-----------------|-------------------------------|-------------------------------|

|                                         |                           | CC | D | 100            | 50                        | 11              | 0.8                           | 235.7                         |

| Slow                                    | 1                         | СС | D | 200            | 50                        | 01              | 0.04                          | 87.4                          |

| SIOW                                    | <sup>I</sup> DRV_SSR_HV   | CC | D | 800            | 50                        | 00              | 0.06                          | 235.7                         |

|                                         |                           | СС | D | 800            | 200                       | 00              | 0.009                         | 47                            |

|                                         |                           | СС | D | 40             | 50                        | 11              | 2.75                          | 258                           |

| Medium                                  | I .                       | СС | D | 100            | 50                        | 01              | 0.11                          | 76.5                          |

| Medium                                  | IDRV_MSR_HV               | СС | D | 500            | 50                        | 00              | 0.02                          | 56.2                          |

|                                         |                           | CC | D | 500            | 200                       | 00              | 0.01                          | 56.2                          |

|                                         |                           | СС | D | 20             | 50                        | 11              | 33.4                          | 35.4                          |

| MultiV <sup>3</sup>                     |                           | СС | D | 30             | 50                        | 01              | 33.4                          | 34.8                          |

| (High swing mode)                       | <sup>I</sup> DRV_MULTV_HV | СС | D | 117            | 50                        | 00              | 33.4                          | 33.8                          |

|                                         |                           | CC | D | 212            | 200                       | 00              | 33.4                          | 33.7                          |

| MultiV <sup>4</sup><br>(Low swing mode) | IDRV_MULTV_HV             | CC | D | 30             | 30                        | 11              | 33.4                          | 33.7                          |

| Table 22. I/O pac | d V <sub>RC33</sub> average I <sub>DDE</sub> specifications | 1 |

|-------------------|-------------------------------------------------------------|---|

|-------------------|-------------------------------------------------------------|---|

<sup>1</sup> These are typical values that are estimated from simulation and not tested. Currents apply to output pins only.

<sup>2</sup> All loads are lumped.

<sup>3</sup> Average current is for pad configured as output only

<sup>4</sup> In low swing mode, multi-voltage pads must operate in highest slew rate setting, ipp\_sre0 = 1, ipp\_sre1 = 1.

1

## 3.14 Platform flash controller electrical characteristics

Table 31. APC, RWSC, WWSC settings vs. frequency of operation<sup>1</sup>

| Max. Flash Operating<br>Frequency (MHz) <sup>2</sup> | APC <sup>3</sup> | RWSC <sup>3</sup> | WWSC |

|------------------------------------------------------|------------------|-------------------|------|

| 20 MHz                                               | 0b000            | 0b000             | 0b01 |

| 61 MHz                                               | 0b001            | 0b001             | 0b01 |

| 90 MHz                                               | 0b010            | 0b010             | 0b01 |

| 123 MHz                                              | 0b011            | 0b011             | 0b01 |

| 153 MHz                                              | 0b100            | 0b100             | 0b01 |

APC, RWSC and WWSC are fields in the flash memory BIUCR register used to specify wait states for address pipelining and read/write accesses. Illegal combinations exist—all entries must be taken from the same row.

<sup>2</sup> Max frequencies including 2% PLL FM.

<sup>3</sup> APC must be equal to RWSC.

## 3.15 Flash memory electrical characteristics

### Table 32. Flash program and erase specifications<sup>1</sup>

|   | # Symbol C               |    |   |                                           |     |       |                             |                  |      |

|---|--------------------------|----|---|-------------------------------------------|-----|-------|-----------------------------|------------------|------|

| # |                          |    | С | Parameter                                 | Min | Тур   | Initial<br>max <sup>2</sup> | Max <sup>3</sup> | Unit |

| 1 | T <sub>dwprogram</sub>   | СС | С | Double Word (64 bits) Program Time        |     | 30    | _                           | 500              | μs   |

| 2 | T <sub>pprogram</sub>    | СС | С | Page Program Time <sup>4</sup>            | _   | 40    | 160                         | 500              | μs   |

| 3 | T <sub>16kpperase</sub>  | СС | С | 16 KB Block Pre-program and Erase Time    | _   | 250   | 1,000                       | 5,000            | ms   |

| 5 | T <sub>64kpperase</sub>  | СС | С | 64 KB Block Pre-program and Erase Time    | _   | 450   | 1,800                       | 5,000            | ms   |

| 6 | T <sub>128kpperase</sub> | СС | С | 128 KB Block Pre-program and Erase Time   |     | 800   | 2,600                       | 7,500            | ms   |

| 7 | T <sub>256kpperase</sub> | СС | С | 256 KB Block Pre-program and Erase Time   |     | 1,400 | 5,200                       | 15,000           | ms   |

| 8 | T <sub>psrt</sub>        | SR |   | Program suspend request rate <sup>5</sup> | 100 | —     | —                           | —                | μS   |

| 9 | T <sub>esrt</sub>        | SR |   | Erase suspend request rate <sup>6</sup>   | 10  |       |                             |                  | ms   |

<sup>1</sup> Typical program and erase times assume nominal supply values and operation at 25 °C. All times are subject to change pending device characterization.

<sup>2</sup> Initial factory condition: ≤ 100 program/erase cycles, 25 °C, typical supply voltage, 80 MHz minimum system frequency.

<sup>3</sup> The maximum erase time occurs after the specified number of program/erase cycles. This maximum value is characterized but not guaranteed.

<sup>4</sup> Page size is 128 bits (4 words)

<sup>5</sup> Time between program suspend resume and the next program suspend request.

<sup>6</sup> Time between erase suspend resume and the next erase suspend request.

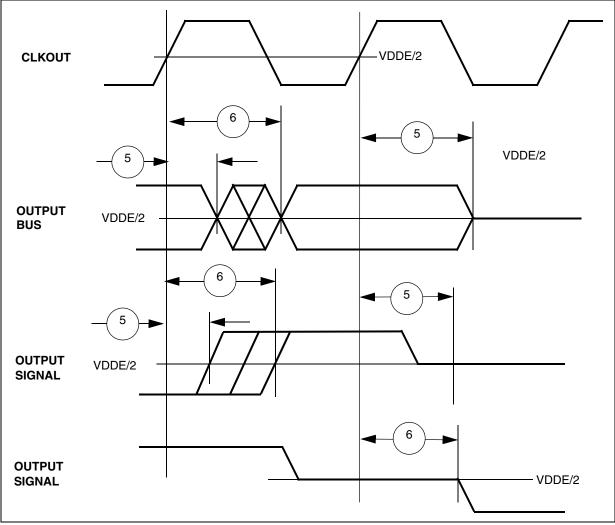

Figure 20. Synchronous output timing

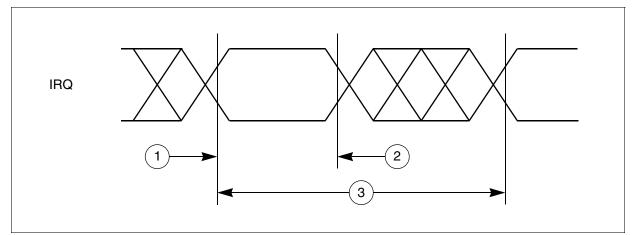

## 3.17.5 External interrupt timing (IRQ pin)

Table 42. External interrupt timing<sup>1</sup>

| #        | Symbol            | Characteristic                     | Va  | lue | Unit             |

|----------|-------------------|------------------------------------|-----|-----|------------------|

| # Symbol |                   | Characteristic                     | Min | Max | Offic            |

| 1        | t <sub>IPWL</sub> | IRQ Pulse Width Low                | 3   | _   | t <sub>CYC</sub> |

| 2        | t <sub>IPWH</sub> | IRQ Pulse Width High               | 3   | _   | t <sub>CYC</sub> |

| 3        | t <sub>ICYC</sub> | IRQ Edge to Edge Time <sup>2</sup> | 6   | —   | t <sub>CYC</sub> |

<sup>1</sup> IRQ timing specified at  $V_{DD}$  = 1.14 V to 1.32 V,  $V_{DDEH}$  = 3.0 V to 5.25 V,  $V_{DD33}$  and  $V_{DDSYN}$  = 3.0 V to 3.6 V,  $T_A = T_L$  to  $T_H$ .

<sup>2</sup> Applies when IRQ pins are configured for rising edge or falling edge events, but not both.

Figure 23. External interrupt timing

## 3.17.6 eTPU timing

### Table 43. eTPU timing<sup>1</sup>

| # Symbol |                   | Characteristic                                                 | Value   | Unit |                  |

|----------|-------------------|----------------------------------------------------------------|---------|------|------------------|

| π        | Symbol            | Unaracteristic                                                 | Min Max | onn  |                  |

| 1        | t <sub>ICPW</sub> | eTPU Input Channel Pulse Width                                 | 4       | _    | t <sub>CYC</sub> |

| 2        | t <sub>OCPW</sub> | t <sub>OCPW</sub> eTPU Output Channel Pulse Width <sup>2</sup> |         | _    | t <sub>CYC</sub> |

<sup>1</sup> eTPU timing specified at  $V_{DD}$  = 1.14 V to 1.32 V,  $V_{DDEH}$  = 3.0 V to 5.25 V,  $V_{DD33}$  and  $V_{DDSYN}$  = 3.0 V to 3.6 V,  $T_A = T_L$  to  $T_H$ , and  $C_L$  = 50 pF with SRC = 0b00.

<sup>2</sup> This specification does not include the rise and fall times. When calculating the minimum eTPU pulse width, include the rise and fall times defined in the slew rate control fields (SRC) of the pad configuration registers (PCR).

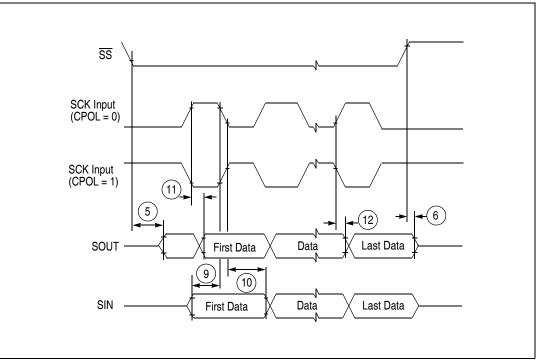

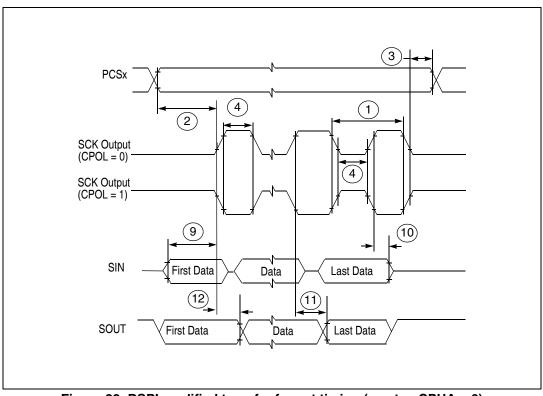

Figure 27. DSPI classic SPI timing (slave, CPHA = 1)

Figure 28. DSPI modified transfer format timing (master, CPHA = 0)

## 3.17.10 FlexCAN system clock source

### Table 48. FlexCAN engine system clock divider threshold

| # | Symbol              | Characteristic                        | Value | Unit |

|---|---------------------|---------------------------------------|-------|------|

| 1 | f <sub>CAN_TH</sub> | FlexCAN engine system clock threshold | 100   | MHz  |

### Table 49. FlexCAN engine system clock divider

| System frequency      | Required SIU_SYSDIV[CAN_SRC] value |

|-----------------------|------------------------------------|

| ≤ f <sub>CAN_TH</sub> | 0 <sup>1,2</sup>                   |

| > f <sub>CAN_TH</sub> | 1 <sup>2,3</sup>                   |

<sup>1</sup> Divides system clock source for FlexCAN engine by 1

<sup>2</sup> System clock is only selected for FlexCAN when CAN\_CR[CLK\_SRC] = 1

<sup>3</sup> Divides system clock source for FlexCAN engine by 2

# 4 Packages

# 4.1 Package mechanical data

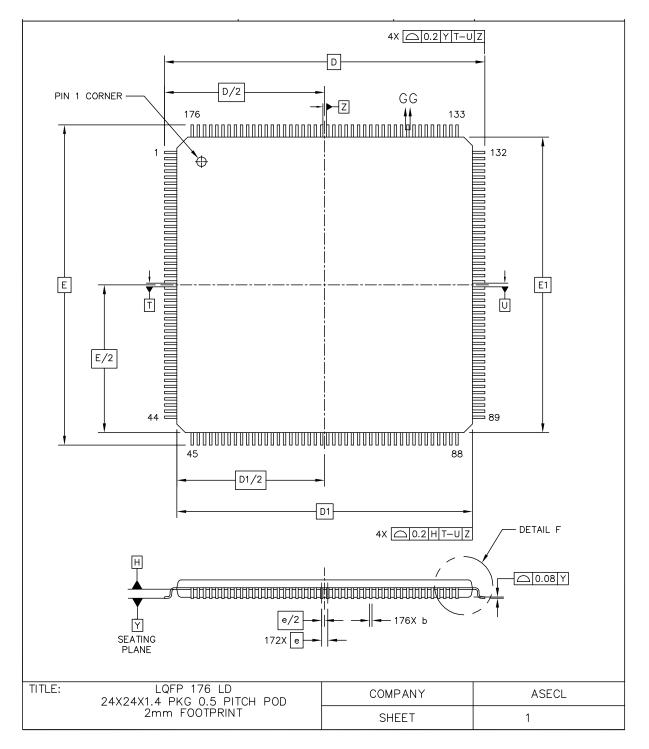

## 4.1.1 176 LQFP

**Document revision history**