Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2011110                    |                                                             |

|----------------------------|-------------------------------------------------------------|

| Product Status             | Active                                                      |

| Core Processor             | e200z4                                                      |

| Core Size                  | 32-Bit Single-Core                                          |

| Speed                      | 80MHz                                                       |

| Connectivity               | CANbus, EBI/EMI, LINbus, SCI, SPI                           |

| Peripherals                | DMA, POR, PWM, WDT                                          |

| Number of I/O              | 151                                                         |

| Program Memory Size        | 2MB (2M x 8)                                                |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 128K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.14V ~ 5.25V                                               |

| Data Converters            | A/D 40x12b                                                  |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                          |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 324-BBGA                                                    |

| Supplier Device Package    | 324-PBGA (23x23)                                            |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=spc5642af2mvz3 |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Addendum List for Revision 3.1

Table 1. MPC5642A Rev 3.1 Addendum

| Location | Description                                                                                                                                         |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

|          | In "Temperature Sensor Electrical Characteristics" table, update the Min and Max value of<br>"Accuracy" parameter to -20°C and +20°C, respectively. |

# 2 Revision History

Table 2 provides a revision history for this datasheet addendum document.

### Table 2. Revision History Table

| Rev. Number | Substantive Changes | Date of Release |

|-------------|---------------------|-----------------|

| 1.0         | Initial release.    | 12/2014         |

# 1.5.4 Interrupt controller (INTC)

The INTC provides priority-based preemptive scheduling of interrupt requests, suitable for statically scheduled hard real-time systems.

For high priority interrupt requests, the time from the assertion of the interrupt request from the peripheral to when the processor is executing the interrupt service routine (ISR) has been minimized. The INTC provides a unique vector for each interrupt request source for quick determination of which ISR needs to be executed. It also provides an ample number of priorities so that lower priority ISRs do not delay the execution of higher priority ISRs. To allow the appropriate priorities for each source of interrupt request, the priority of each interrupt request is software configurable.

When multiple tasks share a resource, coherent accesses to that resource need to be supported. The INTC supports the priority ceiling protocol for coherent accesses. By providing a modifiable priority mask, the priority can be raised temporarily so that all tasks which share the resource cannot preempt each other.

The INTC provides the following features:

- 9-bit vector addresses

- Unique vector for each interrupt request source

- · Hardware connection to processor or read from register

- Each interrupt source can assigned a specific priority by software

- · Preemptive prioritized interrupt requests to processor

- ISR at a higher priority preempts executing ISRs or tasks at lower priorities

- Automatic pushing or popping of preempted priority to or from a LIFO

- · Ability to modify the ISR or task priority to implement the priority ceiling protocol for accessing shared resources

- Low latency—3 clocks from receipt of interrupt request from peripheral to interrupt request to processor

This device also includes a non-maskable interrupt (NMI) pin that bypasses the INTC and multiplexing logic.

## **1.5.5** Memory protection unit (MPU)

The Memory Protection Unit (MPU) provides hardware access control for all memory references generated in a device. Using preprogrammed region descriptors, which define memory spaces and their associated access rights, the MPU concurrently monitors all system bus transactions and evaluates the appropriateness of each transfer. Memory references with sufficient access control rights are allowed to complete; references that are not mapped to any region descriptor or have insufficient rights are terminated with a protection error response.

The MPU has these major features:

- Support for 16 memory region descriptors, each 128 bits in size

- Specification of start and end addresses provide granularity for region sizes from 32 bytes to 4 GB

- MPU is invalid at reset, thus no access restrictions are enforced

- 2 types of access control definitions: processor core bus master supports the traditional {read, write, execute} permissions with independent definitions for supervisor and user mode accesses; the remaining non-core bus masters (eDMA, FlexRay) support {read, write} attributes

- Automatic hardware maintenance of the region descriptor valid bit removes issues associated with maintaining a coherent image of the descriptor

- Alternate memory view of the access control word for each descriptor provides an efficient mechanism to dynamically alter the access rights of a descriptor only

- For overlapping region descriptors, priority is given to permission granting over access denying as this approach

provides more flexibility to system software

- Support for two XBAR slave port connections (SRAM and PBRIDGE)

- For each connected XBAR slave port (SRAM and PBRIDGE), MPU hardware monitors every port access using the preprogrammed memory region descriptors

Introduction

- Second time base counter can work as a continuous angle counter, enabling angle based applications to match angle instead of time

- Both time bases can be exported to the eMIOS timer module

- Both time bases visible from the host

- Event-triggered microengine:

- Fixed-length instruction execution in two-system-clock microcycle

- 14 KB of code memory (SCM)

- 3 KB of parameter (data) RAM (SPRAM)

- Parallel execution of data memory, ALU, channel control and flow control sub-instructions in selected combinations

- 32-bit microengine registers and 24-bit wide ALU, with 1 microcycle addition and subtraction, absolute value, bitwise logical operations on 24-bit, 16-bit, or byte operands, single-bit manipulation, shift operations, sign extension and conditional execution

- Additional 24-bit Multiply/MAC/Divide unit which supports all signed/unsigned Multiply/MAC combinations, and unsigned 24-bit divide. The MAC/Divide unit works in parallel with the regular microcode commands.

- Resource sharing features support channel use of common channel registers, memory and microengine time:

- Hardware scheduler works as a "task management" unit, dispatching event service routines by predefined, host-configured priority

- Automatic channel context switch when a "task switch" occurs, that is, one function thread ends and another begins to service a request from other channel: channel-specific registers, flags and parameter base address are automatically loaded for the next serviced channel

- SPRAM shared between host CPU and eTPU2, supporting communication either between channels and host or inter-channel

- Hardware implementation of 4 semaphores support coherent parameter sharing between both eTPU engines

- Dual-parameter coherency hardware support allows atomic access to 2 parameters by host

- Test and development support features:

- Nexus Class 1 debug, supporting single-step execution, arbitrary microinstruction execution, hardware breakpoints and watchpoints on several conditions

- Software breakpoints

- SCM continuous signature-check built-in self test MISC (multiple input signature calculator), runs concurrently with eTPU2 normal operation

# 1.5.13 Reaction module (REACM)

The REACM provides the ability to modulate output signals to manage closed loop control without CPU assistance. It works in conjunction with the eQADC and eTPU2 to increase system performance by removing the CPU from the current control loop.

The REACM has the following features:

- 6 reaction channels with peak and hold control blocks

- Each channel output is a bus of 3 signals, providing ability to control 3 inputs.

- Each channel can implement a peak and hold waveform, making it possible to implement up to six independent peak and hold control channels

Target applications include solenoid control for direct injection systems and valve control in automatic transmissions.

Introduction

- Provides temperature of silicon as an analog value

- Read using an internal ADC analog channel

- May be read with either ADC

- 2 decimation filters

- Programmable decimation factor (1 to 16)

- Selectable IIR or FIR filter

- Up to 4th order IIR or 8th order FIR

- Programmable coefficients

- Saturated or non-saturated modes

- Programmable Rounding (Convergent; Two's Complement; Truncated)

- Prefill mode to precondition the filter before the sample window opens

- Supports Multiple Cascading Decimation Filters to implement more complex filter designs

- Optional Absolute Integrators on the output of Decimation Filters

- Full duplex synchronous serial interface (SSI) to an external device

- Free-running clock for use by an external device

- Supports a 26-bit message length

- Priority based queues

- Supports 6 queues with fixed priority. When commands of distinct queues are bound for the same ADC, the higher

priority queue is always served first

- Queue\_0 can bypass all prioritization, buffering and abort current conversions to start a Queue\_0 conversion a

deterministic time after the queue trigger

- Supports software and hardware trigger modes to arm a particular queue

- Generates interrupt when command coherency is not achieved

- External hardware triggers

- Supports rising edge, falling edge, high level and low level triggers

- Supports configurable digital filter

# 1.5.15 Deserial serial peripheral interface (DSPI)

The DSPI block provides a synchronous serial interface for communication between the MPC5642A MCU and external devices. The DSPI supports pin count reduction through serialization and deserialization of eTPU and eMIOS channels and memory-mapped registers. The channels and register content are transmitted using a SPI-like protocol. This SPI-like protocol is completely configurable for baud rate, polarity and phase, frame length, chip select assertion, etc. Each bit in the frame may be configured to serialize either eTPU channels, eMIOS channels or GPIO signals. The DSPI can be configured to serialize data to an external device that implements the Microsecond Bus protocol. There are three identical DSPI blocks on the MPC5642A MCU. The DSPI pins support 5 V logic levels or Low Voltage Differential Signalling (LVDS) to improve high speed operation.

DSPI module features include:

- Selectable LVDS pads working at 40 MHz for SOUT and SCK pins for DSPI\_B and DSPI\_C

- Support for downstream Micro Second Channel (MSC) with Timed Serial Bus (TSB) configuration on DSPI\_B and DSPI\_C

- 3 sources of serialized data: eTPU\_A, eMIOS output channels, and memory-mapped register in the DSPI

- 4 destinations for deserialized data: eTPU\_A and eMIOS input channels, SIU external Interrupt input request, memory-mapped register in the DSPI

- 32-bit DSI and TSB modes require 32 PCR registers, 32 GPO and GPI registers in the SIU to select either GPIO, eTPU or eMIOS bits for serialization

- The DSPI module can generate and check parity in a serial frame

## Table 3. MPC5642A signal properties (continued)

| Name <sup>1</sup>                                | Function <sup>2</sup>                                                               | P/A/G <sup>3</sup> | PCR<br>PA                | PCR <sup>5</sup> |                      | Voltage <sup>6</sup> / | Sta           | tus <sup>8</sup> | Pa  | ickage pin | No.  |

|--------------------------------------------------|-------------------------------------------------------------------------------------|--------------------|--------------------------|------------------|----------------------|------------------------|---------------|------------------|-----|------------|------|

|                                                  | Function-                                                                           | P/A/G <sup>o</sup> | field <sup>4</sup>       | PCR°             | type                 | Pad type <sup>7</sup>  | During reset  | After reset      | 176 | 208        | 324  |

| EMIOS6<br>ETPUA6_O<br>GPIO[185]                  | eMIOS channel<br>eTPU A channel (output only)<br>GPIO                               | P<br>A1<br>G       | 01<br>10<br>00           | 185              | I/O<br>O<br>I/O      | VDDEH4 /<br>Slow       | — / Down      | — / Down         | 68  | P7         | AA14 |

| EMIOS7<br>ETPUA7_0<br>GPIO[186]                  | eMIOS channel<br>eTPU A channel (output only)<br>GPIO                               | P<br>A1<br>G       | 01<br>10<br>00           | 186              | I/O<br>O<br>I/O      | VDDEH4 /<br>Slow       | — / Down      | — / Down         | 69  | —          | AB14 |

| EMIOS8<br>ETPUA8_O<br>SCI_B_TX<br>GPIO[187]      | eMIOS channel<br>eTPU A channel (output only)<br>eSCI B transmit<br>GPIO            | P<br>A1<br>A2<br>G | 001<br>010<br>100<br>000 | 187              | I/O<br>O<br>I/O      | VDDEH4 /<br>Slow       | — / Up        | — / Up           | 70  | P8         | W15  |

| EMIOS9<br>ETPUA9_O<br>SCI_B_RX<br>GPIO[188]      | eMIOS channel<br>eTPU A channel (output only)<br>eSCI B receive<br>GPIO             | P<br>A1<br>A2<br>G | 001<br>010<br>100<br>000 | 188              | I/O<br>O<br>I<br>I/O | VDDEH4 /<br>Slow       | — / Up        | — / Up           | 71  | R7         | Y15  |

| EMIOS10<br>DSPI_D_PCS[3]<br>RCH3_B<br>GPIO[189]  | eMIOS channel<br>DSPI D peripheral chip select<br>Reaction channel 3B<br>GPIO       | P<br>A1<br>A2<br>G | 001<br>010<br>100<br>000 | 189              | I/O<br>O<br>O<br>I/O | VDDEH4 /<br>Medium     | — /<br>WKPCFG | — /<br>WKPCFG    | 73  | N8         | AA15 |

| EMIOS11<br>DSPI_D_PCS[4]<br>RCH3_C<br>GPIO[190]  | eMIOS channel<br>DSPI D peripheral chip select<br>Reaction channel 3C<br>GPIO       | P<br>A1<br>A2<br>G | 001<br>010<br>100<br>000 | 190              | I/O<br>O<br>I/O      | VDDEH4 /<br>Medium     | — /<br>WKPCFG | — /<br>WKPCFG    | 75  | R8         | AB15 |

| EMIOS12<br>DSPI_C_SOUT<br>ETPUA27_O<br>GPIO[191] | eMIOS channel<br>DSPI C data output<br>eTPU A channel (output only)<br>GPIO         | P<br>A1<br>A2<br>G | 001<br>010<br>100<br>000 | 191              | I/O<br>O<br>O<br>I/O | VDDEH4 /<br>Medium     | — /<br>WKPCFG | — /<br>WKPCFG    | 76  | N10        | AB16 |

| EMIOS13<br>DSPI_D_SOUT<br>GPIO[192]              | eMIOS channel<br>DSPI D data output<br>GPIO                                         | P<br>A1<br>G       | 01<br>10<br>00           | 192              | I/O<br>O<br>I/O      | VDDEH4 /<br>Medium     | — /<br>WKPCFG | — /<br>WKPCFG    | 77  | Т8         | AA16 |

| EMIOS14<br>IRQ[0]<br>ETPUA29_O<br>GPIO[193]      | eMIOS channel<br>External interrupt request<br>eTPU A channel (output only)<br>GPIO | P<br>A1<br>A2<br>G | 001<br>010<br>100<br>000 | 193              | I/O<br>I<br>O<br>I/O | VDDEH4 /<br>Slow       | — / Down      | — / Down         | 78  | R9         | Y16  |

| EMIOS15<br>IRQ[1]<br>GPIO[194]                   | eMIOS channel<br>External interrupt request<br>GPIO                                 | P<br>A1<br>G       | 01<br>10<br>00           | 194              | I/O<br>I<br>I/O      | VDDEH4 /<br>Slow       | — / Down      | — / Down         | 79  | Т9         | W16  |

| EMIOS16<br>GPIO[195]                             | eMIOS channel<br>GPIO                                                               | P<br>G             | 01<br>00                 | 195              | I/O<br>I/O           | VDDEH4 /<br>Slow       | — / Up        | — / Up           | —   | _          | W17  |

| EMIOS17<br>GPIO[196]                             | eMIOS channel<br>GPIO                                                               | P<br>G             | 01<br>00                 | 196              | I/O<br>I/O           | VDDEH4 /<br>Slow       | — / Up        | — / Up           | -   | —          | ¥17  |

| EMIOS18<br>GPIO[197]                             | eMIOS channel<br>GPIO                                                               | P<br>G             | 01<br>00                 | 197              | I/O<br>I/O           | VDDEH4 /<br>Slow       | — / Up        | — / Up           | -   | _          | AA17 |

| EMIOS19<br>GPIO[198]                             | eMIOS channel<br>GPIO                                                               | P<br>G             | 01<br>00                 | 198              | I/O<br>I/O           | VDDEH4 /<br>Slow       | — /<br>WKPCFG | /<br>WKPCFG      | -   | —          | AB17 |

| Dewer comment | Valtage       | VO nine neward by comment                                                                                                                                                                                                                                                  |  |  |  |  |

|---------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Power segment | Voltage       | I/O pins powered by segment                                                                                                                                                                                                                                                |  |  |  |  |

| VDDE5         | 3.0 V – 3.6 V | ATA[0:15], CLKOUT, ENGCLK                                                                                                                                                                                                                                                  |  |  |  |  |

| VDDE12        | 3.0 V – 3.6 V | CAL_CS0, CAL_CS2, CAL_CS3, CAL_ADDR[12:30], CAL_DATA[0:15],<br>CAL_RD_WR, CAL_WE0, CAL_WE1, CAL_OE, CAL_TS                                                                                                                                                                 |  |  |  |  |

| VDDE-EH       | 3.0 V – 5.5 V | FR_A_TX, FR_A_TX_EN, FR_A_RX, FR_B_TX, FR_B_TX_EN, FR_B_RX                                                                                                                                                                                                                 |  |  |  |  |

| VDDEH1        | 3.3 V – 5.5 V | ETPUA[10:31]                                                                                                                                                                                                                                                               |  |  |  |  |

| VDDEH4        | 3.3 V – 5.5 V | EMIOS[0:23], TCRCLKA, ETPUA[0:9]                                                                                                                                                                                                                                           |  |  |  |  |

| VDDEH6        | 3.3 V – 5.5 V | RESET, RSTOUT, PLLREF, PLLCFG1, RSTCFG, BOOTCFG0, BOOTCFG1,<br>WKPCFG, CAN_A_TX, CAN_A_RX, CAN_B_TX, CAN_B_RX, CAN_C_TX,<br>CAN_C_RX, SCI_A_TX, SCI_A_RX, SCI_B_TX, SCI_B_RX, SCI_C_TX,<br>SCI_C_RX, DSPI_B_SCK, DSPI_B_SIN, DSPI_B_SOUT, DSPI_B_PCS[0:5],<br>EXTAL, XTAL  |  |  |  |  |

| VDDEH7        | 3.3 V – 5.5 V | EMIOS14, EMIOS15, GPIO[98:99], GPIO[203:204], GPIO[206], GPIO[207],<br>GPIO[219], EVTI, EVTO, MDO[4:11], MSEO0, MSEO1, RDY, TCK, TDI, TDO,<br>TMS, JCOMP, DSPI_A_SCK, DSPI_A_SIN, DSPI_A_SOUT, DSPI_A_PCS[0:1],<br>DSPI_A_PCS[4:5], AN12-SDS, AN13-SDO, AN14-SDI, AN15-FCK |  |  |  |  |

| VDDA          | 5.0 V         | AN[0:11], AN[16:39], VRH, VRL, REFBYBC                                                                                                                                                                                                                                     |  |  |  |  |

| VRC33         | 3.3 V         | MCKO, MDO[0:3]                                                                                                                                                                                                                                                             |  |  |  |  |

|               |               | Other power segments                                                                                                                                                                                                                                                       |  |  |  |  |

| VDDREG        | 5.0 V         | —                                                                                                                                                                                                                                                                          |  |  |  |  |

| VRCCTL        | —             | —                                                                                                                                                                                                                                                                          |  |  |  |  |

| VDDPLL        | 1.2 V         | —                                                                                                                                                                                                                                                                          |  |  |  |  |

| VSTBY         | 0.9 V – 6.0 V | —                                                                                                                                                                                                                                                                          |  |  |  |  |

| VSS           |               | —                                                                                                                                                                                                                                                                          |  |  |  |  |

## Table 6. Power/ground segmentation

# 3.2 Maximum ratings

Table 8. Absolute maximum ratings<sup>1</sup>

| Symbol                            |                                                                                                  | Devemeter                                                      | Conditions                           | Va                 | lue                                       | l lait |

|-----------------------------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------|--------------------|-------------------------------------------|--------|

| Symbol                            | Symbol         Parameter           Vpp         SB         1.2 V core supply voltage <sup>2</sup> |                                                                | Conditions                           | Min                | Max                                       | Unit   |

| V <sub>DD</sub>                   | SR                                                                                               | 1.2 V core supply voltage <sup>2</sup>                         |                                      | -0.3               | 1.32                                      | V      |

| V <sub>FLASH</sub>                | SR                                                                                               | Flash core voltage <sup>3,4</sup>                              |                                      | -0.3               | 3.6                                       | V      |

| V <sub>STBY</sub>                 | SR                                                                                               | SRAM standby voltage <sup>5</sup>                              |                                      | -0.3               | 6.0                                       | V      |

| V <sub>DDPLL</sub>                | SR                                                                                               | Clock synthesizer voltage <sup>3</sup>                         |                                      | -0.3               | 1.32                                      | V      |

| V <sub>RC33</sub>                 | SR                                                                                               | Voltage regulator control input voltage <sup>4</sup>           |                                      | -0.3               | 3.6                                       | V      |

| V <sub>DDA</sub>                  | SR                                                                                               | Analog supply voltage <sup>5</sup>                             | Reference to V <sub>SSA</sub>        | -0.3               | 5.5                                       | V      |

| V <sub>DDE</sub>                  | SR                                                                                               | I/O supply voltage <sup>4,6</sup>                              |                                      | -0.3               | 3.6                                       | V      |

| V <sub>DDEH</sub>                 | SR                                                                                               | I/O supply voltage <sup>5,7</sup>                              |                                      | -0.3               | 5.5                                       | V      |

| V <sub>IN</sub>                   | SR                                                                                               | DC input voltage <sup>8</sup>                                  | V <sub>DDEH</sub> powered I/O pads   | -1.0 <sup>10</sup> | V <sub>DDEH</sub> +<br>0.3 V <sup>9</sup> | V      |

|                                   |                                                                                                  |                                                                | V <sub>DDE</sub> powered I/O pads    | -1.0 <sup>14</sup> | V <sub>DDE</sub> +<br>0.3 V <sup>10</sup> |        |

|                                   |                                                                                                  |                                                                | V <sub>DDA</sub> powered I/O pads    | -1.0               | 5.5                                       |        |

| V <sub>DDREG</sub>                | SR                                                                                               | Voltage regulator supply voltage                               |                                      | -0.3               | 5.5                                       | V      |

| V <sub>RH</sub>                   | SR                                                                                               | Analog reference high voltage                                  | Reference to VRL                     | -0.3               | 5.5                                       | V      |

| $V_{SS} - V_{SSA}$                | SR                                                                                               | V <sub>SS</sub> differential voltage                           |                                      | -0.1               | 0.1                                       | V      |

| V <sub>RH</sub> – V <sub>RL</sub> | SR                                                                                               | V <sub>REF</sub> differential voltage                          |                                      | -0.3               | 5.5                                       | V      |

| $V_{RL} - V_{SSA}$                | SR                                                                                               | V <sub>RL</sub> to V <sub>SSA</sub> differential voltage       |                                      | -0.3               | 0.3                                       | V      |

| $V_{SSPLL} - V_{SS}$              | SR                                                                                               | $V_{SSPLL}$ to $V_{SS}$ differential voltage                   |                                      | -0.1               | 0.1                                       | V      |

| I <sub>MAXD</sub>                 | SR                                                                                               | Maximum DC digital input current <sup>11</sup>                 | Per pin, applies to all digital pins | -3                 | 3                                         | mA     |

| I <sub>MAXA</sub>                 | SR                                                                                               | Maximum DC analog input current <sup>12</sup>                  | Per pin, applies to all analog pins  | —                  | 5 <sup>13</sup>                           | mA     |

| TJ                                | SR                                                                                               | Maximum operating temperature range — die junction temperature |                                      | -40.0              | 150.0                                     | °C     |

| T <sub>STG</sub>                  | SR                                                                                               | Storage temperature range                                      |                                      | -55                | 150                                       | °C     |

| T <sub>SDR</sub>                  | SR                                                                                               | Maximum solder temperature <sup>14</sup>                       |                                      | —                  | 260                                       | °C     |

| MSL                               | SR                                                                                               | Moisture sensitivity level <sup>15</sup>                       |                                      | _                  | 3                                         | —      |

<sup>1</sup> Functional operating conditions are given in the DC electrical specifications. Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Stress beyond the listed maxima may affect device reliability or cause permanent damage to the device.

<sup>2</sup> Allowed 2 V for 10 hours cumulative time, remaining time at 1.2 V + 10%

<sup>3</sup> The V<sub>FLASH</sub> supply is connected to V<sub>RC33</sub> in the package substrate. This specification applies to calibration package devices only.

$^4$  Allowed 5.3 V for 10 hours cumulative time, remaining time at 3.3 V + 10%

$^5\,$  Allowed 5.9 V for 10 hours cumulative time, remaining time at 5 V + 10%  $\,$

### Table 25. PLLMRFM electrical specifications<sup>1</sup>

| Cumph              | <b>_</b> ] | с | Parameter                           | Conditions                          | Va       | Value                         |                    |  |

|--------------------|------------|---|-------------------------------------|-------------------------------------|----------|-------------------------------|--------------------|--|

| Symb               | 0I         | C | Parameter                           | Conditions                          | Min      | Max                           | Unit               |  |

| V <sub>ILEXT</sub> | СС         | D | EXTAL input low voltage             | Crystal mode <sup>13</sup>          | -        | Vxtal<br>- 0.4                | V                  |  |

|                    |            | Т |                                     | External reference <sup>13,14</sup> | 0        | V <sub>RC33</sub> /2<br>- 0.4 |                    |  |

|                    | CC         | Т | XTAL load capacitance               | -                                   | 5        | 30                            | pF                 |  |

|                    | CC         | С | XTAL load capacitance <sup>11</sup> | 4 MHz                               | 5        | 30                            | pF                 |  |

|                    |            |   |                                     | 8 MHz                               | 5        | 26                            |                    |  |

|                    |            |   |                                     | 12 MHz                              | 5        | 23                            |                    |  |

|                    |            |   |                                     | 16 MHz                              | 5        | 19                            |                    |  |

|                    |            |   |                                     | 20 MHz                              | 5        | 16                            |                    |  |

|                    |            |   |                                     | 40 MHz                              | 5        | 8                             |                    |  |

| t <sub>lpll</sub>  | CC         | Ρ | PLL lock time <sup>11,15</sup>      | _                                   | —        | 200                           | μs                 |  |

| t <sub>dc</sub>    | CC         | D | Duty cycle of reference             | _                                   | 40       | 60                            | %                  |  |

| f <sub>LCK</sub>   | CC         | D | Frequency LOCK range                | —                                   | -6       | 6                             | % f <sub>sys</sub> |  |

| f <sub>UL</sub>    | СС         | D | Frequency un-LOCK range             | —                                   | -18      | 18                            | % f <sub>sys</sub> |  |

| f <sub>CS</sub>    | CC         | D | Modulation depth                    | Center spread                       | ±0.25    | ±4.0                          | % f <sub>sys</sub> |  |

| f <sub>DS</sub>    |            | D |                                     | Down spread                         | -0.5     | -8.0                          |                    |  |

| f <sub>MOD</sub>   | СС         | D | Modulation frequency <sup>16</sup>  | —                                   | <b>—</b> | 100                           | kHz                |  |

## $(V_{DDPLL} = 1.08 \text{ V to } 3.6 \text{ V}, V_{SS} = V_{SSPLL} = 0 \text{ V}, T_A = T_L \text{ to } T_H)$ (continued)

<sup>1</sup> All values given are initial design targets and subject to change.

<sup>2</sup> Considering operation with PLL not bypassed

<sup>3</sup> All internal registers retain data at 0 Hz.

<sup>4</sup> "Loss of Reference Frequency" window is the reference frequency range outside of which the PLL is in self clocked mode.

<sup>5</sup> Self clocked mode frequency is the frequency that the PLL operates at when the reference frequency falls outside the f<sub>LOR</sub> window.

<sup>6</sup> f<sub>VCO</sub> self clock range is 20–150 MHz. f<sub>SCM</sub> represents f<sub>SYS</sub> after PLL output divider (ERFD) of 2 through 16 in enhanced mode.

<sup>7</sup> This value is determined by the crystal manufacturer and board design.

<sup>8</sup> Jitter is the average deviation from the programmed frequency measured over the specified interval at maximum f<sub>SYS</sub>. Measurements are made with the device powered by filtered supplies and clocked by a stable external clock signal. Noise injected into the PLL circuitry via V<sub>DDPLL</sub> and V<sub>SSPLL</sub> and variation in crystal oscillator frequency increase the C<sub>JITTER</sub> percentage for a given interval.

<sup>9</sup> Proper PC board layout procedures must be followed to achieve specifications.

<sup>10</sup> Values are with frequency modulation disabled. If frequency modulation is enabled, jitter is the sum of C<sub>JITTER</sub> and either f<sub>CS</sub> or f<sub>DS</sub> (depending on whether center spread or down spread modulation is enabled).

<sup>11</sup> This value is determined by the crystal manufacturer and board design. For 4 MHz to 40 MHz crystals specified for this PLL, load capacitors should not exceed these limits.

<sup>12</sup> Proper PC board layout procedures must be followed to achieve specifications.

<sup>13</sup> This parameter is guaranteed by design rather than 100% tested.

\_\_\_\_\_

**Electrical characteristics**

| Symbo     | Symbol C Parameter |   | C Parameter Conditions                                                                                                                         |                                     | Valu    | Unit    |        |

|-----------|--------------------|---|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|---------|---------|--------|

| Symbo     | ,,                 | Ŭ | Falantetei                                                                                                                                     |                                     |         | Тур     | Onic   |

| P/E       | CC                 | D | Number of program/erase<br>cycles per block for 16 KB,<br>48 KB, and 64 KB blocks over<br>the operating temperature<br>range (T <sub>J</sub> ) | _                                   | 100,000 | _       | cycles |

| P/E       | CC                 | D | Number of program/erase<br>cycles per block for 128 KB and<br>256 KB blocks over the<br>operating temperature range<br>(T <sub>J</sub> )       | _                                   | 1,000   | 100,000 | cycles |

| Retention | CC                 | D | Minimum data retention at 85 °C                                                                                                                | Blocks with 0 – 1,000<br>P/E cycles | 20      | _       | years  |

|           |                    | D |                                                                                                                                                | Blocks with 10,000 P/E cycles       | 10      | —       |        |

|           |                    | D |                                                                                                                                                | Blocks with 100,000 P/E cycles      | 5       | —       |        |

#### Table 33. Flash EEPROM module life

| Pad type                              |    | с                            | Low-to  | elay (ns) <sup>2,3</sup><br>b-High /<br>to-Low | Rise/Fall e | edge (ns) <sup>3,4</sup> | Drive load<br>(pF) | SRC/DSC         |

|---------------------------------------|----|------------------------------|---------|------------------------------------------------|-------------|--------------------------|--------------------|-----------------|

| 5.6.7                                 |    |                              | Min     | Max                                            | Min         | Max                      |                    | MSB,LSB         |

| Medium <sup>5,6,7</sup>               | CC | D                            | 5.8/4.4 | 18/17                                          | 2.7/2.1     | 10/10                    | 50                 | 11 <sup>8</sup> |

|                                       | CC | D                            | 16/13   | 46/49                                          | 11.2/8.6    | 34/34                    | 200                |                 |

|                                       |    |                              |         |                                                | _           |                          |                    | 10 <sup>9</sup> |

|                                       | CC | D                            | 14/16   | 37/45                                          | 6.5/6.7     | 19/19                    | 50                 | 01              |

|                                       | CC | D                            | 27/27   | 69/82                                          | 15/13       | 43/43                    | 200                |                 |

|                                       | CC | D                            | 83/86   | 200/210                                        | 38/38       | 86/86                    | 50                 | 00              |

|                                       | CC | D                            | 113/109 | 270/285                                        | 53/46       | 120/120                  | 200                |                 |

| Slow <sup>7,10</sup>                  | СС | D                            | 9.2/6.9 | 27/28                                          | 5.5/4.1     | 20/20                    | 50                 | 11              |

|                                       | CC | D                            | 30/23   | 81/87                                          | 21/16       | 63/63                    | 200                |                 |

|                                       |    |                              |         |                                                |             |                          |                    | 10 <sup>9</sup> |

|                                       | CC | D                            | 31/31   | 80/90                                          | 15.4/15.4   | 42/42                    | 50                 | 01              |

|                                       | CC | D                            | 58/52   | 144/155                                        | 32/26       | 82/85                    | 200                |                 |

|                                       | CC | D                            | 162/168 | 415/415                                        | 80/82       | 190/190                  | 50                 | 00              |

|                                       | CC | D                            | 216/205 | 533/540                                        | 106/95      | 250/250                  | 200                |                 |

| MultiV <sup>7,11</sup>                | CC | D                            | _       | 3.7/3.1                                        | —           | 10/10                    | 30                 | 11 <sup>8</sup> |

| (High Swing Mode)                     | CC | D                            | _       | 46/49                                          | _           | 42/42                    | 200                |                 |

|                                       |    |                              |         |                                                | —           |                          |                    | 10 <sup>9</sup> |

|                                       | CC | D                            | —       | 32                                             | —           | 15/15                    | 50                 | 01              |

|                                       | CC | D                            | _       | 72                                             | _           | 46/46                    | 200                |                 |

|                                       | CC | D                            | _       | 210                                            | —           | 100/100                  | 50                 | 00              |

|                                       | CC | D                            | _       | 295                                            | _           | 134/134                  | 200                |                 |

| MultiV<br>(Low Swing Mode)            |    | Not a valid operational mode |         |                                                |             |                          |                    |                 |

| Fast                                  | CC | D                            | —       | 2.5/2.5                                        | —           | 1.2/1.2                  | 10                 | 00              |

|                                       | СС | D                            | —       | 2.5/2.5                                        | —           | 1.2/1.2                  | 20                 | 01              |

|                                       | СС | D                            | _       | 2.5/2.5                                        |             | 1.2/1.2                  | 30                 | 10              |

|                                       | СС | D                            |         | 2.5/2.5                                        |             | 1.2/1.2                  | 50                 | 11 <sup>8</sup> |

| Standalone input buffer <sup>12</sup> | СС | D                            | 0.5/0.5 | 3/3                                            | 0.4/0.4     | ±1.5/1.5                 | 0.5                | _               |

| Table 35. Pad AC specifications (V <sub>D</sub> | $DF = 3.0 V)^{1}$ |

|-------------------------------------------------|-------------------|

|-------------------------------------------------|-------------------|

<sup>1</sup> These are worst case values that are estimated from simulation and not tested. The values in the table are simulated at  $V_{DD} = 1.14$  V to 1.32 V,  $V_{DDE} = 3$  V to 3.6 V,  $V_{DDEH} = 3$  V to 3.6 V,  $T_A = T_L$  to  $T_H$ .

<sup>2</sup> This parameter is supplied for reference and is not guaranteed by design and not tested.

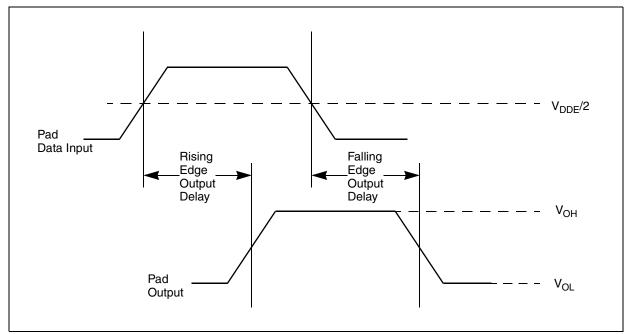

$^3\,$  Delay and rise/fall are measured to 20% or 80% of the respective signal.

<sup>4</sup> This parameter is guaranteed by characterization before qualification rather than 100% tested.

- $^5\,$  In high swing mode, high/low swing pad V\_{OL} and V\_{OH} values are the same as those of the slew controlled output pads.

- <sup>6</sup> Medium Slew-Rate Controlled Output buffer. Contains an input buffer and weak pull-up/pull-down.

- <sup>7</sup> Output delay is shown in Figure 9 and Figure 10. Add a maximum of one system clock to the output delay for delay with respect to system clock.

- <sup>8</sup> Can be used on the tester.

- <sup>9</sup> This drive select value is not supported. If selected, it will be approximately equal to 11.

- <sup>10</sup> Slow Slew-Rate Controlled Output buffer. Contains an input buffer and weak pull-up/pull-down.

- <sup>11</sup> Selectable high/low swing I/O pad with selectable slew in high swing mode only.

- <sup>12</sup> Also has weak pull-up/pull-down.

Figure 9. Pad output delay—Fast pads

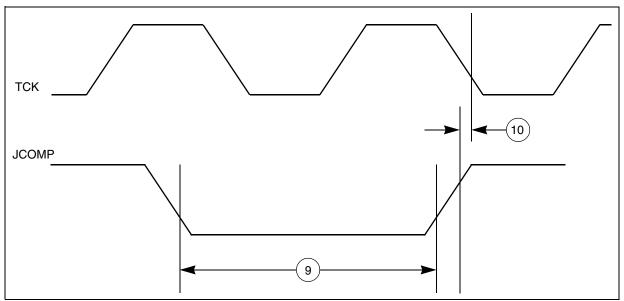

Figure 14. JTAG JCOMP timing

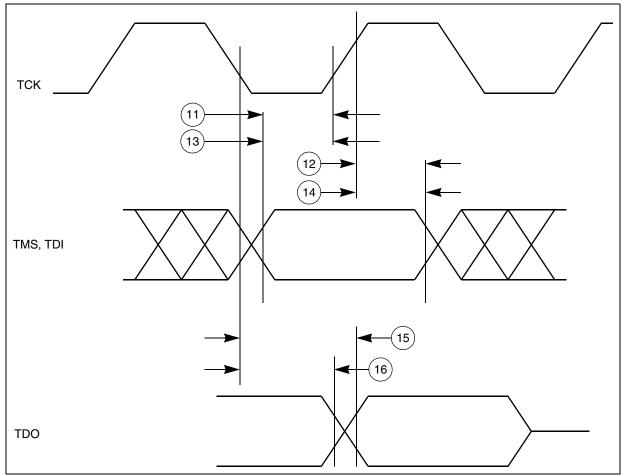

Figure 18. Nexus TDI, TMS, TDO timing

|                     |                                |                                  | I                           | Max. Operating           |                              |                       |

|---------------------|--------------------------------|----------------------------------|-----------------------------|--------------------------|------------------------------|-----------------------|

| Package             | Nexus Width                    | Nexus Routing                    | MDO[0:3]                    | MDO[4:11]                | CAL_MDO[4:1<br>1]            | Frequency             |

| 176 LQFP<br>208 BGA | Reduced port mode <sup>1</sup> | Route to MDO <sup>2</sup>        | Nexus Data Out<br>[0:3]     | GPIO                     | GPIO                         | 40 MHz <sup>3</sup>   |

| 324 BGA             | Full port<br>mode <sup>4</sup> | Route to MDO <sup>2</sup>        | Nexus Data Out<br>[0:3]     | Nexus Data Out<br>[4:11] | GPIO                         | 40 MHz <sup>5,6</sup> |

| 496 CSP             | Reduced port mode <sup>1</sup> | Route to MDO <sup>2</sup>        | Nexus Data Out<br>[0:3]     | GPIO                     | GPIO                         | 40 MHz <sup>3</sup>   |

|                     | Full port<br>mode <sup>4</sup> | Route to MDO <sup>2</sup>        | Nexus Data Out<br>[0:3]     | Nexus Data Out<br>[4:11] | GPIO                         | 40 MHz <sup>5,6</sup> |

|                     |                                | Route to<br>CAL_MDO <sup>7</sup> | Cal Nexus Data<br>Out [0:3] | GPIO                     | Cal Nexus Data<br>Out [4:11] | 40 MHz <sup>3</sup>   |

| Table 39. Nexus | debug port | operating | frequency |

|-----------------|------------|-----------|-----------|

|-----------------|------------|-----------|-----------|

<sup>1</sup> NPC\_PCR[FPM] = 0 <sup>2</sup> NPC\_PCR[NEXCFG] = 0

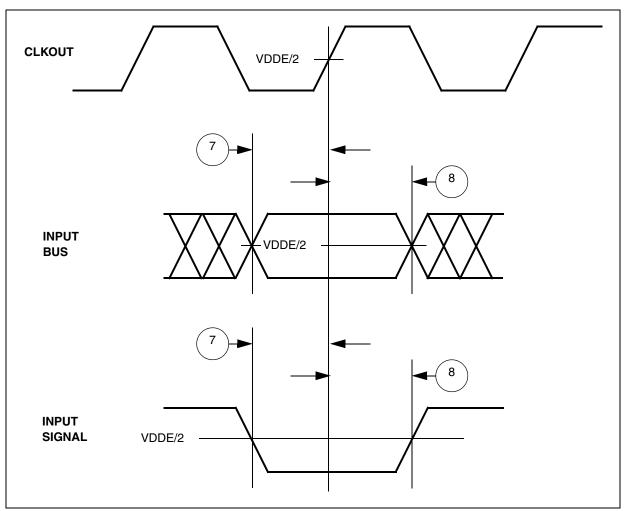

Figure 21. Synchronous input timing

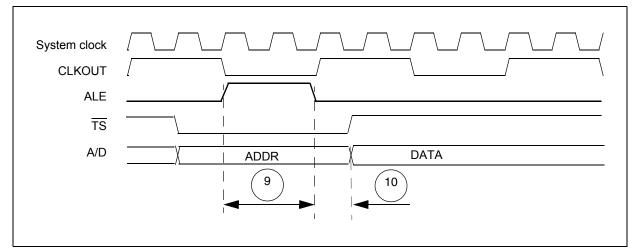

Figure 22. ALE signal timing

# NP

#### **Electrical characteristics**

- <sup>7</sup> Timing met when PCSSCK = 3 (01), and CSSCK = 2 (0000)

- <sup>8</sup> The maximum value is programmable in DSPI\_CTARx[PASC] and DSPI\_CTARx[ASC].

- <sup>9</sup> Timing met when ASC = 2 (0000), and PASC = 3 (01)

- $^{10}$  Timing met when PCSSCK = 3

- <sup>11</sup> Timing met when ASC = 3

<sup>12</sup> This number is calculated assuming the SMPL\_PT bitfield in DSPI\_MCR is set to 0b10.

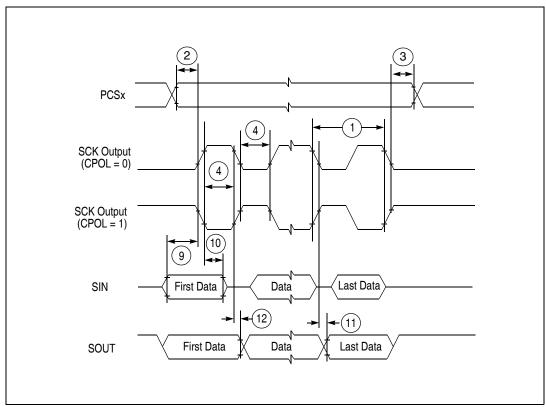

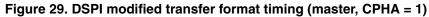

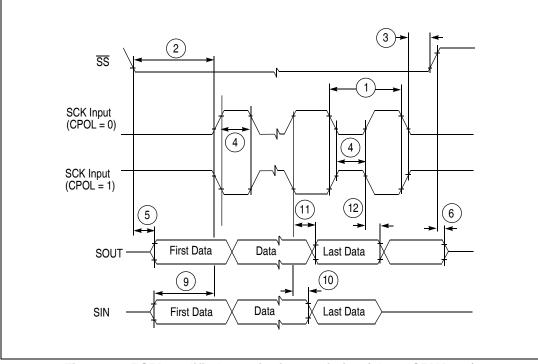

Figure 24. DSPI classic SPI timing (master, CPHA = 0)

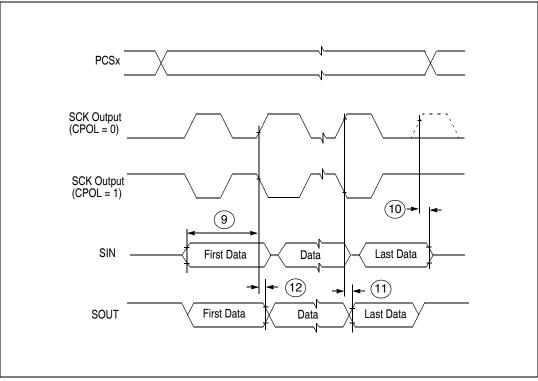

Figure 30. DSPI modified transfer format timing (slave, CPHA = 0)

Figure 31. DSPI modified transfer format timing (slave, CPHA = 1)

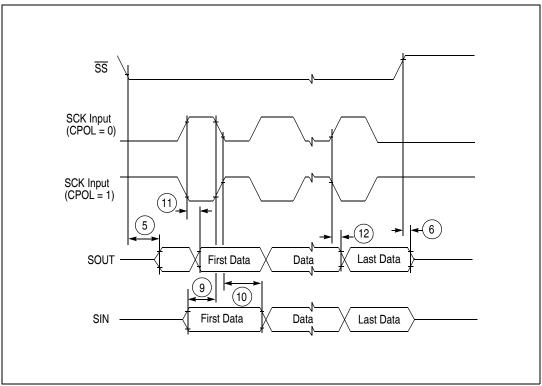

Figure 32. DSPI PCS strobe (PCSS) timing

# 3.17.10 FlexCAN system clock source

## Table 48. FlexCAN engine system clock divider threshold

| # | Symbol              | Characteristic                        | Value | Unit |

|---|---------------------|---------------------------------------|-------|------|

| 1 | f <sub>CAN_TH</sub> | FlexCAN engine system clock threshold | 100   | MHz  |

### Table 49. FlexCAN engine system clock divider

| System frequency      | Required SIU_SYSDIV[CAN_SRC] value |  |  |

|-----------------------|------------------------------------|--|--|

| ≤ f <sub>CAN_TH</sub> | 0 <sup>1,2</sup>                   |  |  |

| > f <sub>CAN_TH</sub> | 1 <sup>2,3</sup>                   |  |  |

<sup>1</sup> Divides system clock source for FlexCAN engine by 1

<sup>2</sup> System clock is only selected for FlexCAN when CAN\_CR[CLK\_SRC] = 1

<sup>3</sup> Divides system clock source for FlexCAN engine by 2

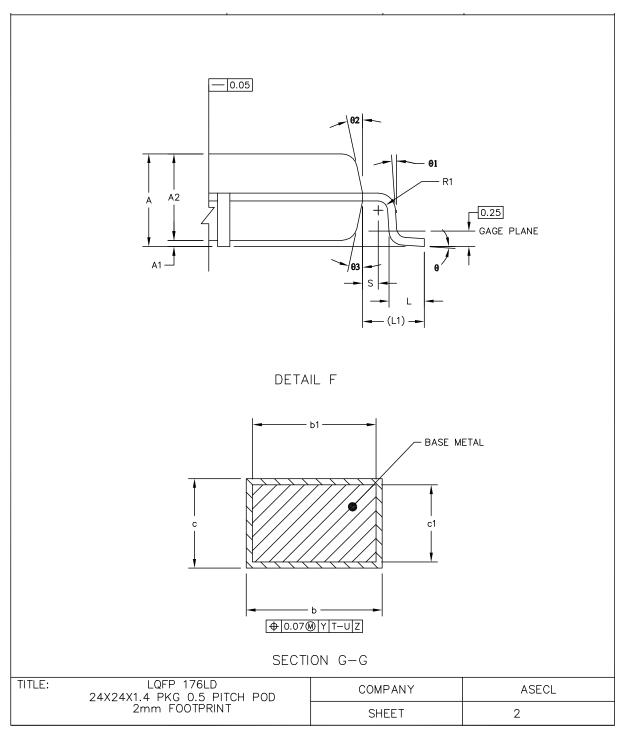

Figure 34. 176 LQFP package mechanical drawing (part 1)

Figure 35. 176 LQFP package mechanical drawing (part 2)

# 4.1.3 324 TEPBGA

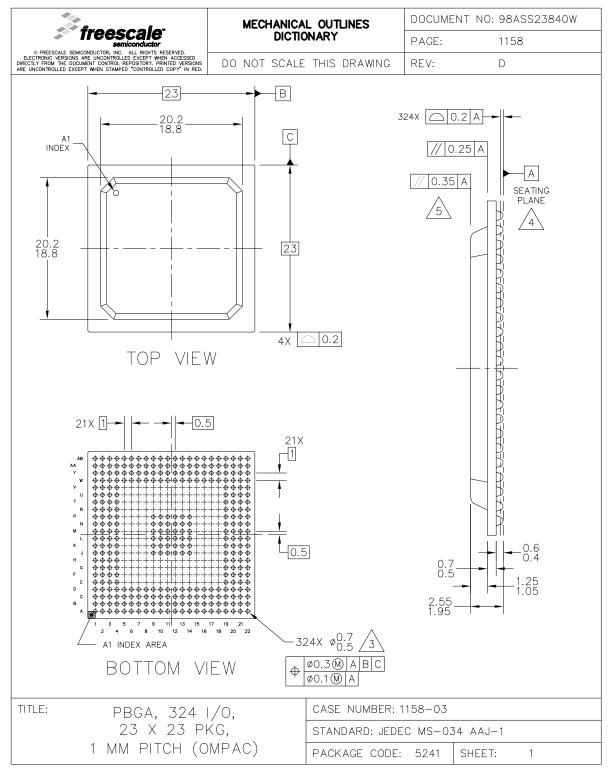

Figure 39. 324 BGA package mechanical drawing (part 1)