Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                     |

| Core Processor             | H8S/2600                                                                     |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 20MHz                                                                        |

| Connectivity               | CANbus, SCI, SmartCard                                                       |

| Peripherals                | POR, PWM, WDT                                                                |

| Number of I/O              | 53                                                                           |

| Program Memory Size        | 256KB (256K x 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 12K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                    |

| Data Converters            | A/D 16x10b; D/A 2x8b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 100-BFQFP                                                                    |

| Supplier Device Package    | 100-QFP (14x14)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df2623fa20v |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Note that the functions of each pin depend on the operating mode.

The H8S/2626 Group and H8S/2623 Group can be used only in modes 4 to 7. This means that the mode pins must be set to select one of these modes. Do not change the inputs at the mode pins during operation.

### 3.1.2 Register Configuration

The H8S/2626 Group and H8S/2623 Group have a mode control register (MDCR) that indicates the inputs at the mode pins (MD2 to MD0), and a system control register (SYSCR) that controls the operation of the H8S/2626 Group or H8S/2623 Group chip. Table 3.2 summarizes these registers.

### Table 3.2MCU Registers

| Name                          | Abbreviation | R/W | Initial Value | Address* |

|-------------------------------|--------------|-----|---------------|----------|

| Mode control register         | MDCR         | R/W | Undetermined  | H'FDE7   |

| System control register       | SYSCR        | R/W | H'01          | H'FDE5   |

| Pin function control register | PFCR         | R/W | H'0D/H'00     | H'FDEB   |

|                               |              |     |               |          |

Note: \* Lower 16 bits of the address.

| Pin                                      | Selection Meth                         | od and Pi                  | n Function                                 | IS            |        |                         |            |

|------------------------------------------|----------------------------------------|----------------------------|--------------------------------------------|---------------|--------|-------------------------|------------|

| P13/P011/<br>TIOCD0/TCLKB/<br>A23 (cont) | TPU Channel<br>0 Setting<br>MD3 to MD0 | (2)<br>B'0                 | (1)                                        | (2)<br>B'0010 | (2)    | (1)<br>B'0011           | (2)        |

|                                          | IOD3 to IOD0                           | B'0000<br>B'0100<br>B'1xxx | B'0001 to<br>B'0011<br>B'0101 to<br>B'0111 | _             | B'xx00 | Other that              | an B'xx00  |

|                                          | CCLR2 to<br>CCLR0                      | —                          | —                                          | _             |        | Other<br>than<br>B'110  | B'110      |

|                                          | Output<br>function                     | —                          | Output<br>compare<br>output                | —             |        | PWM<br>mode 2<br>output | _          |

|                                          |                                        |                            |                                            |               |        | х:                      | Don't care |

### Selection Method and Pin Functions

#### Selection Method and Pin Functions

P12/PO10/ TIOCC0/TCLKA/ A22 (cont)

Pin

| TPU Channel  |        |           |        |          |             |       |

|--------------|--------|-----------|--------|----------|-------------|-------|

| 0 Setting    | (2)    | (1)       | (2)    | (1)      | (1)         | (2)   |

| MD3 to MD0   | B'0    | 000       | B'001x | B'0010   | B'0         | 011   |

| IOC3 to IOC0 | B'0000 | B'0001 to | B'xx00 | Oth      | er than B'x | x00   |

|              | B'0100 | B'0011    |        |          |             |       |

|              | B'1xxx | B'0101 to |        |          |             |       |

|              |        | B'0111    |        |          |             |       |

| CCLR2 to     | _      | _         | _      | — Other  |             | B'101 |

| CCLR0        |        |           |        |          | than        |       |

|              |        |           |        |          | B'101       |       |

| Output       | —      | Output    | —      | PWM      | PWM         | —     |

| function     |        | compare   |        | mode 1   | mode 2      |       |

|              |        | output    |        | output*3 | output      |       |

x: Don't care

Notes: 1. TIOCC0 input when MD3 to MD0 = B'0000, and IOC3 to IOC0 = B'10xx.

TCLKA input when the setting for TCR0 to TCR5 is: TPSC2 to TPSC0 = B'100.

TCLKA input when channels 1 and 5 are set to phase counting mode.

TIOCD0 output is disabled. When BFA = 1 or BFB = 1 in TMDR0, output is disabled and setting (2) applies.

#### 9.6.2 Register Configuration

Table 9.9 shows the port B register configuration.

### Table 9.9Port B Registers

| Name                                  | Abbreviation | R/W | Initial Value | Address* |  |  |  |  |

|---------------------------------------|--------------|-----|---------------|----------|--|--|--|--|

| Port B data direction register        | PBDDR        | W   | H'00          | H'FE3A   |  |  |  |  |

| Port B data register                  | PBDR         | R/W | H'00          | H'FF0A   |  |  |  |  |

| Port B register                       | PORTB        | R   | Undefined     | H'FFBA   |  |  |  |  |

| Port B MOS pull-up control register   | PBPCR        | R/W | H'00          | H'FE41   |  |  |  |  |

| Port B open-drain control register    | PBODR        | R/W | H'00          | H'FE48   |  |  |  |  |

| Note: * Lower 16 bits of the address. |              |     |               |          |  |  |  |  |

### Port B Data Direction Register (PBDDR)

| Bit        | :      | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

|            |        | PB7DDR | PB6DDR | PB5DDR | PB4DDR | PB3DDR | PB2DDR | PB1DDR | PB0DDR |

| Initial va | alue : | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| R/W        | :      | W      | W      | W      | W      | W      | W      | W      | W      |

PBDDR is an 8-bit write-only register, the individual bits of which specify input or output for the pins of port B. PBDDR cannot be read; if it is, an undefined value will be read.

PBDDR is initialized to H'00 by a reset, and in hardware standby mode. It retains its prior state in software standby mode. The OPE bit in SBYCR is used to select whether the address output pins retain their output state or become high-impedance when a transition is made to software standby mode.

• Modes 4 to 6

The corresponding port B pins become address outputs in accordance with the setting of bits AE3 to AE0 in PFCR, irrespective of the value of the PBDDR bits. When pins are not used as address outputs, setting a PBDDR bit to 1 makes the corresponding port B pin an output port, while clearing the bit to 0 makes the pin an input port.

• Mode 7

Setting a PBDDR bit to 1 makes the corresponding port B pin an output port, while clearing the bit to 0 makes the pin an input port.

## Renesas

## 9.8 Port D

### 9.8.1 Overview

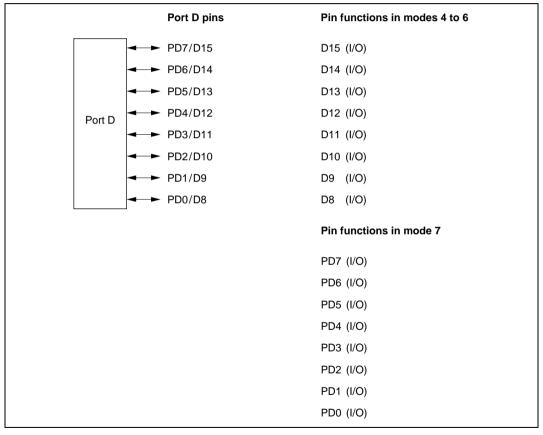

Port D is an 8-bit I/O port. Port D has a data bus I/O function, and the pin functions change according to the operating mode.

Port D has a built-in MOS input pull-up function that can be controlled by software.

Figure 9.7 shows the port D pin configuration.

Figure 9.7 Port D Pin Functions

### 10.2.3 Timer I/O Control Register (TIOR)

Channel 0: TIOR0H

Channel 1: TIOR1

Channel 2: TIOR2

Channel 3: TIOR3H

Channel 4: TIOR4

Channel 5: TIOR5

| Bit         | :       | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-------------|---------|------|------|------|------|------|------|------|------|

|             |         | IOB3 | IOB2 | IOB1 | IOB0 | IOA3 | IOA2 | IOA1 | IOA0 |

| Initial val | lue :   | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| R/W         | :       | R/W  |

|             |         |      |      |      |      |      |      |      |      |

| Channe      | I 0: TI | OR0L |      |      |      |      |      |      |      |

| Channe      | l 3: Tl | OR3L |      |      |      |      |      |      |      |

| Bit         | :       | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|             |         | IOD3 | IOD2 | IOD1 | IOD0 | IOC3 | IOC2 | IOC1 | IOC0 |

| Initial val | lue :   | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| R/W         | :       | R/W  |

Note: When TGRC or TGRD is designated for buffer operation, this setting is invalid and the register operates as a buffer register.

The TIOR registers are 8-bit registers that control the TGR registers. The TPU has eight TIOR registers, two each for channels 0 and 3, and one each for channels 1, 2, 4, and 5. The TIOR registers are initialized to H'00 by a reset, and in hardware standby mode.

Care is required since TIOR is affected by the TMDR setting. The initial output specified by TIOR is valid when the counter is stopped (the CST bit in TSTR is cleared to 0). Note also that, in PWM mode 2, the output at the point at which the counter is cleared to 0 is specified.

| Channel | Bit 3<br>IOC3 | Bit 2<br>IOC2 | Bit 1<br>IOC1                  | Bit 0<br>IOC0 | Descriptio        | on                                                  |                                               |

|---------|---------------|---------------|--------------------------------|---------------|-------------------|-----------------------------------------------------|-----------------------------------------------|

| 0       | 0             | 0             | 0                              | 0             | TGR0C             | Output disabled                                     | (Initial value)                               |

|         |               |               |                                | 1             | is output compare | Initial output is 0 output                          | 0 output at compare match                     |

|         |               |               | 1                              | 0             | register*1        | output                                              | 1 output at compare match                     |

|         | 1             |               | Toggle output at compare match |               |                   |                                                     |                                               |

|         |               | 1             | 0                              | 0             | =                 | Output disabled                                     |                                               |

|         |               |               |                                | 1             | =                 | Initial output is 1                                 | 0 output at compare match                     |

|         |               |               | 1                              | 0             | =                 | output                                              | 1 output at compare match                     |

|         |               |               |                                | 1             | -                 |                                                     | Toggle output at compare match                |

|         | 1             | 0             | 0                              | 0             | TGR0C             | Capture input                                       | Input capture at rising edge                  |

|         |               |               |                                | 1             | is input          | source is<br>TIOCC0 pin                             | Input capture at falling edge                 |

|         |               |               | 1                              | *             | register*1        | neece piir                                          | Input capture at both edges                   |

|         |               | 1             | *                              | *             | -                 | Capture input<br>source is channel<br>1/count clock | Input capture at TCNT1<br>count-up/count-down |

\*: Don't care

Note: 1. When the BFA bit in TMDR0 is set to 1 and TGR0C is used as a buffer register, this setting is invalid and input capture/output compare is not generated.

## Clock

See the section on asynchronous mode.

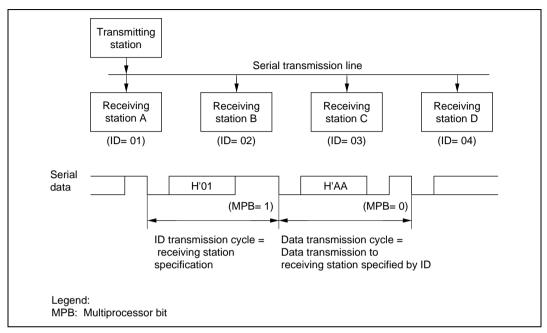

## Figure 13.9 Example of Inter-Processor Communication Using Multiprocessor Format (Transmission of Data H'AA to Receiving Station A)

## **Data Transfer Operations**

**Multiprocessor serial data transmission:** Figure 13.10 shows a sample flowchart for multiprocessor serial data transmission.

The following procedure should be used for multiprocessor serial data transmission.

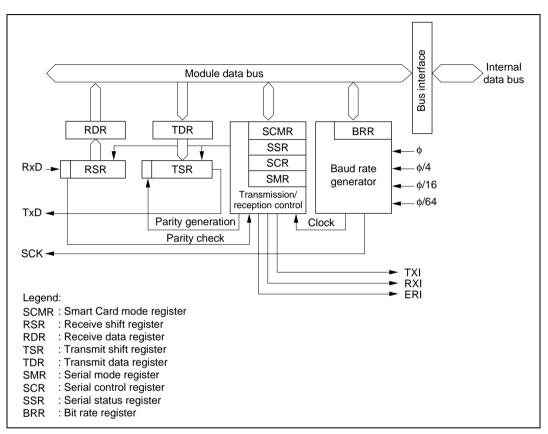

## 14.1.2 Block Diagram

Figure 14.1 shows a block diagram of the Smart Card interface.

Figure 14.1 Block Diagram of Smart Card Interface

## LAFMH Bits 7 to 0 and 15 to 13—11-Bit Identifier Filter (LAFMH7 to LAFMH5,

**LAFMH15 to LAFMH8):** Filter mask bits for the first 11 bits of the receive message identifier (for both standard and extended identifiers).

#### Bit x

| LAFMHx | Description                                                                                                                                  |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | Stored in MC0, MD0 (receive-only mailbox) depending on bit match between MC0message identifier and receive message identifier(Initial value) |

| 1      | Stored in MC0, MD0 (receive-only mailbox) regardless of bit match between MC0 message identifier and receive message identifier              |

LAFMH Bits 12 to 10—Reserved: These bits always read 0. The write value should always be 0.

LAFMH Bits 9 and 8, LAFML Bits 15 to 0—18-Bit Identifier Filter (LAFMH1, LAFMH0, LAFML7 to LAFML0, LAFML15 to LAFML8): Filter mask bits for the 18 bits of the receive message identifier (extended).

### Bit x

| LAFMHx<br>LAFMLx | <br>Description                                                                                                                           |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 0                | Stored in MC0 (receive-only mailbox) depending on bit match between MC0 message identifier and receive message identifier (Initial value) |

| 1                | Stored in MC0 (receive-only mailbox) regardless of bit match between MC0 message identifier and receive message identifier                |

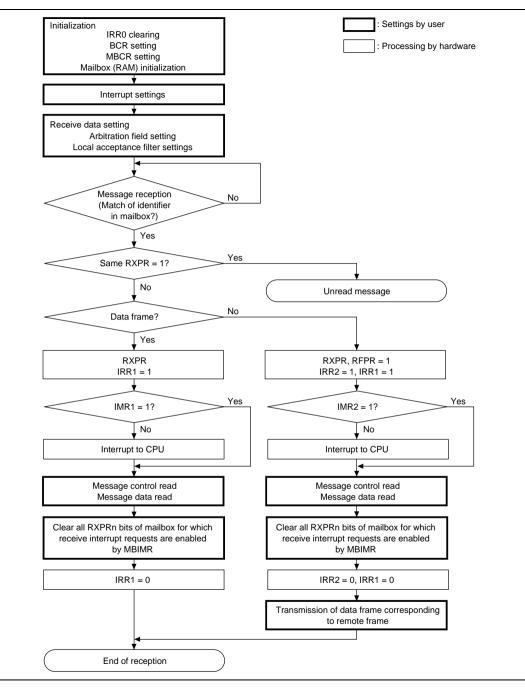

initial setting for mailboxes is 0, designating transmission use. Refer to Mailbox transmit/receive settings in 15.3.2, Initialization after Hardware Reset, for details.

• Mailbox (RAM) initialization

As message control/data registers (MCx[x], MDx[x]) are configured in RAM, their initial values after powering on are undefined, and so bit initialization is necessary. Write 0s or 1s to the mailboxes. See Mailbox (Message Control/Data (MCx[x], MDx[x]) Initial Settings in 15.3.2, Initialization after a Hardware Reset, for details.

Rev. 5.00 Jan 10, 2006 page 576 of 1042 REJ09B0275-0500

### 16.1.3 Pin Configuration

Table 16.1 summarizes the input pins used by the A/D converter.

The AVCC and AVSS pins are the power supply pins for the analog block in the A/D converter. The Vref pin is the A/D conversion reference voltage pin.

The 16 analog input pins are divided into two channel sets and two groups, with analog input pins 0 to 7 (AN0 to AN7) comprising channel set 0, analog input pins 8 to 15 (AN8 to AN15) comprising channel set 1, analog input pins 0 to 3 and 8 to 11 (AN0 to AN3, AN8 to AN11) comprising group 0, and analog input pins 4 to 7 and 12 to 15 (AN4 to AN7, AN12 to AN15) comprising group 1.

| Pin Name                          | Symbol | I/O   | Function                                           |

|-----------------------------------|--------|-------|----------------------------------------------------|

| Analog power supply pin           | AVCC   | Input | Analog block power supply                          |

| Analog ground pin                 | AVSS   | Input | Analog block ground and reference voltage          |

| Reference voltage pin             | Vref   | Input | A/D conversion reference voltage                   |

| Analog input pin 0                | AN0    | Input | Channel set 0 (CH3 = 0) group 0 analog inputs      |

| Analog input pin 1                | AN1    | Input |                                                    |

| Analog input pin 2                | AN2    | Input |                                                    |

| Analog input pin 3                | AN3    | Input |                                                    |

| Analog input pin 4                | AN4    | Input | Channel set 0 (CH3 = 0) group 1 analog inputs      |

| Analog input pin 5                | AN5    | Input |                                                    |

| Analog input pin 6                | AN6    | Input |                                                    |

| Analog input pin 7                | AN7    | Input |                                                    |

| Analog input pin 8                | AN8    | Input | Channel set 1 (CH3 = 1) group 0 analog inputs      |

| Analog input pin 9                | AN9    | Input |                                                    |

| Analog input pin 10               | AN10   | Input |                                                    |

| Analog input pin 11               | AN11   | Input |                                                    |

| Analog input pin 12               | AN12   | Input | Channel set 1 (CH3 = 1) group 1 analog inputs      |

| Analog input pin 13               | AN13   | Input |                                                    |

| Analog input pin 14               | AN14   | Input |                                                    |

| Analog input pin 15               | AN15   | Input | —                                                  |

| A/D external trigger input<br>pin | ADTRG  | Input | External trigger input for starting A/D conversion |

## Table 16.1 A/D Converter Pins

## Renesas

Before branching to the programming control program (RAM area H'FFC000), the chip terminates transmit and receive operations by the on-chip SCI (channel 2) (by clearing the RE and TE bits in SCR to 0), but the adjusted bit rate value remains set in BRR. The transmit data output pin, TxD2, goes to the high-level output state (PA1DDR = 1, PA1DR = 1). The contents of the CPU's internal general registers are undefined at this time, so these registers must be initialized immediately after branching to the programming control program. In particular, since the stack pointer (SP) is used implicitly in subroutine calls, etc., a stack area must be specified for use by the programming control program.

The initial values of other on-chip registers are not changed.

• Boot mode can be entered by making the pin settings shown in table 19.6 and executing a reset-start.

Boot mode can be cleared by driving the reset pin low, waiting at least 20 states, then setting the FWE pin and mode pins, and executing reset release<sup>\*1</sup>. Boot mode can also be cleared by a WDT overflow reset.

Do not change the mode pin input levels in boot mode, and do not drive the FWE pin low while the boot program is being executed or while flash memory is being programmed or erased<sup>\*2</sup>.

• If the mode pin input levels are changed (for example, from low to high) during a reset, the state of ports with multiplexed address functions and bus control output pins (AS, RD, HWR) will change according to the change in the microcomputer's operating mode<sup>\*3</sup>.

Therefore, care must be taken to make pin settings to prevent these pins from becoming output signal pins during a reset, or to prevent collision with signals outside the microcomputer.

- Notes: 1. Mode pin and FWE pin input must satisfy the mode programming setup time ( $t_{MDS} = 4$  states) with respect to the reset release timing.

- 2. For further information on FWE application and disconnection, see section 19.13, Flash Memory Programming and Erasing Precautions.

- 3. See appendix D, Pin States.

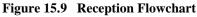

## 19.6.2 User Program Mode

When set to user program mode, the chip can program and erase its flash memory by executing a user program/erase control program. Therefore, on-board reprogramming of the on-chip flash memory can be carried out by providing on-board means of FWE control and supply of programming data, and storing a program/erase control program in part of the program area as necessary.

#### Section 19 ROM (Preliminary)

To select user program mode, select a mode that enables the on-chip flash memory (mode 6 or 7), and apply a high level to the FWE pin. In this mode, on-chip supporting modules other than flash memory operate as they normally would in modes 6 and 7.

The flash memory itself cannot be read while the SWE1 bit is set to 1 to perform programming or erasing, so the control program that performs programming and erasing should be run in on-chip RAM or external memory. If the program is to be located in external memory, the instruction for writing to flash memory, and the following instruction, should be placed in on-chip RAM.

Figure 19.9 shows the procedure for executing the program/erase control program when transferred to on-chip RAM.

## Figure 19.9 User Program Mode Execution Procedure

Rev. 5.00 Jan 10, 2006 page 648 of 1042 REJ09B0275-0500

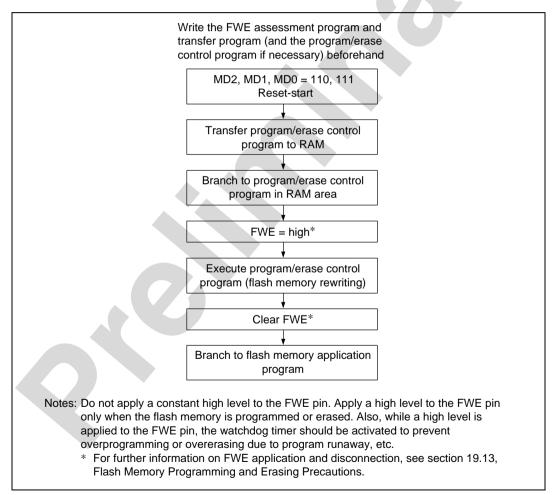

**Crystal Resonator:** Figure 20.3 shows the equivalent circuit of the crystal resonator. Use a crystal resonator that has the characteristics shown in table 20.3. The crystal resonator frequency should not exceed 20 MHz.

Figure 20.3 Crystal Resonator Equivalent Circuit

### Table 20.3 Crystal Resonator Parameters

| Frequency (MHz)         | 4   | 8  | 12 | 16 | 20 |

|-------------------------|-----|----|----|----|----|

| R <sub>s</sub> max (Ω)  | 120 | 80 | 60 | 50 | 40 |

| C <sub>o</sub> max (pF) | 7   | 7  | 7  | 7  | 7  |

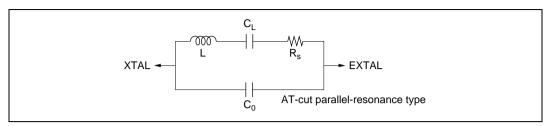

**Note on Board Design:** When a crystal resonator is connected, the following points should be noted:

Other signal lines should be routed away from the oscillator circuit to prevent induction from interfering with correct oscillation. See figure 20.4.

When designing the board, place the crystal resonator and its load capacitors as close as possible to the XTAL and EXTAL pins.

Figure 20.4 Example of Incorrect Board Design

|      |                   | -          | Inst | Ad               | Addressing Mode/<br>Instruction Length (Bytes) | ssin<br>Lei | g M | ode<br>Bj      | ı/<br>ytes | ~              |                                   |          |     |       |                   |                |       |                 |

|------|-------------------|------------|------|------------------|------------------------------------------------|-------------|-----|----------------|------------|----------------|-----------------------------------|----------|-----|-------|-------------------|----------------|-------|-----------------|

|      |                   | erand Size |      | иЯ               | (uЯЭ,b                                         | +uA3@/uA3   | B   | ()<br>()<br>() | 88 (j      |                |                                   | 0        | ouo | ditio | 5                 | Condition Code | No. o | No. of States*1 |

|      | Mnemonic          |            | xx#  | <u>а</u> @<br>пЯ |                                                |             | e @ |                | 00         |                | Operation                         | -        | I   | z     | Ν                 | с<br>>         | -     | Advanced        |

| BCLR | BCLR Rn,@aa:32    | В          |      |                  |                                                |             | 8   |                |            | (Rn            | (Rn8 of @aa:32)←0                 |          |     |       |                   |                |       | 9               |

| BNOT | BNOT #xx:3,Rd     | В          |      | 2                |                                                |             |     |                |            | (X#)           | (#xx:3 of Rd8)←[¬ (#xx:3 of Rd8)] | <u> </u> |     |       |                   |                |       | -               |

|      | BNOT #xx:3,@ERd   | В          |      | 4                |                                                |             |     |                |            | (X#)           | (#xx:3 of @ERd)←                  |          |     |       |                   |                |       | 4               |

|      |                   |            |      |                  |                                                |             |     |                |            | ()<br>[]       | [                                 |          |     |       |                   |                |       |                 |

|      | BNOT #xx:3,@aa:8  | В          |      |                  |                                                |             | 4   |                |            | (x#)           | (#xx:3 of @aa:8)←                 |          |     |       |                   |                |       | 4               |

|      |                   |            |      |                  |                                                |             |     |                |            | <u>۱</u>       | [¬ (#xx:3 of @aa:8)]              |          |     |       |                   |                |       |                 |

|      | BNOT #xx:3,@aa:16 | В          |      |                  |                                                |             | 9   |                |            | (X#)           | (#xx:3 of @aa:16)←                |          |     |       |                   |                |       | 5               |

|      |                   |            |      |                  |                                                |             |     |                |            | ( <sup>j</sup> | [¬ (#xx:3 of @aa:16)]             |          |     |       |                   |                |       |                 |

|      | BNOT #xx:3,@aa:32 | В          |      |                  |                                                |             | 8   |                |            | (X#)           | (#xx:3 of @aa:32)←                |          |     |       |                   |                |       | 6               |

|      |                   |            | _    |                  |                                                |             |     |                |            | <u>+</u> ]     | [¬ (#xx:3 of @aa:32)]             |          |     |       |                   |                |       |                 |

|      | BNOT Rn,Rd        | В          |      | 2                |                                                |             |     |                |            | (Rn            | (Rn8 of Rd8)←[¬ (Rn8 of Rd8)]     |          |     |       |                   |                |       | 1               |

|      | BNOT Rn, @ERd     | В          |      | 4                |                                                |             |     |                |            | (Rn{           | (Rn8 of @ERd)←[¬ (Rn8 of @ERd)]   |          |     |       |                   |                |       | 4               |

|      | BNOT Rn, @aa:8    | В          |      |                  |                                                |             | 4   |                |            | (Rn£           | (Rn8 of @aa:8)←[¬ (Rn8 of @aa:8)] |          |     |       |                   |                |       | 4               |

|      | BNOT Rn, @aa:16   | В          |      |                  |                                                |             | 9   |                |            | (Rn            | (Rn8 of @aa:16)←                  |          |     |       |                   |                |       | 5               |

|      |                   |            |      |                  |                                                |             |     |                |            | <u>-</u>       | [¬ (Rn8 of @aa:16)]               |          |     |       |                   |                |       |                 |

|      | BNOT Rn, @aa:32   | В          |      |                  |                                                |             | ω   |                |            | (Rn            | (Rn8 of @aa:32)←                  |          |     |       | I                 |                |       | 9               |

|      |                   |            |      | _                | _                                              |             |     |                |            | <u>ב</u>       | [¬ (Rn8 of @aa:32)]               | _        |     |       |                   |                |       |                 |

| BTST | BTST #xx:3,Rd     | ш          | . 4  | 2                |                                                |             |     |                |            | т<br>(#        |                                   |          | 1   |       | $\leftrightarrow$ |                |       | -               |

|      | BTST #xx:3,@ERd   | ш          | -    | 4                |                                                |             |     |                |            | #<br>1         | ¬ (#xx:3 of @ERd)→Z               |          |     |       | $\leftrightarrow$ |                |       | 3               |

|      | BTST #xx:3,@aa:8  | ш          |      | _                | _                                              |             | 4   |                |            | #<br>1         | ⊐ (#xx:3 of @aa:8)→Z              |          | 1   |       | $\leftrightarrow$ |                |       | 3               |

|      | BTST #xx:3,@aa:16 | В          |      |                  |                                                |             | 6   |                |            | т<br>(#        | ¬ (#xx:3 of @aa:16)→Z             |          |     |       | $\leftrightarrow$ |                |       | 4               |

|      |                   |            |      |                  |                                                |             |     |                |            |                |                                   |          |     |       |                   |                |       |                 |

| b     0     b     0     b     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0 <th>4     0     4     0     0     0       4     0     0     0     0     0       1     1     0     0     0     0       1     1     0     0     0     0       1     1     0     0     0     0       1     1     0     0     0     0       1     1     0     0     0     0       1     1     0     0     0     0       1     1     0     0     0     0       1     1     0     0     0       1     1     0     0     0       1     1     0     0     0       1     1     0     0     0       1     1     0     0     0       1     1     0     0     0</th> <th>ⓐ<br/>ⓐ<br/>ⓐ<br/>ⓐ<br/>ⓐ<br/>ⓐ<br/>ⓐ<br/>ⓐ<br/>ⓐ<br/>ⓐ<br/>ⓐ<br/>ⓐ<br/>ⓐ<br/>ⓐ</th> <th>Branching<br/>Condition<br/>Always<br/>Never<br/>Never</th> <th>Condition Code</th> <th>No. of<br/>Adv.</th> | 4     0     4     0     0     0       4     0     0     0     0     0       1     1     0     0     0     0       1     1     0     0     0     0       1     1     0     0     0     0       1     1     0     0     0     0       1     1     0     0     0     0       1     1     0     0     0     0       1     1     0     0     0     0       1     1     0     0     0       1     1     0     0     0       1     1     0     0     0       1     1     0     0     0       1     1     0     0     0       1     1     0     0     0 | ⓐ<br>ⓐ<br>ⓐ<br>ⓐ<br>ⓐ<br>ⓐ<br>ⓐ<br>ⓐ<br>ⓐ<br>ⓐ<br>ⓐ<br>ⓐ<br>ⓐ<br>ⓐ | Branching<br>Condition<br>Always<br>Never<br>Never | Condition Code                      | No. of<br>Adv. |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------|-------------------------------------|----------------|

| Mnemonic         Operation         Operation         Operation         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | xx# <th>If condition is true then       PC←PC+d       else next;</th> <th></th> <th>&gt;            <br/>N            <br/>Z            </th> <th></th>                                                                                                                                                                                                                                                                                                                                                                                         | If condition is true then       PC←PC+d       else next;           |                                                    | >            <br>N            <br>Z |                |

| BRA d:8(BT d:8)        -       -         BRA d:16(BT d:16)        -       -         BRN d:16(BF d:16)        -       -       -         BRN d:16(BF d:16)        -       -       -       -         BRN d:16(BF d:16)        -       -       -       -       -         BHI d:8        -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | If condition is true then       PC←PC+d       else next;           |                                                    |                                     | ο m σ m o      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | PC←PC+d<br>else next;                                              | Necer<br>N                                         |                                     | ~ ~ ~ ~ ~      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | else next;                                                         | Never                                              |                                     | 3 3 5          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                    | 1<br>1<br>1<br>(                                   |                                     | 3              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                    |                                                    |                                     |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                    |                                                    |                                     | 7              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                    |                                                    |                                     | ю<br>          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                    | CvZ=1 -                                            |                                     | - 2            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                    |                                                    |                                     | 3              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                    | C=0                                                |                                     | - 2            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                    |                                                    |                                     | ю<br>          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                    | C=1                                                |                                     | - 2            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                    |                                                    |                                     | 3              |

| BNE d:8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                    | – 0=Z                                              |                                     | - 2            |

| BNE d:16 - 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                    |                                                    |                                     | - 3            |

| BEQ d:8 - 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                    | Z=1 –                                              |                                     | - 2            |