Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | F <sup>2</sup> MC-8L                                                           |

| Core Size                  | 8-Bit                                                                          |

| Speed                      | 10MHz                                                                          |

| Connectivity               | EBI/EMI, Serial I/O, UART/USART                                                |

| Peripherals                | POR, PWM, WDT                                                                  |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 16KB (16K x 8)                                                                 |

| Program Memory Type        | Mask ROM                                                                       |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 512 x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 6V                                                                      |

| Data Converters            | A/D 8x10b                                                                      |

| Oscillator Type            | External                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-BQFP                                                                        |

| Supplier Device Package    | 64-QFP (14x20)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb89635rpf-g-1447e1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### (Continued)

- UART

- CLK-synchronous/CLK-asynchronous data transfer capable (6, 7, and 8 bits)

- Serial interface Switchable transfer direction to allows communication with various equipment.

- 10-bit A/D converter Start by an external input capable

- External interrupt: 4 channels Four channels are independent and capable of wake-up from low-power consumption modes (with an edge detection function).

- Low-power consumption modes

Stop mode (Oscillation stops to minimize the current consumption.)

Sleep mode (The CPU stops to reduce the current consumption to approx. 1/3 of normal.)

Subclock mode

Watch mode

- Bus interface function With hold and ready function

- Other specifications Both MB89630 series and MB89635R/636R/637R is the same.

- Electrical specifications/electrical characteristics Electrical specifications of the MB89635R/636R/637R series are the same as that of the MB89630 series. Electrical characteristics of both the series are much the same.

## ■ CORRESPONDENCE BETWEEN THE MB89630 AND MB89630R SERIES

- The MB89630R series is the reduction version of the MB89630 series.

- The the MB89630 and MB89630R series consist of the following products:

| MB89630 series  | MB89635  | MB89636  | MB89637  | MB89P637 | MB89PV630 |

|-----------------|----------|----------|----------|----------|-----------|

| MB89630R series | MB89635R | MB89636R | MB89637R |          |           |

## ■ PIN DESCRIPTION

| Pin no.                                    |                    |                                          |                        | <b>a</b> :      |                                                                                                                                                                                                                                                 |

|--------------------------------------------|--------------------|------------------------------------------|------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SH-DIP <sup>*1</sup><br>MDIP <sup>*2</sup> | QFP2 <sup>*3</sup> | QFP1 <sup>*4</sup><br>MQFP <sup>*5</sup> | Pin name               | Circuit<br>type | Function                                                                                                                                                                                                                                        |

| 30                                         | 22                 | 23                                       | X0                     | А               | Main clock crystal oscillator pins                                                                                                                                                                                                              |

| 31                                         | 23                 | 24                                       | X1                     |                 |                                                                                                                                                                                                                                                 |

| 28                                         | 20                 | 21                                       | MOD0                   | D               | Operating mode selection pins                                                                                                                                                                                                                   |

| 29                                         | 21                 | 22                                       | MOD1                   |                 | Connect directly to Vcc or Vss.                                                                                                                                                                                                                 |

| 27                                         | 19                 | 20                                       | RST                    | C               | Reset I/O pin<br>This pin is an N-ch open-drain output type with a<br>pull-up resistor, and a hysteresis input type.<br>"L" is output from this pin by an internal reset<br>source. The internal circuit is initialized by the<br>input of "L". |

| 56 to 49                                   | 48 to 41           | 49 to 42                                 | P00/AD0 to<br>P07/AD7  | F               | General-purpose I/O ports<br>When an external bus is used, these ports<br>function as the multiplex pins of the lower address<br>output and the data I/O.                                                                                       |

| 48 to 41                                   | 40 to 33           | 41 to 34                                 | P10/A08 to<br>P17/A157 | F               | General-purpose I/O ports<br>When an external bus is used, these ports<br>function as an upper address output.                                                                                                                                  |

| 40                                         | 32                 | 33                                       | P20/BUFC               | Н               | General-purpose output port<br>When an external bus is used, this port can also<br>be used as a buffer control output by setting the<br>BCTR.                                                                                                   |

| 39                                         | 31                 | 32                                       | P21/HAK                | Н               | General-purpose output port<br>When an external bus is used, this port can also<br>be used as a hold acknowledge by setting the<br>BCTR.                                                                                                        |

| 38                                         | 30                 | 31                                       | P22/HRQ                | F               | General-purpose output port<br>When an external bus is used, this port can also<br>be used as a hold request input by setting the<br>BCTR.                                                                                                      |

| 37                                         | 29                 | 30                                       | P23/RDY                | F               | General-purpose output port<br>When an external bus is used, this port functions<br>as a ready input.                                                                                                                                           |

| 36                                         | 28                 | 29                                       | P24/CLK                | Н               | General-purpose output port<br>When an external bus is used, this port functions<br>as a clock output.                                                                                                                                          |

| 35                                         | 27                 | 28                                       | P25/WR                 | Н               | General-purpose output port<br>When an external bus is used, this port functions<br>as a write signal output.                                                                                                                                   |

| 34                                         | 26                 | 27                                       | P26/RD                 | Н               | General-purpose output port<br>When an external bus is used, this port functions<br>as a read signal output.                                                                                                                                    |

\*1: DIP-64P-M01

\*2: MDP-64C-P02 \*3: FPT-64P-M23 \*4: FPT-64P-M06 \*5: MQP-M64C-P01 (Continued)

DS07-12531-4E

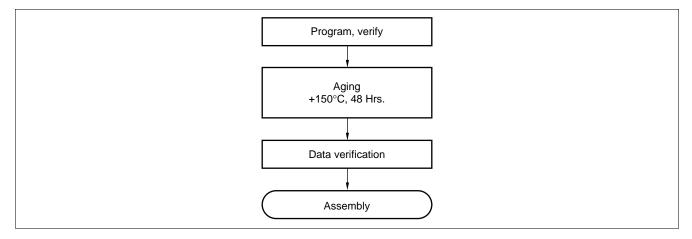

## • Programming procedure

- (1) Set the EPROM programmer to the MBM27C256A.

- (2) Load program data into the EPROM programmer at 0007<sup>H</sup> to 7FFF<sup>H</sup>. (Note that addresses 8000<sup>H</sup> to FFFF<sup>H</sup> in the operating mode assign to 0000<sup>H</sup> to 7FFF<sup>H</sup> in EPROM mode).

- (3) Load option data into addresses 0000H to 0006H of the EPROM programmer. (For information about each corresponding option, see "8. OTPROM Option Bit Map".)

- (4) Program with the EPROM programmer.

## 4. Recommended Screening Conditions

High-temperature aging is recommended as the pre-assembly screening procedure for a product with a blanked OTPROM microcomputer program.

## 5. Programming Yield

All bits cannot be programmed at Fujitsu shipping test to a blanked OTPROM microcomputer, due to its nature. For this reason, a programming yield of 100% cannot be assured at all times.

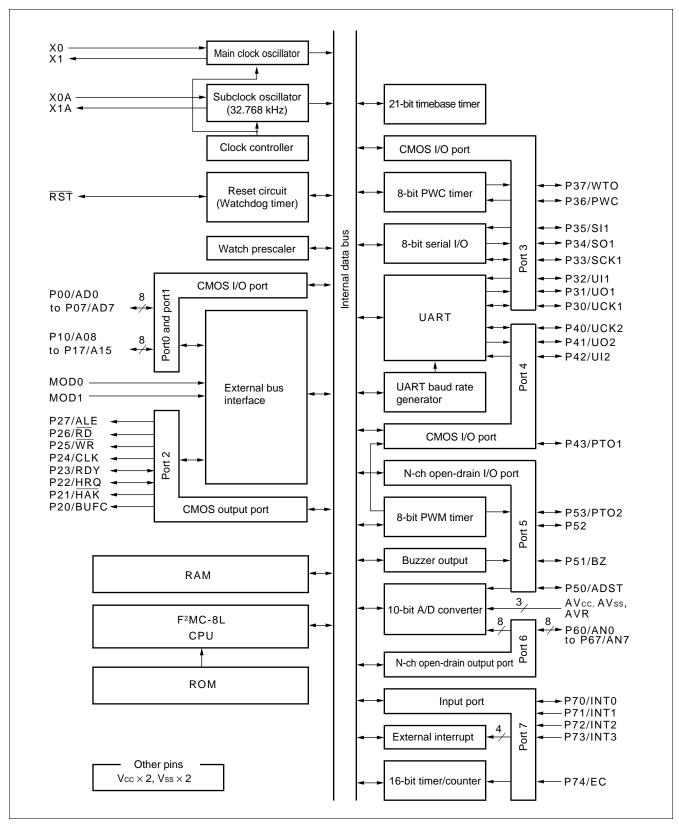

## BLOCK DIAGRAM

## CPU CORE

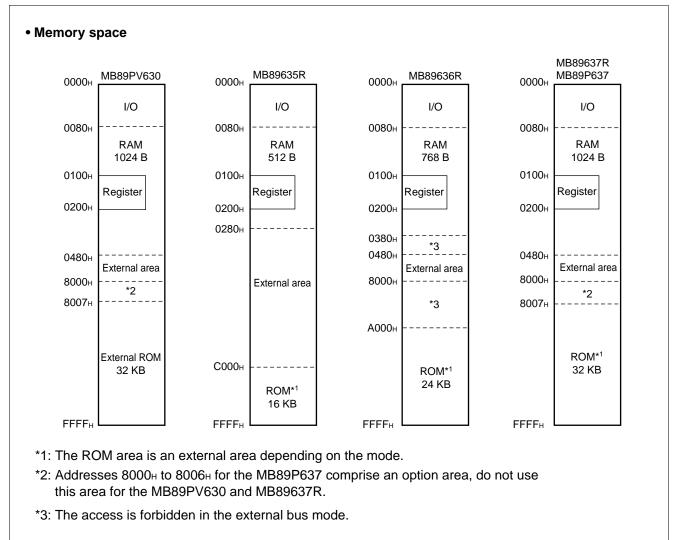

## 1. Memory Space

The microcontrollers of the MB89630R series offer 64 Kbytes of memory for storing all of I/O, data, and program areas. The I/O area is located at the lowest address. The data area is provided immediately above the I/O area. The data area can be divided into register, stack, and direct areas according to the application. The program area is located at exactly the opposite end of I/O area, that is, near the highest address. Provide the tables of interrupt reset vectors and vector call instructions toward the highest address within the program area. The memory space of the MB89630R series is structured as illustrated below.

The following general-purpose registers are provided:

General-purpose registers: An 8-bit register for storing data

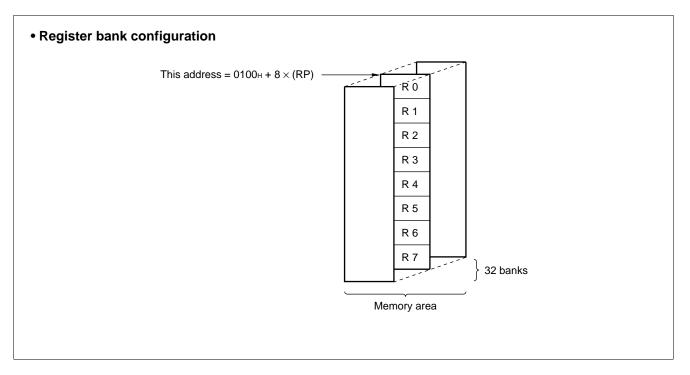

The general-purpose registers are 8 bits and located in the register banks of the memory. One bank contains eight registers and up to a total of 32 banks can be used on the MB89630R series. The bank currently in use is indicated by the register bank pointer (RP).

| Address     | Read/write              | Register name | Register description                                                                |  |  |  |  |

|-------------|-------------------------|---------------|-------------------------------------------------------------------------------------|--|--|--|--|

| 20н         | (R/W)                   | ADC1          | A/D converter control register 1                                                    |  |  |  |  |

| 21н         | (R/W)                   | ADC2          | A/D converter control register 2                                                    |  |  |  |  |

| 22н         | (R/W)                   | ADDH          | A/D converter data register (H)                                                     |  |  |  |  |

| 23н         | (R/W)                   | ADDL          | A/D converter data register (L)                                                     |  |  |  |  |

| 24н         | (R/W)                   | EIC1          | External interrupt control register 1                                               |  |  |  |  |

| 25н         | (R/W)                   | EIC2          | External interrupt control register 2                                               |  |  |  |  |

| 26н         |                         | Vac           | ancy                                                                                |  |  |  |  |

| 27н         |                         | Vac           | ancy                                                                                |  |  |  |  |

| 28н         | (R/W)                   | CNTR1         | PWM timer control register 1                                                        |  |  |  |  |

| 29н         | (R/W)                   | CNTR2         | PWM timer control register 2                                                        |  |  |  |  |

| 2Ан         | (R/W)                   | CNTR3         | PWM timer control register 3                                                        |  |  |  |  |

| 2Вн         | (W)                     | COMR1         | PWM timer compare register 1                                                        |  |  |  |  |

| 2Сн         | (W)                     | COMR2         | PWM timer compare register 2                                                        |  |  |  |  |

| 2Dн         | (R/W)                   | SMC           | UART serial mode control register                                                   |  |  |  |  |

| 2Ен         | (R/W)                   | SRC           | UART serial rate control register                                                   |  |  |  |  |

| 2Fн         | (R/W)                   | SSD           | UART serial status/data register                                                    |  |  |  |  |

| 30н         | (R)<br>(W)              | SIDR<br>SODR  | UART serial input data control register<br>UART serial output data control register |  |  |  |  |

| 31н to 7Вн  |                         | Vac           | ancy                                                                                |  |  |  |  |

| 7Сн         | (W)                     | ILR1          | Interrupt level setting register 1                                                  |  |  |  |  |

| 7Dн         | (W)                     | ILR2          | Interrupt level setting register 2                                                  |  |  |  |  |

| <b>7</b> Ен | (W)                     | ILR3          | Interrupt level setting register 3                                                  |  |  |  |  |

| 7Fн         | 7F <sub>H</sub> Vacancy |               |                                                                                     |  |  |  |  |

Note: Do not use vacancies.

| <b>.</b>              |        | <b>D</b> .                                                                   |                                                                                                                                                                |      | Value |      |      | = -40°C to +85°C                 |  |

|-----------------------|--------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|------|----------------------------------|--|

| Parameter             | Symbol | Pin name                                                                     | Condition                                                                                                                                                      | Min. | Тур.  | Max. | Unit | Remarks                          |  |

| Pull-up<br>resistance | Rpull  | P00 to P07, P10 to P17,<br>P30 to P37, P40 to P43,<br>P50 to P53, P72 to P74 | VI = 0.0 V                                                                                                                                                     | 25   | 50    | 100  | kΩ   | With pull-up<br>resistor         |  |

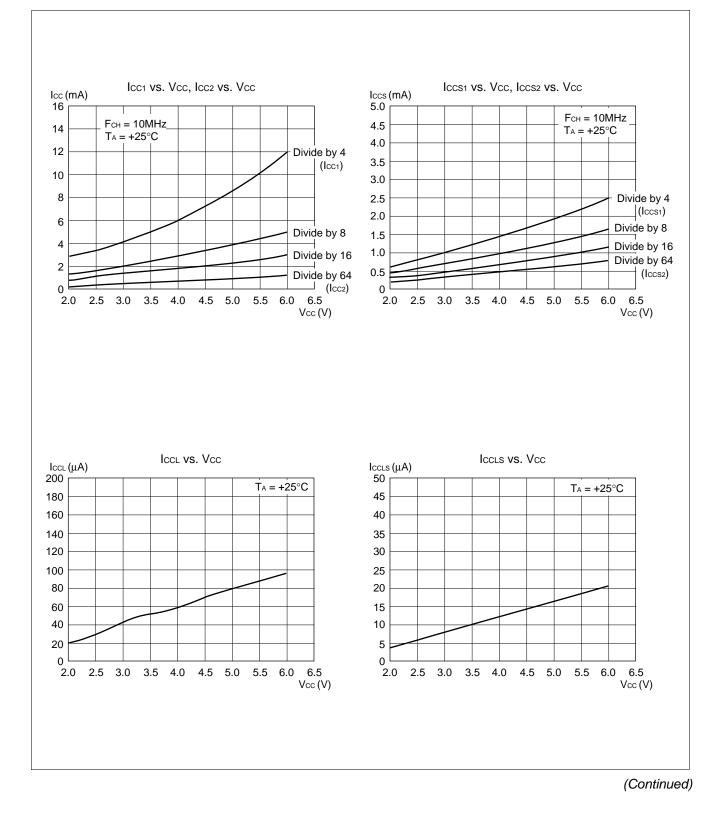

|                       | Icc1   |                                                                              | $F_{CH} = 10 \text{ MHz}$<br>$V_{CC} = 5.0 \text{ V}$<br>$t_{inst}^{*2} = 0.4 \mu\text{s}$                                                                     | _    | 12    | 20   | mA   |                                  |  |

|                       | Icc2   |                                                                              | $F_{CH} = 10 \text{ MHz}$<br>$V_{CC} = 3.0 \text{ V}$                                                                                                          | _    | 1.0   | 2    | mA   | MB89635R/<br>636R/637R/<br>PV630 |  |

|                       |        |                                                                              | $t_{inst}^{*2} = 6.4 \ \mu s$                                                                                                                                  | _    | 1.5   | 2.5  | mA   | MB89P637                         |  |

|                       | Iccs1  |                                                                              | $ \begin{array}{c} F_{CH} = 10 \text{ MHz} \\ \Psi \\ V_{CC} = 5.0 \text{ V} \\ t_{inst}^{*2} = 0.4  \mu s \end{array} $                                       | _    | 3     | 7    | mA   |                                  |  |

|                       | Iccs2  |                                                                              |                                                                                                                                                                | _    | 0.5   | 1.5  | mA   |                                  |  |

| Power supply          | lcc∟   |                                                                              | FcL = 32.768 kHz,<br>Vcc = 3.0 V<br>Subclock mode                                                                                                              | _    | 50    | 100  | μΑ   | MB89635R/<br>636R/637R/<br>PV630 |  |

| current <sup>*1</sup> |        |                                                                              | Subclock mode                                                                                                                                                  | —    | 500   | 700  | μA   | MB89P637                         |  |

|                       | lcc∟s  |                                                                              | $\label{eq:Fcl} \begin{array}{l} F_{\text{CL}} = 32.768 \text{ kHz}, \\ V_{\text{CC}} = 3.0 \text{ V} \\ \textbf{Subclock sleep} \\ \textbf{mode} \end{array}$ | _    | 25    | 50   | μΑ   |                                  |  |

|                       | Ісст   |                                                                              | FcL = 32.768 kHz,<br>Vcc = 3.0 V<br>● Watch mode<br>● Main clock stop<br>mode at dual-<br>clock system                                                         | _    | 3     | 15   | μΑ   |                                  |  |

|                       | Іссн   |                                                                              | <ul> <li>T<sub>A</sub> = +25°C</li> <li>Subclock stop mode</li> <li>Main clock stop mode at single-clock system</li> </ul>                                     | _    | _     | 1    | μΑ   |                                  |  |

$(AVcc = Vcc = 5.0 V, AVss = Vss = 0.0 V, T_A = -40^{\circ}C to +85^{\circ}C)$

(Continued)

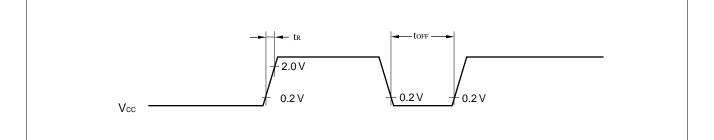

#### (2) Specification for Power-on Reset

$(AV_{SS} = V_{SS} = 0.0 \text{ V}, \text{ } T_{A} = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C})$

| Deremeter                 | Symbol     | Condition | Va | ue        | Unit | Remarks                                        |

|---------------------------|------------|-----------|----|-----------|------|------------------------------------------------|

| Parameter                 | Symbol     | Min. Max. |    | Min. Max. |      | Rellidiks                                      |

| Power supply rising time  | <b>t</b> R |           | —  | 50        | ms   | Power-on reset function only                   |

| Power supply cut-off time | toff       |           | 1  | _         | ms   | Min. interval time for the next power-on reset |

Note: Make sure that power supply rises within the selected oscillation stabilization time. If power supply voltage needs to be varied in the course of operation, a smooth voltage rise is recommended.

#### (3) Clock Timing

$(AV_{SS} = V_{SS} = 0.0 \text{ V}, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C})$

| Parameter                           | Symbol        | Pin name | Condition | Value |        | Unit | Remarks |                |

|-------------------------------------|---------------|----------|-----------|-------|--------|------|---------|----------------|

| Falailletei                         | Symbol        |          | Condition | Min.  | Тур.   | Max. | Unit    | Remarks        |

| Clock frequency                     | Fсн           | X0, X1   |           | 1     | —      | 10   | MHz     |                |

| Clock frequency                     | Fc∟           | X0A, X1A |           | _     | 32.768 |      | kHz     |                |

|                                     | <b>t</b> HCYL | X0, X1   |           | 100   |        | 1000 | ns      |                |

| Clock cycle time                    | <b>t</b> LCYL | X0A, X1A |           | _     | 30.5   | _    | μs      |                |

| Input clock pulse width             | Pwн<br>Pw∟    | X0       |           | 20    | _      | _    | ns      | External clock |

| Input clock pulse width             | Pwlh<br>Pwll  | X0A      |           | _     | 15.2   | _    | μs      | External clock |

| Input clock rising/<br>falling time | tcr<br>tcf    | X0       |           |       |        | 10   | ns      | External clock |

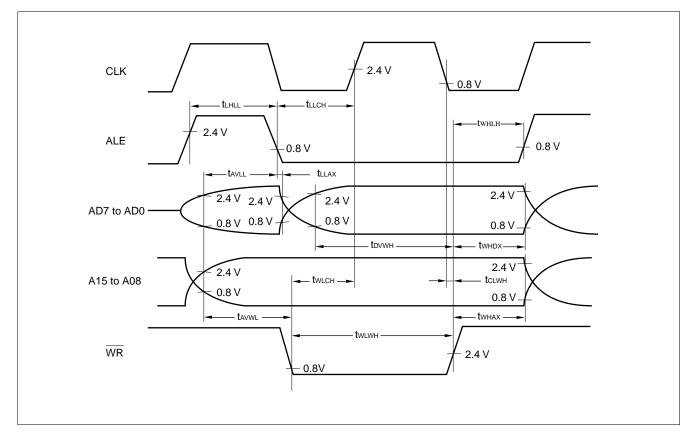

### (7) Bus Write Timing

| Devementer                                                | Symbol                              | Din nomo          | Condition | Value                              | e    | Unit | Domorko |

|-----------------------------------------------------------|-------------------------------------|-------------------|-----------|------------------------------------|------|------|---------|

| Parameter                                                 | Parameter Symbol Pin name Condition |                   | Condition | Min.                               | Max. | Unit | Remarks |

| Valid address $\rightarrow$ ALE $\downarrow$ time         | tavll                               | AD7 to AD0,       |           | 1/4 t <sub>inst</sub> *1-64 ns*2   | _    | μs   |         |

| ALE $\downarrow$ time $\rightarrow$ address loss time     | tllax                               | ALE<br>A15 to A08 |           | 5                                  | —    | ns   |         |

| Valid address $\rightarrow \overline{WR} \downarrow time$ | tavwl                               | WR, ALE           |           | 1/4 t <sub>inst</sub> *1-60 ns*2   | _    | μs   |         |

| WR pulse width                                            | twlwн                               | WR                |           | 1/2 t <sub>inst</sub> *1 – 20 ns*2 | —    | μs   |         |

| Write data $\rightarrow \overline{WR} \uparrow$ time      | tovwн                               | AD7 to AD0, WR    |           | 1/2 t <sub>inst</sub> *1-60 ns*2   | —    | μs   |         |

| $\overline{WR} \uparrow \rightarrow address  loss time$   | twhax                               | WR, A15 to A08    |           | 1/4 t <sub>inst</sub> *1-40 ns*2   | —    | μs   |         |

| $\overline{WR} \uparrow \rightarrow data  hold time$      | <b>t</b> whdx                       | AD7 to AD0, WR    |           | 1/4 t <sub>inst</sub> *1-40 ns*2   | —    | μs   |         |

| $\overline{WR} \uparrow \rightarrow ALE \uparrow time$    | twнLн                               | WR, ALE           |           | 1/4 t <sub>inst</sub> *1-40 ns*2   | —    | μs   |         |

| $\overline{WR} \downarrow \rightarrow CLK \uparrow time$  | twlch                               | WR, CLK           |           | 1/4 t <sub>inst</sub> *1-40 ns*2   | —    | μs   |         |

| $CLK \downarrow \to \overline{WR} \uparrow time$          | <b>t</b> clwh                       | WR, ULN           |           | 0                                  | —    | ns   |         |

| ALE pulse width                                           | tlhll                               | ALE               |           | 1/4 t <sub>inst</sub> *1-35 ns*2   | _    | μs   |         |

| $ALE \downarrow \rightarrow CLK \uparrow time$            | <b>t</b> llch                       | ALE,CLK           |           | 1/4 t <sub>inst</sub> *1-30 ns*2   | —    | μs   |         |

#### (Vcc = 5.0 V±10%, FcH = 10 MHz, AVss = Vss= 0.0 V, TA = $-40^{\circ}C$ to $+85^{\circ}C$ )

\*1: For information on t<sub>inst</sub>, see "(4) Instruction Cycle".

\*2: This characteristics are also applicable to the bus read timing.

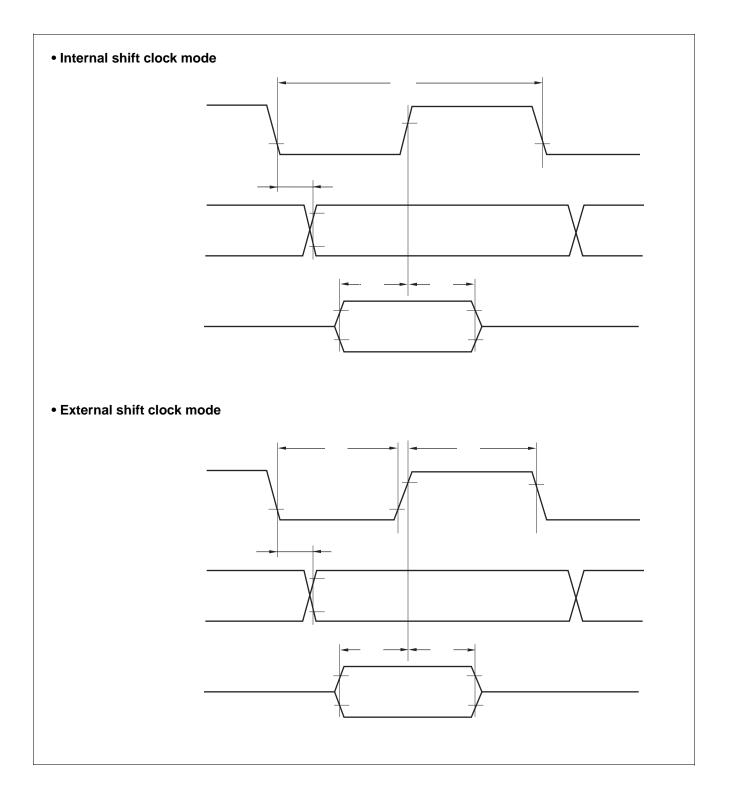

### (9) Serial I/O Timing

| Parameter                                                                                                                                                                                                                      | Parameter Symbol Pin name Condition |                                     | Condition            | Va                      | lue | Unit | Remarks  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------------------------------|----------------------|-------------------------|-----|------|----------|

| Parameter                                                                                                                                                                                                                      | Symbol                              | Fin name                            | Condition            | Min. Max.               |     | Unit | Relliars |

| Serial clock cycle time                                                                                                                                                                                                        | tscyc                               | SCK1, UCK1,<br>UCK2                 |                      | 2 t <sub>inst</sub> *   | _   | μs   |          |

| $\begin{array}{l} SCK1 \downarrow \to SO1 \text{ time} \\ UCK1 \downarrow \to UO1 \text{ time} \\ UCK2 \downarrow \to UO2 \text{ time} \end{array}$                                                                            | ts∟ov                               | SCK1, SO1<br>UCK1, UO1<br>UCK2, UO2 | Internal             | -200                    | 200 | ns   |          |

| Valid SI1 → SCK1 $\uparrow$<br>Valid UI1 → UCK1 $\uparrow$<br>Valid UI2 → UCK2 $\uparrow$                                                                                                                                      | tıvsн                               | SI1, SCK1<br>UI1, UCK1<br>UI2, UCK2 | shift clock<br>mode  | 1/2 t <sub>inst</sub> * | _   | μs   |          |

| $\begin{array}{l} SCK1 \uparrow \to valid \; SI1 \; hold \; time \\ UCK1 \uparrow \to valid \; UI1 \; hold \; time \\ UCK2 \uparrow \to valid \; UI2 \; hold \; time \end{array}$                                              | tsнıx                               | SCK1, SI1<br>UCK1, UI1<br>UCK2, UI2 |                      | 1/2 t <sub>inst</sub> * | _   | μs   |          |

| Serial clock "H" pulse width                                                                                                                                                                                                   | tshsl                               | SCK1, UCK1,<br>UCK2                 |                      | 1 t <sub>inst</sub> *   | _   | μs   |          |

| Serial clock "L" pulse width                                                                                                                                                                                                   | tslsh                               | SCK1, UCK1,<br>UCK2                 |                      | 1 t <sub>inst</sub> *   | _   | μs   |          |

| $\begin{array}{l} SCK1 \downarrow \to SO1 \text{ time} \\ UCK1 \downarrow \to UO1 \text{ time} \\ UCK2 \downarrow \to UO2 \text{ time} \end{array}$                                                                            | ts∟ov                               | SCK1, SO1<br>UCK1, UO1<br>UCK2, UO2 | External shift clock | 0                       | 200 | ns   |          |

| Valid SI1 → SCK1 $\uparrow$<br>Valid UI1 → UCK1 $\uparrow$<br>Valid UI2 → UCK2 $\uparrow$                                                                                                                                      | tıvsн                               | SI1, SCK1<br>UI1, UCK1<br>UI2, UCK2 | mode                 | 1/2 t <sub>inst</sub> * |     | μs   |          |

| $\begin{array}{l} \text{SCK1} \downarrow \rightarrow \text{valid SI1 hold time} \\ \text{UCK1} \downarrow \rightarrow \text{valid UI1 hold time} \\ \text{UCK2} \downarrow \rightarrow \text{valid UI2 hold time} \end{array}$ | tsнıx                               | SCK1, SI1<br>UCK1, UI1<br>UCK2, UI2 |                      | 1/2 t <sub>inst</sub> * |     | μs   |          |

(Vcc = 5.0 V $\pm$ 10%, FcH = 10 MHz, AVss = Vss= 0.0 V, TA = -40°C to +85°C)

\* : For information on tinst, see "(4) Instruction Cycle".

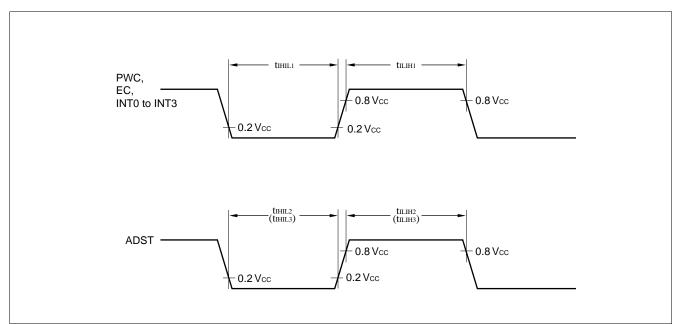

### (10) Peripheral Input Timing

| Baramatar                          | Symbol          | Pin name             | Value                     |      | Unit | Remarks    |

|------------------------------------|-----------------|----------------------|---------------------------|------|------|------------|

| Parameter                          | Symbol Pin name |                      | Min.                      | Max. | Unit | Remarks    |

| Peripheral input "H" pulse width 1 | tiliH1          | PWC, INT0 to INT3,EC | 2 tinst*                  | _    | μs   |            |

| Peripheral input "L" pulse width 1 | tiHi∟1          |                      | 2 tinst*                  |      | μs   |            |

| Peripheral input "H" pulse width 2 | tilih2          | ADST                 | 2 <sup>8</sup> tinst*     |      | μs   | A/D mode   |

| Peripheral input "L" pulse width 2 | tihil2          | ADST                 | 2 <sup>8</sup> tinst*     |      | μs   | A/D mode   |

| Peripheral input "H" pulse width 3 | <b>t</b> ILIH3  | ADST                 | $2^8 t_{\text{inst}}^{*}$ |      | μs   | Sense mode |

| Peripheral input "L" pulse width 3 | tініlз          |                      | 2 <sup>8</sup> tinst*     |      | μs   | Sense mode |

#### (Vcc = 5.0 V $\pm$ 10%, AVss = Vss = 0.0 V, T<sub>A</sub> = -40°C to +85°C)

\* : For information on tinst, see "(4) Instruction Cycle".

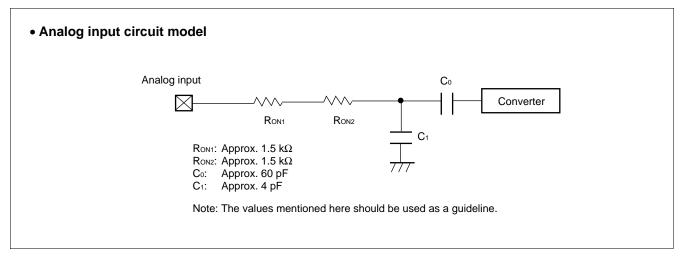

### 7. Notes on Using A/D Converter

#### · Input impedance of the analog input pins

The output impedance of the external circuit for the analog input must satisfy the following conditions. If the output impedance of the external circuit is too high, an analog voltage sampling time might be insufficient (sampling time = 6  $\mu$ s at 10 MHz oscillation.) Therefore, it is recommended to keep the output impedance of the external circuit below 10 k $\Omega$ .

#### • Error

The smaller the | AVR-AVss |, the greater the error would become relatively.

## (5) Power Supply Current (External Clock)

## ■ MASK OPTIONS

| No. | Part number                                                                                                                                                                                                                                                                     | MB89637R<br>Specify when Set with EPROM |                     | MB89PV630                                                             |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|---------------------|-----------------------------------------------------------------------|

|     | Specifying procedure                                                                                                                                                                                                                                                            |                                         |                     | Setting not possible                                                  |

| 1   | Pull-up resistors<br>P00 to P07, P10 to P17,<br>P30 to P37, P40 to P43,<br>P50 to P53, P72 to P74                                                                                                                                                                               | Selectable by pin                       | Can be set per pin* | Fixed to "without pull-up resistor"                                   |

| 2   | Power-on reset selection<br>With power-on reset<br>Without power-on reset                                                                                                                                                                                                       | Selectable                              | Setting possible    | Fixed to "with power-on reset"                                        |

| 3   | Selection of the main clock<br>oscillation stabilization time<br>(at 10 MHz)<br>2 <sup>18</sup> /Fсн (Approx. 26.2 ms)<br>2 <sup>17</sup> /Fсн (Approx. 13.1 ms)<br>2 <sup>14</sup> /Fсн (Approx. 1.6 ms)<br>2 <sup>4</sup> /Fсн (Approx. 1.6 µs)<br>Fсн : Main clock frequency | Selectable                              | Setting possible    | Fixed to 2 <sup>18</sup> /Fсн<br>(Approx. 26.2 ms)                    |

| 4   | Reset pin output<br>Reset output provided<br>No reset output                                                                                                                                                                                                                    | Selectable                              | Setting possible    | Fixed to "with reset output"                                          |

| 5   | Single/dual-clock system option<br>Single clock<br>Dual clock                                                                                                                                                                                                                   | Selectable                              | Setting possible    | MB89PV630-101 Single-clock system<br>MB89PV630-102 Dual-clock systems |

\* : For P50 to P53, fixed to "Without pull-up resistor."

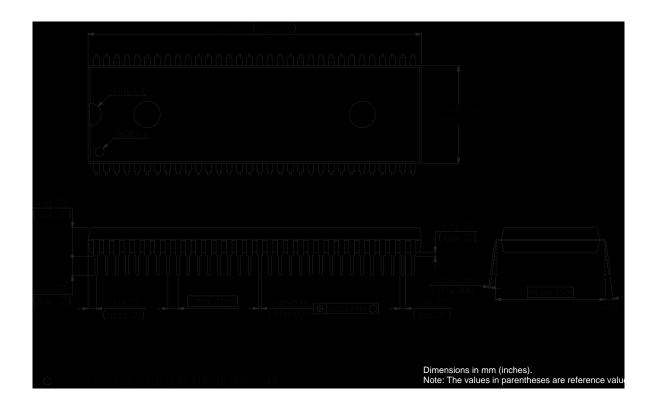

## ■ PACKAGE DIMENSIONS

Please confirm the latest Package dimension by following URL. http://edevice.fujitsu.com/package/en-search/

(Continued)

## ■ MAIN CHANGES IN THIS EDITION

| Page | Section        | Change Results                                       |

|------|----------------|------------------------------------------------------|

| 49   | ■ MASK OPTIONS | Changed the explanation for "*" in "■ MASK OPTIONS". |

The vertical lines marked in the left side of the page show the changes.