#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | F <sup>2</sup> MC-8L                                                         |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 10MHz                                                                        |

| Connectivity               | EBI/EMI, Serial I/O, UART/USART                                              |

| Peripherals                | POR, PWM, WDT                                                                |

| Number of I/O              | 53                                                                           |

| Program Memory Size        | 16KB (16K x 8)                                                               |

| Program Memory Type        | Mask ROM                                                                     |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 512 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 6V                                                                    |

| Data Converters            | A/D 8x10b                                                                    |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

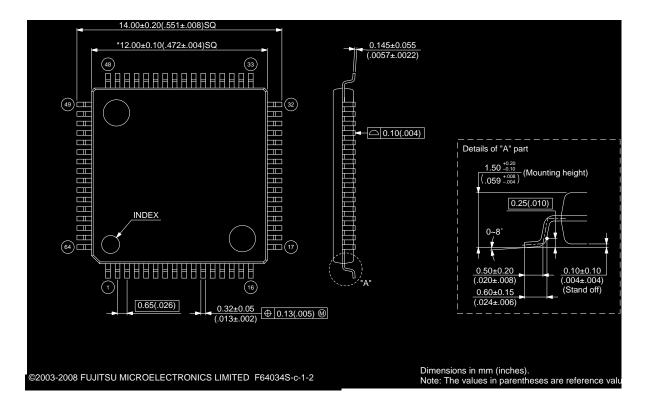

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 64-BQFP                                                                      |

| Supplier Device Package    | 64-QFP (14x20)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb89635rpf-g-1485 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 8-bit Proprietary Microcontroller

### CMOS

# F<sup>2</sup>MC-8L MB89630R Series

# MB89635R/636R/637R/P637/PV630

###

The MB89630R series has been developed as a general-purpose version of the F<sup>2</sup>MC\*-8L family consisting of proprietary 8-bit, single-chip microcontrollers.

In addition to a compact instruction set, the microcontrollers contain a variety of peripheral functions such as dual-clock control system, five operating speed control stages, a UART, timers, a PWM timer, a serial interface, an A/D converter, an external interrupt, and a watch prescaler.

\* : F<sup>2</sup>MC is the abbreviation for Fujitsu Flexible Microcontroller.

### ■ FEATURES

- · High-speed operating capability at low voltage

- Minimum execution time: 0.4  $\mu s@3.5$  V, 0.8  $\mu s@2.7$  V

- F<sup>2</sup>MC-8L family CPU core

Instruction set optimized for controllers

Multiplication and division instructions 16-bit arithmetic operations Test and branch instructions Bit manipulation instructions, etc.

Five types of timers

8-bit PWM timer: 2 channels (Also usable as a reload timer)

8-bit pulse-width count timer (Continuous measurement capable, applicable to remote control, etc.)

16-bit timer/counter

21-bit timebase timer

(Continued)

For the information for microcontroller supports, see the following web site.

http://edevice.fujitsu.com/micom/en-support/

- UART

- CLK-synchronous/CLK-asynchronous data transfer capable (6, 7, and 8 bits)

- Serial interface Switchable transfer direction to allows communication with various equipment.

- 10-bit A/D converter Start by an external input capable

- External interrupt: 4 channels Four channels are independent and capable of wake-up from low-power consumption modes (with an edge detection function).

- Low-power consumption modes

Stop mode (Oscillation stops to minimize the current consumption.)

Sleep mode (The CPU stops to reduce the current consumption to approx. 1/3 of normal.)

Subclock mode

Watch mode

- Bus interface function With hold and ready function

### ■ DIFFERENCES AMONG PRODUCTS

#### 1. Memory Size

Before evaluating using the piggyback product, verify its differences from the product that will actually be used. Take particular care on the following points:

• On the MB89P637, the program area starts from address 8007<sup>H</sup> but on the MB89PV630 and MB89637R starts from 8000<sup>H</sup>.

(On the MB89P637, addresses 8000<sup>H</sup> to 8006<sup>H</sup> comprise the option setting area, option settings can be read by reading these addresses. On the MB89PV630/MB89637R, addresses 8000<sup>H</sup> to 8006<sup>H</sup> could also be used as a program ROM. However, do not use these addresses in order to maintain compatibility of the MB89P637.)

- The stack area, etc., is set at the upper limit of the RAM.

- The external area is used.

### 2. Current Consumption

- In the case of the MB89PV630, add the current consumed by the EPROM which connected to the top socket.

#### 3. Mask Options

Functions that can be selected as options and how to designate these options vary by the product.

Before using options check section "■ Mask Options".

Take particular care on the following points:

- A pull-up resistor cannot be set for P50 to P53 on the MB89P637.

- Options are fixed on the MB89PV630.

#### 4. Differences between the MB89630 and MB89630R Series

Memory access area

There are no difference between the access area of MB89635/MB89635R, and that of MB89637/MB89637R. The access area of MB89636 is different from that of the MB89636R when using in external bus mode.

| Address        | Memory area   |                   |  |  |

|----------------|---------------|-------------------|--|--|

| Address        | MB89636       | MB89636R          |  |  |

| 0000н to 007Fн | I/O area      | I/O area          |  |  |

| 0080н to 037Fн | RAM area      | RAM area          |  |  |

| 0380н to 047Fн |               | Access prohibited |  |  |

| 0480н to 7FFFн | External area | External area     |  |  |

| 8000н to 9FFFн |               | Access prohibited |  |  |

| A000н to FFFFн | ROM area      | ROM area          |  |  |

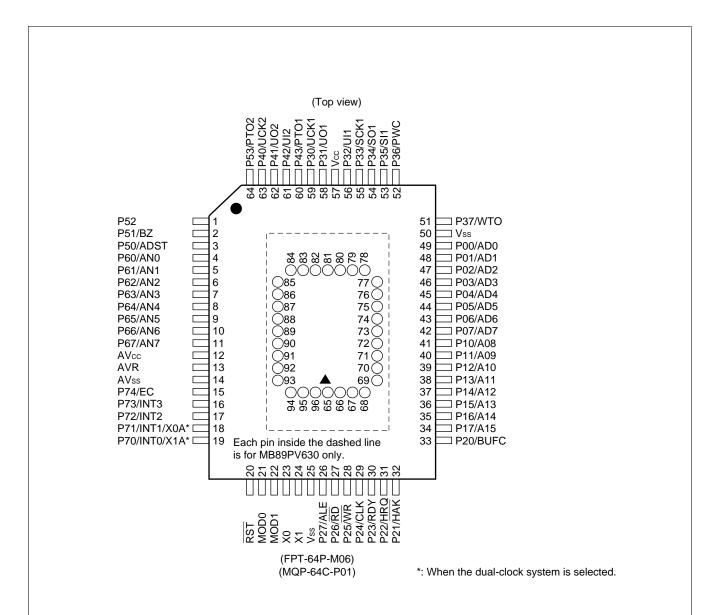

#### • Pin assignment on package top (MB89PV630 only)

| Pin no. | Pin name |

|---------|----------|---------|----------|---------|----------|---------|----------|

| 65      | N.C.     | 73      | A2       | 81      | N.C.     | 89      | ŌĒ       |

| 66      | Vpp      | 74      | A1       | 82      | O4       | 90      | N.C.     |

| 67      | A12      | 75      | A0       | 83      | O5       | 91      | A11      |

| 68      | A7       | 76      | N.C.     | 84      | O6       | 92      | A9       |

| 69      | A6       | 77      | 01       | 85      | 07       | 93      | A8       |

| 70      | A5       | 78      | O2       | 86      | O8       | 94      | A13      |

| 71      | A4       | 79      | O3       | 87      | CE       | 95      | A14      |

| 72      | A3       | 80      | Vss      | 88      | A10      | 96      | Vcc      |

N.C.: Internally connected. Do not use.

|                                            | Pin no.            |                                          |          | <b>O</b> imerrit |                                                                                                                                                    |

|--------------------------------------------|--------------------|------------------------------------------|----------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| SH-DIP <sup>*1</sup><br>MDIP <sup>*2</sup> | QFP2 <sup>*3</sup> | QFP1 <sup>*4</sup><br>MQFP <sup>*5</sup> | Pin name | Circuit<br>type  | Function                                                                                                                                           |

| 33                                         | 25                 | 26                                       | P27/ALE  | Н                | General-purpose output port<br>When an external bus is used, this port functions<br>as an address latch signal output.                             |

| 2                                          | 58                 | 59                                       | P30/UCK1 | G                | General-purpose I/O port<br>Also serves as the clock I/O 1 for the UART.<br>This port is a hysteresis input type.                                  |

| 1                                          | 57                 | 58                                       | P31/UO1  | F                | General-purpose I/O port<br>Also serves as the data output 1 for the UART.                                                                         |

| 63                                         | 55                 | 56                                       | P32/UI1  | G                | General-purpose I/O port<br>Also serves as the data input 1 for the UART.<br>This port is a hysteresis input type.                                 |

| 62                                         | 54                 | 55                                       | P33/SCK1 | G                | General-purpose I/O port<br>Also serves as the data input for the 8-bit serial<br>I/O.<br>This port is a hysteresis input type.                    |

| 61                                         | 53                 | 54                                       | P34/SO1  | F                | General-purpose I/O port<br>Also serves as the data output for the 8-bit serial<br>I/O.                                                            |

| 60                                         | 52                 | 53                                       | P35/SI1  | G                | General-purpose I/O port<br>Also serves as the data input for the 8-bit serial<br>I/O.<br>This port is a hysteresis input type.                    |

| 59                                         | 51                 | 52                                       | P36/PWC  | G                | General-purpose I/O port<br>Also serves as the measured pulse input for the<br>8-bit pulse width counter.<br>This port is a hysteresis input type. |

| 58                                         | 50                 | 51                                       | P37/WTO  | F                | General-purpose I/O port<br>Also serves as the toggle output for the 8-bit pulse<br>width counter.                                                 |

| 6                                          | 62                 | 63                                       | P40/UCK2 | G                | General-purpose I/O port<br>Also serves as the clock I/O 2 for the UART.<br>This port is a hysteresis input type.                                  |

| 5                                          | 61                 | 62                                       | P41/UO2  | F                | General-purpose I/O port<br>Also serves as the data output 2 for the UART.                                                                         |

| 4                                          | 60                 | 61                                       | P42/UI2  | G                | General-purpose I/O port<br>Also serves as the data input 2 for the UART.<br>This port is a hysteresis input type.                                 |

| 3                                          | 59                 | 60                                       | P43/PTO1 | F                | General-purpose I/O port<br>Also serves as the toggle output for the 8-bit PWM<br>timer.                                                           |

| 10                                         | 2                  | 3                                        | P50/ADST | K                | General-purpose I/O port<br>Also serves as an A/D converter external<br>activation.<br>This port is a hysteresis input type.                       |

\*1: DIP-64P-M01

\*2: MDP-64C-P02

\*4: FPT-64P-M06

\*5: MQP-M64C-P01

\*3: FPT-64P-M23

| Pin                                                | no.                                                | Pin name                                            | I/O | Function                                                 |

|----------------------------------------------------|----------------------------------------------------|-----------------------------------------------------|-----|----------------------------------------------------------|

| MDIP                                               | MQFP                                               | Pin name                                            | 1/0 | Function                                                 |

| 65                                                 | 66                                                 | Vpp                                                 | 0   | "H" level output pin                                     |

| 66<br>67<br>68<br>69<br>70<br>71<br>72<br>73<br>74 | 67<br>68<br>69<br>70<br>71<br>72<br>73<br>74<br>75 | A12<br>A7<br>A6<br>A5<br>A4<br>A3<br>A2<br>A1<br>A0 | 0   | Address output pins                                      |

| 75<br>76<br>77                                     | 77<br>78<br>79                                     | 01<br>02<br>03                                      | I   | Data input pins                                          |

| 78                                                 | 80                                                 | Vss                                                 | 0   | Power supply (GND) pin                                   |

| 79<br>80<br>81<br>82<br>83                         | 82<br>83<br>84<br>85<br>86                         | O4<br>O5<br>O6<br>O7<br>O8                          | I   | Data input pins                                          |

| 84                                                 | 87                                                 | CE                                                  | 0   | ROM chip enable pin<br>Outputs "H" during standby.       |

| 85                                                 | 88                                                 | A10                                                 | 0   | Address output pin                                       |

| 86                                                 | 89                                                 | ŌĒ                                                  | 0   | ROM output enable pin<br>Outputs "L" at all times.       |

| 87<br>88<br>89                                     | 91<br>92<br>93                                     | A11<br>A9<br>A8                                     | 0   | Address output pins                                      |

| 90                                                 | 94                                                 | A13                                                 | 0   |                                                          |

| 91                                                 | 95                                                 | A14                                                 | 0   |                                                          |

| 92                                                 | 96                                                 | Vcc                                                 | 0   | EPROM power supply pin                                   |

|                                                    | 65<br>76<br>81<br>90                               | N.C.                                                |     | Internally connected pins<br>Be sure to leave them open. |

• External EPROM pins (MB89PV630 only)

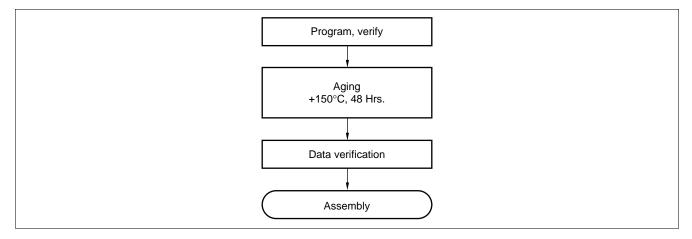

#### • Programming procedure

- (1) Set the EPROM programmer to the MBM27C256A.

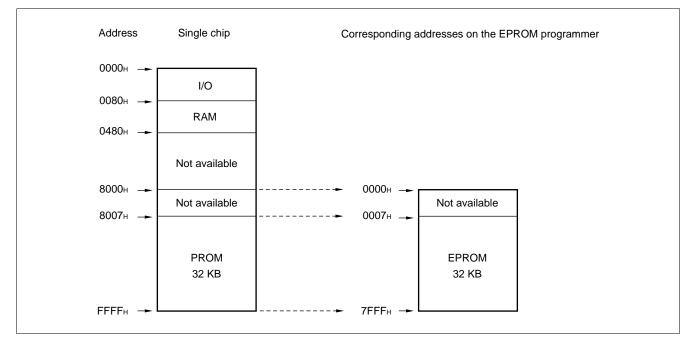

- (2) Load program data into the EPROM programmer at 0007<sup>H</sup> to 7FFF<sup>H</sup>. (Note that addresses 8000<sup>H</sup> to FFFF<sup>H</sup> in the operating mode assign to 0000<sup>H</sup> to 7FFF<sup>H</sup> in EPROM mode).

- (3) Load option data into addresses 0000H to 0006H of the EPROM programmer. (For information about each corresponding option, see "8. OTPROM Option Bit Map".)

- (4) Program with the EPROM programmer.

### 4. Recommended Screening Conditions

High-temperature aging is recommended as the pre-assembly screening procedure for a product with a blanked OTPROM microcomputer program.

### 5. Programming Yield

All bits cannot be programmed at Fujitsu shipping test to a blanked OTPROM microcomputer, due to its nature. For this reason, a programming yield of 100% cannot be assured at all times.

### ■ PROGRAMMING TO THE EPROM WITH PIGGYBACK/EVALUATION DEVICE

#### 1. EPROM for Use

MBM27C256A-20CZ, MBM27C256A-20TV

#### 2. Memory Space

Memory space in each mode, such as 32-Kbyte PROM, option area is diagrammed below.

### 3. Programming to the EPROM

- (1) Set the EPROM programmer to the MBM27C256A.

- (3) Program to 0000H to 7FFFH with the EPROM programmer.

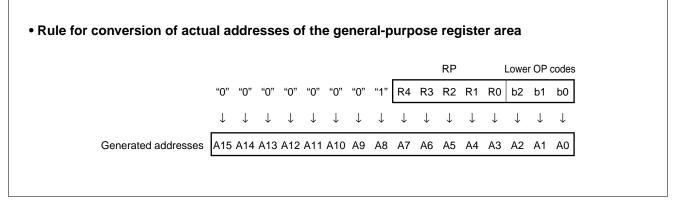

The RP indicates the address of the register bank currently in use. The relationship between the pointer contents and the actual address is based on the conversion rule illustrated below.

The CCR consists of bits indicating the results of arithmetic operations and the contents of transfer data and bits for control of CPU operations at the time of an interrupt.

- H-flag: Set to '1' when a carry or a borrow from bit 3 to bit 4 occurs as a result of an arithmetic operation. Cleared to '0' otherwise. This flag is for decimal adjustment instructions.

- I-flag: Interrupt is enabled when this flag is set to '1'. Interrupt is disabled when the flag is cleared to '0'. Cleared to '0' at the reset.

- IL1, IL0: Indicates the level of the interrupt currently allowed. Processes an interrupt only if its request level is higher than the value indicated by this bit.

| IL1 | IL0 | Interrupt level | High-low |

|-----|-----|-----------------|----------|

| 0   | 0   | 1               | High     |

| 0   | 1   |                 | t        |

| 1   | 0   | 2               |          |

| 1   | 1   | 3               | Low      |

- N-flag: Set to '1' if the MSB becomes to '1' as the result of an arithmetic operation. Cleared to '0' when the bit is cleared to '0'.

- Z-flag: Set to '1' when an arithmetic operation results in 0. Cleared to '0' otherwise.

- V-flag: Set to '1' if the complement on 2 overflows as a result of an arithmetic operation. Cleared to '0' if the overflow does not occur.

- C-flag: Set to '1' when a carry or a borrow from bit 7 occurs as a result of an arithmetic operation. Cleared to '0' otherwise.

Set to the shift-out value in the case of a shift instruction.

The following general-purpose registers are provided:

General-purpose registers: An 8-bit register for storing data

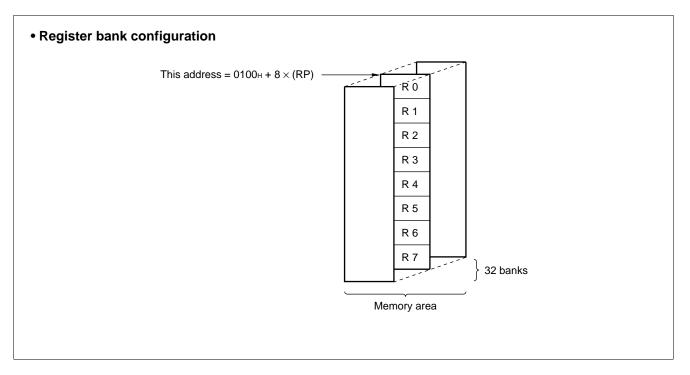

The general-purpose registers are 8 bits and located in the register banks of the memory. One bank contains eight registers and up to a total of 32 banks can be used on the MB89630R series. The bank currently in use is indicated by the register bank pointer (RP).

| Address     | Read/write | Register name | Register description                                                                |

|-------------|------------|---------------|-------------------------------------------------------------------------------------|

| 20н         | (R/W)      | ADC1          | A/D converter control register 1                                                    |

| 21н         | (R/W)      | ADC2          | A/D converter control register 2                                                    |

| 22н         | (R/W)      | ADDH          | A/D converter data register (H)                                                     |

| 23н         | (R/W)      | ADDL          | A/D converter data register (L)                                                     |

| 24н         | (R/W)      | EIC1          | External interrupt control register 1                                               |

| 25н         | (R/W)      | EIC2          | External interrupt control register 2                                               |

| 26н         |            | Vac           | ancy                                                                                |

| 27н         |            | Vac           | ancy                                                                                |

| 28н         | (R/W)      | CNTR1         | PWM timer control register 1                                                        |

| 29н         | (R/W)      | CNTR2         | PWM timer control register 2                                                        |

| 2Ан         | (R/W)      | CNTR3         | PWM timer control register 3                                                        |

| 2Вн         | (W)        | COMR1         | PWM timer compare register 1                                                        |

| 2Сн         | (W)        | COMR2         | PWM timer compare register 2                                                        |

| 2Dн         | (R/W)      | SMC           | UART serial mode control register                                                   |

| 2Ен         | (R/W)      | SRC           | UART serial rate control register                                                   |

| 2Fн         | (R/W)      | SSD           | UART serial status/data register                                                    |

| 30н         | (R)<br>(W) | SIDR<br>SODR  | UART serial input data control register<br>UART serial output data control register |

| 31н to 7Вн  |            | Vac           | ancy                                                                                |

| 7Сн         | (W)        | ILR1          | Interrupt level setting register 1                                                  |

| 7Dн         | (W)        | ILR2          | Interrupt level setting register 2                                                  |

| <b>7</b> Ен | (W)        | ILR3          | Interrupt level setting register 3                                                  |

| 7Fн         |            | Vac           | ancy                                                                                |

Note: Do not use vacancies.

### ■ ELECTRICAL CHARACTERISTICS

### 1. Absolute Maximum Ratings

(AVss = Vss = 0.0 V)

| Devenetor                              | Symbol          | Va      | lue       | Unit | Remarks                                                   |

|----------------------------------------|-----------------|---------|-----------|------|-----------------------------------------------------------|

| Parameter                              | Symbol          | Min.    | Max.      | Unit | Remarks                                                   |

| Power supply voltage                   | Vcc             | Vss-0.3 | Vss + 7.0 | V    | *                                                         |

| rower supply voltage                   | AVcc            | Vss-0.3 | Vss + 7.0 | V    | *                                                         |

| A/D converter reference input voltage  | AVR             | Vss-0.3 | Vss + 7.0 | V    | AVR must not exceed<br>"AVcc + 0.3 V".                    |

|                                        | Vı              | Vss-0.3 | Vcc + 0.3 | V    | Except P50 to P53                                         |

| Input voltage                          | Vı2             | Vss-0.3 | Vss + 7.0 | V    | P50 to P53                                                |

| Output voltage                         | Vo              | Vss-0.3 | Vcc + 0.3 | V    | Except P50 to P53                                         |

| Output voltage                         | V <sub>02</sub> | Vss-0.3 | Vss + 7.0 | V    | P50 to P53                                                |

| "L" level maximum output current       | Iol             |         | 20        | mA   |                                                           |

| "L" level average output current       | IOLAV           |         | 4         | mA   | Average value (operating current $\times$ operating rate) |

| "L" level total maximum output current | ΣΙοι            |         | 100       | mA   |                                                           |

| "L" level total average output current | ΣΙοιαν          |         | 40        | mA   | Average value (operating current $\times$ operating rate) |

| "H" level maximum output current       | Іон             |         | -20       | mA   |                                                           |

| "H" level average output current       | Іонач           |         | -4        | mA   | Average value (operating current $\times$ operating rate) |

| "H" level total maximum output current | ΣІон            |         | -50       | mA   |                                                           |

| "H" level total average output current | ΣΙοήαν          |         | -20       | mA   | Average value (operating current × operating rate)        |

| Power consumption                      | PD              |         | 500       | mW   |                                                           |

| Operating temperature                  | TA              | -40     | +85       | °C   |                                                           |

| Storage temperature                    | Tstg            | -55     | +150      | °C   |                                                           |

$^{\ast}$  : Use AVcc and Vcc set at the same voltage.

Take care so that AV $_{CC}$  does not exceed V $_{CC}$ , such as when power is turned on.

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

| <b>.</b>                                        |        | <b>D</b> .                                                                   |                                                                                                                                                                |      | Value |      |      | = -40°C to +85°C                 |  |

|-------------------------------------------------|--------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|------|----------------------------------|--|

| Parameter                                       | Symbol | Pin name                                                                     | Condition                                                                                                                                                      | Min. | Тур.  | Max. | Unit | Remarks                          |  |

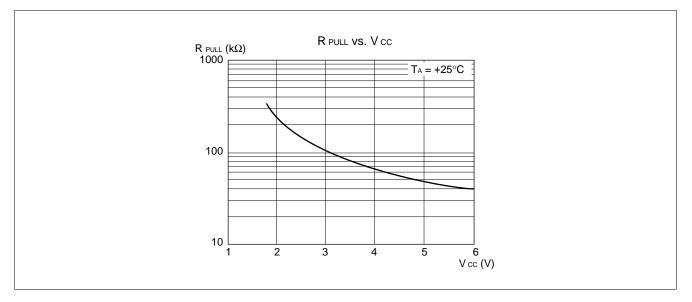

| Pull-up<br>resistance                           | Rpull  | P00 to P07, P10 to P17,<br>P30 to P37, P40 to P43,<br>P50 to P53, P72 to P74 | VI = 0.0 V                                                                                                                                                     | 25   | 50    | 100  | kΩ   | With pull-up<br>resistor         |  |

| Icc1<br>Icc2<br>Iccs1<br>Iccs2<br>Iccs2<br>IccL | Icc1   |                                                                              | $F_{CH} = 10 \text{ MHz}$<br>$V_{CC} = 5.0 \text{ V}$<br>$t_{inst}^{*2} = 0.4 \mu\text{s}$                                                                     | _    | 12    | 20   | mA   |                                  |  |

|                                                 | Icc2   |                                                                              | $F_{CH} = 10 \text{ MHz}$<br>$V_{CC} = 3.0 \text{ V}$                                                                                                          | _    | 1.0   | 2    | mA   | MB89635R/<br>636R/637R/<br>PV630 |  |

|                                                 |        |                                                                              | $t_{inst}^{*2} = 6.4 \ \mu s$                                                                                                                                  | _    | 1.5   | 2.5  | mA   | MB89P637                         |  |

|                                                 | Iccs1  | -                                                                            | $ \begin{array}{c} F_{CH} = 10 \text{ MHz} \\ \Psi \\ V_{CC} = 5.0 \text{ V} \\ t_{inst}^{*2} = 0.4  \mu s \end{array} $                                       | _    | 3     | 7    | mA   |                                  |  |

|                                                 | Iccs2  |                                                                              |                                                                                                                                                                | _    | 0.5   | 1.5  | mA   |                                  |  |

|                                                 | lcc∟   |                                                                              | FcL = 32.768 kHz,<br>Vcc = 3.0 V<br>Subclock mode                                                                                                              | _    | 50    | 100  | μΑ   | MB89635R/<br>636R/637R/<br>PV630 |  |

| current <sup>*1</sup>                           |        | Vcc                                                                          | Subcidek mode                                                                                                                                                  | —    | 500   | 700  | μA   | MB89P637                         |  |

| lc<br>Ic                                        | lcc∟s  |                                                                              | $\label{eq:Fcl} \begin{array}{l} F_{\text{CL}} = 32.768 \text{ kHz}, \\ V_{\text{CC}} = 3.0 \text{ V} \\ \textbf{Subclock sleep} \\ \textbf{mode} \end{array}$ | _    | 25    | 50   | μΑ   |                                  |  |

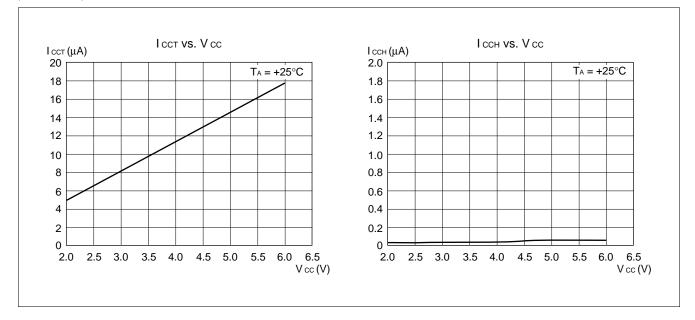

|                                                 | Ісст   |                                                                              | FcL = 32.768 kHz,<br>Vcc = 3.0 V<br>• Watch mode<br>• Main clock stop<br>mode at dual-<br>clock system                                                         | _    | 3     | 15   | μΑ   |                                  |  |

|                                                 | Іссн   |                                                                              | <ul> <li>T<sub>A</sub> = +25°C</li> <li>Subclock stop mode</li> <li>Main clock stop mode at single-clock system</li> </ul>                                     | _    | _     | 1    | μΑ   |                                  |  |

$(AVcc = Vcc = 5.0 V, AVss = Vss = 0.0 V, T_A = -40^{\circ}C to +85^{\circ}C)$

#### (4) Instruction Cycle

| Parameter                                     | Symbol   | Value (typical)              | Unit | Remarks                                                                                     |

|-----------------------------------------------|----------|------------------------------|------|---------------------------------------------------------------------------------------------|

| Instruction cycle<br>(minimum execution time) | <b>t</b> | 4/Fсн, 8/Fсн, 16/Fсн, 64/Fсн | μs   | (4/F <sub>CH</sub> ) t <sub>inst</sub> = 0.4 $\mu$ s, operating at F <sub>CH</sub> = 10 MHz |

|                                               | Tinst    | 2/FcL                        | μs   | $t_{inst} = 61.036 \ \mu s$ , operating at $F_{CL} = 32.768 \ kHz$                          |

Note: Operating at 10 MHz, the cycle varies with the set execution time.

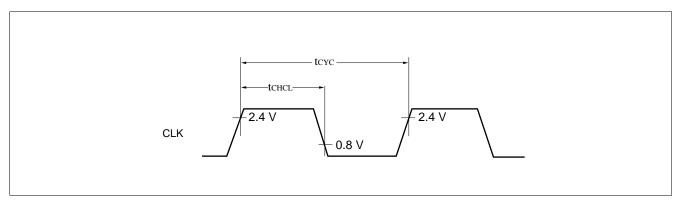

#### (5) Clock Output Timing

$(V_{CC} = 5.0 \text{ V} \pm 10\%, \text{ AV}_{SS} = \text{V}_{SS} = 0.0 \text{ V}, \text{ T}_{A} = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C})$

| Parameter                         | Symbol        | Pin  | Condition | Value                           |                         | Unit | Remarks |

|-----------------------------------|---------------|------|-----------|---------------------------------|-------------------------|------|---------|

| Farameter                         | Symbol        | name | Condition | Min.                            | Max.                    | Unit |         |

| Cycle time                        | tcyc          | CLK  |           | 1/2 tinst*                      | —                       | μs   |         |

| $CLK \uparrow \to CLK \downarrow$ | <b>t</b> CHCL | CLK  |           | 1/4 t <sub>inst</sub> * – 70 ns | 1/4 t <sub>inst</sub> * | μs   |         |

\* : For information on tinst, see "(4) Instruction Cycle".

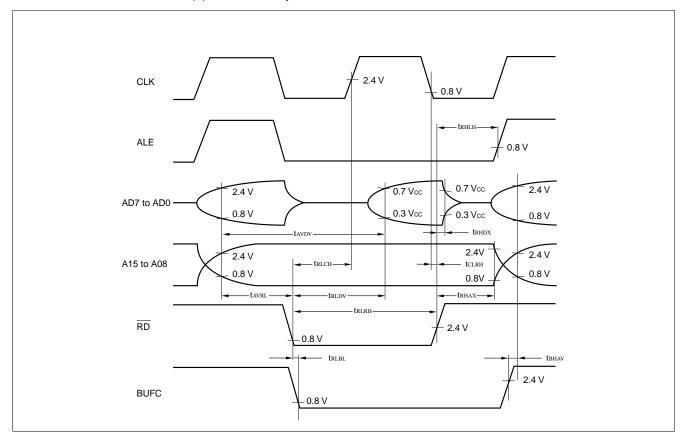

#### (6) Bus Read Timing

|                                                                                  | ( •           | CC - 0.0 V⊥I                       | J%, 10 MHZ, AVSS = VSS = 0.0 V, TA = - |                                |      |      |         |

|----------------------------------------------------------------------------------|---------------|------------------------------------|----------------------------------------|--------------------------------|------|------|---------|

| Parameter                                                                        | Symbol        | Pin name                           | Condition                              | Value                          |      | Unit | Remarks |

|                                                                                  |               |                                    |                                        | Min.                           | Max. | Unit |         |

| Valid address $\rightarrow \overline{RD} \downarrow$ time                        | <b>t</b> avrl | RD, A15 to A08,<br>AD7 to AD0      |                                        | 1/4 t <sub>inst</sub> *– 64 ns | —    | μs   |         |

| RD pulse width                                                                   | <b>t</b> rlrh | RD                                 |                                        | 1/2 t <sub>inst</sub> *– 20 ns | _    | μs   |         |

| Valid address $\rightarrow$ data read time                                       | tavdv         | AD7 to AD0,<br>A15 to A08          |                                        | 1/2 t <sub>inst</sub> *        | 200  | μs   | No wait |

| $\overline{RD} \downarrow \rightarrow data \ read \ time$                        | <b>t</b> rldv | RD, AD7 to AD0                     |                                        | 1/2 t <sub>inst</sub> *– 80 ns | 120  | μs   | No wait |

| $\overline{RD} \uparrow \rightarrow$ data hold time                              | <b>t</b> RHDX | AD7 to AD0,<br>RD                  |                                        | 0                              | _    | μs   |         |

| $\overline{RD} \uparrow \rightarrow ALE \uparrow time$                           | <b>t</b> RHLH | RD, ALE                            |                                        | 1/4 t <sub>inst</sub> *– 40 ns | _    | μs   |         |

| $\overline{RD} \uparrow \rightarrow address$ loss time                           | <b>t</b> rhax | RD, A15 to A08                     |                                        | 1/4 t <sub>inst</sub> *– 40 ns | —    | μs   |         |

| $\overline{RD} \downarrow \rightarrow CLK \uparrow time$                         | <b>t</b> rlch | RD, CLK                            |                                        | 1/4 t <sub>inst</sub> *– 40 ns | —    | μs   |         |

| $CLK \downarrow \to \overline{RD} \uparrow time$                                 | <b>t</b> clrh |                                    |                                        | 0                              | —    | ns   |         |

| $\overline{RD} \downarrow \rightarrow BUFC \downarrow time$                      | <b>t</b> rlbl | RD, BUFC                           |                                        | -5                             | _    | μs   |         |

| $\begin{array}{l} BUFC \uparrow \rightarrow valid \ address \\ time \end{array}$ | <b>t</b> bhav | A15 to A08,<br>AD7 to AD0,<br>BUFC |                                        | 5                              | _    | μs   |         |

#### (Vcc = 5.0 V±10%, 10 MHz, AVss = Vss= 0.0 V, $T_{\text{A}}$ = –40°C to +85°C)

\* : For information on tinst, see "(4) Instruction Cycle".

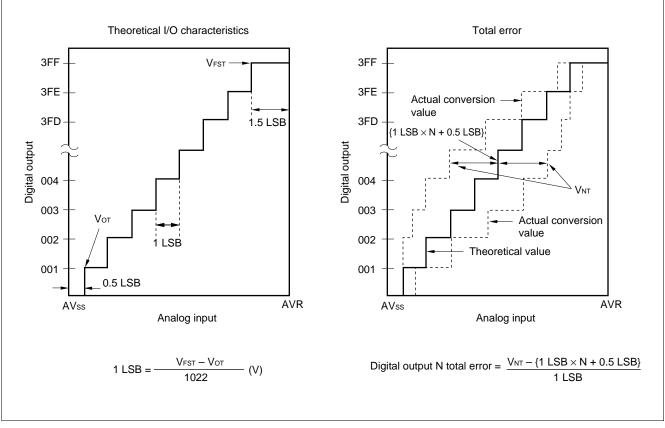

### 6. A/D Converter Glossary

Resolution

Analog changes that are identifiable with the A/D converter

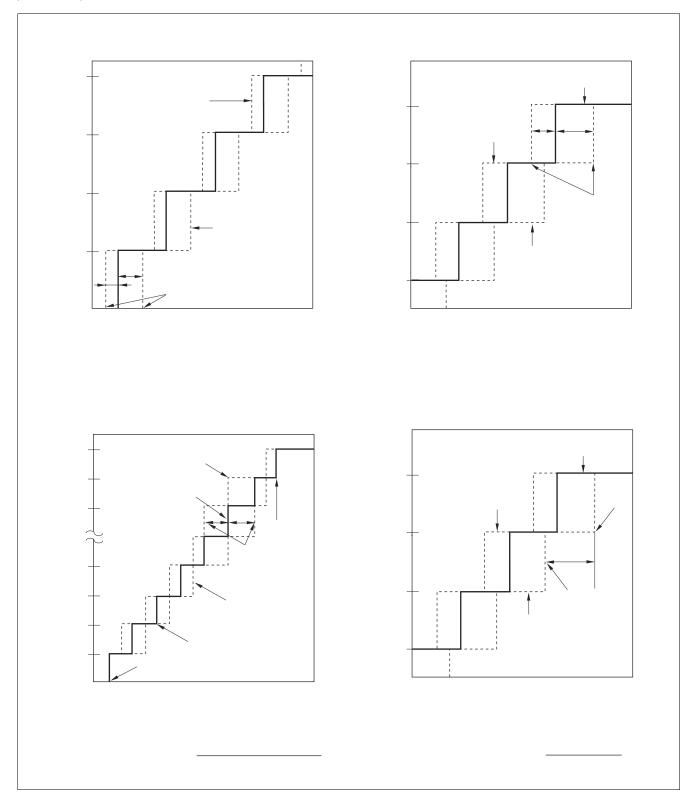

- Linearity error

The deviation of the straight line connecting the zero transition point ("00 0000 0000" ↔ "00 0000 0001") with

the full-scale transition point ("11 1111 1110" ↔ "11 1111 1111") from actual conversion characteristics

- Differential linearity error The deviation of input voltage needed to change the output code by 1 LSB from the theoretical value

- Total error (unit: LSB)

The difference between theoretical and actual conversion values caused by the zero transition error, full-scale transition error, linearity error, quantization error, and noise

(Continued)

#### (Continued)

#### (6) Pull-up Resistance

Please confirm the latest Package dimension by following URL. http://edevice.fujitsu.com/package/en-search/