Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                               |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                     |

| Core Size                  | 32-Bit Single-Core                                                   |

| Speed                      | 48MHz                                                                |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB, USB OTG              |

| Peripherals                | Brown-out Detect/Reset, DMA, LVD, POR, PWM, WDT                      |

| Number of I/O              | 66                                                                   |

| Program Memory Size        | 64KB (64K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 8K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                         |

| Data Converters            | A/D 14x16b; D/A 1x12b                                                |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 80-LQFP                                                              |

| Supplier Device Package    | 80-FQFP (12x12)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mkl25z64vlk4 |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Terminology and guidelines

| Field | Description                 | Values                                                                                                                                                       |

|-------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R     | Silicon revision            | <ul> <li>(Blank) = Main</li> <li>A = Revision after main</li> </ul>                                                                                          |

| Т     | Temperature range (°C)      | • V = -40 to 105                                                                                                                                             |

| PP    | Package identifier          | <ul> <li>FM = 32 QFN (5 mm x 5 mm)</li> <li>FT = 48 QFN (7 mm x 7 mm)</li> <li>LH = 64 LQFP (10 mm x 10 mm)</li> <li>LK = 80 LQFP (12 mm x 12 mm)</li> </ul> |

| CC    | Maximum CPU frequency (MHz) | • 4 = 48 MHz                                                                                                                                                 |

| Ν     | Packaging type              | <ul> <li>R = Tape and reel</li> <li>(Blank) = Trays</li> </ul>                                                                                               |

## 2.4 Example

This is an example part number:

MKL25Z64VLK4

## 3 Terminology and guidelines

## 3.1 Definition: Operating requirement

An *operating requirement* is a specified value or range of values for a technical characteristic that you must guarantee during operation to avoid incorrect operation and possibly decreasing the useful life of the chip.

### 3.1.1 Example

This is an example of an operating requirement, which you must meet for the accompanying operating behaviors to be guaranteed:

| Symbol          | Description               | Min. | Max. | Unit |

|-----------------|---------------------------|------|------|------|

| V <sub>DD</sub> | 1.0 V core supply voltage | 0.9  | 1.1  | V    |

## 3.7 Guidelines for ratings and operating requirements

Follow these guidelines for ratings and operating requirements:

- Never exceed any of the chip's ratings.

- During normal operation, don't exceed any of the chip's operating requirements.

- If you must exceed an operating requirement at times other than during normal operation (for example, during power sequencing), limit the duration as much as possible.

## 3.8 Definition: Typical value

A *typical value* is a specified value for a technical characteristic that:

- Lies within the range of values specified by the operating behavior

- Given the typical manufacturing process, is representative of that characteristic during operation when you meet the typical-value conditions or other specified conditions

Typical values are provided as design guidelines and are neither tested nor guaranteed.

## 3.8.1 Example 1

This is an example of an operating behavior that includes a typical value:

| Symbol          | Description                                    | Min. | Тур. | Max. | Unit |

|-----------------|------------------------------------------------|------|------|------|------|

| I <sub>WP</sub> | Digital I/O weak<br>pullup/pulldown<br>current | 10   | 70   | 130  | μΑ   |

## 3.8.2 Example 2

This is an example of a chart that shows typical values for various voltage and temperature conditions:

## 5.1 AC electrical characteristics

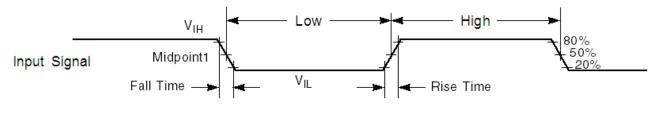

Unless otherwise specified, propagation delays are measured from the 50% to the 50% point, and rise and fall times are measured at the 20% and 80% points, as shown in the following figure.

The midpoint is  $V_{IL}$  +  $(V_{IH} - V_{IL})/2$ .

### Figure 1. Input signal measurement reference

All digital I/O switching characteristics, unless otherwise specified, assumes:

- 1. output pins

- have  $C_L$ =30pF loads,

- are slew rate disabled, and

- are normal drive strength

## 5.2 Nonswitching electrical specifications

## 5.2.1 Voltage and current operating requirements

Table 1. Voltage and current operating requirements

| Symbol                             | Description                                                  | Min.                 | Max.                 | Unit | Notes |

|------------------------------------|--------------------------------------------------------------|----------------------|----------------------|------|-------|

| V <sub>DD</sub>                    | Supply voltage                                               | 1.71                 | 3.6                  | V    |       |

| V <sub>DDA</sub>                   | Analog supply voltage                                        | 1.71                 | 3.6                  | V    |       |

| V <sub>DD</sub> – V <sub>DDA</sub> | V <sub>DD</sub> -to-V <sub>DDA</sub> differential voltage    | -0.1                 | 0.1                  | V    |       |

| $V_{SS} - V_{SSA}$                 | V <sub>SS</sub> -to-V <sub>SSA</sub> differential voltage    | -0.1                 | 0.1                  | V    |       |

| V <sub>IH</sub>                    | Input high voltage                                           |                      |                      |      |       |

|                                    | • $2.7 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}$ | $0.7 \times V_{DD}$  | —                    | V    |       |

|                                    | • $1.7 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}$ | $0.75 \times V_{DD}$ | _                    | V    |       |

| V <sub>IL</sub>                    | Input low voltage                                            |                      |                      |      |       |

|                                    | • $2.7 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}$ | _                    | $0.35 \times V_{DD}$ | V    |       |

|                                    | • $1.7 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}$ |                      | $0.3 \times V_{DD}$  | V    |       |

Table continues on the next page ...

| Symbol             | Description                                                                                                                                                                                                                                              | Min.                 | Max.    | Unit | Notes |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------|------|-------|

| V <sub>HYS</sub>   | Input hysteresis                                                                                                                                                                                                                                         | $0.06 \times V_{DD}$ | _       | V    |       |

| I <sub>ICDIO</sub> | Digital pin negative DC injection current — single pin<br>• V <sub>IN</sub> < V <sub>SS</sub> -0.3V                                                                                                                                                      | -5                   | _       | mA   | 1     |

| Iicaio             | <ul> <li>Analog<sup>2</sup> pin DC injection current — single pin</li> <li>V<sub>IN</sub> &lt; V<sub>SS</sub>-0.3V (Negative current injection)</li> <li>V<sub>IN</sub> &gt; V<sub>DD</sub>+0.3V (Positive current injection)</li> </ul>                 | -5                   | <br>+5  | mA   | 3     |

| liCcont            | <ul> <li>Contiguous pin DC injection current —regional limit, includes sum of negative injection currents or sum of positive injection currents of 16 contiguous pins</li> <li>Negative current injection</li> <li>Positive current injection</li> </ul> | -25<br>—             | <br>+25 | mA   |       |

| V <sub>RAM</sub>   | V <sub>DD</sub> voltage required to retain RAM                                                                                                                                                                                                           | 1.2                  | _       | V    |       |

### Table 1. Voltage and current operating requirements (continued)

- All digital I/O pins are internally clamped to V<sub>SS</sub> through a ESD protection diode. There is no diode connection to V<sub>DD</sub>. If V<sub>IN</sub> greater than V<sub>DIO\_MIN</sub> (=V<sub>SS</sub>-0.3V) is observed, then there is no need to provide current limiting resistors at the pads. If this limit cannot be observed then a current limiting resistor is required. The negative DC injection current limiting resistor is calculated as R=(V<sub>DIO\_MIN</sub>-V<sub>IN</sub>)/|I<sub>LC</sub>|.

- 2. Analog pins are defined as pins that do not have an associated general purpose I/O port function.

- 3. All analog pins are internally clamped to V<sub>SS</sub> and V<sub>DD</sub> through ESD protection diodes. If V<sub>IN</sub> is greater than V<sub>AIO\_MIN</sub> (=V<sub>SS</sub>-0.3V) and V<sub>IN</sub> is less than V<sub>AIO\_MAX</sub>(=V<sub>DD</sub>+0.3V) is observed, then there is no need to provide current limiting resistors at the pads. If these limits cannot be observed then a current limiting resistor is required. The negative DC injection current limiting resistor is calculated as R=(V<sub>AIO\_MIN</sub>-V<sub>IN</sub>)/II<sub>IC</sub>I. The positive injection current limiting resistor is calculated as R=(V<sub>IN</sub>-V<sub>AIO\_MAX</sub>)/II<sub>IC</sub>I. Select the larger of these two calculated resistances.

# 5.2.2 LVD and POR operating requirements

Table 2. V<sub>DD</sub> supply LVD and POR operating requirements

| Symbol             | Description                                                 | Min. | Тур. | Max. | Unit | Notes |

|--------------------|-------------------------------------------------------------|------|------|------|------|-------|

| V <sub>POR</sub>   | Falling VDD POR detect voltage                              | 0.8  | 1.1  | 1.5  | V    |       |

| V <sub>LVDH</sub>  | Falling low-voltage detect threshold — high range (LVDV=01) | 2.48 | 2.56 | 2.64 | V    |       |

|                    | Low-voltage warning thresholds — high range                 |      |      |      |      | 1     |

| $V_{LVW1H}$        | Level 1 falling (LVWV=00)                                   | 2.62 | 2.70 | 2.78 | V    |       |

| $V_{LVW2H}$        | Level 2 falling (LVWV=01)                                   | 2.72 | 2.80 | 2.88 | V    |       |

| V <sub>LVW3H</sub> | <ul> <li>Level 3 falling (LVWV=10)</li> </ul>               | 2.82 | 2.90 | 2.98 | V    |       |

| $V_{LVW4H}$        | Level 4 falling (LVWV=11)                                   | 2.92 | 3.00 | 3.08 | V    |       |

| V <sub>HYSH</sub>  | Low-voltage inhibit reset/recover hysteresis — high range   |      | ±60  |      | mV   |       |

| $V_{LVDL}$         | Falling low-voltage detect threshold — low range (LVDV=00)  | 1.54 | 1.60 | 1.66 | V    |       |

Table continues on the next page ...

#### General

| Symbol             | Description                                                 | Min. | Тур. | Max. | Unit | Notes |

|--------------------|-------------------------------------------------------------|------|------|------|------|-------|

|                    | Low-voltage warning thresholds — low range                  |      |      |      |      | 1     |

| $V_{LVW1L}$        | Level 1 falling (LVWV=00)                                   | 1.74 | 1.80 | 1.86 | V    |       |

| V <sub>LVW2L</sub> | Level 2 falling (LVWV=01)                                   | 1.84 | 1.90 | 1.96 | V    |       |

| V <sub>LVW3L</sub> | Level 3 falling (LVWV=10)                                   | 1.94 | 2.00 | 2.06 | V    |       |

| $V_{LVW4L}$        | Level 4 falling (LVWV=11)                                   | 2.04 | 2.10 | 2.16 | v    |       |

| V <sub>HYSL</sub>  | Low-voltage inhibit reset/recover hysteresis —<br>low range | -    | ±40  | -    | mV   |       |

| V <sub>BG</sub>    | Bandgap voltage reference                                   | 0.97 | 1.00 | 1.03 | V    |       |

| t <sub>LPO</sub>   | Internal low power oscillator period — factory trimmed      | 900  | 1000 | 1100 | μs   |       |

### Table 2. V<sub>DD</sub> supply LVD and POR operating requirements (continued)

1. Rising thresholds are falling threshold + hysteresis voltage

# 5.2.3 Voltage and current operating behaviors

| Symbol           | Description                                                             | Min.                  | Max.  | Unit | Notes |

|------------------|-------------------------------------------------------------------------|-----------------------|-------|------|-------|

| V <sub>OH</sub>  | Output high voltage — Normal drive pad                                  |                       |       |      | 1     |

|                  | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OH</sub> = -5 mA    | V <sub>DD</sub> – 0.5 | —     | V    |       |

|                  | • 1.71 V $\leq$ V <sub>DD</sub> $\leq$ 2.7 V, I <sub>OH</sub> = -1.5 mA | $V_{DD} - 0.5$        | —     | V    |       |

| V <sub>OH</sub>  | Output high voltage — High drive pad                                    |                       |       |      | 1     |

|                  | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OH</sub> = -18 mA   | V <sub>DD</sub> – 0.5 | —     | V    |       |

|                  | • 1.71 V $\leq$ V <sub>DD</sub> $\leq$ 2.7 V, I <sub>OH</sub> = -6 mA   | $V_{DD} - 0.5$        | —     | V    |       |

| I <sub>OHT</sub> | Output high current total for all ports                                 | _                     | 100   | mA   |       |

| V <sub>OL</sub>  | Output low voltage — Normal drive pad                                   |                       |       |      | 1     |

|                  | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OL</sub> = 5 mA     | —                     | 0.5   | V    |       |

|                  | • 1.71 V $\leq$ V <sub>DD</sub> $\leq$ 2.7 V, I <sub>OL</sub> = 1.5 mA  | —                     | 0.5   | V    |       |

| V <sub>OL</sub>  | Output low voltage — High drive pad                                     |                       |       |      | 1     |

|                  | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OL</sub> = 18 mA    | _                     | 0.5   | V    |       |

|                  | • 1.71 V $\leq$ V <sub>DD</sub> $\leq$ 2.7 V, I <sub>OL</sub> = 6 mA    | —                     | 0.5   | V    |       |

| I <sub>OLT</sub> | Output low current total for all ports                                  |                       | 100   | mA   |       |

| I <sub>IN</sub>  | Input leakage current (per pin) for full temperature range              | —                     | 1     | μA   | 2     |

| I <sub>IN</sub>  | Input leakage current (per pin) at 25 °C                                | —                     | 0.025 | μA   | 2     |

| I <sub>IN</sub>  | Input leakage current (total all pins) for full temperature range       | —                     | 65    | μΑ   | 2     |

| I <sub>OZ</sub>  | Hi-Z (off-state) leakage current (per pin)                              |                       | 1     | μA   |       |

Table 3. Voltage and current operating behaviors

Table continues on the next page...

## 5.2.5 Power consumption operating behaviors

Table 5.

Power consumption operating behaviors

| Symbol                 | Description                                                                                                                                                                                                  | Min. | Тур. | Max.     | Unit | Notes |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|----------|------|-------|

| I <sub>DDA</sub>       | Analog supply current                                                                                                                                                                                        | _    | —    | See note | mA   | 1     |

| IDD_RUNCO_<br>CM       | Run mode current in compute operation - 48<br>MHz core / 24 MHz flash/ bus disabled, LPTMR<br>running using 4MHz internal reference clock,<br>CoreMark® benchmark code executing from<br>flash<br>• at 3.0 V | _    | 6.4  | _        | mA   | 2     |

| I <sub>DD_RUNCO</sub>  | Run mode current in compute operation - 48<br>MHz core / 24 MHz flash / bus clock disabled,<br>code of while(1) loop executing from flash                                                                    |      | 4.1  | 5.2      | mA   | 3     |

|                        | • at 3.0 V                                                                                                                                                                                                   |      |      | 0.2      |      |       |

| I <sub>DD_RUN</sub>    | Run mode current - 48 MHz core / 24 MHz bus<br>and flash, all peripheral clocks disabled, code of<br>while(1) loop executing from flash                                                                      |      | 5.1  | 6.3      | mA   | 3     |

|                        | • at 3.0 V                                                                                                                                                                                                   |      | 5.1  | 0.3      | ma   |       |

| I <sub>DD_RUN</sub>    | Run mode current - 48 MHz core / 24 MHz bus<br>and flash, all peripheral clocks enabled, code of<br>while(1) loop executing from flash                                                                       |      |      |          |      | 3, 4, |

|                        | • at 3.0 V                                                                                                                                                                                                   |      |      |          |      |       |

|                        | • at 25 °C                                                                                                                                                                                                   | _    | 6.4  | 7.8      | mA   |       |

|                        | • at 125 °C                                                                                                                                                                                                  | _    | 6.8  | 8.3      | mA   |       |

| I <sub>DD_WAIT</sub>   | Wait mode current - core disabled / 48 MHz<br>system / 24 MHz bus / flash disabled (flash doze<br>enabled), all peripheral clocks disabled<br>• at 3.0 V                                                     | _    | 3.7  | 5.0      | mA   | 3     |

| I <sub>DD_WAIT</sub>   | Wait mode current - core disabled / 24 MHz<br>system / 24 MHz bus / flash disabled (flash doze<br>enabled), all peripheral clocks disabled<br>• at 3.0 V                                                     |      | 2.9  | 4.2      | mA   | 3     |

| I <sub>DD_PSTOP2</sub> | Stop mode current with partial stop 2 clocking<br>option - core and system disabled / 10.5 MHz<br>bus<br>• at 3.0 V                                                                                          | _    | 2.5  | 3.7      | mA   | 3     |

| I <sub>DD_VLPRCO</sub> | Very low power run mode current in compute<br>operation - 4 MHz core / 0.8 MHz flash / bus<br>clock disabled, code of while(1) loop executing<br>from flash<br>• at 3.0 V                                    |      | 188  | 570      | μΑ   | 5     |

| I <sub>DD_VLPR</sub>   | Very low power run mode current - 4 MHz core /<br>0.8 MHz bus and flash, all peripheral clocks<br>disabled, code of while(1) loop executing from<br>flash<br>• at 3.0 V                                      | _    | 224  | 613      | μA   | 5     |

Table continues on the next page ...

| Table 5. | Power | consumption | operating | behaviors | (continued) |

|----------|-------|-------------|-----------|-----------|-------------|

|----------|-------|-------------|-----------|-----------|-------------|

| Symbol                | Description                                                                                                                                                                | Min. | Тур. | Max. | Unit | Notes |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|-------|

| I <sub>DD_VLPR</sub>  | Very low power run mode current - 4 MHz core /<br>0.8 MHz bus and flash, all peripheral clocks<br>enabled, code of while(1) loop executing from<br>flash<br>• at 3.0 V     | _    | 300  | 745  | μA   | 5, 4  |

| I <sub>DD_VLPW</sub>  | Very low power wait mode current - core<br>disabled / 4 MHz system / 0.8 MHz bus / flash<br>disabled (flash doze enabled), all peripheral<br>clocks disabled<br>• at 3.0 V |      | 135  | 496  | μΑ   | 5     |

| I <sub>DD_STOP</sub>  | Stop mode current at 3.0 V                                                                                                                                                 |      |      |      |      |       |

|                       | at 25 °C                                                                                                                                                                   | —    | 345  | 490  |      |       |

|                       | at 50 °C                                                                                                                                                                   | —    | 357  | 827  | μA   |       |

|                       | at 70 °C                                                                                                                                                                   | —    | 392  | 869  |      |       |

|                       | at 85 °C                                                                                                                                                                   | _    | 438  | 927  |      |       |

|                       | at 105 °C                                                                                                                                                                  | _    | 551  | 1065 |      |       |

| I <sub>DD_VLPS</sub>  | Very-low-power stop mode current at 3.0 V                                                                                                                                  |      |      |      |      |       |

|                       | at 25 °C                                                                                                                                                                   | —    | 4.4  | 16   |      |       |

|                       | at 50 °C                                                                                                                                                                   | —    | 10   | 35   | μA   |       |

|                       | at 70 °C                                                                                                                                                                   | _    | 20   | 50   |      |       |

|                       | at 85 °C                                                                                                                                                                   | _    | 37   | 112  |      |       |

|                       | at 105 °C                                                                                                                                                                  | _    | 81   | 201  |      |       |

| I <sub>DD_LLS</sub>   | Low leakage stop mode current at 3.0 V                                                                                                                                     |      |      |      |      |       |

|                       | at 25 °C                                                                                                                                                                   | _    | 1.9  | 3.7  | μA   |       |

|                       | at 50 °C                                                                                                                                                                   | _    | 3.6  | 39   |      |       |

|                       | at 70 °C                                                                                                                                                                   | _    | 6.5  | 43   |      |       |

|                       | at 85 °C                                                                                                                                                                   | _    | 13   | 49   |      |       |

|                       | at 105 °C                                                                                                                                                                  | _    | 30   | 69   |      |       |

| I <sub>DD_VLLS3</sub> | Very low-leakage stop mode 3 current at 3.0 V                                                                                                                              |      |      |      |      |       |

|                       | at 25 °C                                                                                                                                                                   | —    | 1.4  | 3.2  | μA   |       |

|                       | at 50 °C                                                                                                                                                                   | —    | 2.5  | 19   |      |       |

|                       | at 70 °C                                                                                                                                                                   | _    | 5.1  | 21   |      |       |

|                       | at 85 °C                                                                                                                                                                   | _    | 9.2  | 26   |      |       |

|                       | at 105 °C                                                                                                                                                                  | _    | 21   | 38   |      |       |

| I <sub>DD_VLLS1</sub> | Very low-leakage stop mode 1 current at 3.0V                                                                                                                               |      |      |      |      |       |

|                       | at 25°C                                                                                                                                                                    | _    | 0.7  | 1.4  |      |       |

|                       | at 50°C                                                                                                                                                                    | _    | 1.3  | 13   | μA   |       |

|                       | at 70°C                                                                                                                                                                    | _    | 2.3  | 14   |      |       |

|                       | at 85°C                                                                                                                                                                    | _    | 5.1  | 17   |      |       |

|                       | at 105°C                                                                                                                                                                   | _    | 13   | 25   |      |       |

Table continues on the next page...

| Symbol                | Description                                                                | Min. | Тур.       | Max.         | Unit | Notes |

|-----------------------|----------------------------------------------------------------------------|------|------------|--------------|------|-------|

| I <sub>DD_VLLS0</sub> | Very low-leakage stop mode 0 current<br>(SMC_STOPCTRL[PORPO] = 0) at 3.0 V |      | 001        | 0.40         | nA   |       |

|                       | at 25 °C                                                                   |      | 381<br>956 | 943<br>11760 |      |       |

|                       | at 50 °C                                                                   | _    | 2370       | 13260        |      |       |

|                       | at 70 °C                                                                   | _    | 4800       | 15700        |      |       |

|                       | at 85 °C                                                                   | _    | 12410      | 23480        |      |       |

|                       | at 105 °C                                                                  |      |            |              |      |       |

| I <sub>DD_VLLS0</sub> | Very low-leakage stop mode 0 current<br>(SMC_STOPCTRL[PORPO] = 1) at 3.0 V | _    | 176        | 860          |      | 6     |

|                       | at 25 °C                                                                   | _    | 760        | 3577         | nA   |       |

|                       | at 50 °C                                                                   | _    | 2120       | 11660        |      |       |

|                       | at 70 °C                                                                   | _    | 4500       | 18450        |      |       |

|                       | at 85 °C                                                                   | _    | 12130      | 22441        |      |       |

|                       | at 105 °C                                                                  |      |            |              |      |       |

### Table 5. Power consumption operating behaviors (continued)

1. The analog supply current is the sum of the active or disabled current for each of the analog modules on the device. See each module's specification for its supply current.

- 2. MCG configured for PEE mode. CoreMark benchmark compiled using Keil 4.54 with optimization level 3, optimized for time.

- 3. MCG configured for FEI mode.

- 4. Incremental current consumption from peripheral activity is not included.

- 5. MCG configured for BLPI mode.

- 6. No brownout

### Table 6. Low power mode peripheral adders — typical value

| Symbol        | Description                                                                                                      |     | Temperature (°C) |     |     |     | Unit |    |

|---------------|------------------------------------------------------------------------------------------------------------------|-----|------------------|-----|-----|-----|------|----|

|               |                                                                                                                  | -40 | 25               | 50  | 70  | 85  | 105  |    |

| IIREFSTEN4MHz | 4 MHz internal reference clock (IRC)<br>adder. Measured by entering STOP or<br>VLPS mode with 4 MHz IRC enabled. | 56  | 56               | 56  | 56  | 56  | 56   | μA |

| IREFSTEN32KHz | 32 kHz internal reference clock (IRC)<br>adder. Measured by entering STOP<br>mode with the 32 kHz IRC enabled.   | 52  | 52               | 52  | 52  | 52  | 52   | μA |

| IEREFSTEN4MHz | External 4MHz crystal clock adder.<br>Measured by entering STOP or VLPS<br>mode with the crystal enabled.        | 206 | 228              | 237 | 245 | 251 | 258  | uA |

Table continues on the next page ...

| Symbol | Description                                                                                                                                                                                                             | Temperature (°C) |     |     |     |     | Unit |    |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|-----|-----|-----|------|----|

|        |                                                                                                                                                                                                                         | -40              | 25  | 50  | 70  | 85  | 105  |    |

|        | ADC peripheral adder combining the<br>measured values at VDD and VDDA by<br>placing the device in STOP or VLPS<br>mode. ADC is configured for low power<br>mode using the internal clock and<br>continuous conversions. | 366              | 366 | 366 | 366 | 366 | 366  | μΑ |

Table 6. Low power mode peripheral adders — typical value (continued)

### 5.2.5.1 Diagram: Typical IDD\_RUN operating behavior

The following data was measured under these conditions:

- MCG in FBE for run mode, and BLPE for VLPR mode

- USB regulator disabled

- No GPIOs toggled

- Code execution from flash with cache enabled

- For the ALLOFF curve, all peripheral clocks are disabled except FTFA

- 2.  $V_{DD} = 3.3 \text{ V}, T_A = 25 \text{ °C}, f_{OSC} = 8 \text{ MHz}$  (crystal),  $f_{SYS} = 48 \text{ MHz}, f_{BUS} = 48 \text{ MHz}$

- 3. Specified according to Annex D of IEC Standard 61967-2, Measurement of Radiated Emissions TEM Cell and Wideband TEM Cell Method

### 5.2.7 Designing with radiated emissions in mind

To find application notes that provide guidance on designing your system to minimize interference from radiated emissions:

- 1. Go to www.freescale.com.

- 2. Perform a keyword search for "EMC design."

### 5.2.8 Capacitance attributes

### Table 8. Capacitance attributes

| Symbol            | Description                     | Min. | Max. | Unit |

|-------------------|---------------------------------|------|------|------|

| C <sub>IN_A</sub> | Input capacitance: analog pins  | —    | 7    | pF   |

| C <sub>IN_D</sub> | Input capacitance: digital pins | _    | 7    | pF   |

## 5.3 Switching specifications

### 5.3.1 Device clock specifications

| Symbol               | Description                                            | Min.           | Max. | Unit | Notes |

|----------------------|--------------------------------------------------------|----------------|------|------|-------|

|                      | Normal run m                                           | ode            | 1    |      |       |

| f <sub>SYS</sub>     | System and core clock                                  | —              | 48   | MHz  |       |

| f <sub>BUS</sub>     | Bus clock                                              | _              | 24   | MHz  |       |

| f <sub>FLASH</sub>   | Flash clock                                            | _              | 24   | MHz  |       |

| f <sub>SYS_USB</sub> | System and core clock when Full Speed USB in operation | 20             | -    | MHz  |       |

| f <sub>LPTMR</sub>   | LPTMR clock                                            | _              | 24   | MHz  |       |

|                      | VLPR mode                                              | , <sup>1</sup> | 1    | •    |       |

| f <sub>SYS</sub>     | System and core clock                                  | _              | 4    | MHz  |       |

| f <sub>BUS</sub>     | Bus clock                                              | _              | 1    | MHz  |       |

| f <sub>FLASH</sub>   | Flash clock                                            | _              | 1    | MHz  |       |

| f <sub>LPTMR</sub>   | LPTMR clock                                            | _              | 24   | MHz  |       |

| f <sub>ERCLK</sub>   | External reference clock                               | _              | 16   | MHz  |       |

| $f_{LPTMR_pin}$      | LPTMR clock                                            | _              | 24   | MHz  |       |

Table continues on the next page ...

#### Peripheral operating requirements and behaviors

| Symbol | Description                                     | Min. | Max. | Unit |

|--------|-------------------------------------------------|------|------|------|

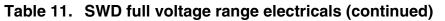

| J1     | SWD_CLK frequency of operation                  |      |      |      |

|        | Serial wire debug                               | 0    | 25   | MHz  |

| J2     | SWD_CLK cycle period                            | 1/J1 |      | ns   |

| J3     | SWD_CLK clock pulse width                       |      |      |      |

|        | Serial wire debug                               | 20   | _    | ns   |

| J4     | SWD_CLK rise and fall times                     | _    | 3    | ns   |

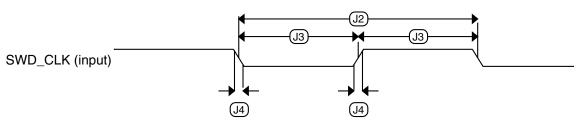

| J9     | SWD_DIO input data setup time to SWD_CLK rise   | 10   | _    | ns   |

| J10    | SWD_DIO input data hold time after SWD_CLK rise | 0    | —    | ns   |

| J11    | SWD_CLK high to SWD_DIO data valid              | _    | 32   | ns   |

| J12    | SWD_CLK high to SWD_DIO high-Z                  | 5    |      | ns   |

Figure 4. Serial wire clock input timing

## 6.2 System modules

There are no specifications necessary for the device's system modules.

## 6.3 Clock modules

## 6.3.1 MCG specifications

| Symbol                  | Description                                                                                                      |                                                                                              | Min.                            | Тур.      | Max.    | Unit                  | Notes |

|-------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------|-----------|---------|-----------------------|-------|

| f <sub>ints_ft</sub>    |                                                                                                                  | frequency (slow clock) —<br>nominal V <sub>DD</sub> and 25 °C                                | —                               | 32.768    | —       | kHz                   |       |

| f <sub>ints_t</sub>     | Internal reference<br>trimmed                                                                                    | frequency (slow clock) — user                                                                | 31.25                           |           | 39.0625 | kHz                   |       |

| $\Delta_{fdco\_res\_t}$ |                                                                                                                  | ned average DCO output<br>voltage and temperature —<br>d SCFTRIM                             | _                               | ± 0.3     | ± 0.6   | %f <sub>dco</sub>     | 1     |

| $\Delta f_{dco\_t}$     |                                                                                                                  | rimmed average DCO output tage and temperature                                               |                                 | +0.5/-0.7 | ± 3     | %f <sub>dco</sub>     | 1, 2  |

| $\Delta f_{dco_t}$      |                                                                                                                  | •                                                                                            |                                 | ± 0.4     | ± 1.5   | %f <sub>dco</sub>     | 1, 2  |

| f <sub>intf_ft</sub>    | Internal reference frequency (fast clock) — factory trimmed at nominal $V_{\text{DD}}$ and 25 $^{\circ}\text{C}$ |                                                                                              | —                               | 4         | —       | MHz                   |       |

| $\Delta f_{intf_{ft}}$  | (fast clock) over te                                                                                             | on of internal reference clock<br>mperature and voltage<br>nominal V <sub>DD</sub> and 25 °C | —                               | +1/-2     | ± 3     | %f <sub>intf_ft</sub> | 2     |

| f <sub>intf_t</sub>     | Internal reference<br>trimmed at nomina                                                                          | frequency (fast clock) — user<br>Il V <sub>DD</sub> and 25 °C                                | 3                               | _         | 5       | MHz                   |       |

| f <sub>loc_low</sub>    | Loss of external cl<br>RANGE = 00                                                                                | ock minimum frequency —                                                                      | (3/5) x<br>f <sub>ints_t</sub>  | _         | —       | kHz                   |       |

| f <sub>loc_high</sub>   | Loss of external cl<br>RANGE = 01, 10,                                                                           | ock minimum frequency —<br>or 11                                                             | (16/5) x<br>f <sub>ints_t</sub> |           | —       | kHz                   |       |

|                         |                                                                                                                  | FI                                                                                           | L                               | •         |         |                       |       |

| f <sub>fll_ref</sub>    | FLL reference freq                                                                                               | uency range                                                                                  | 31.25                           | _         | 39.0625 | kHz                   |       |

| f <sub>dco</sub>        | DCO output<br>frequency range                                                                                    | Low range (DRS = 00)<br>640 × f <sub>fll_ref</sub>                                           | 20                              | 20.97     | 25      | MHz                   | 3, 4  |

|                         |                                                                                                                  | Mid range (DRS = 01)<br>1280 × f <sub>fll_ref</sub>                                          | 40                              | 41.94     | 48      | MHz                   |       |

### Table 12. MCG specifications

Table continues on the next page...

## 6.3.2 Oscillator electrical specifications

This section provides the electrical characteristics of the module.

### 6.3.2.1 Oscillator DC electrical specifications Table 13. Oscillator DC electrical specifications

| Symbol          | Description                                                | Min. | Тур. | Max. | Unit | Notes |

|-----------------|------------------------------------------------------------|------|------|------|------|-------|

| V <sub>DD</sub> | Supply voltage                                             | 1.71 | —    | 3.6  | V    |       |

| IDDOSC          | Supply current — low-power mode (HGO=0)                    |      |      |      |      | 1     |

|                 | • 32 kHz                                                   | _    | 500  | _    | nA   |       |

|                 | • 4 MHz                                                    | _    | 200  | _    | μA   |       |

|                 | • 8 MHz (RANGE=01)                                         | _    | 300  | _    | μA   |       |

|                 | • 16 MHz                                                   | _    | 950  | _    | μA   |       |

|                 | • 24 MHz                                                   | _    | 1.2  | _    | mA   |       |

|                 | • 32 MHz                                                   | _    | 1.5  | _    | mA   |       |

| IDDOSC          | Supply current — high gain mode (HGO=1)                    |      |      |      |      | 1     |

|                 | • 32 kHz                                                   | _    | 25   | _    | μA   |       |

|                 | • 4 MHz                                                    | _    | 400  | _    | μA   |       |

|                 | • 8 MHz (RANGE=01)                                         | _    | 500  | _    | μA   |       |

|                 | • 16 MHz                                                   | _    | 2.5  | _    | mA   |       |

|                 | • 24 MHz                                                   | _    | 3    | _    | mA   |       |

|                 | • 32 MHz                                                   | _    | 4    | _    | mA   |       |

| C <sub>x</sub>  | EXTAL load capacitance                                     |      | _    |      |      | 2, 3  |

| Cy              | XTAL load capacitance                                      | _    | —    | _    |      | 2, 3  |

| R <sub>F</sub>  | Feedback resistor — low-frequency, low-power mode (HGO=0)  | _    | _    | _    | MΩ   | 2, 4  |

|                 | Feedback resistor — low-frequency, high-gain mode (HGO=1)  | _    | 10   | _    | MΩ   |       |

|                 | Feedback resistor — high-frequency, low-power mode (HGO=0) |      | _    |      | MΩ   |       |

|                 | Feedback resistor — high-frequency, high-gain mode (HGO=1) |      | 1    |      | MΩ   |       |

Table continues on the next page ...

KL25 Sub-Family Data Sheet Data Sheet, Rev. 3, 9/19/2012.

| Symbol                       | Description                                                                                            | Min. | Тур.            | Max. | Unit | Notes |

|------------------------------|--------------------------------------------------------------------------------------------------------|------|-----------------|------|------|-------|

| R <sub>S</sub>               | Series resistor — low-frequency, low-power mode (HGO=0)                                                | —    | _               | _    | kΩ   |       |

|                              | Series resistor — low-frequency, high-gain mode (HGO=1)                                                | —    | 200             | _    | kΩ   |       |

|                              | Series resistor — high-frequency, low-power mode (HGO=0)                                               | —    |                 |      | kΩ   |       |

|                              | Series resistor — high-frequency, high-gain<br>mode (HGO=1)                                            |      |                 |      |      |       |

|                              |                                                                                                        | —    | 0               | _    | kΩ   |       |

| V <sub>pp</sub> <sup>5</sup> | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — low-frequency, low-power mode<br>(HGO=0)  | _    | 0.6             | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — low-frequency, high-gain mode<br>(HGO=1)  | _    | V <sub>DD</sub> | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — high-frequency, low-power mode<br>(HGO=0) | _    | 0.6             | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — high-frequency, high-gain mode<br>(HGO=1) |      | V <sub>DD</sub> | _    | V    |       |

### Table 13. Oscillator DC electrical specifications (continued)

- 1.  $V_{DD}$ =3.3 V, Temperature =25 °C

- 2. See crystal or resonator manufacturer's recommendation

- 3. C<sub>x</sub>,C<sub>y</sub> can be provided by using the integrated capacitors when the low frequency oscillator (RANGE = 00) is used. For all other cases external capacitors must be used.

- 4. When low power mode is selected,  $R_F$  is integrated and must not be attached externally.

- 5. The EXTAL and XTAL pins should only be connected to required oscillator components and must not be connected to any other devices.

### 6.3.2.2 Oscillator frequency specifications Table 14. Oscillator frequency specifications

| Symbol                | Description                                                                                           | Min. | Тур. | Max. | Unit | Notes |

|-----------------------|-------------------------------------------------------------------------------------------------------|------|------|------|------|-------|

| f <sub>osc_lo</sub>   | Oscillator crystal or resonator frequency — low frequency mode (MCG_C2[RANGE]=00)                     | 32   | _    | 40   | kHz  |       |

| f <sub>osc_hi_1</sub> | Oscillator crystal or resonator frequency — high<br>frequency mode (low range)<br>(MCG_C2[RANGE]=01)  | 3    | _    | 8    | MHz  |       |

| f <sub>osc_hi_2</sub> | Oscillator crystal or resonator frequency — high<br>frequency mode (high range)<br>(MCG_C2[RANGE]=1x) | 8    | _    | 32   | MHz  |       |

| f <sub>ec_extal</sub> | Input clock frequency (external clock mode)                                                           | —    | —    | 48   | MHz  | 1, 2  |

| t <sub>dc_extal</sub> | Input clock duty cycle (external clock mode)                                                          | 40   | 50   | 60   | %    |       |

Table continues on the next page...

| Symbol              | Description            | Conditions <sup>1</sup>                         | Min. | Typ. <sup>2</sup>                 | Max. | Unit  | Notes                                                                                                                |

|---------------------|------------------------|-------------------------------------------------|------|-----------------------------------|------|-------|----------------------------------------------------------------------------------------------------------------------|

| E <sub>IL</sub>     | Input leakage<br>error |                                                 |      | I <sub>In</sub> × R <sub>AS</sub> |      | mV    | I <sub>In</sub> =<br>leakage<br>current<br>(refer to<br>the MCU's<br>voltage<br>and current<br>operating<br>ratings) |

|                     | Temp sensor<br>slope   | Across the full temperature range of the device | _    | 1.715                             | _    | mV/°C |                                                                                                                      |

| V <sub>TEMP25</sub> | Temp sensor<br>voltage | 25 °C                                           | —    | 719                               | —    | mV    |                                                                                                                      |

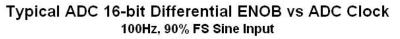

### Table 20. 16-bit ADC characteristics ( $V_{REFH} = V_{DDA}$ , $V_{REFL} = V_{SSA}$ ) (continued)

- 1. All accuracy numbers assume the ADC is calibrated with  $V_{\mathsf{REFH}}$  =  $V_{\mathsf{DDA}}$

- Typical values assume V<sub>DDA</sub> = 3.0 V, Temp = 25°C, f<sub>ADCK</sub> = 2.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

- The ADC supply current depends on the ADC conversion clock speed, conversion rate and the ADLPC bit (low power). For lowest power operation the ADLPC bit must be set, the HSC bit must be clear with 1 MHz ADC conversion clock speed.

- 4. 1 LSB =  $(V_{REFH} V_{REFL})/2^N$

- 5. ADC conversion clock < 16 MHz, Max hardware averaging (AVGE = %1, AVGS = %11)

- 6. Input data is 100 Hz sine wave. ADC conversion clock < 12 MHz.

- 7. Input data is 1 kHz sine wave. ADC conversion clock < 12 MHz.

#### Peripheral operating requirements and behaviors

| Symbol | Description                                      | Min. | Тур. | Max. | Unit | Notes |

|--------|--------------------------------------------------|------|------|------|------|-------|

| SR     | Slew rate -80h→ F7Fh→ 80h                        |      |      |      | V/µs |       |

|        | <ul> <li>High power (SP<sub>HP</sub>)</li> </ul> | 1.2  | 1.7  | —    |      |       |

|        | <ul> <li>Low power (SP<sub>LP</sub>)</li> </ul>  | 0.05 | 0.12 | —    |      |       |

| BW     | 3dB bandwidth                                    |      |      |      | kHz  |       |

|        | <ul> <li>High power (SP<sub>HP</sub>)</li> </ul> | 550  | —    | —    |      |       |

|        | • Low power (SP <sub>LP</sub> )                  | 40   | —    | _    |      |       |

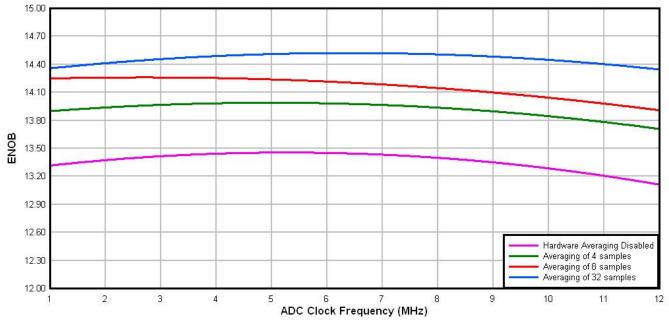

Table 23. 12-bit DAC operating behaviors (continued)

- 1. Settling within ±1 LSB

- 2. The INL is measured for 0 + 100 mV to  $V_{DACR}$  –100 mV

- 3. The DNL is measured for 0 + 100 mV to  $V_{DACR}$  –100 mV

- 4. The DNL is measured for 0 + 100 mV to  $V_{DACR}$  –100 mV with  $V_{DDA}$  > 2.4 V

- 5. Calculated by a best fit curve from  $V_{SS}$  + 100 mV to  $V_{DACR}$  100 mV 6.  $V_{DDA}$  = 3.0 V, reference select set for  $V_{DDA}$  (DACx\_CO:DACRFS = 1), high power mode (DACx\_CO:LPEN = 0), DAC set to 0x800, temperature range is across the full range of the device

### Figure 11. Typical INL error vs. digital code

#### Peripheral operating requirements and behaviors

1. If configured as an output.

2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

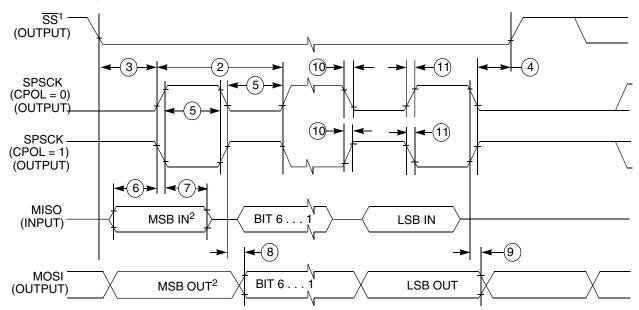

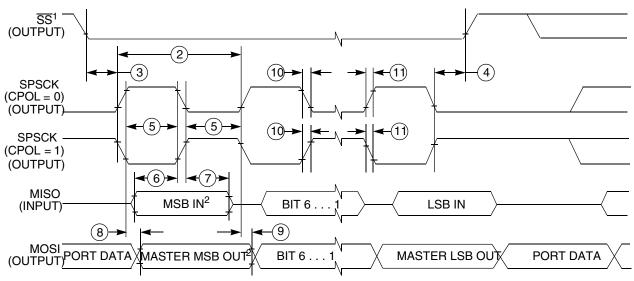

### Figure 13. SPI master mode timing (CPHA = 0)

1.If configured as output

2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

### Figure 14. SPI master mode timing (CPHA = 1)

| Num. | Symbol              | Description                    | Min.                     | Max.                   | Unit                | Note |

|------|---------------------|--------------------------------|--------------------------|------------------------|---------------------|------|

| 1    | f <sub>op</sub>     | Frequency of operation         | 0                        | f <sub>periph</sub> /4 | Hz                  | 1    |

| 2    | t <sub>SPSCK</sub>  | SPSCK period                   | 4 x t <sub>periph</sub>  | _                      | ns                  | 2    |

| 3    | t <sub>Lead</sub>   | Enable lead time               | 1                        | _                      | t <sub>periph</sub> | —    |

| 4    | t <sub>Lag</sub>    | Enable lag time                | 1                        | _                      | t <sub>periph</sub> | —    |

| 5    | t <sub>WSPSCK</sub> | Clock (SPSCK) high or low time | t <sub>periph</sub> - 30 |                        | ns                  | —    |

Table continues on the next page...

## 6.9 Human-machine interfaces (HMI)

### 6.9.1 TSI electrical specifications

### Table 29. TSI electrical specifications

| Symbol    | Description                                                                        | Min. | Туре | Max  | Unit |

|-----------|------------------------------------------------------------------------------------|------|------|------|------|

| TSI_RUNF  | Fixed power consumption in run mode                                                | —    | 100  | —    | μA   |

| TSI_RUNV  | Variable power consumption in run mode (depends on oscillator's current selection) | 1.0  |      | 128  | μA   |

| TSI_EN    | Power consumption in enable mode                                                   | _    | 100  |      | μA   |

| TSI_DIS   | Power consumption in disable mode                                                  |      | 1.2  |      | μA   |

| TSI_TEN   | TSI analog enable time                                                             | _    | 66   |      | μs   |

| TSI_CREF  | TSI reference capacitor                                                            | _    | 1.0  |      | pF   |

| TSI_DVOLT | Voltage variation of VP & VM around nominal<br>values                              | 0.19 | —    | 1.03 | V    |

## 7 Dimensions

## 7.1 Obtaining package dimensions

Package dimensions are provided in package drawings.

To find a package drawing, go to www.freescale.com and perform a keyword search for the drawing's document number:

| If you want the drawing for this package | Then use this document number |  |  |  |  |

|------------------------------------------|-------------------------------|--|--|--|--|

| 32-pin QFN                               | 98ASA00473D                   |  |  |  |  |

| 48-pin QFN                               | 98ASA00466D                   |  |  |  |  |

| 64-pin LQFP                              | 98ASS23234W                   |  |  |  |  |

| 80-pin LQFP                              | 98ASS23174W                   |  |  |  |  |

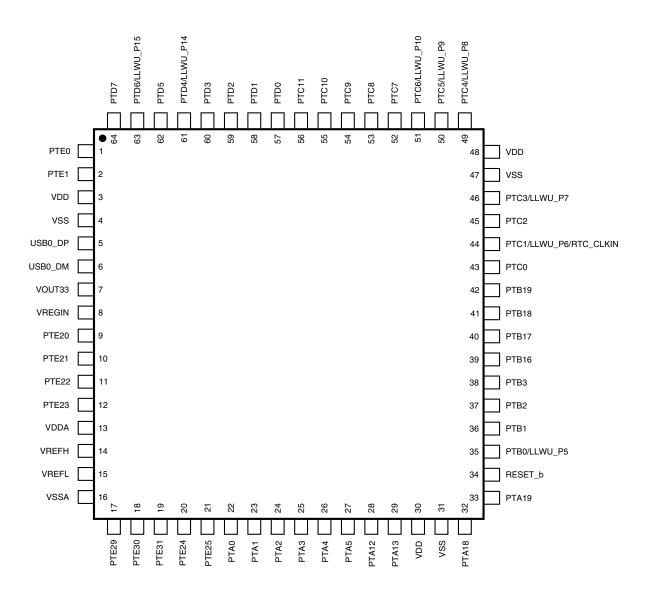

## 8 Pinout

#### Pinout

## 8.1 KL25 Signal Multiplexing and Pin Assignments

The following table shows the signals available on each pin and the locations of these pins on the devices supported by this document. The Port Control Module is responsible for selecting which ALT functionality is available on each pin.

| 80<br>LQFP | 64<br>LQFP | 48<br>QFN | 32<br>QFN | Pin Name | Default                             | ALT0                                | ALT1  | ALT2      | ALT3     | ALT4       | ALT5      | ALT6     | ALT7    |

|------------|------------|-----------|-----------|----------|-------------------------------------|-------------------------------------|-------|-----------|----------|------------|-----------|----------|---------|

| 1          | 1          | -         | 1         | PTE0     | DISABLED                            |                                     | PTE0  |           | UART1_TX | RTC_CLKOUT | CMP0_OUT  | I2C1_SDA |         |

| 2          | 2          | -         | -         | PTE1     | DISABLED                            |                                     | PTE1  | SPI1_MOSI | UART1_RX |            | SPI1_MISO | I2C1_SCL |         |

| 3          | -          | -         | _         | PTE2     | DISABLED                            |                                     | PTE2  | SPI1_SCK  |          |            |           |          |         |

| 4          | -          | -         | -         | PTE3     | DISABLED                            |                                     | PTE3  | SPI1_MISO |          |            | SPI1_MOSI |          |         |

| 5          | _          | -         | -         | PTE4     | DISABLED                            |                                     | PTE4  | SPI1_PCS0 |          |            |           |          |         |

| 6          | _          | -         | _         | PTE5     | DISABLED                            |                                     | PTE5  |           |          |            |           |          |         |

| 7          | 3          | 1         | -         | VDD      | VDD                                 | VDD                                 |       |           |          |            |           |          |         |

| 8          | 4          | 2         | 2         | VSS      | VSS                                 | VSS                                 |       |           |          |            |           |          |         |

| 9          | 5          | 3         | 3         | USB0_DP  | USB0_DP                             | USB0_DP                             |       |           |          |            |           |          |         |

| 10         | 6          | 4         | 4         | USB0_DM  | USB0_DM                             | USB0_DM                             |       |           |          |            |           |          |         |

| 11         | 7          | 5         | 5         | VOUT33   | VOUT33                              | VOUT33                              |       |           |          |            |           |          |         |

| 12         | 8          | 6         | 6         | VREGIN   | VREGIN                              | VREGIN                              |       |           |          |            |           |          |         |

| 13         | 9          | 7         | -         | PTE20    | ADC0_DP0/<br>ADC0_SE0               | ADC0_DP0/<br>ADC0_SE0               | PTE20 |           | TPM1_CH0 | UART0_TX   |           |          |         |

| 14         | 10         | 8         | -         | PTE21    | ADC0_DM0/<br>ADC0_SE4a              | ADC0_DM0/<br>ADC0_SE4a              | PTE21 |           | TPM1_CH1 | UART0_RX   |           |          |         |

| 15         | 11         | -         | -         | PTE22    | ADC0_DP3/<br>ADC0_SE3               | ADC0_DP3/<br>ADC0_SE3               | PTE22 |           | TPM2_CH0 | UART2_TX   |           |          |         |

| 16         | 12         | -         | -         | PTE23    | ADC0_DM3/<br>ADC0_SE7a              | ADC0_DM3/<br>ADC0_SE7a              | PTE23 |           | TPM2_CH1 | UART2_RX   |           |          |         |

| 17         | 13         | 9         | 7         | VDDA     | VDDA                                | VDDA                                |       |           |          |            |           |          |         |

| 18         | 14         | 10        | _         | VREFH    | VREFH                               | VREFH                               |       |           |          |            |           |          |         |

| 19         | 15         | 11        | _         | VREFL    | VREFL                               | VREFL                               |       |           |          |            |           |          |         |

| 20         | 16         | 12        | 8         | VSSA     | VSSA                                | VSSA                                |       |           |          |            |           |          |         |

| 21         | 17         | 13        | -         | PTE29    | CMP0_IN5/<br>ADC0_SE4b              | CMP0_IN5/<br>ADC0_SE4b              | PTE29 |           | TPM0_CH2 | TPM_CLKIN0 |           |          |         |

| 22         | 18         | 14        | 9         | PTE30    | DAC0_OUT/<br>ADC0_SE23/<br>CMP0_IN4 | DAC0_OUT/<br>ADC0_SE23/<br>CMP0_IN4 | PTE30 |           | TPM0_CH3 | TPM_CLKIN1 |           |          |         |

| 23         | 19         | -         | _         | PTE31    | DISABLED                            |                                     | PTE31 |           | TPM0_CH4 |            |           |          |         |

| 24         | 20         | 15        | _         | PTE24    | DISABLED                            |                                     | PTE24 |           | TPM0_CH0 |            | I2C0_SCL  |          |         |

| 25         | 21         | 16        | _         | PTE25    | DISABLED                            |                                     | PTE25 |           | TPM0_CH1 |            | I2C0_SDA  |          |         |

| 26         | 22         | 17        | 10        | PTA0     | SWD_CLK                             | TSI0_CH1                            | PTA0  |           | TPM0_CH5 |            |           |          | SWD_CLK |

| 27         | 23         | 18        | 11        | PTA1     | DISABLED                            | TSI0_CH2                            | PTA1  | UART0_RX  | TPM2_CH0 |            |           |          |         |

| 28         | 24         | 19        | 12        | PTA2     | DISABLED                            | TSI0_CH3                            | PTA2  | UART0_TX  | TPM2_CH1 |            |           |          |         |

| 29         | 25         | 20        | 13        | PTA3     | SWD_DIO                             | TSI0_CH4                            | PTA3  | I2C1_SCL  | TPM0_CH0 |            |           |          | SWD_DIO |

| 30         | 26         | 21        | 14        | PTA4     | NMI_b                               | TSI0_CH5                            | PTA4  | I2C1_SDA  | TPM0_CH1 |            |           |          | NMI_b   |

| 31         | 27         | -         | -         | PTA5     | DISABLED                            |                                     | PTA5  | USB_CLKIN | TPM0_CH2 |            |           |          |         |

Figure 18. KL25 64-pin LQFP pinout diagram