Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 60                                                                          |

| Program Memory Size        | 128KB (64K x 16)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 3.5K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 47x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-VFQFN Exposed Pad                                                        |

| Supplier Device Package    | 64-VQFN (9x9)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf67k40-e-mr |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 6.0 POWER-SAVING OPERATION MODES

The purpose of the Power-Down modes is to reduce power consumption. There are three Power-Down modes:

- Doze mode

- Sleep mode

- Idle mode

### 6.1 Doze Mode

Doze mode allows for power saving by reducing CPU operation and program memory (PFM) access, without affecting peripheral operation. Doze mode differs from Sleep mode because the bandgap and system oscillators continue to operate, while only the CPU and PFM are affected. The reduced execution saves power by eliminating unnecessary operations within the CPU and memory.

When the Doze Enable (DOZEN) bit is set (DOZEN = 1), the CPU executes only one instruction cycle out of every N cycles as defined by the DOZE<2:0> bits of the CPUDOZE register. For example, if DOZE<2:0> = 001, the instruction cycle ratio is 1:4. The CPU and memory execute for one instruction cycle and then lay idle for three instruction cycles. During the unused cycles, the peripherals continue to operate at the system clock speed.

### 6.1.1 DOZE OPERATION

The Doze operation is illustrated in Figure 6-1. For this example:

- Doze enable (DOZEN) bit set (DOZEN = 1)

- DOZE<2:0> = 001 (1:4) ratio

- Recover-on-Interrupt (ROI) bit set (ROI = 1)

As with normal operation, the PFM fetches for the next instruction cycle. The Q-clocks to the peripherals continue throughout.

## TABLE 10-5: REGISTER FILE SUMMARY FOR PIC18(L)F6XK40 DEVICES (CONTINUED)

| Address            | Name     | Bit 7         | Bit 6 | Bit 5 | Bit 4         | Bit 3  | Bit 2    | Bit 1 | Bit 0     | <u>Value on</u><br>POR, BOR |

|--------------------|----------|---------------|-------|-------|---------------|--------|----------|-------|-----------|-----------------------------|

| DF9h               | T5CKIPPS | -             | -     |       |               | T5CKIF | PPS<5:0> |       |           | 011001                      |

| DF8h               | T3GPPS   | _             | _     |       |               | T3GP   | PS<5:0>  |       |           | 000101                      |

| DF7h               | T3CKIPPS | _             | _     |       |               | T3CKI  | PPS<5:0> |       |           | 001101                      |

| DF6h               | T1GPPS   | _             | _     |       |               | T1GP   | PS<5:0>  |       |           | 001101                      |

| DF5h               | T1CKIPPS | _             | _     |       | T1CKIPPS<5:0> |        |          |       | 010000    |                             |

| DF4h               | TOCKIPPS | _             | _     |       | T0CKIPPS<5:0> |        |          |       | 000100    |                             |

| DF3h               | INT3PPS  | _             |       |       | INT3PPS<5:0>  |        |          |       | 000100    |                             |

| DF2h               | INT2PPS  | _             | _     |       |               | INT2P  | PS<5:0>  |       |           | 001010                      |

| DF1h               | INT1PPS  | _             | _     |       |               | INT1P  | PS<5:0>  |       |           | 001001                      |

| DF0h               | INT0PPS  | _             | _     |       | INT0PPS<5:0>  |        |          |       | 001000    |                             |

| DE0h               | PPSLOCK  | _             | _     | —     | —             | —      | —        | —     | PPSLOCKED | 0                           |

| DD0h<br>to<br>E7Eh | —        | Unimplemented |       |       |               |        | _        |       |           |                             |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition

Note 1: Not available on LF devices.

#### 14.4 INTCON Registers

The INTCON registers are readable and writable registers, which contain various enable and priority bits.

#### 14.5 PIR Registers

The PIR registers contain the individual flag bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are 10 Peripheral Interrupt Request Flag registers (PIR0, PIR1, PIR2, PIR3, PIR4, PIR5, PIR6, PIR7, PIR8, and PIR9).

### 14.6 PIE Registers

The PIE registers contain the individual enable bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are 10 Peripheral Interrupt Enable registers (PIE0, PIE1, PIE2, PIE3, PIE4, PIE5, PIE6, PIE7, PIE8 and PIE9). When IPEN = 0, the PEIE/GIEL bit must be set to enable any of these peripheral interrupts.

#### 14.7 IPR Registers

The IPR registers contain the individual priority bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are 10 Peripheral Interrupt Priority registers (IPR0, IPR1, IPR2, IPR3, IPR4 and IPR5, IPR6, IPR7, IPR8 and IPR9). Using the priority bits requires that the Interrupt Priority Enable (IPEN) bit be set.

| U-0 U-0                                                   | R/W-0/0               | R/W-0/0                   | R/W-0/0               | R/W-0/0               | R/W-0/0               | R/W-0/0               |

|-----------------------------------------------------------|-----------------------|---------------------------|-----------------------|-----------------------|-----------------------|-----------------------|

|                                                           | TMR0IE <sup>(1)</sup> | IOCIE <sup>(1)</sup>      | INT3IE <sup>(1)</sup> | INT2IE <sup>(1)</sup> | INT1IE <sup>(1)</sup> | INT0IE <sup>(1)</sup> |

| bit 7                                                     |                       |                           | •                     |                       |                       | bit                   |

|                                                           |                       |                           |                       |                       |                       |                       |

| Legend: IE                                                |                       |                           |                       |                       |                       |                       |

| R = Readable bit                                          | W = Writable          | bit                       | U = Unimpler          | mented bit, read      | d as '0'              |                       |

| -n = Value at POR                                         | '1' = Bit is set      |                           | '0' = Bit is cle      | ared                  | x = Bit is unkr       | nown                  |

|                                                           |                       |                           |                       |                       |                       |                       |

| bit 7-6 Unimplemen                                        | ted: Read as 'd       | )'                        |                       |                       |                       |                       |

| bit 5 TMR0IE: Tim                                         | er0 Interrupt Er      | nable bit <sup>(1)</sup>  |                       |                       |                       |                       |

| 1 = Enabled                                               |                       |                           |                       |                       |                       |                       |

| 0 = Disabled                                              |                       |                           |                       |                       |                       |                       |

|                                                           | upt-on-Change         | Enable bit <sup>(1)</sup> |                       |                       |                       |                       |

| 1 = Enabled<br>0 = Disabled                               | 1 = Enabled           |                           |                       |                       |                       |                       |

|                                                           | rnal Interrupt 3      | Enable bit(1)             |                       |                       |                       |                       |

| 1 = Enabled                                               | nai interrupt s       |                           |                       |                       |                       |                       |

| 0 = Disabled                                              |                       |                           |                       |                       |                       |                       |

| bit 2 INT2IE: Exter                                       | rnal Interrupt 2      | Enable bit <sup>(1)</sup> |                       |                       |                       |                       |

| 1 = Enabled                                               |                       |                           |                       |                       |                       |                       |

| 0 = Disabled                                              |                       |                           |                       |                       |                       |                       |

| bit 1 INT1IE: Exter                                       | rnal Interrupt 1      | Enable bit <sup>(1)</sup> |                       |                       |                       |                       |

| 1 = Enabled                                               |                       |                           |                       |                       |                       |                       |

| 0 = Disabled                                              |                       |                           |                       |                       |                       |                       |

|                                                           | rnal Interrupt 0      | Enable bit <sup>(1)</sup> |                       |                       |                       |                       |

|                                                           |                       |                           |                       |                       |                       |                       |

| 1 = Enabled<br>0 = Disabled<br>Note 1: PIR0 interrupts ar |                       | by the PEIE I             | hit in the INTCO      | ON register an        | e not disabled b      | w the F               |

### REGISTER 14-12: PIE0: PERIPHERAL INTERRUPT ENABLE REGISTER 0

**Note 1:** PIR0 interrupts are not disabled by the PEIE bit in the INTCON register. are not disabled by the PEIE bit in the INTCON register.

# PIC18(L)F67K40

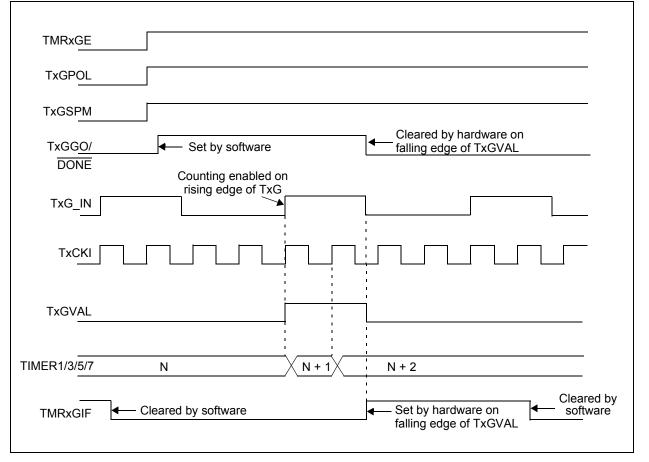

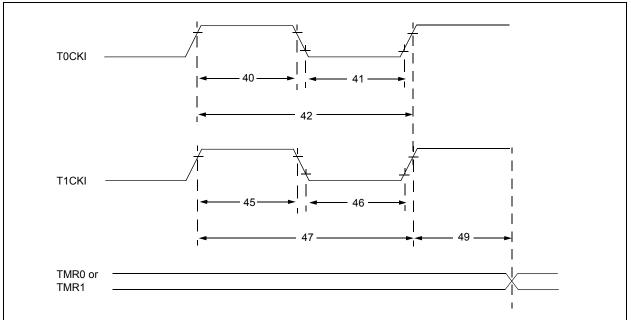

#### FIGURE 19-6: TIMER1/3/5/7 GATE SINGLE-PULSE MODE

© 2016-2017 Microchip Technology Inc.

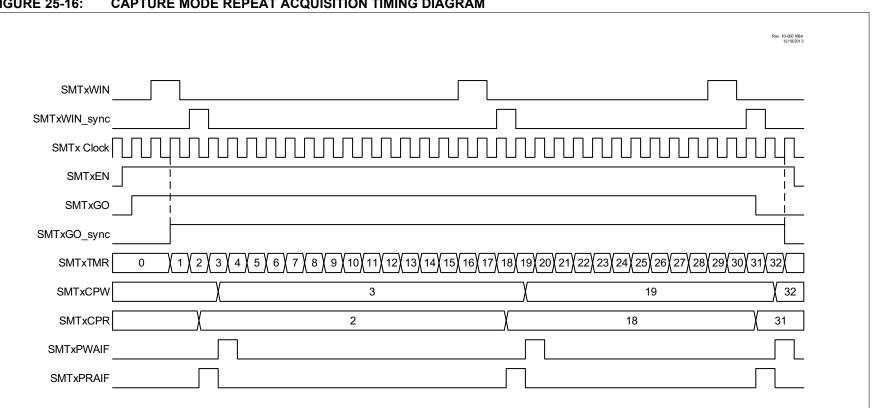

#### 25.7.6 GATED WINDOW MEASURE MODE

This mode measures the duty cycle of the SMTx\_signal input over a known input window. It does so by incrementing the timer on each pulse of the clock signal while the SMTx\_signal input is high, updating the SMTxCPR register and resetting the timer on every rising edge of the SMTWINx input after the first. See Figure 25-12 and Figure 25-13.

#### FIGURE 25-16: CAPTURE MODE REPEAT ACQUISITION TIMING DIAGRAM

PIC18(L)F67K40

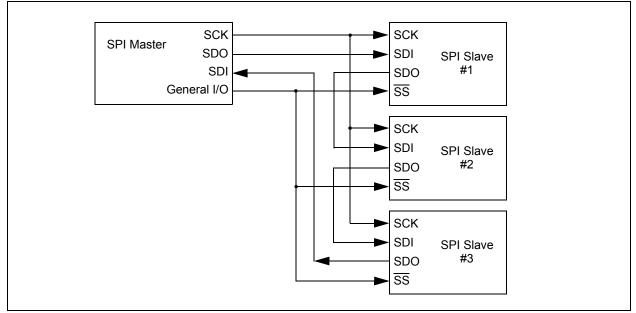

#### 27.5.4 SLAVE SELECT SYNCHRONIZATION

The Slave Select can also be used to synchronize communication. The Slave Select line is held high until the master device is ready to communicate. When the Slave Select line is pulled low, the slave knows that a new transmission is starting.

If the slave fails to receive the communication properly, it will be reset at the end of the transmission, when the Slave Select line returns to a high state. The slave is then ready to receive a new transmission when the Slave Select line is pulled low again. If the Slave Select line is not used, there is a risk that the slave will eventually become out of sync with the master. If the slave misses a bit, it will always be one bit off in future transmissions. Use of the Slave Select line allows the slave and master to align themselves at the beginning of each transmission.

The  $\overline{SS}$  pin allows a Synchronous Slave mode. The SPI must be in Slave mode with  $\overline{SS}$  pin control enabled (SSPxCON1<3:0> = 0100).

FIGURE 27-5: SPI DAISY-CHAIN CONNECTION

When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven.

When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven, even if in the middle of a transmitted byte and becomes a floating output. External pull-up/pull-down resistors may be desirable depending on the application.

- Note 1: When the SPI is in Slave mode with  $\overline{SS}$  pin control enabled (SSPxCON1<3:0> = 0100), the SPI module will reset if the  $\overline{SS}$ pin is set to VDD.

- 2: When the SPI is used in Slave mode with CKE set; the user must enable SS pin control.

- While operated in SPI Slave mode the SMP bit of the SSPxSTAT register must remain clear.

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the SS pin to a high level or clearing the SSPEN bit.

| 1          |                               |                                                                                                          |                                   |                      |                      |                      |                      |  |  |  |

|------------|-------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------|----------------------|----------------------|----------------------|----------------------|--|--|--|

| R/W-0      | R/W/HC-0                      | R/W-0                                                                                                    | R/W-0                             | R/W-0                | R/W-0                | R/W-0                | R/W-0                |  |  |  |

| WCOL       | SSPOV                         | SSPEN <sup>(1)</sup>                                                                                     | CKP                               | SSPM3 <sup>(2)</sup> | SSPM2 <sup>(2)</sup> | SSPM1 <sup>(2)</sup> | SSPM0 <sup>(2)</sup> |  |  |  |

| bit 7      |                               |                                                                                                          |                                   |                      |                      |                      | bit 0                |  |  |  |

|            |                               |                                                                                                          |                                   |                      |                      |                      |                      |  |  |  |

| Legend:    |                               |                                                                                                          |                                   |                      |                      |                      |                      |  |  |  |

| R = Reada  | able bit                      | W = Writable b                                                                                           | bit                               | HC = Bit is cle      | eared by hardw       | /are                 |                      |  |  |  |

| -n = Value | at POR                        | '1' = Bit is set                                                                                         |                                   | '0' = Bit is clea    | ared                 | x = Bit is unkr      | nown                 |  |  |  |

| bit 7      | WCOL · Write                  | e Collision Detec                                                                                        | t hit                             |                      |                      |                      |                      |  |  |  |

|            | In Master Tra                 |                                                                                                          |                                   |                      |                      |                      |                      |  |  |  |

|            | 1 = A write                   | to the SSPxBU                                                                                            | 0                                 |                      |                      | nditions were        | not valid for a      |  |  |  |

|            | transmis<br>0 = No collis     | sion to be starte                                                                                        | d (must be cl                     | eared in softwar     | re)                  |                      |                      |  |  |  |

|            | In Slave Tran                 |                                                                                                          |                                   |                      |                      |                      |                      |  |  |  |

|            |                               | PxBUF register is                                                                                        | s written while                   | e it is still transm | nitting the previ    | ious word (mus       | t be cleared in      |  |  |  |

|            | software                      | ,                                                                                                        |                                   |                      |                      |                      |                      |  |  |  |

|            | 0 = No collis                 |                                                                                                          | Slavo modoc)                      |                      |                      |                      |                      |  |  |  |

|            | This is a "dor                | ode (Master or S<br>n't care" bit.                                                                       |                                   | <u>-</u>             |                      |                      |                      |  |  |  |

| bit 6      | SSPOV: Rec                    | eive Overflow In                                                                                         | dicator bit                       |                      |                      |                      |                      |  |  |  |

|            |                               | In Receive mode:                                                                                         |                                   |                      |                      |                      |                      |  |  |  |

|            | •                             | 1 = A byte is received while the SSPxBUF register is still holding the previous byte (must be cleared in |                                   |                      |                      |                      |                      |  |  |  |

|            | software<br>0 = No overf      | ,                                                                                                        |                                   |                      |                      |                      |                      |  |  |  |

|            | In Transmit m                 |                                                                                                          |                                   |                      |                      |                      |                      |  |  |  |

|            |                               | n't care" bit in Tra                                                                                     |                                   |                      |                      |                      |                      |  |  |  |

| bit 5      |                               | ter Synchronous                                                                                          |                                   |                      |                      |                      |                      |  |  |  |

|            |                               | the serial port ar<br>serial port and c                                                                  |                                   |                      |                      | ne serial port pi    | ns                   |  |  |  |

| bit 4      |                               | Release Control                                                                                          |                                   |                      |                      |                      |                      |  |  |  |

| Dit 4      | In Slave mod                  |                                                                                                          | bit                               |                      |                      |                      |                      |  |  |  |

|            | 1 = Releases                  |                                                                                                          |                                   |                      |                      |                      |                      |  |  |  |

|            |                               | ck low (clock str                                                                                        | etch), used to                    | ensure data se       | etup time            |                      |                      |  |  |  |

|            | In Master mo<br>Unused in thi |                                                                                                          |                                   |                      |                      |                      |                      |  |  |  |

| bit 3-0    |                               | Master Synchro                                                                                           | nous Serial F                     | Port Mode Selec      | t hits(2)            |                      |                      |  |  |  |

| 511 5-0    |                               | Blave mode: 10-k                                                                                         |                                   |                      |                      | enabled              |                      |  |  |  |

|            | $1110 = I^2 C S$              | lave mode: 7-bi                                                                                          | t address with                    | Start and Stop       | bit interrupts e     |                      |                      |  |  |  |

|            |                               | irmware Control                                                                                          |                                   |                      |                      |                      |                      |  |  |  |

|            | $1000 = I^2 C N$              | laster mode: Clo<br>Slave mode: 10-b                                                                     | )0CK = FOSC/(4<br>0it address(3,4 | * (SSPxADD +<br>)    | 1))                  |                      |                      |  |  |  |

|            |                               | Slave mode: 7-bi                                                                                         |                                   |                      |                      |                      |                      |  |  |  |

| Note 1:    | When enabled, th              | ne SDAv and SC                                                                                           | 1 v nine muet                     | be configured (      | ae innute            |                      |                      |  |  |  |

|            | Bit combinations              |                                                                                                          | •                                 | •                    | •                    | ed in SPI mode       | a only               |  |  |  |

## **REGISTER 27-7:** SSPxCON1: MSSPx CONTROL REGISTER 1 (I<sup>2</sup>C MASTER MODE)

2: Bit combinations not specifically listed here are either reserved or implemented in SPI mode only.

#### 32.3 **ADC Acquisition Requirements**

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 32-4. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), refer to Figure 32-4. The maximum recommended impedance for analog sources is 10 k $\Omega$ . As the

source impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an ADC acquisition must be completed before the conversion can be started. To calculate the minimum acquisition time, Equation 32-1 may be used. This equation assumes that 1/2 LSb error is used (1,024 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

#### EQUATION 32-1: ACQUISITION TIME EXAMPLE

Assumptions: Temperature =

$$50^{\circ}C$$

and external impedance of  $10k\Omega 5.0V$  VDD

$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient$

$= TAMP + TC + TCOFF$

$= 2\mu s + TC + [(Temperature - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$

The value for TC can be approximated with the following equations:

The value for TC can be approximated with the following equations:

$$V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) = V_{CHOLD} ; [1] V_{CHOLD} charged to within 1/2 lsb$$

$$V_{APPLIED}\left(1 - e^{\frac{-TC}{RC}}\right) = V_{CHOLD} ; [2] V_{CHOLD} charge response to V_{APPLIED} V_{APPLIED}\left(1 - e^{\frac{-TC}{RC}}\right) = V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) ; combining [1] and [2]$$

Note: Where n = number of bits of the ADC.

Solving for TC:

$$Tc = -C_{HOLD}(RIC + RSS + RS) \ln(1/2047)$$

= -10pF(1k\Omega + 7k\Omega + 10k\Omega) \ln(0.0004885)

= 1.37\mus

Therefore:

$$TACQ = 2\mu s + 892ns + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

= 4.62\mu s

Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- 3: The maximum recommended impedance for analog sources is 10 k $\Omega$ . This is required to meet the pin leakage specification.

| U-0     | R/W-0/0 | R/W-0/0     | R/W-0/0 | R/W/HC-0 | R/W-0/0 | R/W-0/0    | R/W-0/0 |

|---------|---------|-------------|---------|----------|---------|------------|---------|

| -       |         | ADCALC<2:0> |         | ADSOI    |         | ADTMD<2:0> |         |

| bit 7   |         |             |         |          |         |            | bit 0   |

|         |         |             |         |          |         |            |         |

| Legend: |         |             |         |          |         |            |         |

| J. J |                      |                                                       |

|------------------------------------------|----------------------|-------------------------------------------------------|

| R = Readable bit                         | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged                     | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set                         | '0' = Bit is cleared | HC = Bit is cleared by hardware                       |

#### bit 7 Unimplemented: Read as '0'

bit 6-4 ADCALC<2:0>: ADC Error Calculation Mode Select bits

|        | Action During                    |                                                     |                                                              |

|--------|----------------------------------|-----------------------------------------------------|--------------------------------------------------------------|

| ADCALC | ADDSEN = 0<br>Single-Sample Mode | ADDSEN = 1 CVD<br>Double-Sample Mode <sup>(1)</sup> | Application                                                  |

| 111    | Reserved                         | Reserved                                            | Reserved                                                     |

| 110    | Reserved                         | Reserved                                            | Reserved                                                     |

| 101    | ADLFTR-ADSTPT                    | ADFLTR-ADSTPT                                       | Average/filtered value vs. setpoint                          |

| 100    | ADPREV-ADFLTR                    | ADPREV-ADFLTR                                       | First derivative of filtered value <sup>(3)</sup> (negative) |

| 011    | Reserved                         | Reserved                                            | Reserved                                                     |

| 010    | ADRES-ADFLTR                     | (ADRES-ADPREV)-ADFLTR                               | Actual result vs.<br>averaged/filtered value                 |

| 001    | ADRES-ADSTPT                     | (ADRES-ADPREV)-ADSTPT                               | Actual result vs.setpoint                                    |

| 000    | ADRES-ADPREV                     | ADRES-ADPREV                                        | First derivative of single measurement <sup>(2)</sup>        |

|        |                                  |                                                     | Actual CVD result in CVD mode <sup>(2)</sup>                 |

bit 3 ADSOI: ADC Stop-on-Interrupt bit

#### If ADCONT = 1:

- 1 = ADGO is cleared when the threshold conditions are met, otherwise the conversion is retriggered

- 0 = ADGO is not cleared by hardware, must be cleared by software to stop retriggers

#### bit 2-0 ADTMD<2:0>: Threshold Interrupt Mode Select bits

- 111 = Interrupt regardless of threshold test results

- 110 = Interrupt if ADERR>ADUTH

- 101 = Interrupt if ADERR≤ADUTH

- 100 = Interrupt if ADERR<ADLTH or ADERR>ADUTH

- 011 = Interrupt if ADERR>ADLTH and ADERR<ADUTH

- 010 = Interrupt if ADERR≥ADLTH

- 001 = Interrupt if ADERR<ADLTH

- 000 = Never interrupt

- Note 1: When ADPSIS = 0, the value of ADRES-ADPREV) is the value of (S2-S1) from Table 32-3.

- **2:** When ADPSIS = 0

- 3: When ADPSIS = 1.

| R/W-0/0              | R/W-0/0    | R/W-0/0                            | R/W-0/0          | R/W-0/0                                               | R/W-0/0                            | R/W-0/0 | R/W-0/0 |  |  |

|----------------------|------------|------------------------------------|------------------|-------------------------------------------------------|------------------------------------|---------|---------|--|--|

|                      |            |                                    | ADPR             | RE<7:0>                                               |                                    |         |         |  |  |

| bit 7                |            |                                    |                  |                                                       |                                    |         | bit 0   |  |  |

|                      |            |                                    |                  |                                                       |                                    |         |         |  |  |

| Legend:              |            |                                    |                  |                                                       |                                    |         |         |  |  |

| R = Readable bit     |            | W = Writable                       | W = Writable bit |                                                       | U = Unimplemented bit, read as '0' |         |         |  |  |

| u = Bit is unchanged |            | x = Bit is unknown                 |                  | -n/n = Value at POR and BOR/Value at all other Resets |                                    |         |         |  |  |

| '1' = Bit is se      | t          | '0' = Bit is clea                  | ared             |                                                       |                                    |         |         |  |  |

|                      |            |                                    |                  |                                                       |                                    |         |         |  |  |

| bit 7-0              | ADPRE<7:0  | >: Precharge Ti                    | me Select bits   | 3                                                     |                                    |         |         |  |  |

|                      |            | <ul> <li>Precharge time</li> </ul> |                  |                                                       |                                    |         |         |  |  |

|                      | 11111110 = | <ul> <li>Precharge time</li> </ul> | e is 254 clocks  | s of the selected                                     | ADC clock                          |         |         |  |  |

|                      | •          |                                    |                  |                                                       |                                    |         |         |  |  |

### REGISTER 32-9: ADPRE: ADC PRECHARGE TIME CONTROL REGISTER

00000001 = Precharge time is 1 clock of the selected ADC clock 00000000 = Precharge time is not included in the data conversion cycle

#### REGISTER 32-10: ADACQ: ADC ACQUISITION TIME CONTROL REGISTER

| R/W-0/0 | R/W-0/0    | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|------------|---------|---------|---------|---------|---------|---------|

|         | ADACQ<7:0> |         |         |         |         |         |         |

| bit 7   |            |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-0 | <b>ADACQ&lt;7:0&gt;</b> : Acquisition (charge share time) Select bits<br>11111111 = Acquisition time is 255 clocks of the selected ADC clock<br>11111110 = Acquisition time is 254 clocks of the selected ADC clock |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | •                                                                                                                                                                                                                   |

|         | 00000001 = Acquisition time is 1 clock of the selected ADC clock<br>00000000 = Acquisition time is not included in the data conversion cycle                                                                        |

| Notor   | If ADDRE is not equal to $(a)$ then ADACO = b'0000000 means Acquisition time is 256 elements                                                                                                                        |

**Note:** If ADPRE is not equal to '0', then ADACQ = b'00000000 means Acquisition time is 256 clocks of the selected ADC clock.

#### REGISTER 32-21: ADPREVL: ADC PREVIOUS RESULT REGISTER

| R-x                                                                                           | R-x | R-x             | R-x  | R-x          | R-x              | R-x      | R-x   |

|-----------------------------------------------------------------------------------------------|-----|-----------------|------|--------------|------------------|----------|-------|

|                                                                                               |     |                 | ADPF | REV<7:0>     |                  |          |       |

| bit 7                                                                                         |     |                 |      |              |                  |          | bit ( |

|                                                                                               |     |                 |      |              |                  |          |       |

| Legend:                                                                                       |     |                 |      |              |                  |          |       |

| R = Readable b                                                                                | oit | W = Writable bi | it   | U = Unimpler | nented bit, read | d as '0' |       |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets |     |                 |      |              |                  |          |       |

| bit 7-0 | ADPREV<7:0>: Previous ADC Results bits                                    |

|---------|---------------------------------------------------------------------------|

|         | If ADPSIS = 1:                                                            |

|         | Lower byte of ADFLTR at the start of current ADC conversion               |

|         | If $ADPSIS = 0$ :                                                         |

|         | Lower bits of ADRES at the start of current ADC conversion <sup>(1)</sup> |

'0' = Bit is cleared

'1' = Bit is set

**Note 1:** If ADPSIS = 0, ADPREVH and ADPREVL are formatted the same way as ADRES is, depending on the ADFM bit.

#### REGISTER 32-22: ADACCH: ADC ACCUMULATOR REGISTER HIGH

| R/W-x/u     | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |

|-------------|---------|---------|---------|---------|---------|---------|---------|--|

| ADACC<15:8> |         |         |         |         |         |         |         |  |

| bit 7       |         |         |         |         |         |         | bit 0   |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ADACC<15:8>: ADC Accumulator MSB. Upper eight bits of accumulator value. See Table 32-2 for more details.

#### REGISTER 32-23: ADACCL: ADC ACCUMULATOR REGISTER LOW

|                  | -       |                     |         |                |                  |                |              |

|------------------|---------|---------------------|---------|----------------|------------------|----------------|--------------|

| R/W-x/u          | R/W-x/u | R/W-x/u             | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u        | R/W-x/u      |

|                  |         |                     | ADACO   | C<7:0>         |                  |                |              |

| bit 7            |         |                     |         |                |                  |                | bit 0        |

|                  |         |                     |         |                |                  |                |              |

| Legend:          |         |                     |         |                |                  |                |              |

| R = Readable     | bit     | W = Writable bit    |         | U = Unimpler   | nented bit, read | d as '0'       |              |

| u = Bit is unch  | anged   | x = Bit is unknow   | wn      | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is set |         | '0' = Bit is cleare | ed      |                |                  |                |              |

bit 7-0 **ADACC<7:0>**: ADC Accumulator LSB. Lower eight bits of accumulator value. See Table 32-2 for more details.

© 2016-2017 Microchip Technology Inc.

# PIC18(L)F67K40

| MULLW                                                                                        | Multiply                                                                                                             | Multiply literal with W                                                                                                                                                                                                                                                                                                                                                                      |                                       |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--|--|--|--|--|--|

| Syntax:                                                                                      | MULLW                                                                                                                | MULLW k                                                                                                                                                                                                                                                                                                                                                                                      |                                       |  |  |  |  |  |  |

| Operands:                                                                                    | $0 \le k \le 255$                                                                                                    | $0 \leq k \leq 255$                                                                                                                                                                                                                                                                                                                                                                          |                                       |  |  |  |  |  |  |

| Operation:                                                                                   | (W) x k $\rightarrow$                                                                                                | PRODH:PRO                                                                                                                                                                                                                                                                                                                                                                                    | DL                                    |  |  |  |  |  |  |

| Status Affected:                                                                             | None                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                              |                                       |  |  |  |  |  |  |

| Encoding:                                                                                    | 0000                                                                                                                 | 1101 kk                                                                                                                                                                                                                                                                                                                                                                                      | kk kkkk                               |  |  |  |  |  |  |

| Description:                                                                                 | out betwee<br>8-bit literal<br>placed in th<br>pair. PROE<br>W is uncha<br>None of the<br>Note that r<br>possible in | An unsigned multiplication is carried<br>out between the contents of W and the<br>8-bit literal 'k'. The 16-bit result is<br>placed in the PRODH:PRODL register<br>pair. PRODH contains the high byte.<br>W is unchanged.<br>None of the Status flags are affected.<br>Note that neither overflow nor carry is<br>possible in this operation. A zero result<br>is possible but not detected. |                                       |  |  |  |  |  |  |

| Words:                                                                                       | 1                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                              |                                       |  |  |  |  |  |  |

| Cycles:                                                                                      | 1                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                              |                                       |  |  |  |  |  |  |

| Q Cycle Activity:                                                                            |                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                              |                                       |  |  |  |  |  |  |

| Q1                                                                                           | Q2                                                                                                                   | Q3                                                                                                                                                                                                                                                                                                                                                                                           | Q4                                    |  |  |  |  |  |  |

| Decode                                                                                       | Read<br>literal 'k'                                                                                                  | Process<br>Data                                                                                                                                                                                                                                                                                                                                                                              | Write<br>registers<br>PRODH:<br>PRODL |  |  |  |  |  |  |

| Example:<br>Before Instruc<br>W<br>PRODH<br>PRODL<br>After Instructic<br>W<br>PRODH<br>PRODH | = E2<br>= ?<br>= ?<br>m<br>= E2                                                                                      | 2h<br>Dh                                                                                                                                                                                                                                                                                                                                                                                     |                                       |  |  |  |  |  |  |

| MULWF             | Multiply                                                                                                                                                                                                                                                                                                | W with f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                       |  |  |  |  |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--|--|--|--|--|--|

| Syntax:           | MULWF                                                                                                                                                                                                                                                                                                   | MULWF f {,a}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                       |  |  |  |  |  |  |

| Operands:         | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                                                                                                                                                                                                                                                | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                       |  |  |  |  |  |  |

| Operation:        | (W) x (f) –                                                                                                                                                                                                                                                                                             | > PRODH:PR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ODL                                   |  |  |  |  |  |  |

| Status Affected:  | None                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       |  |  |  |  |  |  |

| Encoding:         | 0000                                                                                                                                                                                                                                                                                                    | 001a ff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ff ffff                               |  |  |  |  |  |  |

| Description:      | out betwee<br>register file<br>result is st<br>register pa<br>high byte.<br>unchange<br>None of th<br>Note that is<br>possible in<br>result is po<br>If 'a' is '0',<br>selected. I<br>to select th<br>If 'a' is '0' a<br>set is enal<br>operates i<br>Addressin<br>$f \le 95$ (5FF<br><b>36.2.3 "By</b> | An unsigned multiplication is carried<br>out between the contents of W and the<br>register file location 'f'. The 16-bit<br>result is stored in the PRODH:PRODL<br>register pair. PRODH contains the<br>high byte. Both W and 'f' are<br>unchanged.<br>None of the Status flags are affected.<br>Note that neither overflow nor carry is<br>possible in this operation. A zero<br>result is possible but not detected.<br>If 'a' is '0', the Access Bank is<br>selected. If 'a' is '1', the BSR is used<br>to select the GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction<br>operates in Indexed Literal Offset<br>Addressing mode whenever<br>$f \le 95$ (5Fh). See Section<br><b>36.2.3 "Byte-Oriented and Bit-Ori-<br/>ented Instructions in Indexed Literal</b> |                                       |  |  |  |  |  |  |

| Words:            | 1                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       |  |  |  |  |  |  |

| Cycles:           | 1                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       |  |  |  |  |  |  |

| Q Cycle Activity: |                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       |  |  |  |  |  |  |

| Q1                | Q2                                                                                                                                                                                                                                                                                                      | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Q4                                    |  |  |  |  |  |  |

| Decode            | Read<br>register 'f'                                                                                                                                                                                                                                                                                    | Process<br>Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Write<br>registers<br>PRODH:<br>PRODL |  |  |  |  |  |  |

| Example:          | MULWF                                                                                                                                                                                                                                                                                                   | REG, 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                       |  |  |  |  |  |  |

| Before Instruc    | tion                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       |  |  |  |  |  |  |

| W                 | • • • • • • • • • • • • • • • • • • • •                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       |  |  |  |  |  |  |

B5h ? ?

C4h

B5h 8Ah 94h

= = =

=

= = =

REG PRODH

PRODL After Instruction W

REG PRODH PRODL

© 2016-2017 Microchip Technology Inc.

| TBL   | RD              | Table Rea                                                                                                                                                                                                                                                                                                                                                                                | d                                                                                                   |                                                                       |                                                                                                                          |                                             |  |  |

|-------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|--|--|

| Synta | ax:             | TBLRD ( *; *                                                                                                                                                                                                                                                                                                                                                                             | *+; *-;                                                                                             | +*)                                                                   |                                                                                                                          |                                             |  |  |

| Oper  | ands:           | None                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                     |                                                                       |                                                                                                                          |                                             |  |  |

| Oper  |                 | if TBLRD *,<br>(Prog Mem (TBLPTR)) $\rightarrow$ TABLAT;<br>TBLPTR – No Change;<br>if TBLRD *+,<br>(Prog Mem (TBLPTR)) $\rightarrow$ TABLAT;<br>(TBLPTR) + 1 $\rightarrow$ TBLPTR;<br>if TBLRD *-,<br>(Prog Mem (TBLPTR)) $\rightarrow$ TABLAT;<br>(TBLPTR) – 1 $\rightarrow$ TBLPTR;<br>if TBLRD +*,<br>(TBLPTR) + 1 $\rightarrow$ TBLPTR;<br>(Prog Mem (TBLPTR)) $\rightarrow$ TABLAT; |                                                                                                     |                                                                       |                                                                                                                          |                                             |  |  |

| Statu | s Affected:     | None                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                     |                                                                       |                                                                                                                          |                                             |  |  |

| Enco  | ding:           | 0000                                                                                                                                                                                                                                                                                                                                                                                     | 000                                                                                                 | 00                                                                    | 0000                                                                                                                     | 0 10nn<br>nn=0 *<br>=1 *+<br>=2 *-<br>=3 +* |  |  |