Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 64MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 60                                                                           |

| Program Memory Size        | 128KB (64K x 16)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 1K x 8                                                                       |

| RAM Size                   | 3.5K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 47x10b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 64-TQFP                                                                      |

| Supplier Device Package    | 64-TQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf67k40t-i-pt |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC18(L)F67K40

#### **REGISTER 4-5: OSCFRQ: HFINTOSC FREQUENCY SELECTION REGISTER** U-0 R/W-q/q R/W-q/q R/W-q/q U-0 U-0 U-0 R/W-q/q \_\_\_\_ \_\_\_\_ HFFRQ<3:0> \_\_\_\_ \_\_\_\_ bit 7 bit 0

# Legend:

| Legenu.              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Reset value is determined by hardware             |

#### bit 7-4 Unimplemented: Read as '0'

bit 3-0 HFFRQ<3:0>: HFINTOSC Frequency Selection bits

| HFFRQ<3:0>          | Nominal Freq (MHz) |  |  |  |  |  |  |

|---------------------|--------------------|--|--|--|--|--|--|

| 1001                |                    |  |  |  |  |  |  |

| 1010                |                    |  |  |  |  |  |  |

| 1111                |                    |  |  |  |  |  |  |

| 1110                | Reserved           |  |  |  |  |  |  |

| 1101                | Reserved           |  |  |  |  |  |  |

| 1100                |                    |  |  |  |  |  |  |

| 1011                |                    |  |  |  |  |  |  |

| 1000 <sup>(3)</sup> | 64                 |  |  |  |  |  |  |

| 0111                | 48                 |  |  |  |  |  |  |

| 0110                | 32                 |  |  |  |  |  |  |

| 0101 <sup>(4)</sup> | 16                 |  |  |  |  |  |  |

| 0100                | 12                 |  |  |  |  |  |  |

| 0011                | 8                  |  |  |  |  |  |  |

| 0010 <b>(1,2)</b>   | 4                  |  |  |  |  |  |  |

| 0001                | 2                  |  |  |  |  |  |  |

| 0000                | 1                  |  |  |  |  |  |  |

**Note 1:** Refer to Table 4-1 for more information.

| U-0            | U-0                | U-0               | U-0         | U-0            | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|----------------|--------------------|-------------------|-------------|----------------|------------------|------------------|--------------|

| _              | _                  | —                 | —           | —              |                  | CLK<2:0>         |              |

| bit 7          |                    |                   |             |                |                  |                  | bit C        |

|                |                    |                   |             |                |                  |                  |              |

| Legend:        |                    |                   |             |                |                  |                  |              |

| R = Reada      | ble bit            | W = Writable      | bit         | U = Unimpler   | nented bit, read | d as '0'         |              |

| u = Bit is u   | nchanged           | x = Bit is unkr   | iown        | -n/n = Value a | at POR and BC    | R/Value at all o | other Resets |

| '1' = Bit is s | set                | '0' = Bit is clea | ared        |                |                  |                  |              |

|                |                    |                   |             |                |                  |                  |              |

| bit 7-3        | Unimplemen         | nted: Read as '   | כי          |                |                  |                  |              |

| bit 2-0        | CLK<2:0>: C        | LKR Clock Sel     | ection bits |                |                  |                  |              |

|                | 111 <b>= Unimp</b> | lemented          |             |                |                  |                  |              |

|                | 110 <b>= Unimp</b> | lemented          |             |                |                  |                  |              |

|                | 101 <b>= Unimp</b> | lemented          |             |                |                  |                  |              |

|                | 100 <b>= SOSC</b>  |                   |             |                |                  |                  |              |

|                | 011 = MFINT        | OSC (500 kHz      | )           |                |                  |                  |              |

|                | 010 = LFINT        | OSC (31 kHz)      |             |                |                  |                  |              |

|                | 001 = HFINT        | OSC               |             |                |                  |                  |              |

|                | 000 = FOSC         |                   |             |                |                  |                  |              |

#### TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH CLOCK REFERENCE OUTPUT

| Name    | Bit 7  | Bit 6 | Bit 5  | Bit 4       | Bit 3  | Bit 2    | Bit 1  | Bit 0 | Register<br>on Page |  |

|---------|--------|-------|--------|-------------|--------|----------|--------|-------|---------------------|--|

| CLKRCON | EN     | _     | _      | DC<         | :1:0>  |          | 54     |       |                     |  |

| CLKRCLK | —      | _     | _      | _           | _      | CLK<2:0> |        |       | 55                  |  |

| PMD0    | SYSCMD | FVRMD | HLVDMD | CRCMD       | SCANMD | NVMMD    | CLKRMD | IOCMD | 66                  |  |

| RxyPPS  | —      | —     |        | RxyPPS<5:0> |        |          |        |       |                     |  |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the CLKR module.

#### 6.2.3.2 Peripheral Usage in Sleep

Some peripherals that can operate in Sleep mode will not operate properly with the Low-Power Sleep mode selected. The Low-Power Sleep mode is intended for use with these peripherals:

- Brown-out Reset (BOR)

- Windowed Watchdog Timer (WWDT)

- External interrupt pin/Interrupt-On-Change pins

- Peripherals that run off external secondary clock source

It is the responsibility of the end user to determine what is acceptable for their application when setting the VREGPM settings in order to ensure operation in Sleep.

| Note: | The PIC18LF6xK40 devices do not have a   |

|-------|------------------------------------------|

|       | configurable Low-Power Sleep mode.       |

|       | PIC18LF6xK40 devices are unregulated     |

|       | and are always in the lowest power state |

|       | when in Sleep, with no wake-up time      |

|       | penalty. These devices have a lower max- |

|       | imum VDD and I/O voltage than the        |

|       | PIC18F6xK40 devices. See Section         |

|       | 38.0 "Electrical Specifications" for     |

|       | more information.                        |

### 6.2.4 IDLE MODE

When IDLEN is set (IDLEN = 1), the SLEEP instruction will put the device into Idle mode. In Idle mode, the CPU and memory operations are halted, but the peripheral clocks continue to run. This mode is similar to Doze mode, except that in IDLE both the CPU and PFM are shut off.

Note: If CLKOUTEN is enabled (CLKOUTEN = 0, Configuration Word 1H), the output will continue operating while in Idle.

### 6.2.4.1 Idle and Interrupts

IDLE mode ends when an interrupt occurs (even if GIE = 0), but IDLEN is not changed. The device can reenter IDLE by executing the SLEEP instruction.

If Recover-On-Interrupt is enabled (ROI = 1), the interrupt that brings the device out of Idle also restores full-speed CPU execution when doze is also enabled.

#### 6.2.4.2 Idle and WWDT

When in Idle, the WWDT Reset is blocked and will instead wake the device. The WWDT wake-up is not an interrupt, therefore ROI does not apply.

Note: The WDT can bring the device out of Idle, in the same way it brings the device out of Sleep. The DOZEN bit is not affected.

# 6.3 Peripheral Operation in Power Saving Modes

All selected clock sources and the peripherals running off them are active in both IDLE and DOZE mode. Only in Sleep mode, both the Fosc and Fosc/4 clocks are unavailable. All the other clock sources are active, if enabled manually or through peripheral clock selection before the part enters Sleep.

# 7.5 Register Definitions: Peripheral Module Disable

| REGISTER                                                                                                                                               | R/W-0/0                            | R/W-0/0                                                                           | R/W-0/0                         | R/W-0/0            | R/W-0/0        | R/W-0/0        | R/W-0/0      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------------------------------------------------------------------|---------------------------------|--------------------|----------------|----------------|--------------|

| SYSCMD                                                                                                                                                 | FVRMD                              | HLVDMD                                                                            | CRCMD                           | SCANMD             | NVMMD          | CLKRMD         | IOCMD        |

| 7                                                                                                                                                      |                                    |                                                                                   |                                 |                    |                |                | (            |

|                                                                                                                                                        |                                    |                                                                                   |                                 |                    |                |                |              |

| Legend:                                                                                                                                                | - h:t                              |                                                                                   | L :4                            |                    |                | l (0)          |              |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other |                                    |                                                                                   |                                 |                    |                |                |              |

| u = Bit is und                                                                                                                                         | •                                  | x = Bit is unkr                                                                   |                                 |                    |                |                | ther Resets  |

| '1' = Bit is se                                                                                                                                        | et                                 | '0' = Bit is clea                                                                 | ared                            | q = value dep      | ends on condi  | lion           |              |

| bit 7                                                                                                                                                  | See descript<br>1 = System         | isable Periphera<br>ion in <b>Section 7</b><br>clock network d<br>clock network e | 7.4 "System C<br>isabled (Fosc) | lock Disable".     |                |                |              |

| bit 6                                                                                                                                                  | 1 = FVR mo                         | able Fixed Volta<br>dule disabled<br>dule enabled                                 | ige Reference                   | bit                |                |                |              |

| bit 5                                                                                                                                                  | 1 = HLVD n                         | isable Low-Volta<br>nodule disabled<br>nodule enabled                             | age Detect bit                  |                    |                |                |              |

| bit 4                                                                                                                                                  | 1 = CRC mo                         | able CRC Engir<br>odule disabled<br>odule enabled                                 | ne bit                          |                    |                |                |              |

| bit 3                                                                                                                                                  | 1 = NVM M                          | isable NVM Me<br>emory Scan mo<br>emory Scan mo                                   | dule disabled                   | bit <sup>(2)</sup> |                |                |              |

| bit 2                                                                                                                                                  | 1 = All Mem                        | /M Module Disal<br>ory reading and<br>odule enabled                               |                                 | bled; NVMCON       | registers canr | not be written |              |

| bit 1                                                                                                                                                  | 1 = CLKR m                         | isable Clock Re<br>nodule disabled<br>nodule enabled                              | ference bit                     |                    |                |                |              |

| bit 0                                                                                                                                                  | 1 = IOC mo                         | able Interrupt-on<br>dule(s) disabled<br>dule(s) enabled                          | -Change bit, A                  | All Ports          |                |                |              |

|                                                                                                                                                        | learing the SYS<br>y Fosc/4 are no | SCMD bit disable of affected.                                                     | es the system                   | clock (Fosc) to    | peripherals, h | owever periphe | rals clocked |

# REGISTER 7-1: PMD0: PMD CONTROL REGISTER 0

- 2: Subject to SCANE bit in CONFIG4H.

- **3:** When enabling NVM, a delay of up to 1 µs may be required before accessing data.

# EXAMPLE 11-4: WRITING TO PROGRAM FLASH MEMORY (CONTINUED)

| WRITE_BYTE  | TO_HREGS |                     |                                         |

|-------------|----------|---------------------|-----------------------------------------|

|             | MOVF     | POSTINC0, W         | ; get low byte of buffer data           |

|             | MOVWF    | TABLAT              | ; present data to table latch           |

|             | TBLWT+*  |                     | ; write data, perform a short write     |

|             |          |                     | ; to internal TBLWT holding register.   |

|             | DECFSZ   | COUNTER             | ; loop until holding registers are full |

|             | BRA      | WRITE_WORD_TO_HREGS |                                         |

| PROGRAM_MEN | MORY     |                     |                                         |

|             | BCF      | NVMCON1, NVMREG0    | ; point to Program Flash Memory         |

|             | BSF      | NVMCON1, NVMREG1    | ; point to Program Flash Memory         |

|             | BSF      | NVMCON1, WREN       | ; enable write to memory                |

|             | BCF      | NVMCON1, FREE       | ; enable write to memory                |

|             | BCF      | INTCON, GIE         | ; disable interrupts                    |

|             | MOVLW    | 55h                 |                                         |

| Required    | MOVWF    | NVMCON2             | ; write 55h                             |

| Sequence    | MOVLW    | 0AAh                |                                         |

|             | MOVWF    | NVMCON2             | ; write OAAh                            |

|             | BSF      | NVMCON1, WR         | ; start program (CPU stall)             |

|             | DCFSZ    | COUNTER2            | ; repeat for remaining write blocks     |

|             | BRA      | WRITE_BYTE_TO_HREGS |                                         |

|             | BSF      | INTCON, GIE         | ; re-enable interrupts                  |

|             | BCF      | NVMCON1, WREN       | ; disable write to memory               |

|             |          |                     |                                         |

## 13.9 Program Memory Scan Configuration

If desired, the program memory scan module may be used in conjunction with the CRC module to perform a CRC calculation over a range of program memory addresses. In order to set up the scanner to work with the CRC you need to perform the following steps:

- 1. Set the Enable bit in both the CRCCON0 and SCANCON0 registers. If they get disabled, all internal states of the scanner and the CRC are reset (registers are unaffected).

- Choose which memory access mode is to be used (see Section 13.11 "Scanning Modes") and set the MODE bits of the SCANCON0 register appropriately.

- 3. Based on the memory access mode, set the INTM bits of the SCANCON0 register to the appropriate interrupt mode (see Section 13.11.5 "Interrupt Interaction")

- 4. Set the SCANLADRL/H/U and SCANHADRL/H/ U registers with the beginning and ending locations in memory that are to be scanned.

- 5. The CRCGO bit must be set before setting the SCANGO bit. Setting the SCANGO bit starts the scan. Both CRCEN and CRCGO bits must be enabled to use the scanner. When either of these bits are disabled, the scan aborts and the INVALID bit SCANCON0 is set. The scanner will wait for the signal from the CRC that it is ready for the first Flash memory location, then begin loading data into the CRC. It will continue to do so until it either hits the configured end address or an address that is unimplemented on the device, at which point the SCANGO bit will clear, Scanner functions will cease, and the SCANIF interrupt will be triggered. Alternately, the SCANGO bit can be cleared in software if desired.

# 13.10 Scanner Interrupt

The scanner will trigger an interrupt when the SCANGO bit transitions from '1' to '0'. The SCANIF interrupt flag of PIR7 is set when the last memory location is reached and the data is entered into the CRCDATA registers. The SCANIF bit can only be cleared in software. The SCAN interrupt enable is the SCANIE bit of the PIE7 register.

## 13.11 Scanning Modes

The memory scanner can scan in four modes: Burst, Peek, Concurrent, and Triggered. These modes are controlled by the MODE bits of the SCANCON0 register. The four modes are summarized in Table 13-2.

### 13.11.1 BURST MODE

When MODE = 01, the scanner is in Burst mode. In Burst mode, CPU operation is stalled beginning with the operation after the one that sets the SCANGO bit, and the scan begins, using the instruction clock to execute. The CPU is held in its current state until the scan stops. Note that because the CPU is not executing instructions, the SCANGO bit cannot be cleared in software, so the CPU will remain stalled until one of the hardware endconditions occurs. Burst mode has the highest throughput for the scanner, but has the cost of stalling other execution while it occurs.

#### 13.11.2 CONCURRENT MODE

When MODE = 00, the scanner is in Concurrent mode. Concurrent mode, like Burst mode, stalls the CPU while performing accesses of memory. However, while Burst mode stalls until all accesses are complete, Concurrent mode allows the CPU to execute in between access cycles.

#### 13.11.3 TRIGGERED MODE

When MODE = 11, the scanner is in Triggered mode. Triggered mode behaves identically to Concurrent mode, except instead of beginning the scan immediately upon the SCANGO bit being set, it waits for a rising edge from a separate trigger clock, the source of which is determined by the SCANTRIG register.

### 13.11.4 PEEK MODE

When MODE = 10, the scanner is in Peek mode. Peek mode waits for an instruction cycle in which the CPU does not need to access the NVM (such as a branch instruction) and uses that cycle to do its own NVM access. This results in the lowest throughput for the NVM access (and can take a much longer time to complete a scan than the other modes), but does so without any impact on execution times, unlike the other modes.

# 20.5.4 LEVEL-TRIGGERED HARDWARE LIMIT MODE

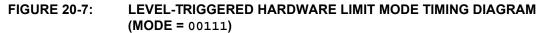

In the Level-Triggered Hardware Limit Timer modes the counter is reset by high or low levels of the external signal TMRx\_ers, as shown in Figure 20-7. Selecting MODE<4:0> = 0.0110 will cause the timer to reset on a low level external signal. Selecting MODE<4:0> = 0.0111 will cause the timer to reset on a high level external signal. In the example, the counter is reset while TMRx\_ers = 1. ON is controlled by BSF and BCF instructions. When ON = 0 the external signal is ignored.

When the CCP uses the timer as the PWM time base then the PWM output will be set high when the timer starts counting and then set low only when the timer count matches the CCPRx value. The timer is reset when either the timer count matches the PRx value or two clock periods after the external Reset signal goes true and stays true.

The timer starts counting, and the PWM output is set high, on either the clock following the PRx match or two clocks after the external Reset signal relinquishes the Reset. The PWM output will remain high until the timer counts up to match the CCPRx pulse width value. If the external Reset signal goes true while the PWM output is high then the PWM output will remain high until the Reset signal is released allowing the timer to count up to match the CCPRx value.

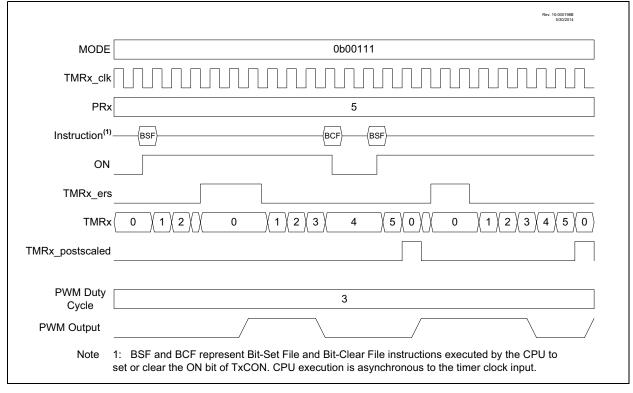

#### 20.5.6 EDGE-TRIGGERED ONE-SHOT MODE

The Edge-Triggered One-Shot modes start the timer on an edge from the external signal input, after the ON bit is set, and clear the ON bit when the timer matches the PRx period value. The following edges will start the timer:

- Rising edge (MODE<4:0> = 01001)

- Falling edge (MODE<4:0> = 01010)

- Rising or Falling edge (MODE<4:0> = 01011)

If the timer is halted by clearing the ON bit then another TMRx\_ers edge is required after the ON bit is set to resume counting. Figure 20-9 illustrates operation in the rising edge One-Shot mode.

When Edge-Triggered One-Shot mode is used in conjunction with the CCP then the edge-trigger will activate the PWM drive and the PWM drive will deactivate when the timer matches the CCPRx pulse width value and stay deactivated when the timer halts at the PRx period count match.

#### FIGURE 20-9: EDGE-TRIGGERED ONE-SHOT MODE TIMING DIAGRAM (MODE = 01001)

#### 20.5.7 EDGE-TRIGGERED HARDWARE LIMIT ONE-SHOT MODE

In Edge-Triggered Hardware Limit One-Shot modes the timer starts on the first external signal edge after the ON bit is set and resets on all subsequent edges. Only the first edge after the ON bit is set is needed to start the timer. The counter will resume counting automatically two clocks after all subsequent external Reset edges. Edge triggers are as follows:

- Rising edge start and Reset (MODE<4:0> = 01100)

- Falling edge start and Reset (MODE<4:0> = 01101)

The timer resets and clears the ON bit when the timer value matches the PRx period value. External signal edges will have no effect until after software sets the ON bit. Figure 20-10 illustrates the rising edge hardware limit one-shot operation.

When this mode is used in conjunction with the CCP then the first starting edge trigger, and all subsequent Reset edges, will activate the PWM drive. The PWM drive will deactivate when the timer matches the CCPRx pulse-width value and stay deactivated until the timer halts at the PRx period match unless an external signal edge resets the timer before the match occurs.

| Name     | Bit 7    | Bit 6     | Bit 5                | Bit 4  | Bit 3       | Bit 2                   | Bit 1   | Bit 0   | Register<br>on Page |  |

|----------|----------|-----------|----------------------|--------|-------------|-------------------------|---------|---------|---------------------|--|

| INTCON   | GIE/GIEH | PEIE/GIEL | IPEN                 | —      | INT3EDG     | INT2EDG                 | INT1EDG | INT0EDG | 173                 |  |

| PIE7     | _        | _         | _                    | CCP5IE | CCP4IE      | CCP3IE                  | CCP2IE  | CCP1IE  | 192                 |  |

| PIR7     | _        | _         | _                    | CCP5IF | CCP4IF      | CCP3IF                  | CCP2IF  | CCP1IF  | 181                 |  |

| IPR7     | _        | _         | _                    | CCP5IP | CCP4IP      | CCP3IP                  | CCP2IP  | CCP1IP  | 202                 |  |

| PMD4     | _        | PWM7MD    | PWM6MD               | CCP5MD | CCP4MD      | CCP3MD                  | CCP2MD  | CCP1MD  | 70                  |  |

| CCPxCON  | EN       | _         | OUT                  | FMT    |             | MOD                     | E<3:0>  |         | 279                 |  |

| CCPxCAP  |          | _         |                      | —      | —           | —                       | CTS<    | <1:0>   | 283                 |  |

| CCPRxL   |          |           |                      |        | CCPRx<7:0>  |                         |         |         | 283                 |  |

| CCPRxH   |          |           |                      |        | CCPRx<15:8> |                         |         |         | 284                 |  |

| CCPTMRS0 | C4TSE    | L<1:0>    | C3TSE                | L<1:0> | C2TSE       | C2TSEL<1:0> C1TSEL<1:0> |         |         |                     |  |

| CCPTMRS1 | _        | _         | P7TSE                | L<1:0> | P6TSE       | L<1:0>                  | C5TSE   | L<1:0>  | 282                 |  |

| CCPxPPS  | _        | _         |                      |        | CCP         | xPPS<5:0>               |         |         | 225                 |  |

| RxyPPS   | _        | _         |                      |        | Rxy         | PPS<5:0>                |         |         | 228                 |  |

| T1CON    | _        | _         | T1CKP                | S<1:0> | _           | T1SYNC                  | T1RD16  | TMR10N  | 240                 |  |

| T1GCON   | TMR1GE   | T1GPOL    | T1GTM                | T1GSPM | T1GO/DONE   | T1GVAL                  | _       |         | 241                 |  |

| T1CLK    | _        | _         | _                    | _      |             | CS<                     | <3:0>   |         | 242                 |  |

| T1GATE   | _        | _         | _                    | _      |             | GSS                     | <3:0>   |         | 243                 |  |

| TMR1L    | TMR1L7   | TMR1L6    | TMR1L5               | TMR1L4 | TMR1L3      | TMR1L2                  | TMR1L1  | TMR1L0  | 244                 |  |

| TMR1H    | TMR1H7   | TMR1H6    | TMR1H5               | TMR1H4 | TMR1H3      | TMR1H2                  | TMR1H1  | TMR1H0  | 244                 |  |

| TMR2     |          |           |                      |        | TMR2<7:0>   |                         |         |         | 255*                |  |

| T2PR     |          |           |                      |        | PR2<7:0>    |                         |         |         | 255*                |  |

| T2CON    | ON       |           | CKPS<2:0> OUTPS<3:0> |        |             |                         |         | 273     |                     |  |

| T2HLT    | PSYNC    | CPOL      | CSYNC                |        |             | MODE<4:0>               |         |         | 274                 |  |

| T2CLKCON | _        | —         | _                    | —      |             | CS<                     | <3:0>   |         | 275                 |  |

| T2RST    | _        | _         | _                    | _      |             | RSEL                    | _<3:0>  |         | 276                 |  |

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by the CCP module.

Not a physical register.

| Name       | Bit 7    | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2         | Bit 1     | Bit 0  | Register<br>on Page |

|------------|----------|-------|-------|-------|-------|---------------|-----------|--------|---------------------|

| CWG1CON0   | EN       | LD    | —     | —     | —     |               | MODE<2:0> | •      | 327                 |

| CWG1CON1   | _        | _     | IN    | —     | POLD  | POLC          | POLB      | POLA   | 328                 |

| CWG1CLKCON | _        | _     | _     | _     | _     | _             | _         | CS     | 329                 |

| CWG1ISM    | —        | _     | —     | —     |       | ISM<3:0>      |           |        |                     |

| CWG1STR    | OVRD     | OVRC  | OVRB  | OVRA  | STRD  | STRC          | STRB      | STRA   | 330                 |

| CWG1AS0    | SHUTDOWN | REN   | LSBD  | <1:0> | LSAC  | LSAC<1:0> — — |           | —      | 331                 |

| CWG1AS1    | AS7E     | AS6E  | AS5E  | AS4E  | AS3E  | AS2E          | AS1E      | AS0E   | 332                 |

| CWG1DBR    |          | _     |       |       | DBR<  | <5:0>         |           |        | 333                 |

| CWG1DBF    | _        | _     |       |       | DBF<  | :5:0>         |           |        | 333                 |

| PIE8       | SCANIE   | CRCIE | NVMIE | _     | _     | _             | _         | CWG1IE | 193                 |

| PIR8       | SCANIF   | CRCIF | NVMIF | —     | —     | _             | _         | CWG1IF | 183                 |

| IPR8       | SCANIP   | CRCIP | NVMIP | —     | _     | _             | _         | CWG1IP | 203                 |

| PMD2       | —        | _     | CWGMD | —     | DSMMD | SMT2MD        | SMT1MD    | TMR8MD | 68                  |

#### TABLE 24-3: SUMMARY OF REGISTERS ASSOCIATED WITH CWG

Legend: -= unimplemented locations read as '0'. Shaded cells are not used by CWG.

| Name      | Bit 7 | Bit 6 | Bit 5 | Bit 4        | Bit 3 | Bit 2   | Bit 1  | Bit 0  | Register<br>on Page |  |

|-----------|-------|-------|-------|--------------|-------|---------|--------|--------|---------------------|--|

| MDCON0    | EN    | _     | OUT   | OPOL         | —     | —       | —      | BIT    | 381                 |  |

| MDCON1    | _     |       | CHPOL | CHSYNC       | —     | _       | CLPOL  | CLSYNC | 382                 |  |

| MDCARH    | _     | —     | _     | — — CHS<3:0> |       |         |        |        |                     |  |

| MDCARL    |       |       | _     | — — CLS<3:0> |       |         |        |        |                     |  |

| MDSRC     | —     | _     | _     | — SRCS<4:0>  |       |         |        |        |                     |  |

| MDCARLPPS |       | —     |       | CARLPPS<5:0> |       |         |        |        |                     |  |

| MDCARHPPS | _     | _     |       |              | CARHP | PS<5:0> |        |        | 225                 |  |

| MDSRCPPS  | _     | —     |       | SRCPPS<5:0>  |       |         |        |        |                     |  |

| RxyPPS    | —     |       |       | RxyPPS<5:0>  |       |         |        |        |                     |  |

| PMD2      | _     |       | CWGMD |              | DSMMD | SMT2MD  | SMT1MD | TMR8MD | 68                  |  |

# TABLE 26-4: SUMMARY OF REGISTERS ASSOCIATED WITH DATA SIGNAL MODULATOR MODE

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used in the Data Signal Modulator mode.

# 27.4 Register Definitions: MSSP Control

| R/W-0        | R/W-0                                                                          | R-0                 | R-0            | R-0              | R-0             | R-0             | R-0           |  |  |  |  |  |

|--------------|--------------------------------------------------------------------------------|---------------------|----------------|------------------|-----------------|-----------------|---------------|--|--|--|--|--|

| SMP          | CKE <sup>(1)</sup>                                                             | D/A                 | Р              | S                | R/W             | UA              | BF            |  |  |  |  |  |

| bit 7        |                                                                                |                     |                |                  |                 |                 | bit           |  |  |  |  |  |

|              |                                                                                |                     |                |                  |                 |                 |               |  |  |  |  |  |

| Legend:      |                                                                                |                     |                |                  |                 |                 |               |  |  |  |  |  |

| R = Readab   | ole bit                                                                        | W = Writable        | bit            | U = Unimpler     | nented bit, rea | ad as '0'       |               |  |  |  |  |  |

| -n = Value a | It POR                                                                         | '1' = Bit is set    |                | '0' = Bit is cle | ared            | x = Bit is unkr | nown          |  |  |  |  |  |

|              |                                                                                |                     |                |                  |                 |                 |               |  |  |  |  |  |

| bit 7        | SMP: Samp                                                                      |                     |                |                  |                 |                 |               |  |  |  |  |  |

|              | <u>SPI Master</u>                                                              |                     | the end of de  |                  |                 |                 |               |  |  |  |  |  |

|              |                                                                                | ita is sampled at   |                |                  | <u>e</u>        |                 |               |  |  |  |  |  |

|              | 0 = Input data is sampled at the middle of data output time<br>SPI Slave mode: |                     |                |                  |                 |                 |               |  |  |  |  |  |

|              | SMP must be cleared when SPI is used in Slave mode.                            |                     |                |                  |                 |                 |               |  |  |  |  |  |

| bit 6        | CKE: SPI Clock Select bit <sup>(1)</sup>                                       |                     |                |                  |                 |                 |               |  |  |  |  |  |

|              | 1 = Transmit occurs on the transition from active to Idle clock state          |                     |                |                  |                 |                 |               |  |  |  |  |  |

|              | 0 = Transmit occurs on the transition from Idle to active clock state          |                     |                |                  |                 |                 |               |  |  |  |  |  |

| bit 5        | D/A: Data/Address bit                                                          |                     |                |                  |                 |                 |               |  |  |  |  |  |

|              | Used in I <sup>2</sup> C mode only.                                            |                     |                |                  |                 |                 |               |  |  |  |  |  |

| bit 4        | P: Stop bit                                                                    |                     |                |                  |                 |                 |               |  |  |  |  |  |

|              | Used in I <sup>2</sup> C                                                       | mode only. This     | bit is cleared | when the MSSF    | Px module is d  | lisabled; SSPEN | l is cleared. |  |  |  |  |  |

| bit 3        | S: Start bit                                                                   |                     |                |                  |                 |                 |               |  |  |  |  |  |

|              | Used in I <sup>2</sup> C                                                       | mode only.          |                |                  |                 |                 |               |  |  |  |  |  |

| bit 2        | R/W: Read/Write Information bit                                                |                     |                |                  |                 |                 |               |  |  |  |  |  |

|              | Used in I <sup>2</sup> C mode only.                                            |                     |                |                  |                 |                 |               |  |  |  |  |  |

| bit 1        | UA: Update Address bit                                                         |                     |                |                  |                 |                 |               |  |  |  |  |  |

|              | Used in I <sup>2</sup> C mode only.                                            |                     |                |                  |                 |                 |               |  |  |  |  |  |

| bit 0        | BF: Buffer F                                                                   | Full Status bit (Re | eceive mode    | only)            |                 |                 |               |  |  |  |  |  |

|              |                                                                                | is complete, SS     |                |                  |                 |                 |               |  |  |  |  |  |

|              | 0 = Receive                                                                    | is not complete     | , SSPxBUF is   | sempty           |                 |                 |               |  |  |  |  |  |

| Note 1: F    | Polarity of clock                                                              | state is set by th  | ne CKP bit (S  | SPxCON1<4>).     |                 |                 |               |  |  |  |  |  |

|              | -                                                                              | •                   |                | ,                |                 |                 |               |  |  |  |  |  |

# REGISTER 27-1: SSPxSTAT: MSSPx STATUS REGISTER (SPI MODE)

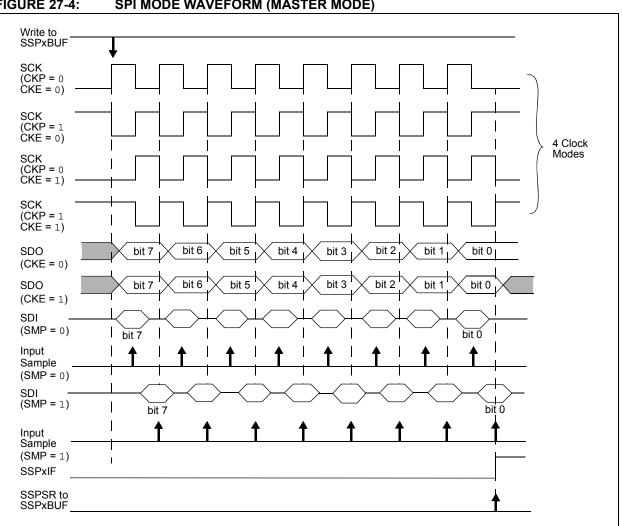

#### FIGURE 27-4: SPI MODE WAVEFORM (MASTER MODE)

#### 27.5.2 SPI SLAVE MODE

In Slave mode, the data is transmitted and received as external clock pulses appear on SCK. When the last bit is latched, the SSPxIF interrupt flag bit is set.

Before enabling the module in SPI Slave mode, the clock line must match the proper Idle state. The clock line can be observed by reading the SCK pin. The Idle state is determined by the CKP bit of the SSPxCON1 register.

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. The shift register is clocked from the SCK pin input and when a byte is received, the device will generate an interrupt. If enabled, the device will wake-up from Sleep.

#### 27.5.3 DAISY-CHAIN CONFIGURATION

The SPI bus can sometimes be connected in a daisy-chain configuration. The first slave output is connected to the second slave input, the second slave output is connected to the third slave input, and so on. The final slave output is connected to the master input. Each slave sends out, during a second group of clock pulses, an exact copy of what was received during the first group of clock pulses. The whole chain acts as one large communication shift register. The daisy-chain feature only requires a single Slave Select line from the master device.

Figure 27-5 shows the block diagram of a typical daisy-chain connection when operating in SPI mode.

In a daisy-chain configuration, only the most recent byte on the bus is required by the slave. Setting the BOEN bit of the SSPxCON3 register will enable writes to the SSPxBUF register, even if the previous byte has not been read. This allows the software to ignore data that may not apply to it.

© 2016-2017 Microchip Technology Inc.

| R/W-0            | R/W-0 | R/W-0              | R/W-0 | R/W-0          | R/W-0            | R/W-0          | R/W-0        |

|------------------|-------|--------------------|-------|----------------|------------------|----------------|--------------|

|                  |       |                    | ADD   | <7:0>          |                  |                |              |

| bit 7            |       |                    |       |                |                  |                | bit 0        |

|                  |       |                    |       |                |                  |                |              |

| Legend:          |       |                    |       |                |                  |                |              |

| R = Readable     | bit   | W = Writable b     | it    | U = Unimpler   | nented bit, read | 1 as '0'       |              |

| u = Bit is unch  | anged | x = Bit is unkno   | own   | -n/n = Value a | at POR and BO    | R/Value at all | other Resets |

| '1' = Bit is set |       | '0' = Bit is clear | red   |                |                  |                |              |

## **REGISTER 27-11:** SSPxADD: MSSP ADDRESS REGISTER (I<sup>2</sup>C MASTER MODE)

# Master mode: |<sup>2</sup>C mode

| bit 7-0 | Baud Rate Clock Divider bits <sup>(1)</sup>             |

|---------|---------------------------------------------------------|

|         | SCK/SCL pin clock period = ((SSPxADD<7:0> + 1) *4)/Fosc |

#### 10-Bit Slave mode – Most Significant Address Byte:

- bit 7-3 **Not used:** Unused for Most Significant Address Byte. Bit state of this register is a don't care. Bit pattern sent by master is fixed by I<sup>2</sup>C specification and must be equal to, '11110'. However, those bits are compared by hardware and are not affected by the value in this register.

- bit 2-1 ADD<9:8>: Two Most Significant bits of 10-bit Address

- bit 0 Not used: Unused in this mode. Bit state is a don't care.

#### 10-Bit Slave mode – Least Significant Address Byte:

bit 7-0 ADD<7:0>: Eight Least Significant bits of 10-bit Address

#### 7-Bit Slave mode:

bit 0 Not used: Unused in this mode. Bit state is a don't care.

**Note 1:** Values of 0x00, 0x01 and 0x02 are not valid for SSPxADD when used as a Baud Rate Generator for I<sup>2</sup>C. This is an implementation limitation.

#### REGISTER 27-12: SSPxMSK: MSSPx ADDRESS MASK REGISTER

| R/W-1   | R/W-1 | R/W-1 | R/W-1    | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|---------|-------|-------|----------|-------|-------|-------|-------|

|         |       |       | MSK<7:1> |       |       |       | MSK0  |

| bit 7   |       |       |          |       |       |       | bit 0 |

|         |       |       |          |       |       |       |       |

| Legend: |       |       |          |       |       |       |       |

| Legena:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

|                      |                      |                                                       |

| bit 7-1 | MSK<7:1>: Mask bits                                                                                                                                                                                          |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = The received address bit n is compared to SSPxADDn to detect I<sup>2</sup>C address match</li> <li>0 = The received address bit n is not used to detect I<sup>2</sup>C address match</li> </ul> |

| bit 0   | <b>MSK0:</b> Mask bit for I <sup>2</sup> C Slave mode, 10-bit Address<br>I <sup>2</sup> C Slave mode, 10-bit address (SSPM<3:0> = 0111 or 1111):                                                             |

|         | 1 =  The received address bit 0 is compared to SSPxADD0 to detect I <sup>2</sup> C address match                                                                                                             |

|         | 0 = The received address bit 0 is not used to detect I <sup>2</sup> C address match                                                                                                                          |

|         | I <sup>2</sup> C Slave mode, 7-bit address, the bit is ignored.                                                                                                                                              |

|         |                                                                                                                                                                                                              |

© 2016-2017 Microchip Technology Inc.

PIC18(L)F67K40

PIC18(L)F67K40

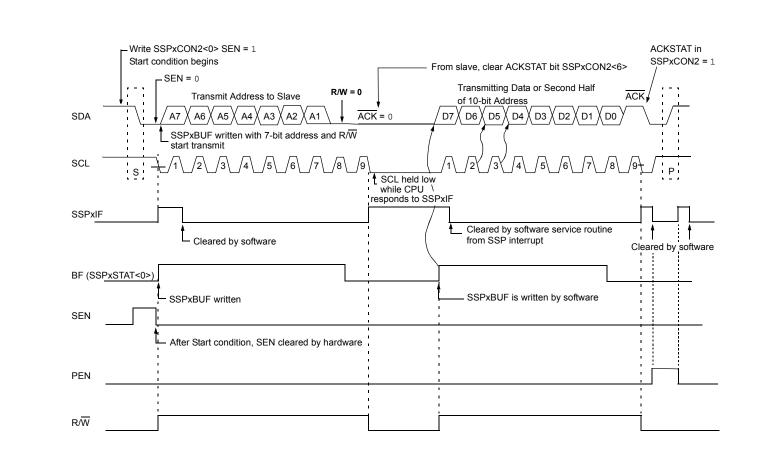

#### 27.10.10 SLEEP OPERATION

While in Sleep mode, the I<sup>2</sup>C slave module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSP interrupt is enabled).

#### 27.10.11 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

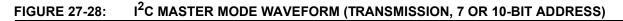

#### 27.10.12 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the I<sup>2</sup>C bus may be taken when the P bit of the SSPxSTAT register is set, or the bus is Idle, with both the S and P bits clear. When the bus is busy, enabling the SSP interrupt will generate the interrupt when the Stop condition occurs.

In multi-master operation, the SDA line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed by hardware with the result placed in the BCLxIF bit.

The states where arbitration can be lost are:

- · Address Transfer

- Data Transfer

- A Start Condition

- A Repeated Start Condition

- An Acknowledge Condition

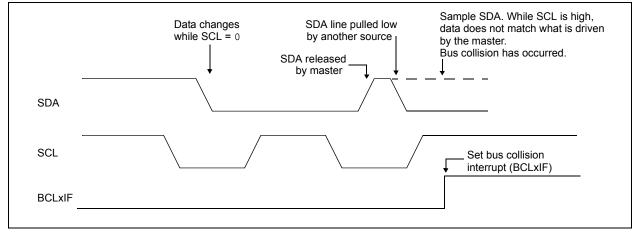

#### 27.10.13 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA, by letting SDA float high and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin is '0', then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLxIF and reset the I<sup>2</sup>C port to its Idle state (Figure 27-32).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are deasserted and the SSPxBUF can be written to. When the user services the bus collision Interrupt Service Routine and if the I<sup>2</sup>C bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are deasserted and the respective control bits in the SSPxCON2 register are cleared. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDA and SCL pins. If a Stop condition occurs, the SSPxIF bit will be set.

A write to the SSPxBUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPxSTAT register, or the bus is Idle and the S and P bits are cleared.

#### FIGURE 27-32: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

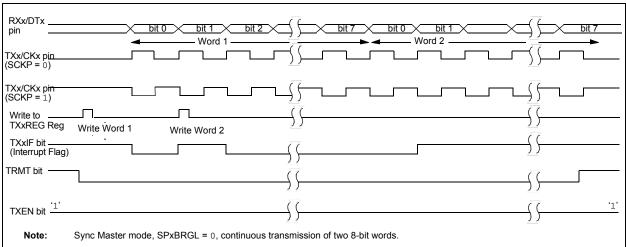

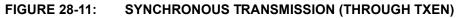

#### FIGURE 28-10: SYNCHRONOUS TRANSMISSION

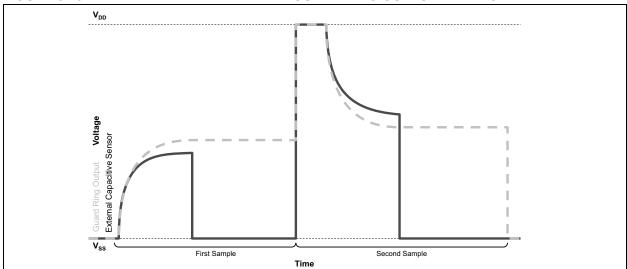

FIGURE 32-9: DIFFERENTIAL CVD WITH GUARD RING OUTPUT WAVEFORM

| Precharge<br>Time                                           | Conversion Time<br>(Traditional Timing of ADC Conversion)                                                |                |                                                                |    |    |                                                         |    |    |     |       |    |    |    |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------|----------------------------------------------------------------|----|----|---------------------------------------------------------|----|----|-----|-------|----|----|----|

| 1-255 TINST<br>(TPRE)                                       | 1-255 TINST<br>(TACQ)                                                                                    | <br>,TCY - TAE | TCY - TAD TAD1 TAD2 TAD3 TAD4 TAD5 TAD6 TAD7 TAD8 TAD9 TAD10 T |    |    |                                                         |    |    |     | Tad11 |    |    |    |

|                                                             |                                                                                                          | <b>Ì</b> ↑ _ 4 |                                                                | b9 | b8 | b7                                                      | b6 | b5 | b4  | b3    | b2 | b1 | b0 |

| External and Internal<br>Channels are<br>charged/discharged | Channels share                                                                                           |                |                                                                |    |    |                                                         |    |    | ıs) |       |    |    |    |

| If ADPRE ≠ 0                                                | If ADPRE = 0<br>If ADACQ = 0                                                                             |                |                                                                |    |    | On the following cycle:<br>AADRES0H:AADRES0L is loaded, |    |    |     |       |    |    |    |

| et GO/DONE bit                                              | (Traditional Operation Start) AADRESOH:AADRESOL is loaded,<br>ADIF bit is set,<br>GO/DONE bit is cleared |                |                                                                |    |    |                                                         |    |    |     |       |    |    |    |

# 32.4.5 ADDITIONAL SAMPLE AND HOLD CAPACITANCE

Additional capacitance can be added in parallel with the internal sample and hold capacitor (CHOLD) by using the ADCAP register. This register selects a digitally programmable capacitance which is added to the ADC conversion bus, increasing the effective internal capacitance of the sample and hold capacitor in the ADC module. This is used to improve the match between internal and external capacitance for a better sensing performance. The additional capacitance does not affect analog performance of the ADC because it is not connected during conversion. See Figure 32-11.

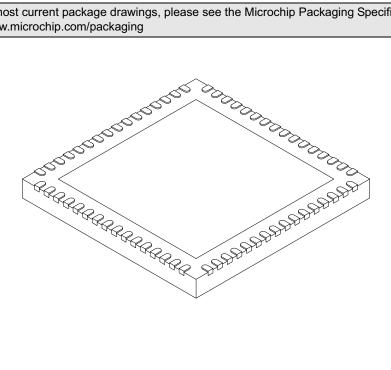

#### 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [QFN] With 7.15 x 7.15 Exposed Pad [QFN]

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Ν         | MILLIMETERS    |          |      |  |  |  |  |

|------------------------|-----------|----------------|----------|------|--|--|--|--|

| Dimensio               | on Limits | MIN            | NOM      | MAX  |  |  |  |  |

| Number of Pins         | N         |                | 64       |      |  |  |  |  |

| Pitch                  | е         |                | 0.50 BSC |      |  |  |  |  |

| Overall Height         | A         | 0.80 0.90 1.00 |          |      |  |  |  |  |

| Standoff               | A1        | 0.00           | 0.02     | 0.05 |  |  |  |  |

| Contact Thickness      | A3        |                | 0.20 REF |      |  |  |  |  |

| Overall Width          | E         |                | 9.00 BSC |      |  |  |  |  |

| Exposed Pad Width      | E2        | 7.05           | 7.15     | 7.50 |  |  |  |  |

| Overall Length         | D         |                | 9.00 BSC |      |  |  |  |  |

| Exposed Pad Length     | D2        | 7.05           | 7.15     | 7.50 |  |  |  |  |

| Contact Width          | b         | 0.18           | 0.25     | 0.30 |  |  |  |  |

| Contact Length         | L         | 0.30           | 0.40     | 0.50 |  |  |  |  |

| Contact-to-Exposed Pad | K         | 0.20           | -        | -    |  |  |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-149C Sheet 2 of 2