Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                             |

|--------------------------------|-----------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                    |

| Number of LABs/CLBs            | -                                                                           |

| Number of Logic Elements/Cells | 10368                                                                       |

| Total RAM Bits                 | 113664                                                                      |

| Number of I/O                  | 204                                                                         |

| Number of Gates                | 643000                                                                      |

| Voltage - Supply               | 1.425V ~ 3.6V                                                               |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | 0°C ~ 70°C (TA)                                                             |

| Package / Case                 | 484-BBGA                                                                    |

| Supplier Device Package        | 484-FPBGA (23x23)                                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/orso42g5-2bm484c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Support for OC-48 and OC-192 (in block OC-48) formats.

- · SONET framing, scrambling and SONET Mode channel alignment.

- Performance monitoring functions such as Bit Interleaved Parity (BIP-8) generation and checking and Out-Of-Frame (OOF) and Remote Defect Indication (RDI-L) detection.

- Cell Mode cell creation and extraction, idle cell insertion/deletion, destriping and striping functions.

- Additionally, there are two independent memory blocks in the core. Each embedded RAM block has a capacity of 4K words by 36 bits.

The ORSO42G5 and ORSO82G5 embedded cores contain, respectively, four-channel and eight-channel clock and data recovery macrocells and logical blocks performing functions such as SONET framing, scrambling/descrambling and cell processing. The channels each operate from 0.6 to 2.7 Gbps with per channel CDR functionality. The CDR interface enables high-speed asynchronous serial data transfer between system devices. Devices can be on the same PC-board, on separate boards connected across a backplane, or connected by cables. Figure 2 shows a top level block diagram of the backplane driver logic in the embedded core (embedded RAM not shown).

User or eight data channels Receive (RX) Path MUX/DEMUX and SERDES organized in two blocks Configurable ORCA 4E04 Psuedo-Cell **FPGA Logic** SONET Processing Configurable as four Processing Transmit (TX) Path I/O

Figure 2. Top Level Block Diagram ORSO42G5 and ORSO82G5 Embedded Cores

### ORSO42G5 and ORSO82G5 Main Operating Modes - Overview

The ORSO42G5 and ORSO82G5 support four and eight 0.6 to 2.7 Gbps serial data channels respectively, which can operate independently or can be combined together (aligned) to achieve higher bit rates. The mode of operation of the core is defined by a set of control registers, which can be written through the system bus interface. The status of the core is stored in a set of status registers, which can be read through the system bus interface.

The serial data channels support OC-48 rates on each channel. The standard OC-48 rate, 2.488 Gbits, is used as the nominal data rate for the technical discussions that follow. OC-192 is also supported but is transmitted and received in block OC-48 links. The scrambled data stream conforms to the GR-255 specified polynomial sequence of  $1+x^6+x^7$ .

There are three main operating modes in the ORSO42G5 and ORSO82G5 as described below:

- SERDES only (bypass) mode

- SONET mode

- Cell mode

- Two-link sub-mode

- Eight-link sub-mode (ORSO82G5 only)

**FPGA Logic Embedded Core** TCK78X Divide by 2 311MHz from Divide TCK156x Other Links by 2 in Block Divide TCK39x by 4 Logic Common to Block TSYSCLKx[A:D] 311MHz 77.76 MHz SYSCLK156x[1:2] Divide by 2 or SYSCLK156 87 Data **SERDES Cell Processing SONET Processing** from xck311 **FPGA** 600 Mb/s - 2.7 Gb/s 32:8 8 Payload OPC2/  $\mathsf{TX}$ TOH SONET MUX ö OPC8 Scrambler **FIFO** Block Block LDIN REFCLK (155.52MHz) nominal Line Key: Legend: SERDES-Only Mode -TCK39x SONET Mode TCK78x Cell Mode - - -TCK156x Cell/SONET or All Modes TSYSCLKx[A:D] x = A for Block A, B for Block B SYSCLK 156 8 (\*ORSO82G5 only)

Figure 3. Top Level Overview, TX Path Logic, Single Channel

#### **Receiver Architecture**

The receiver section receives high-speed serial data at the external differential CML input pins. These data are fed to the clock recovery section which generates a recovered clock and retimes the data. Therefore the receive clocks are asynchronous between channels. The data are then optionally framed, reformatted, aligned and passed to the FPGA logic in various parallel data formats.

The top level receiver architecture is shown in Figure 4. The main logical blocks in the receive path are:

- · Receive SERDES and 8:32 DEMUX.

- SONET processing logic.

- Input Port Controllers (IPCs) which contain the cell processing logic.

Depending on the mode of operation, the FPGA to backplane data path may include or bypass the various logical blocks.

The receive PLL has two modes of operation as follows: lock to reference and lock to data with retiming. The control bit LCKREFN\_xx selects the operating mode. When setup to lock to data and no data or invalid data are present on the HDINP and HDINN pins, the receive VCO will not lock to data and its frequency can drift outside of the nominal ±100 ppm range. Under this condition, the receive PLL will lock to REFCLK for a fixed time interval and then will attempt to lock to receive data. The process of attempting to lock to data, then locking to clock will repeat until valid input data exists. The default mode is lock to reference.

The recovered byte clock (RBC0) is only centered on the data when operating in the lock to data mode. In the lock to reference mode, RBC0 is not centered on the data and may not capture the correct byte value.

The SERDES receives MSB first and LSB last. Hence LDOUTx[7] is the bit that is received first and LDOUTx[0] is the bit that is received last.

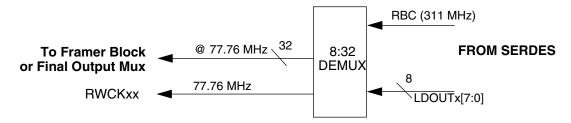

#### 8:32 **DEMUX**

The SERDES provides an eight bit data bus, and a clock, RBC0, which has a rising edge which occurs in the center of the valid data region. The DEMUX block will create one 32-bit data word from the single 8-bit bus. The DEMUX block will also provide a 77.76 MHz clock (divide-by-4 clock of RBC0) called RWCKxx to the rest of the logic blocks such as the framer, descrambler, cell extractor and FIFOs.

Figure 9. 8:32 DEMUX Block

In the DEMUX block, LDOUTx[7:0] is demultiplexed to a 32-bit data bus synchronous to the derived 77.76 MHz clock generated by dividing the 311.04 MHz clock by four. The 77.76 MHz clock is used by the remaining embedded blocks, as well as being fed to the FPGA. Receive data from the DEMUX block is unframed. Parallel data can be sent directly to the FPGA logic (SERDES only mode) or to the framer block for processing. Bit and byte alignment for the DEMUX block is shown in Figure 10.

#### **Supported Data Formats**

The ORSO42G5 and ORSO82G5 in the SONET mode support the following formats:

- Single OC-48 on each of the channels at a bit rate of 2.488 Gbps.

- OC-192 received in block OC-48 format on four channels at a combined rate of 9.952 Gbps.

The ORSO42G5 and ORSO82G5 SERDES will operate at the OC-12 rate of 622 MHz. For this rate, REFCLK is set to 77 MHz and the SERDES is used in half rate mode. However the embedded core SONET framing/processing logic is fixed at the OC-48 rate and therefore can not talk directly with standard STS-12 devices. In order to interoperate with standard STS-12 devices, the user must bypass the SONET functionality in the ORSO embedded core (SERDES-only mode) and implement all framing, TOH and scrambling/descrambling functionality in FPGA logic.

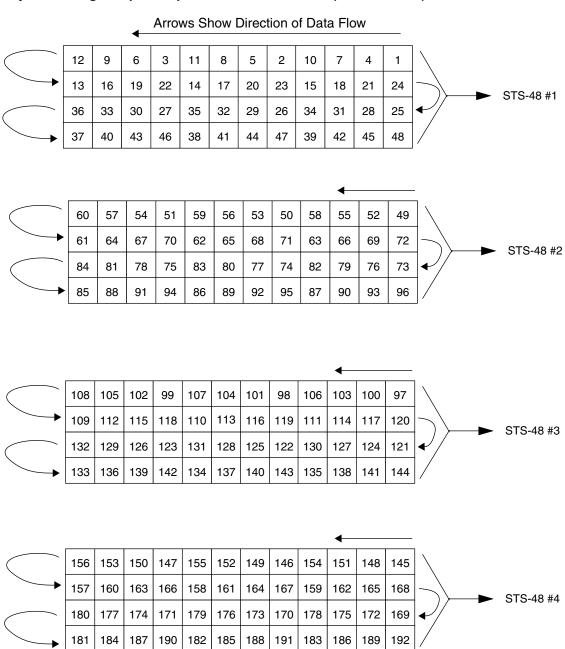

Figure 13 reveals the byte-ordering of the individual STS-48 streams. STS-192 is supported but it must be received in the block STS-48 format as shown in Figure 14. Each OC-48 stream is composed of byte-interleaved OC-1 data as described in GR-253 standard. Note that the SPE data is not touched by the core.

STS-192 in

block STS-48 format

Figure 14. Byte Ordering of Input/Output Interface in STS-192 (Block STS-48) Mode

DINxy\_FP Cell Mode DINxy[31:0] data Frame Pulse **FPGA INTERFACE** (SONET MODE) TX FRM PROC Error **PAYLOAD** injection **BLOCK** controls (control register bits) scramble\_disable 32-bit payload TRANSPORT scramble\_out (31:0) **SCRAMBLE** 32-bit TOH data **OVERHEAD BLOCK LOGIC** MUX **BLOCK** LDIN(7:0) XCK311 **SERDES INTERFACE**

Figure 16. TX Frame Processor (TFP) Block Diagram

#### **Payload Sub-block**

The Payload sub block is activated by the cell mode frame pulse (cell mode) or DINxx\_FP from FPGA (SONET mode). A pulse on this signal indicates the start of a frame.

In SONET mode, only two types of data bytes are in each frame:

- TOH bytes

- SPE data bytes

There are N x 3 (N = 48) bytes of TOH per row and there are a total of 9 rows in a SONET frame. The rest of the bytes in each row are SPE data bytes in SONET mode.

#### **TOH Sub-block**

This block is responsible formatting the 144 (48 x 3) bytes of TOH at the beginning of each row of the transport frame. All TOH bytes may be transmitted transparently from the FPGA logic using the transparent mode. Alternately, some or all TOH bytes may be inserted by the TOH block (AUTO\_SOH and AUTO\_TOH mode). The TOH data is transferred across the FPGA/core interface as 32-bit words, hence 36 clock cycles (12 x 3) are needed to transfer a TOH row. TOH insertion is controlled by software register bits as shown in the Register Map tables.

frame (or A1A2 framing bytes). This frame pulse is used to synchronize multiple channels within an alignment group.

If a channel is not in any alignment group, the FIFO control logic will set the FIFO-write-address to the beginning of the FIFO, and will set the FIFO-read-address to the middle of the FIFO at the first assertion of frame pulse after reset or after the resync command.

The RX\_FIFO\_MIN register bits can be used to control the threshold for minimum unused buffer space in the alignment FIFOs between read and write pointers before OVFL status is flagged. The synchronization algorithm consists of a down counter which starts to count down by 1 from its initial value of 18 (decimal) when a frame pulse from any channel within an alignment group has been received. The OOS alarm indicates the FIFO is out-of sync and the channel skew exceeds that which can be handled by the FIFO. Once the frame pulse for all channels within the alignment group have been received, the count is decremented by 2 until 0 is reached. Data are then read from the FIFOs and output to the SPE generator before being sent to the FPGA.

For every alignment group, there is an OVFL and OOS status register bit. The OOS bit is flagged when the down counter in the synchronization algorithm has reached a value of 0 and frame pulse from all channels within an alignment group have not been received. The OVFL bit is flagged when the read address at the time of receiving a frame pulse, is less than the minimum threshold set by RX\_FIFO\_MIN. In the memory map section OOS is referred to as SYNC[2,4]\_[A1,A2,B1,B2]\_OOS, SYNC8\_OOS. OVFL is referred to as SYNC[2,4]\_[A1,A2,B1,B2]\_OVFL, SYNC8\_OVFL.

### Receive Clocking for Multi-channel Alignment – ORSO82G5

There are a total of nine clocks for the receive path, from FPGA to the core. The four used in SONET mode are RSYSCLKA1 and RSYSCLKA2 (both for block A), and RSYSCLKB1 and RSYSCLKB2 (both for block B). The following diagrams show the recommended clock distribution approaches for SONET mode multi-channel alignment modes. Cell mode alignment is discussed in the section describing the Input Port Controller (IPC).)

#### **SONET Mode Twin Alignment**

Figure 27 describes the clocking scheme for twin alignment in the ORSO82G5. In twin alignment, the valid channel pairs are AA,AB and AC,AD in block A and BA,BB and BC,BD in block B. The figure provides the clocking scheme for block A as an example. RSYSCLKA1 should be sourced from RWCKAA or RWCKAB. RSYSCLKA2 should be sourced from RWCKAC or RWCKAD. This clocking approach provides the required 0 ppm clock frequency matching for each pair and provides flexibility in applications where the two pairs in the block are received from asynchronous sources or operate at different rates.

#### **ORSO42G5 Configuration**

At startup, the legacy SERDES channel logic must be powered down and removed from any multi-channel alignment groups:

- Setting bit 1 to one in registers at locations 30002, 30012, 30102 and 30112 powers down the legacy logic. (Note that the reset value for these bits is 0.)

- Setting bit 1 to zero (reset condition) in the register at locations 30802, 30812, 30902 and 30912 removes the legacy logic from any alignment group.

Register settings for SONET multi-channel alignment are shown in Table 7.

Table 7. Multichannel Alignment Modes - ORSO42G5

| Register Bits<br>FMPU_SYNMODE_xx[2:3] | Mode                      |

|---------------------------------------|---------------------------|

| 00                                    | No multichannel alignment |

| 01                                    | Twin channel alignment    |

| 11                                    | Four channel alignment    |

Note: xx = [AC,AD,BC,BD]

To align two channels in SERDES A:

- FMPU\_SYNMODE\_AC = 01 (Register Location 30822)

- FMPU\_SYNMODE\_AD = 01 (Register Location 30832)

To align two channels in SERDES B:

- FMPU SYNMODE BC = 01 (Register Location 30922)

- FMPU\_SYNMODE\_BD = 01 (Register Location 30932)

To align all four channels:

- FMPU\_SYNMODE\_AC = 11 (Register Location 30822)

- FMPU\_SYNMODE\_AD = 11 (Register Location 30832)

- FMPU\_SYNMODE\_BC = 11 (Register Location 30922)

- FMPU SYNMODE BD = 11 (Register Location 30932)

To enable/disable multi-channel alignment of individual channels within a multi-channel alignment group:

- FMPU STR EN xx = 1 enabled

- FMPU\_STR\_EN\_xx = 0 disabled

where xx = [AC,AD,BC,BD]

To resynchronize a multichannel alignment group set the following bits to one, and then set to zero:

- FMPU\_RESYNC4 for four channels, AC, AD, BC and BD. (Register Location 30A04, bit 7)

- FMPU\_RESYNCA2 for dual channels, AC and AD. (Register Location 30A04, bit 2)

- FMPU\_RESYNCB2 for dual channels, BC and BD. (Register Location 30A04, bit 5)

To resynchronize an independent channel (resetting the write and the read pointer of the FIFO) set the following bits to one, and then set to zero.

FMPU\_RESYNC1\_xx (Register Locations 30824, 20834, 30924 and 30934, bit 7) where xx is one of AC, AD, BC or BD.

### Alignment Mode Setup Procedures - ORSO82G5

The control register bits for alignment FIFO in the ORSO42G5 and ORSO82G5 are described below.

Table 8. Multichannel Alignment Modes – ORSO82G5

| Register Bits<br>FMPU_SYNMODE_xx | Mode                                 |

|----------------------------------|--------------------------------------|

| 00                               | No multichannel alignment. (default) |

| 01                               | Twin channel alignment               |

| 10                               | Block channel alignment              |

| 11                               | Eight channel alignment              |

Note: Where xx is one of A[A:D] and B[A:D].

### To align all eight channels:

- FMPU\_SYNMODE\_A[A:D] = 11

- FMPU\_SYNMODE\_B[A:D] = 11

### To align twin channels in SERDES A:

• FMPU\_SYNMODE\_A[A:D] = 01

#### To align four channels in SERDES A:

- FMPU SYNMODE AB = 10

- FMPU\_SYNMODE\_AD = 10

Similar alignment can be defined for SERDES B. To enable/disable synchronization signal of individual channel within a multi-channel alignment group:

- FMPU\_STR\_EN\_xx = 1 enabled

- FMPU\_STR\_EN\_xx = 0 disabled where xx is one of A[A:D] and B[A:D].

### To re-synchronize a multi-channel alignment group

Set the following bit to zero, and then set it to 1 since it is a rising edge sensitive bit.

- FMPU RESYNC8 for eight channel A[A:D] and B[A:D]

- FMPU\_RESYNC4A for block channel A[A:D]

- FMPU\_RESYNC2A1 for twin channel A[A:B]

- FMPU\_RESYNC2A2 for twin channel A[C:D]

- FMPU RESYNC4B for block channel B[A:D]

Re-synchronization will cause the multi-channel alignment group to perform a new synchronization procedure. This would need to occur if a link is removed from an alignment group and then paced back into service as part of the alignment group. This is not required at power up if the alignment mode is set before the channels receive the first frame pulse.

Table 28. Common Control Register Descriptions – ORSO42G5

| (0x)<br>Absolute<br>Address | Bit   | Name              | Reset<br>Value<br>(0x) | Description                                                                                                                                                                                                                                                                                                                                              | Mode  |

|-----------------------------|-------|-------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 30A00                       | [0:1] | RCKSELB           |                        | "10" - Channel BC source for clock RCK78B<br>"11" - Channel BD source for clock RCK78B                                                                                                                                                                                                                                                                   | Both  |

|                             | [2:3] | TCKSELB           | 00                     | "10" - Channel BC source for clock TCK78B<br>"11" - Channel BD source for clock TCK78B                                                                                                                                                                                                                                                                   | Both  |

|                             | [4:5] | RCKSELA           |                        | "10" - Channel AC source for clock RCK78A<br>"11" - Channel AD source for clock RCK78A                                                                                                                                                                                                                                                                   | Both  |

|                             | [6:7] | TCKSELA           |                        | "10" - Channel AC source for clock TCK78A "11" - Channel AD source for clock TCK78A                                                                                                                                                                                                                                                                      | Both  |

|                             | [0:2] | CELL_SIZE         |                        | Cell Size, Three bits to set cell size.  "000" - Cell size is 75 bytes,  "001" - Cell size is 79 bytes,  "010" - Cell size is 83 bytes,  "011" - Cell size is 91 bytes  These are the only supported cell sizes.                                                                                                                                         | Cell  |

| 30A01                       | [3:7] | RX_FIFO_MIN       | 00                     | Set Minimum threshold value for alignment FIFO in SONET mode. When the read address for the FIFO is below this value at the time when write address is zero, it indicates that the FIFO is near overflow. This event will go high only once during a frame when a framing byte has been detected by the aligner. The default threshold value is "00000". | SONET |

| 30A02                       | 0     | TX_DISABLE_ON_RDI | 00                     | Transmitter Disable on RDI (Detection), If TX_DISABLE_ON_RDI = 1 - No cell data is transmitted on a link in which a RDI has been detected by the corresponding link's receiver. If this bit is set to 0, cell data will be transmitted on a link irrespective of detection of a RDI.                                                                     | Cell  |

|                             | [1:7] | RSVD              |                        | Reserved                                                                                                                                                                                                                                                                                                                                                 | _     |

Table 28. Common Control Register Descriptions – ORSO42G5 (Continued)

| (0x)<br>Absolute | D.:   |                 | Reset<br>Value | B                                                                                                                                                                                                                                                                                                                                                                                        |       |

|------------------|-------|-----------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Address          | Bit   | Name            | (0x)           | Description                                                                                                                                                                                                                                                                                                                                                                              | Mode  |

|                  | [0]   | NO_TX_RDI_EXSEQ |                | Not Transmission of RDI, If NO_TX_RDI_EXSEQ = 1, a transmit link will not send data if its corresponding receive link is not good due to excessive sequence errors. If this bit is set to 0, a transmit link will still send data even if its corresponding receive link has excessive sequence errors. This bit should always be set during simulation and in SONET mode.               | Both  |

| 30A03            | [1]   | [1] AUTO_BUNDLE |                | Automatic (Link) Bundle, AUTO_BUNDLE = 1 allows a link within a link group to remain active even when another link within that group is defective. Cell data from all links within that group will continue to be sent to the FPGA. If this bit is set to 0, then all links within a link group must be good before cell data are read from the links by the IPC and passed to the FPGA. | Cell  |

|                  | [2]   | RSVD            |                | Reserved                                                                                                                                                                                                                                                                                                                                                                                 | _     |

|                  | [3]   | REJOIN_A        | 00             | Link Rejoin, REJOIN = 1 forces any link in a SERDES block to reassert a "RX link good" signal automatically when three consecutive sequence numbers are correct on that link.                                                                                                                                                                                                            | Cell  |

|                  | [4]   | AUTO_REMOVE_A   |                | Automatic (Link) Remove, AUTO_REMOVE = 1 indicates that any link in a SERDES block which sees three excessive sequence errors should deassert the "RX link good" signal which will cause the link to be inactive.                                                                                                                                                                        | Cell  |

|                  | [5]   | RSVD            |                | Reserved                                                                                                                                                                                                                                                                                                                                                                                 |       |

|                  | [6]   | REJOIN_B        |                | Link Rejoin, REJOIN = 1 forces any link in a SERDES block to reassert a "RX link good" signal automatically when three consecutive sequence numbers are correct on that link.                                                                                                                                                                                                            | Cell  |

|                  | [7]   | AUTO_REMOVE_B   |                | AUTO_REMOVE_B = 1 indicates that any link in SERDES block B which sees three excessive sequence errors should deassert the "RX link good" signal which will cause the link to be inactive.                                                                                                                                                                                               | Cell  |

|                  | [0:1] | RSVD            |                | Reserved                                                                                                                                                                                                                                                                                                                                                                                 | _     |

|                  | [2]   | FMPU_RESYNC2_B2 |                | Control to resync channels BC and BD which have been configured for multi channel alignment in SONET mode in block B. Requires a rising edge on this bit. Write a 0 followed by a 1.                                                                                                                                                                                                     | SONET |

|                  | [3:4] | RSVD            | ]              | Reserve                                                                                                                                                                                                                                                                                                                                                                                  | SONET |

| 30A04            | [5]   | FMPU_RESYNC2_A2 | 00             | Control to resync channels AC and AD which have been configured for multi channel alignment in SONET mode in block A. Requires a rising edge on this bit. Write a 0 followed by a 1.                                                                                                                                                                                                     | SONET |

|                  | [6]   | RSVD            |                | Reserved                                                                                                                                                                                                                                                                                                                                                                                 | SONET |

|                  | [7]   | FMPU_RESYNC4    |                | Control to resync all four channels which have been configured for multi channel alignment.                                                                                                                                                                                                                                                                                              | SONET |

Table 34. Per-Channel Control Register Descriptions – ORSO82G5 (Continued)

| (0x)<br>Absolute<br>Address                          | Bit   | Name           | Reset<br>Value<br>(0x) | Description                                                                                                                                                        | Mode   |

|------------------------------------------------------|-------|----------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

|                                                      | [0:5] | RSVD           |                        | Reserved                                                                                                                                                           |        |

| 30806 - AA<br>30816 - AB<br>30826 - AC<br>30836 - AD | [6]   | [6] AUTO_B1_xx | 00                     | AUTO_B1_xx = 0, B1 is not inserted by the embedded core AUTO_B1_xx = 1, B1 is calculated and inserted by the embedded core AUTO_TOH_xx = 1 overrides this bit      | - Both |

| 30906 - BA<br>30916 - BB<br>30926 - BC<br>30936 - BD | [7]   | AUTO_A1A2_xx   |                        | AUTO_A1A2_xx = 0, A1/A2 bytes are not inserted by the embedded core AUTO_A1A2_xx = 1, A1/A2 bytes inserted by the embedded core AUTO_TOH_xx = 1 overrides this bit |        |

# Table 35. Per-Channel Status Register Descriptions – ORSO82G5

| (0x)<br>Absolute<br>Address                                                                                  | Bit       | Name                         | Reset<br>Value<br>(0x) | Description                                                                                                                                                                                                                                                                                                             | Mode |

|--------------------------------------------------------------------------------------------------------------|-----------|------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Channel Status                                                                                               | s Registe | ers (Read Only) xx = [AA,,BD | )]                     |                                                                                                                                                                                                                                                                                                                         |      |

|                                                                                                              | [0:4]     | RSVD                         |                        | Reserved                                                                                                                                                                                                                                                                                                                | _    |

| 30808 - AA<br>30818 - AB<br>30828 - AC<br>30838 - AD<br>30908 - BA<br>30918 - BB<br>30928 - BC<br>30938 - BD | [5]       | CELL_ALIGN_ERR_xx            |                        | Cell Alignment Error, CELL_ALIGN_ERR = 1 indicates that the internal transmit frame processor did not detect a start of cell indicator when it was expecting a new cell. If the corresponding alarm enable bit has been set, a 1 on this bit will cause an alarm.                                                       | Cell |

|                                                                                                              | [6]       | TX_URUN_ERR_xx               | 00                     | Transmit Underrun Error, TX_URUN_ERR = 1 indicates an underrun error in the transmit Asynchronous FIFO. If the corresponding alarm enable bit has been set, a 1 on this bit will cause an alarm.                                                                                                                        | Cell |

|                                                                                                              | [7]       | TX_ORUN_ERR_xx               |                        | Transmit Overrun Error, TX_ORUN_ERR = 1 indicates an overrun error in the transmit Asynchronous FIFO. The TX FIFO is designed to not overflow since it sends backpressure signal to the FPGA when it cannot accept more cells. If the corresponding alarm enable bit has been set, a 1 on this bit will cause an alarm. | Cell |

Table 36. Common Control Register Descriptions – ORSO82G5 (Continued)

| (0x)<br>Absolute |       |                    | Reset<br>Value |                                                                                                                                                                                                  |       |

|------------------|-------|--------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Address          | Bit   | Name               | (0x)           | Description                                                                                                                                                                                      | Mode  |

| 30A0D            | [0]   | SYNC4_B_OVFL       |                | Reserved  SYNC8_OOS = 1 indicates that the alignment FIFO(s) in the links in block B are near overflow (i.e., at the time of writing into address 0, the read address was less than RX_FIFO_MIN) | SONET |

|                  | [2]   | SYNC2_B2_OVFL      |                | SYNC2_B2_OVFL = 1 indicates that the alignment FIFO(s) in the links BC and BD are near overflow (i.e., at the time of writing into address 0, the read address was less than RX_FIFO_MIN)        | SONET |

|                  | [3]   | SYNC2_B1_OVFL      |                | SYNC2_B1_OVFL = 1 indicates that the alignment FIFO(s) in the links BA and BB are near overflow (i.e., at the time of writing into address 0, the read address was less than RX_FIFO_MIN)        | SONET |

|                  | [4]   | SYNC4_A_OVFL       | 00             | SYNC4_A_OVFL = 1 indicates that the alignment FIFO(s) in the links in block A are near overflow (i.e., at the time of writing into address 0, the read address was less than RX_FIFO_MIN)        | SONET |

|                  | [5]   | SYNC2_A2_OVFL      |                | SYNC2_A2_OVFL = 1 indicates that the alignment FIFO(s) in the links AC and AD are near overflow (i.e., at the time of writing into address 0, the read address was less than RX_FIFO_MIN)        | SONET |

|                  | [6]   | SYNC2_A1_OVFL      |                | SYNC2_A1_OVFL = 1 indicates that the alignment FIFO(s) in the links AA and AB are near overflow (i.e., at the time of writing into address 0, the read address was less than RX_FIFO_MIN)        | SONET |

|                  | [7]   | SYNC8_OVFL         |                | SYNC8_OVFL = 1 Indicates that the alignment FIFO(s) in eight-links are near overflow (At the time of writing into address 0, the read address was less than RX_FIFO_MIN)                         | SONET |

|                  | [0:2] | RSVD               |                | Reserved                                                                                                                                                                                         | _     |

|                  | [3]   | BDL_ALIGN_ERR_B2   |                | Alignment Error, BDL_ALIGN_ERR = 1 indicates that an alignment error has occurred in the link group pairs BC and BD                                                                              | Cell  |

|                  | [4]   | BDL_ALIGN_ERR_B1   |                | Alignment Error, BDL_ALIGN_ERR = 1 indicates that an alignment error has occurred in the link group pairs BA and BB                                                                              | Cell  |

| 30A0E            | [5]   | BDL_ALIGN_ERR_A2   | 00             | Alignment Error, BDL_ALIGN_ERR = 1 indicates that an alignment error has occurred in the link group pairs AC and AD                                                                              | Cell  |

|                  | [6]   | BDL_ALIGN_ERR_A1   |                | Alignment Error, BDL_ALIGN_ERR = 1 indicates that an alignment error has occurred in the link group pairs AA and AB                                                                              | Cell  |

|                  | [7]   | BDL_ALIGN_ERR_ALL8 |                | BDL_ALIGN_ERR_ALL8 = 1 -indicates that an alignment error has occurred in cell group of all eight-links                                                                                          | Cell  |

Table 47. Pin Descriptions (Continued)

| Symbol                     | I/O | Description                                                                                                                                                                                                                                 |

|----------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MPI_ACK                    | 0   | In MPI mode this is driven low indicating the MPI received the data on the write cycle or returned data on a read cycle.                                                                                                                    |

|                            | I/O | If not used for MPI these pins are user-programmable I/O pins after configuration.1                                                                                                                                                         |

| MPI_CLK                    | I   | This is the PowerPC synchronous, positive-edge bus clock used for the MPI interface. It can be a source of the clock for the Embedded System Bus. If MPI is used this will be the AMBA bus clock.                                           |

|                            | I/O | If not used for MPI these pins are user-programmable I/O pins after configuration.1                                                                                                                                                         |

| MPI_TEA                    | 0   | A low on the MPI transfer error acknowledge indicates that the MPI detects a bus error on the internal system bus for the current transaction.                                                                                              |

|                            | I/O | If not used for MPI these pins are user-programmable I/O pins after configuration.1                                                                                                                                                         |

| MPI_RTRY                   | 0   | This pin requests the MPC860 to relinquish the bus and retry the cycle.                                                                                                                                                                     |

|                            | I/O | If not used for MPI these pins are user-programmable I/O pins after configuration.1                                                                                                                                                         |

| D[0:31]                    | I/O | Selectable data bus width from 8, 16, 32-bit in MPI mode. Driven by the bus master in a write transaction and driven by MPI in a read transaction.                                                                                          |

|                            | I   | D[7:0] receive configuration data during master parallel, peripheral, and slave parallel configuration modes when $\overline{\text{WR}}$ is low and each pin has a pull-up enabled. During serial configuration modes, D0 is the DIN input. |

|                            | 0   | D[7:3] output internal status for asynchronous peripheral mode when $\overline{RD}$ is low.                                                                                                                                                 |

|                            | I/O | After configuration, if MPI is not used, the pins are user-programmable I/O pins.1                                                                                                                                                          |

| DP[0:3]                    | I/O | Selectable parity bus width in MPI mode from 1, 2, 4-bit, DP[0] for D[0:7], DP[1] for D[8:15], DP[2] for D[16:23], and DP[3] for D[24:31].  After configuration, if MPI is not used, the pins are user-programmable I/O pin. <sup>1</sup>   |

| DIN                        | I   | During slave serial or master serial configuration modes, DIN accepts serial configuration data synchronous with CCLK. During parallel configuration modes, DIN is the D0 input. During configuration, a pull-up is enabled.                |

|                            | I/O | After configuration, this pin is a user-programmable I/O pin.1                                                                                                                                                                              |

| DOUT                       | 0   | During configuration, DOUT is the serial data output that can drive the DIN of daisy-chained slave devices. Data out on DOUT changes on the rising edge of CCLK.                                                                            |

|                            | I/O | After configuration, DOUT is a user-programmable I/O pin.1                                                                                                                                                                                  |

| TESTCFG<br>(ORSO82G5 only) | I   | During configuration this pin should be held high, to allow configuration to occur. A pull up is enabled during configuration.                                                                                                              |

|                            | I/O | After configuration, TESTCFG is a user programmable I/O pin.1                                                                                                                                                                               |

<sup>1.</sup> The FPGA States of Operation section in the ORCA Series 4 FPGAs data sheet contains more information on how to control these signals during start-up. The timing of DONE release is controlled by one set of bit stream options, and the timing of the simultaneous release of all other configuration pins (and the activation of all user I/Os) is controlled by a second set of options.

Table 51. ORSO42G5 484-pin PBGAM Pinout (Continued)

| 484-PBGAM | VDDIO Bank | VREF Group | I/O     | Pin Description | Additional Function | 484-PBGAM |

|-----------|------------|------------|---------|-----------------|---------------------|-----------|

| P17       | -          | -          | VDD_ANA | VDD_ANA         | -                   | -         |

| G20       | -          | -          | VDDIB   | VDDIB_AC        | -                   | -         |

| P18       | -          | -          | VDD_ANA | VDD_ANA         | -                   | -         |

| P19       | -          | -          | VDD_ANA | VDD_ANA         | -                   | -         |

| T17       | -          | -          | VDD_ANA | VDD_ANA         | -                   | -         |

| T18       | -          | -          | VDD_ANA | VDD_ANA         | -                   | -         |

| R17       | -          | _          | VSS     | VSS             | -                   | -         |

| G21       | -          | _          | I       | REFCLKP_A       | -                   | HSP_10    |

| G22       | -          | _          | l       | REFCLKN_A       | -                   | HSN_10    |

| F21       | -          | -          | 0       | REXTN_A         | -                   | -         |

| F22       | -          | -          | 0       | REXT_A          | -                   | -         |

| U18       | -          | -          | VDD_ANA | VDD_ANA         | -                   | -         |

| E21       | _          | _          | VDDGB_A |                 |                     | _         |

| E22       | _          | _          | VSS     | VSS             | -                   | _         |

| D21       | _          | _          | 0       | PSYS_RSSIG_ALL  |                     | -         |

| D22       | _          | _          | ı       | PSYS_DOBISTN    |                     | _         |

| D20       | _          | _          | VDD33   | VDD33           |                     | _         |

| K15       | _          | -          | VDD15   | VDD15           | -                   | -         |

| K10       | -          | -          | VSS     | VSS             | -                   | -         |

| L7        | _          | _          | VDD15   | VDD15           |                     | _         |

| D19       | _          | -          | I       | PBIST_TEST_ENN  | -                   | -         |

| D18       | -          | _          | l l     | PLOOP_TEST_ENN  | <u> </u>            | -         |

| L15       | _          | _          | VDD15   | VDD15           |                     | _         |

| E17       | _          | -          | I       | PASB_PDN        | -                   | -         |

| K11       | _          | _          | VSS     | VSS             |                     | _         |

| D17       | _          | _          | VDD33   | VDD33           |                     | _         |

| M7        | _          | _          | VDD15   | VDD15           | -                   | _         |

| C21       | _          | _          | 1       | PASB_RESETN     |                     |           |

| C22       | _          | _          | ı       | PASB_TRISTN     | -                   | _         |

| K12       | _          | _          | VSS     | VSS             |                     |           |

| E16       | _          | _          | I       | PASB_TESTCLK    | <u> </u>            | _         |

| M15       | -          | -          | VDD15   | VDD15           | -                   | _         |

| C17       | -          | -          | VDD33   | VDD33           | -                   | -         |

| D16       | 1 (TC)     | 7          | 10      | PT36D           | -                   | -         |

| C16       | 1 (TC)     | 7          | 10      | PT36B           | -                   | -         |

| F14       | 1 (TC)     | 7          | 10      | PT35D           | -                   | -         |

| F15       | 1 (TC)     | 7          | 10      | PT35B           | -                   | -         |

| E14       | 1 (TC)     | 7          | IO      | PT34D           | VREF_1_07           | -         |

| E15       | 1 (TC)     | 8          | 10      | PT34B           | -                   | -         |

| D15       | 1 (TC)     | 8          | 10      | PT33D           | -                   | L53C      |

| C15       | 1 (TC)     | 8          | 10      | PT33C           | VREF_1_08           | L53T      |

| E12       | 1 (TC)     | -          | VDDIO1  | VDDIO1          | -                   | -         |

| C18       | 1 (TC)     | 8          | IO      | PT32D           | -                   | L54C      |

| C19       | 1 (TC)     | 8          | 10      | PT32C           |                     | L54T      |

Table 51. ORSO42G5 484-pin PBGAM Pinout (Continued)

| 484-PBGAM | VDDIO Bank | VREF Group | I/O | Pin Description | Additional Function | 484-PBGAM |

|-----------|------------|------------|-----|-----------------|---------------------|-----------|

| M10       | -          | -          | VSS | VSS             | -                   | -         |

| M11       | -          | -          | VSS | VSS             | -                   | -         |

| M12       | -          | -          | VSS | VSS             | -                   | -         |

| M13       | -          | -          | VSS | VSS             | -                   | -         |

| M14       | -          | -          | VSS | VSS             | -                   | -         |

| N8        | -          | -          | VSS | VSS             | -                   | -         |

| N9        | -          | -          | VSS | VSS             | -                   | -         |

| N10       | -          | -          | VSS | VSS             | -                   | -         |

| N11       | -          | -          | VSS | VSS             | -                   | -         |

| N12       | -          | -          | VSS | VSS             | -                   | -         |

| N13       | -          | -          | VSS | VSS             | -                   | -         |

| N14       | -          | -          | VSS | VSS             | -                   | -         |

| P7        | -          | -          | VSS | VSS             | -                   | -         |

| P8        | -          | -          | VSS | VSS             | -                   | -         |

| P9        | -          | -          | VSS | VSS             | -                   | -         |

| P10       | -          | -          | VSS | VSS             | -                   | -         |

| P11       | -          | -          | VSS | VSS             | -                   | -         |

| P12       | -          | -          | VSS | VSS             | -                   | -         |

| P13       | -          | -          | VSS | VSS             | -                   | -         |

| P14       | -          | -          | VSS | VSS             | -                   | -         |

| R7        | -          | -          | VSS | VSS             | -                   | -         |

| R8        | -          | -          | VSS | VSS             | -                   | -         |

| R9        | -          | -          | VSS | VSS             | -                   | -         |

| R10       | -          | -          | VSS | VSS             | -                   | -         |

| R11       | -          | -          | VSS | VSS             | -                   | -         |

| R12       | -          | -          | VSS | VSS             | -                   | -         |

| R13       | -          | -          | VSS | VSS             | -                   | -         |

| R14       | -          | -          | VSS | VSS             | -                   | -         |

| AA1       | -          | -          | VSS | VSS             | -                   | -         |

| AA19      | -          | -          | VSS | VSS             | -                   | -         |

| AA20      | -          | -          | VSS | VSS             | -                   | -         |

| AA21      | -          | -          | VSS | VSS             | -                   | -         |

| AA22      | -          | -          | VSS | VSS             | -                   | -         |

| AB1       | -          | -          | VSS | VSS             | -                   | -         |

| AB19      | -          | -          | VSS | VSS             | -                   | -         |

| AB20      | -          | -          | VSS | VSS             | -                   | -         |

| AB21      | -          | -          | VSS | VSS             | -                   | -         |

| AB22      | -          | -          | VSS | VSS             | -                   | -         |

Table 52. ORSO82G5 680-Pin PBGAM (fpBGA) Pinout (Continued)

| W31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 680-PBGAM | VDDIO Bank | VREF Group | I/O     | Pin Description | Additional Function | 680-PBGAM |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------|------------|---------|-----------------|---------------------|-----------|

| W33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | W31       | _          | _          | Vss     | Vss             | _                   | _         |

| H33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | V30       | _          | _          | VDDOB   | VDDOB_BD        | _                   | _         |

| W34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | W33       | _          | _          | 0       | HDOUTN_BD       | _                   | _         |

| V31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | H33       | _          | _          | Vss     | Vss             | _                   | _         |

| H34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | W34       | _          | _          | 0       | HDOUTP_BD       | _                   | _         |

| J32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | V31       | _          | _          | VDDOB   | VDDOB_BD        | _                   | _         |

| U31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | H34       | _          | _          | Vss     | Vss             | _                   | _         |

| T34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | J32       | _          | _          | Vss     | Vss             | _                   | _         |

| M32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | U31       | _          | _          | VDDOB   | VDDOB_AD        | _                   | _         |

| T33         —         —         O         HDOUTN_AD         —         —           U30         —         —         VDDOB         VDDOB_AD         —         —           T31         —         —         VSS         VSS         —         —           R34         —         —         I         HDINP_AD         —         —         —           N32         —         —         VSS         VSS         —         —         —           R33         —         —         I         HDINN_AD         —         —         —           T30         —         —         VDDIB         VDDIB_AD         —         —         —         —           U32         —         —         VSS         VSS         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —                                                                                                                       | T34       | _          | _          | 0       | HDOUTP_AD       | _                   | _         |

| U30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | M32       | _          | _          | Vss     | Vss             | _                   | _         |

| T31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | T33       | _          | _          | 0       | HDOUTN_AD       | _                   | _         |

| R34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | U30       | _          | _          | VDDOB   | VDDOB_AD        | _                   | _         |

| N32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | T31       | _          | _          | Vss     | Vss             | _                   | _         |

| R33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R34       | _          | _          | I       | HDINP_AD        | _                   | _         |

| T30         —         VDDIB         VDDIB_AD         —         —           U32         —         VSS         VSS         —         —           R31         —         —         VDDOB         VDDOB_AC         —         —           P34         —         —         O         HDOUTP_AC         —         —           U33         —         —         VSS         VSS         —         —           P33         —         —         O         HDOUTN_AC         —         —           R30         —         —         VDDOB         VDDOB_AC         —         —           P31         —         —         VSS         VSS         —         —           N34         —         —         I         HDINP_AC         —         —         —           N33         —         —         I         HDINP_AC         —         —         —         —           N33         —         —         I         HDINN_AC         —         —         —         —         —         —         —         —         —         —         —         —         —         —         — <td< td=""><td>N32</td><td>_</td><td>_</td><td>Vss</td><td>Vss</td><td>_</td><td>_</td></td<>                                     | N32       | _          | _          | Vss     | Vss             | _                   | _         |