Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

-XF

| 2 0 0 0 0 0                |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                           |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-UQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f24k42-e-mv |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 8.13 Power Control (PCON0/PCON1) Register

The Power Control (PCON0/PCON1) register contains flag bits to differentiate between a:

- Brown-out Reset (BOR)

- Power-on Reset (POR)

- Reset Instruction Reset (RI)

- MCLR Reset (RMCLR)

- Watchdog Timer Reset (RWDT)

- Watchdog Window Violation (WDTWV)

- Stack Underflow Reset (STKUNF)

- Stack Overflow Reset (STKOVF)

- Memory Violation Reset (MEMV)

The PCON0/1 register bits are shown in Register 8-2 and Register 8-3. Hardware will change the corresponding register bit during the Reset process; if the Reset was not caused by the condition, the bit remains unchanged (Table 8-3).

Software should reset the bit to the inactive state after restart (hardware will not reset the bit). Software may also set any PCON0 bit to the active state, so that user code may be tested, but no Reset action will be generated.

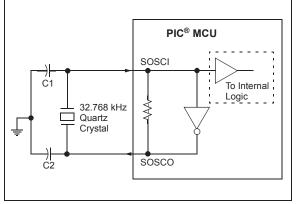

### 9.2.1.5 Secondary Oscillator

The secondary oscillator is a separate oscillator block that can be used as an alternate system clock source. The secondary oscillator is optimized for 32.768 kHz, and can be used with an external crystal oscillator connected to the SOSCI and SOSCO device pins, or an external clock source connected to the SOSCIN pin. The secondary oscillator can be selected during run-time using clock switching. Refer to **Section 9.3 "Clock Switching"** for more information.

Two power modes are available for the secondary oscillator. These modes are selected with the SOSCPWR (OSCCON3<6>). Clearing this bit selects the lower Crystal Gain mode which provides lowest microcontroller power consumption. Setting this bit enables a higher Gain mode to support faster crystal start-up or crystals with higher ESR.

### FIGURE 9-5: QUARTZ CRYSTAL OPERATION (SECONDARY OSCILLATOR)

### Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- 2: Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Application Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for PIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PIC<sup>®</sup> Oscillator Design" (DS00849)

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

- TB097, "Interfacing a Micro Crystal MS1V-T1K 32.768 kHz Tuning Fork Crystal to a PIC16F690/SS" (DS91097)

- AN1288, "Design Practices for Low-Power External Oscillators" (DS01288)

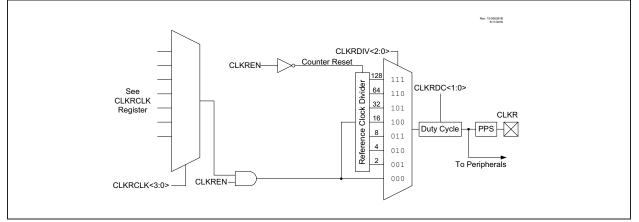

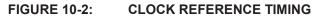

## 10.0 REFERENCE CLOCK OUTPUT MODULE

The reference clock output module provides the ability to send a clock signal to the clock reference output pin (CLKR). The reference clock output can also be used as a signal for other peripherals, such as the Data Signal Modulator (DSM), Memory Scanner and Timer module.

The reference clock output module has the following features:

- Selectable clock source using the CLKRCLK register

- Programmable clock divider

- · Selectable duty cycle

### 11.5 Context Saving

The Interrupt controller supports a two-level deep context saving (Main routine context and Low ISR context). Refer to state machine shown in Figure 11-6 for details.

The Program Counter (PC) is saved on the dedicated device PC stack. CPU registers saved include STATUS, WREG, BSR, FSR0/1/2, PRODL/H and PCLATH/U.

After WREG has been saved to the context registers, the resolved vector number of the interrupt source to be serviced is copied into WREG. Context save and restore operation is completed by the interrupt controller based on current state of the interrupts and the order in which they were sent to the CPU.

Context save/restore works the same way in both states of MVECEN. When IPEN = 0, there is only one level interrupt active. Hence, only the main context is saved when an interrupt is received.

### 11.5.1 ACCESSING SHADOW REGISTERS

The Interrupt controller automatically saves the context information in the shadow registers available in Bank 56. Both the saved context values (i.e., main routine and low ISR) can be accessed using the same set of shadow registers. By clearing the SHADLO bit in the SHADCON register (Register 11-43), the CPU register values saved for main routine context can accessed, and by setting the SHADLO bit of the CPU register, values saved for low ISR context can accessed. Low ISR context is automatically restored to the CPU registers upon exiting the high ISR. Similarly, the main context is automatically restored to the CPU registers upon exiting the low ISR.

The Shadow registers in Bank 56 are readable and writable, so if the user desires to modify the context then the corresponding shadow register should be modified and the value will be restored when exiting the ISR. Depending on the user's application, other registers may also need to be saved.

| U-0          | U-0                | R/W/HS-0/0                                                                                                                                                                                                                                                   | R/W/HS-0/0     | R/W/HS-0/0     | U-0             | R/W/HS-0/0       | R/W/HS-0/0  |  |

|--------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|-----------------|------------------|-------------|--|

| —            | -                  | INT2IF                                                                                                                                                                                                                                                       | CLC2IF         | CWG2IF         | —               | CCP2IF           | TMR4IF      |  |

| bit 7        |                    |                                                                                                                                                                                                                                                              |                |                |                 |                  | bit (       |  |

|              |                    |                                                                                                                                                                                                                                                              |                |                |                 |                  |             |  |

| Legend:      |                    |                                                                                                                                                                                                                                                              |                |                |                 |                  |             |  |

| R = Read     | able bit           | W = Writable                                                                                                                                                                                                                                                 | bit            | U = Unimpler   | mented bit, rea | d as '0'         |             |  |

| u = Bit is   | unchanged          | x = Bit is unkr                                                                                                                                                                                                                                              | iown           | -n/n = Value a | at POR and BC   | R/Value at all o | ther Resets |  |

| '1' = Bit is | s set              | '0' = Bit is clea                                                                                                                                                                                                                                            | ared           | HS = Bit is se | et in hardware  |                  |             |  |

|              |                    |                                                                                                                                                                                                                                                              |                |                |                 |                  |             |  |

| bit 7-6      | Unimpleme          | ented: Read as '                                                                                                                                                                                                                                             | )'             |                |                 |                  |             |  |

| bit 5        | INT2IF: Ext        | ernal Interrupt 2                                                                                                                                                                                                                                            | Interrupt Flag | bit            |                 |                  |             |  |

|              |                    | ot has occurred (                                                                                                                                                                                                                                            |                | ed by software | )               |                  |             |  |

|              | 0 = Interrup       | ot event has not o                                                                                                                                                                                                                                           | occurred       |                |                 |                  |             |  |

| bit 4        |                    | C2 Interrupt Flag                                                                                                                                                                                                                                            | ,<br>,         |                |                 |                  |             |  |

|              |                    | <ol> <li>I = Interrupt has occurred (must be cleared by software)</li> <li>0 = Interrupt event has not occurred</li> </ol>                                                                                                                                   |                |                |                 |                  |             |  |

| bit 3        | CWG2IF: C          | WG2 Interrupt Fl                                                                                                                                                                                                                                             | ag bit         |                |                 |                  |             |  |

|              |                    | ot has occurred (                                                                                                                                                                                                                                            |                | ed by software | )               |                  |             |  |

|              | 0 = Interrup       | ot event has not o                                                                                                                                                                                                                                           | occurred       |                |                 |                  |             |  |

| bit 2        | Unimpleme          | ented: Read as '                                                                                                                                                                                                                                             | )'             |                |                 |                  |             |  |

| bit 1        | CCP2IF: CO         | CP2 Interrupt Fla                                                                                                                                                                                                                                            | g bit          |                |                 |                  |             |  |

|              |                    | ot has occurred (<br>ot event has not o                                                                                                                                                                                                                      |                | ed by software | )               |                  |             |  |

| bit 0        | TMR4IF: TM         | MR4 Interrupt Fla                                                                                                                                                                                                                                            | g bit          |                |                 |                  |             |  |

|              |                    | <ul> <li>1 = Interrupt has occurred (must be cleared by software)</li> <li>0 = Interrupt event has not occurred</li> </ul>                                                                                                                                   |                |                |                 |                  |             |  |

| Note:        | enable bit, or the | Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its correspond<br>enable bit, or the global enable bit. User software should ensure the appropriate interrupt flag bits are cl<br>prior to enabling an interrupt. |                |                |                 |                  |             |  |

## REGISTER 11-10: PIR7: PERIPHERAL INTERRUPT REGISTER 7

### 15.1.2 CONTROL REGISTERS

Several control registers are used in conjunction with the TBLRD and TBLWT instructions. These include the following registers:

- NVMCON1 register

- NVMCON2 register

- TABLAT register

- TBLPTR registers

### 15.1.2.1 NVMCON1 and NVMCON2 Registers

The NVMCON1 register (Register 15-1) is the control register for memory accesses. The NVMCON2 register is not a physical register; it is used exclusively in the memory write and erase sequences. Reading NVMCON2 will read all '0's.

The REG<1:0> control bits determine if the access will be to Data EEPROM Memory locations. PFM locations or User IDs, Configuration bits, Rev ID and Device ID. When REG<1:0> = 00, any subsequent operations will operate on the Data EEPROM Memory. When REG<1:0> = 10, any subsequent operations will operate on the program memory. When REG<1:0> = x1, any subsequent operations will operate on the Configuration bits, User IDs, Rev ID and Device ID.

The FREE bit allows the program memory erase operation. When the FREE bit is set, an erase operation is initiated on the next WR command. When FREE is clear, only writes are enabled. This bit is applicable only to the PFM and not to data EEPROM.

When set, the WREN bit will allow a program/erase operation. The WREN bit is cleared on power-up.

The WRERR bit is set by hardware when the WR bit is set and is cleared when the internal programming timer expires and the write operation is successfully complete.

The WR control bit initiates erase/write cycle operation when the REG<1:0> bits point to the Data EEPROM Memory location, and it initiates a write operation when the REG<1:0> bits point to the PFM location. The WR bit cannot be cleared by firmware; it can only be set by firmware. Then the WR bit is cleared by hardware at the completion of the write operation.

The NVMIF Interrupt Flag bit is set when the write is complete. The NVMIF flag stays set until cleared by firmware.

### 15.1.2.2 TABLAT – Table Latch Register

The Table Latch (TABLAT) is an 8-bit register mapped into the SFR space. The Table Latch register is used to hold 8-bit data during data transfers between program memory and data RAM.

### 15.1.2.3 TBLPTR – Table Pointer Register

The Table Pointer (TBLPTR) register addresses a byte within the program memory. The TBLPTR is comprised of three SFR registers: Table Pointer Upper Byte, Table Pointer High Byte and Table Pointer Low Byte (TBLPTRU:TBLPTRH:TBLPTRL). These three registers join to form a 22-bit wide pointer. The low-order 21 bits allow the device to address up to 2 Mbytes of program memory space. The 22<sup>nd</sup> bit allows access to the Device ID, the User ID and the Configuration bits.

The Table Pointer register, TBLPTR, is used by the TBLRD and TBLWT instructions. These instructions can update the TBLPTR in one of four ways based on the table operation. These operations on the TBLPTR affect only the low-order 21 bits.

### 15.1.2.4 Table Pointer Boundaries

TBLPTR is used in reads, writes and erases of the Program Flash Memory.

When a TBLRD is executed, all 22 bits of the TBLPTR determine which byte is read from program memory directly into the TABLAT register.

When a TBLWT is executed the byte in the TABLAT register is written, not to memory but, to a holding register in preparation for a program memory write. The holding registers constitute a write block which varies depending on the device (see Table 15-3). The 3, 4, or 5 LSbs of the TBLPTRL register determine which specific address within the holding register block is written to. The MSBs of the Table Pointer have no effect during TBLWT operations.

When a program memory write is executed the entire holding register block is written to the memory at the address determined by the MSbs of the TBLPTR. The 3, 4, or 5 LSBs are ignored during memory writes. For more detail, see Section 15.1.6 "Writing to Program Flash Memory".

Figure 15-3 describes the relevant boundaries of TBLPTR based on Program Flash Memory operations.

| TRIGEN | BURSTMD | Scanner Operation                                                                                                                                                                   |

|--------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | 0       | Memory access is requested when the CRC module is ready to accept data; the request is granted if no other higher priority source request is pending.                               |

| 1      | 0       | Memory access is requested when the CRC module is ready to accept data and trigger selection is true; the request is granted if no other higher priority source request is pending. |

| х      | 1       | Memory access is always requested, the request is granted if no other higher priority source request is pending.                                                                    |

### TABLE 16-2: SCANNER OPERATING MODES<sup>(1)</sup>

Note 1: See Section 3.1 "System Arbitration" for Priority selection and Section 3.2 "Memory Access Scheme" for Memory Access Scheme.

### REGISTER 16-12: SCANLADRU: SCAN LOW ADDRESS UPPER BYTE REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0                 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|-------------------------|---------|---------|

| —     | —   |         |         | LADR<2  | 21:16> <sup>(1,2)</sup> |         |         |

| bit 7 |     |         |         |         |                         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 Unimplemented: Read as '0'

bit 5-0

LADR<21:16>: Scan Start/Current Address bits<sup>(1,2)</sup>

Upper bits of the current address to be fetched from, value increments on each fetch of memory.

- **Note 1:** Registers SCANLADRU/H/L form a 22-bit value, but are not guarded for atomic or asynchronous access; registers should only be read or written while SGO = 0 (SCANCON0 register).

- 2: While SGO = 1 (SCANCON0 register), writing to this register is ignored.

### REGISTER 16-13: SCANLADRH: SCAN LOW ADDRESS HIGH BYTE REGISTER

| R/W-0/0                      | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|------------------------------|---------|---------|---------|---------|---------|---------|---------|

| LADR<15:8> <sup>(1, 2)</sup> |         |         |         |         |         |         |         |

| bit 7                        |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 LADR<15:8>: Scan Start/Current Address bits<sup>(1, 2)</sup> Most Significant bits of the current address to be fetched from, value increments on each fetch of memory.

- **Note 1:** Registers SCANLADRU/H/L form a 22-bit value, but are not guarded for atomic or asynchronous access; registers should only be read or written while SGO = 0 (SCANCON0 register).

- **2:** While SGO = 1 (SCANCON0 register), writing to this register is ignored.

### **REGISTER 19-3: PPSLOCK: PPS LOCK REGISTER**

| U-0              | U-0                               | U-0                  | U-0  | U-0                                                   | U-0 | U-0 | R/W-0/0        |

|------------------|-----------------------------------|----------------------|------|-------------------------------------------------------|-----|-----|----------------|

| _                | —                                 | —                    | —    | —                                                     | _   | _   | PPSLOCKED      |

| bit 7            | ·                                 |                      |      | •                                                     |     |     | bit 0          |

|                  |                                   |                      |      |                                                       |     |     |                |

| Legend:          |                                   |                      |      |                                                       |     |     |                |

| R = Readable     | R = Readable bit W = Writable bit |                      | bit  | U = Unimplemented bit, read as '0'                    |     |     |                |

| u = Bit is unc   | hanged                            | d x = Bit is unknown |      | -n/n = Value at POR and BOR/Value at all other Resets |     |     | l other Resets |

| '1' = Bit is set | t                                 | '0' = Bit is clea    | ared |                                                       |     |     |                |

| bit 7-1 Unimplemented: Read as '0 |

|-----------------------------------|

|-----------------------------------|

bit 0 PPSLOCKED: PPS Locked bit

1 = PPS is locked. PPS selections can not be changed.

0 = PPS is not locked. PPS selections can be changed.

## PIC18(L)F24/25K42

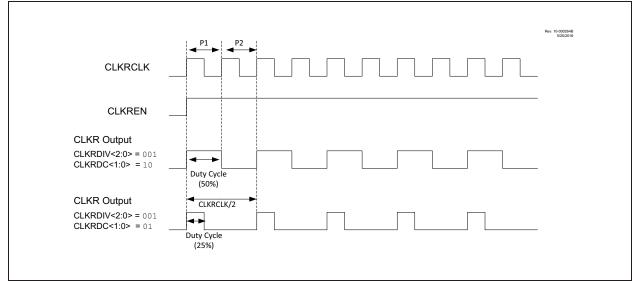

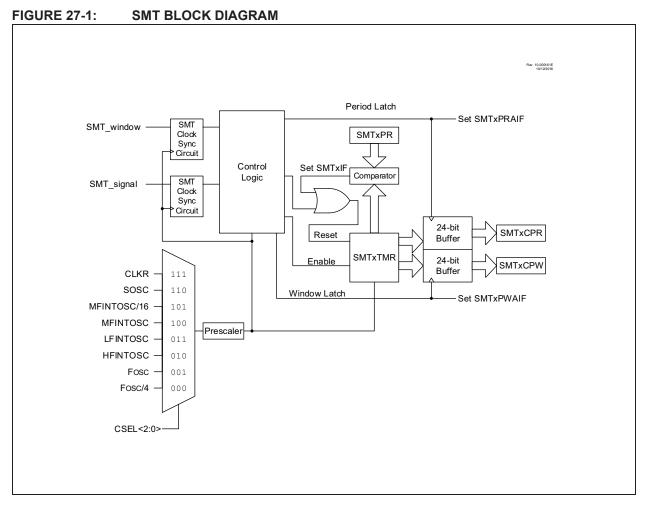

FIGURE 27-2: SMT SIGNAL AND WINDOW BLOCK DIAGRAM

© 2016-2017 Microchip Technology Inc.

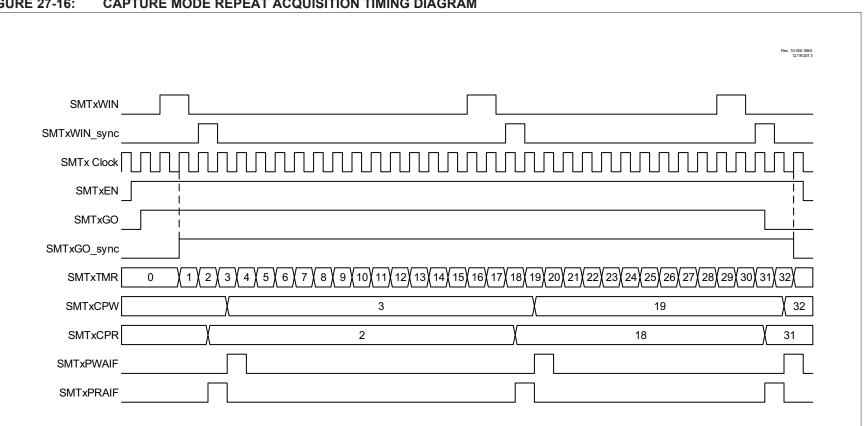

#### FIGURE 27-16: CAPTURE MODE REPEAT ACQUISITION TIMING DIAGRAM

PIC18(L)F24/25K42

PIC18(L)F24/25K42

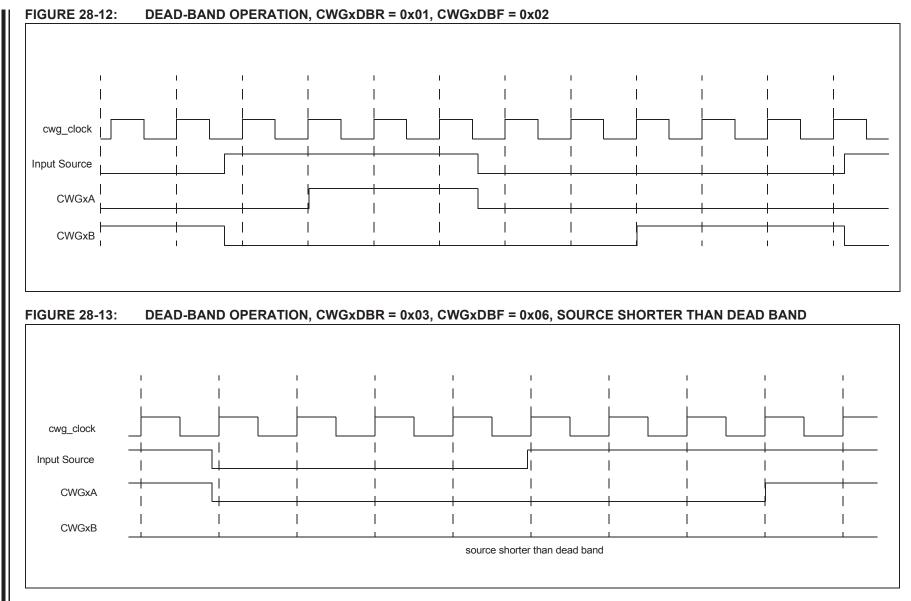

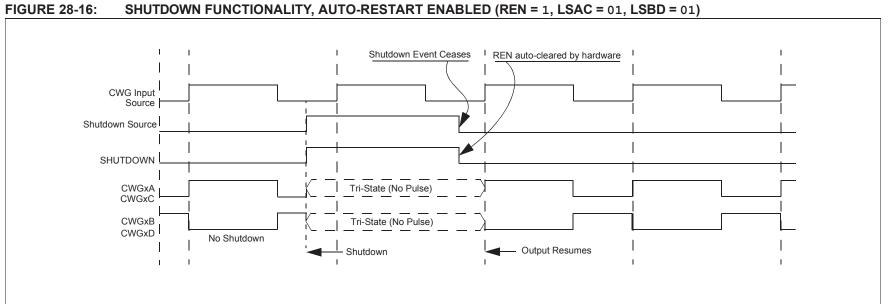

SHUTDOWN FUNCTIONALITY, AUTO-RESTART ENABLED (REN = 1, LSAC = 01, LSBD = 01)

## 33.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART) WITH PROTOCOL SUPPORT

The Universal Asynchronous Receiver Transmitter (UART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer, independent of device program execution. The UART, also known as a Serial Communications Interface (SCI), can be configured as a full-duplex asynchronous system or one of several automated protocols. Full-Duplex mode is useful for communications with peripheral systems, such as CRT terminals and personal computers.

Supported protocols include:

- LIN Master and Slave

- DMX mode

- · DALI control gear and control device

The UART module includes the following capabilities:

- · Full-duplex asynchronous transmit and receive

- Two-character input buffer

- · One-character output buffer

- · Programmable 7-bit or 8-bit character length

- 9th bit Address detection

- · 9th bit even or odd parity

- · Input buffer overrun error detection

- Received character framing error detection

- · Hardware and software flow control

- · Automatic checksums

- Programmable 1, 1.5, and 2 Stop bits

- Programmable data polarity

- Manchester encoder/decoder

- · Operation in Sleep

- Automatic detection and calibration of the baud rate

- Wake-up on Break reception

- Automatic and user timed Break period generation

- RX and TX inactivity timeouts (with Timer2)

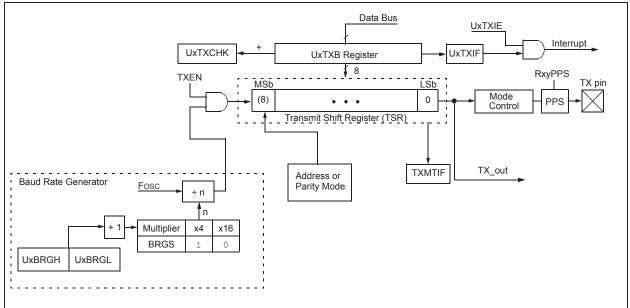

Block diagrams of the UART transmitter and receiver are shown in Figure 33-1 and Figure 33-2.

The UART transmit output (TX\_out) is available to the TX pin and internally to various peripherals.

### FIGURE 33-1: UART TRANSMIT BLOCK DIAGRAM

## 35.1 I<sup>2</sup>C Features

- Inter-Integrated Circuit (I<sup>2</sup>C) interface supports the following modes in hardware:

- Master mode

- Slave mode with byte NACKing

- Multi-Master mode

- Dedicated Address, Receive and Transmit buffers

- Up to four Slave addresses matching

- · General Call address matching

- 7-bit and 10-bit addressing with masking

- Start, Restart, Stop, Address, Write, and ACK Interrupts

- Clock Stretching hardware for:

- RX Buffer Full

- TX Buffer Empty

- After Address, Write, and ACK

- · Bus Collision Detection with arbitration

- Bus Timeout Detection

- · SDA hold time selection

- I<sup>2</sup>C, SMBus 2.0, and SMBus 3.0 input level selections

## 35.2 I<sup>2</sup>C Module Overview

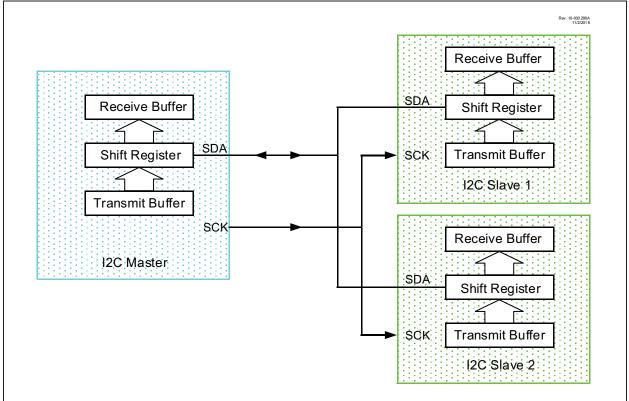

The I<sup>2</sup>C module provides a synchronous interface between the microcontroller and other I<sup>2</sup>C-compatible devices using the two-wire I<sup>2</sup>C serial bus. Devices communicate in a master/slave environment. The I<sup>2</sup>C bus specifies two signal connections:

- Serial Clock (SCL)

- Serial Data (SDA)

Both the SCL and SDA connections are bidirectional open-drain lines, each requiring pull-up resistors to the supply voltage. Pulling the line to ground is considered a logical zero and letting the line float is considered a logical one. Every transaction on the I<sup>2</sup>C bus has to be initiated by the Master.

Figure 35-25 shows a typical connection between a master and more than one slave.

### FIGURE 35-2: I<sup>2</sup>C MASTER/SLAVE CONNECTIONS

## TABLE 38-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES<sup>(1,4)</sup>

| ADC CI              | lock Period (TAD) | Device Frequency (Fosc) |                         |                       |                       |                        |                        |                         |

|---------------------|-------------------|-------------------------|-------------------------|-----------------------|-----------------------|------------------------|------------------------|-------------------------|

| ADC<br>Clock Source | CS<5:0>           | 64 MHz                  | 32 MHz                  | 20 MHz                | 16 MHz                | 8 MHz                  | 4 MHz                  | 1 MHz                   |

| Fosc/2              | 000000            | 31.25 ns <sup>(2)</sup> | 62.5 ns <sup>(2)</sup>  | 100 ns <sup>(2)</sup> | 125 ns <sup>(2)</sup> | 250 ns <sup>(2)</sup>  | 500 ns <sup>(2)</sup>  | 2.0 μs                  |

| Fosc/4              | 000001            | 62.5 ns <sup>(2)</sup>  | 125 ns <sup>(2)</sup>   | 200 ns <sup>(2)</sup> | 250 ns <sup>(2)</sup> | 500 ns <sup>(2)</sup>  | 1.0 μs                 | 4.0 μs                  |

| Fosc/6              | 000010            | 125 ns <sup>(2)</sup>   | 187.5 ns <sup>(2)</sup> | 300 ns <sup>(2)</sup> | 375 ns <sup>(2)</sup> | 750 ns <sup>(2)</sup>  | 1.5 μs                 | 6.0 μs                  |

| Fosc/8              | 000011            | 187.5 ns <sup>(2)</sup> | 250 ns <sup>(2)</sup>   | 400 ns <sup>(2)</sup> | 500 ns <sup>(2)</sup> | 1.0 μs                 | 2.0 μs                 | 9.0 μs <sup>(3)</sup>   |

|                     |                   |                         |                         |                       |                       |                        |                        |                         |

| Fosc/16             | 000111            | 250 ns <sup>(2)</sup>   | 500 ns <sup>(2)</sup>   | 800 ns <sup>(2)</sup> | 1.0 μs                | 2.0 μs                 | 4.0 μs                 | 16.0 μs <sup>(3)</sup>  |

|                     |                   |                         |                         |                       |                       |                        |                        |                         |

| Fosc/128            | 111111            | 2.0 μs                  | 4.0 μs                  | 6.4 μs                | 8.0 μs                | 16.0 μs <sup>(3)</sup> | 32.0 μs <sup>(2)</sup> | 128.0 μs <sup>(2)</sup> |

| FRC                 | CS(ADCON0<4>) = 1 | 1.0-6.0 μs              | 1.0-6.0 μs              | 1.0-6.0 μs            | 1.0-6.0 μs            | 1.0-6.0 μs             | 1.0-6.0 μs             | 1.0-6.0 μs              |

Legend: Shaded cells are outside of recommended range.

Note 1: See TAD parameter for FRC source typical TAD value.

**2:** These values violate the required TAD time.

- **3:** Outside the recommended TAD time.

- 4: The ADC clock period (TAD) and total ADC conversion time can be minimized when the ADC clock is derived from the system clock FOSC. However, the FRC oscillator source must be used when conversions are to be performed with the device in Sleep mode.

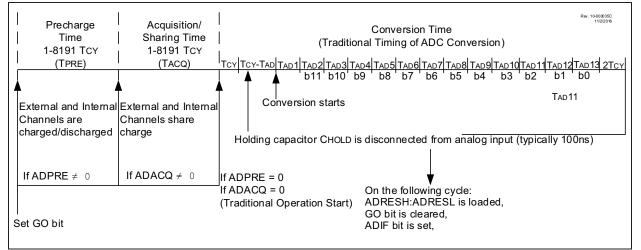

### FIGURE 38-2: ANALOG-TO-DIGITAL CONVERSION TAD CYCLES

#### 38.3 **ADC Acquisition Requirements**

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 38-4. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), refer to Figure 38-4. The maximum recommended impedance for analog sources is 10 k $\Omega$ . If the source

impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an ADC acquisition must be completed before the conversion can be started. To calculate the minimum acquisition time, Equation 38-1 may be used. This equation assumes that 1/2 LSb error is used (4,096 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

### EQUATION 38-1: ACQUISITION TIME EXAMPLE

Assumptions: Temperature =

$$50^{\circ}C$$

and external impedance of  $10k\Omega 5.0V VDD$

$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient$

$= TAMP + TC + TCOFF$

$= 2\mu s + TC + [(Temperature - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$

The value for TC can be approximated with the following equations:

Τ

$$V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) = V_{CHOLD} ; [1] V_{CHOLD} charged to within 1/2 lsb$$

$$V_{APPLIED}\left(1 - e^{\frac{-Tc}{RC}}\right) = V_{CHOLD} ; [2] V_{CHOLD} charge response to V_{APPLIED} (1 - \frac{1}{(2^{n+1}) - 1}) ; combining [1] and [2]$$

*Note: Where* n = number *of bits of the ADC.*

Solving for TC:

$$T_{C} = -C_{HOLD}(R_{IC} + R_{SS} + R_{S}) \ln(1/8191)$$

=  $-28pF(1k\Omega + 7k\Omega + 10k\Omega) \ln(0.0001221)$

=  $4.54\mu s$

Therefore:

$$TACQ = 2\mu s + 4.54\mu s + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

= 7.79\mu s

Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- 3: The maximum recommended impedance for analog sources is 10 k $\Omega$ . This is required to meet the pin leakage specification.

### REGISTER 38-22: ADPREVH: ADC PREVIOUS RESULT REGISTER

| R-x                | R-x | R-x                  | R-x | R-x            | R-x              | R-x            | R-x          |

|--------------------|-----|----------------------|-----|----------------|------------------|----------------|--------------|

|                    |     |                      | PRE | V<15:8>        |                  |                |              |

| bit 7              |     |                      |     |                |                  |                | bit 0        |

|                    |     |                      |     |                |                  |                |              |

| Legend:            |     |                      |     |                |                  |                |              |

| R = Readable bit   |     | W = Writable bit     |     | U = Unimpler   | nented bit, read | d as '0'       |              |

| u = Bit is unchang | ged | x = Bit is unknown   | ı   | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is set   |     | '0' = Bit is cleared |     |                |                  |                |              |

| bit 7-0 | PREV<15:8>: Previous ADC Results bits                                     |

|---------|---------------------------------------------------------------------------|

|         | If ADPSIS = 1:                                                            |

|         | Upper byte of FLTR at the start of current ADC conversion                 |

|         | If ADPSIS = 0:                                                            |

|         | Upper bits of ADRES at the start of current ADC conversion <sup>(1)</sup> |

|         |                                                                           |

**Note 1:** If ADPSIS = 0, ADPREVH and ADPREVL are formatted the same way as ADRES is, depending on the FM bit.

### REGISTER 38-23: ADPREVL: ADC PREVIOUS RESULT REGISTER

| R-x       | R-x | R-x | R-x | R-x | R-x | R-x | R-x   |

|-----------|-----|-----|-----|-----|-----|-----|-------|

| PREV<7:0> |     |     |     |     |     |     |       |

| bit 7     |     |     |     |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-0 | PREV<7:0>: Previous ADC Results bits                                      |  |  |  |

|---------|---------------------------------------------------------------------------|--|--|--|

|         | If ADPSIS = 1:                                                            |  |  |  |

|         | Lower byte of FLTR at the start of current ADC conversion                 |  |  |  |

|         | If $ADPSIS = 0$ :                                                         |  |  |  |

|         | Lower bits of ADRES at the start of current ADC conversion <sup>(1)</sup> |  |  |  |

|         |                                                                           |  |  |  |

**Note 1:** If ADPSIS = 0, ADPREVH and ADPREVL are formatted the same way as ADRES is, depending on the FM bit.

# PIC18(L)F24/25K42

| INFS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SNZ                  | Incremen                               | Increment f, skip if not 0       |                                                                                                                                                                                                                        |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Synta                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ax:                  | INFSNZ f                               | {,d {,a}}                        |                                                                                                                                                                                                                        |  |  |  |  |

| Operands:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                      | $0 \le f \le 255$                      |                                  |                                                                                                                                                                                                                        |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                      | $d \in \llbracket 0,1 \rrbracket$      | d ∈ [0,1]                        |                                                                                                                                                                                                                        |  |  |  |  |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                      | a ∈ [0,1]                              |                                  |                                                                                                                                                                                                                        |  |  |  |  |

| Oper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ation:               | (f) + 1 $\rightarrow$ de skip if resul |                                  |                                                                                                                                                                                                                        |  |  |  |  |

| Statu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | s Affected:          | None                                   |                                  |                                                                                                                                                                                                                        |  |  |  |  |

| Enco                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ding:                | 0100                                   | 0100 10da ffff ffff              |                                                                                                                                                                                                                        |  |  |  |  |

| Desc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ription:             | The conten                             | The contents of register 'f' are |                                                                                                                                                                                                                        |  |  |  |  |

| <ul> <li>incremented. If 'd' is '0', the result placed in W. If 'd' is '1', the result placed back in register 'f' (default). If the result is not '0', the next instruction, which is already fetched discarded and a NOP is executed instead, making it a 2-cycle instruction. If 'a' is '0', the Access Bank is sele. If 'a' is '1', the BSR is used to sele. GPR bank. If 'a' is '0' and the extended instruster is enabled, this instruction ope in Indexed Literal Offset Addressim mode whenever f ≤ 95 (5Fh). See tion 43.2.3 "Byte-Oriented and F Oriented Instructions in Indexed eral Offset Mode" for details.</li> <li>Words: 1</li> </ul> |                      |                                        |                                  | he result is<br>e result is<br>(default).<br>hext<br>dy fetched, is<br>kecuted<br>le<br>hk is selected.<br>d to select the<br>ed instruction<br>operates<br>addressing<br>Fh). See Sec-<br>ed and Bit-<br>Indexed Lit- |  |  |  |  |

| Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | es:                  | 1(2)<br>Note: 3 (                      | cycles if skip a                 | nd followed                                                                                                                                                                                                            |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                      |                                        | a 2-word instr                   |                                                                                                                                                                                                                        |  |  |  |  |

| QC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ycle Activity:       |                                        |                                  |                                                                                                                                                                                                                        |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Q1                   | Q2                                     | Q3                               | Q4                                                                                                                                                                                                                     |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Decode               | Read                                   | Process                          | Write to                                                                                                                                                                                                               |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                      | register 'f'                           | Data                             | destination                                                                                                                                                                                                            |  |  |  |  |

| lf sk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ip:                  |                                        |                                  |                                                                                                                                                                                                                        |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Q1                   | Q2                                     | Q3                               | Q4                                                                                                                                                                                                                     |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | No                   | No                                     | No                               | No                                                                                                                                                                                                                     |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | operation            | operation                              | operation                        | operation                                                                                                                                                                                                              |  |  |  |  |

| lf sk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ip and followe       | d by 2-word in                         | struction:                       |                                                                                                                                                                                                                        |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Q1                   | Q2                                     | Q3                               | Q4                                                                                                                                                                                                                     |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | No                   | No                                     | No                               | No                                                                                                                                                                                                                     |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | operation            | operation                              | operation                        | operation                                                                                                                                                                                                              |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | No                   | No                                     | No                               | No                                                                                                                                                                                                                     |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | operation            | operation                              | operation                        | operation                                                                                                                                                                                                              |  |  |  |  |

| <u>Exan</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | nple:                | HERE I<br>ZERO<br>NZERO                | ZERO                             |                                                                                                                                                                                                                        |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Before Instruc<br>PC | = Address                              |                                  |                                                                                                                                                                                                                        |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | After Instructio     |                                        | 4                                |                                                                                                                                                                                                                        |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | REG<br>If REG        | = REG + <sup>*</sup><br>≠ 0;           | 1                                |                                                                                                                                                                                                                        |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | PC                   | = Address                              | (NZERO)                          |                                                                                                                                                                                                                        |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | If REG<br>PC         | = 0;<br>= Address                      | (ZERO)                           |                                                                                                                                                                                                                        |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | .0                   | 71001000                               | (2000)                           |                                                                                                                                                                                                                        |  |  |  |  |

| IOR          | LW             | Inclusiv            | e OR lite                                                                             | ral wi | th \ | N        |  |  |

|--------------|----------------|---------------------|---------------------------------------------------------------------------------------|--------|------|----------|--|--|

| Synta        | ax:            | IORLW I             | <                                                                                     |        |      |          |  |  |

| Oper         | ands:          | $0 \le k \le 25$    | $0 \leq k \leq 255$                                                                   |        |      |          |  |  |

| Operation:   |                | (W) .OR.            | $k \rightarrow W$                                                                     |        |      |          |  |  |

| Statu        | s Affected:    | N, Z                |                                                                                       |        |      |          |  |  |

| Enco         | ding:          | 0000                | 1001                                                                                  | kkk    | k    | kkkk     |  |  |

| Description: |                |                     | The contents of W are ORed with the 8-<br>bit literal 'k'. The result is placed in W. |        |      |          |  |  |

| Word         | ls:            | 1                   |                                                                                       |        |      |          |  |  |

| Cycle        | es:            | 1                   |                                                                                       |        |      |          |  |  |

| QC           | ycle Activity: |                     |                                                                                       |        |      |          |  |  |

|              | Q1             | Q2                  | Q                                                                                     | 3      |      | Q4       |  |  |

|              | Decode         | Read<br>literal 'k' | Proce<br>Dat                                                                          |        | Wr   | ite to W |  |  |

|              |                |                     | -                                                                                     |        |      |          |  |  |

| Example:     |                | IORLW               | 35h                                                                                   |        |      |          |  |  |

|              | Before Instruc | tion                |                                                                                       |        |      |          |  |  |

|              | W              | = 9Ah               |                                                                                       |        |      |          |  |  |

BFh

=

After Instruction W

© 2016-2017 Microchip Technology Inc.

# PIC18(L)F24/25K42

| ADDWF                                                          | ADD W to Indexed<br>(Indexed Literal Offset mode)                                                                                                                                                                     |                                       |     |         |                     |  |  |  |

|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----|---------|---------------------|--|--|--|

| Syntax:                                                        | ADDWF                                                                                                                                                                                                                 | [k] {,d}                              |     |         |                     |  |  |  |

| Operands:                                                      | $\begin{array}{l} 0 \leq k \leq 95 \\ d \ \in \ [0,1] \end{array}$                                                                                                                                                    |                                       |     |         |                     |  |  |  |