Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                           |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f24k42-i-ml |

# PIC18(L)F2X/4X/5XK42 FAMILY TYPES

| Device         | Data Sheet Index | Program Flash Memory (KB) | Data EEPROM (B) | Data SRAM (bytes) | I/OPins | 12-bit ADC <sup>2</sup><br>(ch) | 5-bit DAC | Comparator | 8-bit/ (with HLT) /16-bit Timer | Window Watchdog Timer<br>(WWDT) | Signal Measurement Timer (SMT) | CCP/10-bit PWM | CWG | NCO | CLC | Zero-Cross Detect | Direct Memory Access (DMA)<br>(ch) | Memory Access Partition | Vectored Interrupts | UART | l <sup>2</sup> C/SPI | Peripheral Pin Select | Peripheral Module Disable | Debug <sup>(1)</sup> |

|----------------|------------------|---------------------------|-----------------|-------------------|---------|---------------------------------|-----------|------------|---------------------------------|---------------------------------|--------------------------------|----------------|-----|-----|-----|-------------------|------------------------------------|-------------------------|---------------------|------|----------------------|-----------------------|---------------------------|----------------------|

| PIC18(L)F24K42 | Α                | 16                        | 256             | 1024              | 25      | 24                              | 1         | 2          | 3                               | Υ                               | Υ                              | 4/4            | 3   | 1   | 4   | Υ                 | 2                                  | Υ                       | Υ                   | 2    | 2/1                  | Υ                     | Υ                         | I                    |

| PIC18(L)F25K42 | Α                | 32                        | 256             | 2048              | 25      | 24                              | 1         | 2          | 3                               | Υ                               | Υ                              | 4/4            | 3   | 1   | 4   | Υ                 | 2                                  | Υ                       | Υ                   | 2    | 2/1                  | Υ                     | Υ                         | I                    |

| PIC18(L)F26K42 | В                | 64                        | 1024            | 4096              | 25      | 24                              | 1         | 2          | 3                               | Υ                               | Υ                              | 4/4            | 3   | 1   | 4   | Υ                 | 2                                  | Υ                       | Υ                   | 2    | 2/1                  | Υ                     | Υ                         | I                    |

| PIC18(L)F27K42 | С                | 128                       | 1024            | 8192              | 25      | 24                              | 1         | 2          | 3                               | Υ                               | Υ                              | 4/4            | 3   | 1   | 4   | Υ                 | 2                                  | Υ                       | Υ                   | 2    | 2/1                  | Υ                     | Υ                         | I                    |

| PIC18(L)F45K42 | В                | 32                        | 256             | 2048              | 36      | 35                              | 1         | 2          | 3                               | Υ                               | Υ                              | 4/4            | 3   | 1   | 4   | Υ                 | 2                                  | Υ                       | Υ                   | 2    | 2/1                  | Υ                     | Υ                         | I                    |

| PIC18(L)F46K42 | В                | 64                        | 1024            | 4096              | 36      | 35                              | 1         | 2          | 3                               | Υ                               | Υ                              | 4/4            | 3   | 1   | 4   | Υ                 | 2                                  | Υ                       | Υ                   | 2    | 2/1                  | Υ                     | Υ                         | -1                   |

| PIC18(L)F47K42 | С                | 128                       | 1024            | 8192              | 36      | 35                              | 1         | 2          | 3                               | Υ                               | Υ                              | 4/4            | 3   | 1   | 4   | Υ                 | 2                                  | Υ                       | Υ                   | 2    | 2/1                  | Υ                     | Υ                         | I                    |

| PIC18(L)F55K42 | В                | 32                        | 1024            | 2048              | 44      | 43                              | 1         | 2          | 3                               | Υ                               | Υ                              | 4/4            | 3   | 1   | 4   | Υ                 | 2                                  | Υ                       | Υ                   | 2    | 2/1                  | Υ                     | Υ                         | I                    |

| PIC18(L)F56K42 | В                | 64                        | 1024            | 4096              | 44      | 43                              | 1         | 2          | 3                               | Υ                               | Υ                              | 4/4            | 3   | 1   | 4   | Υ                 | 2                                  | Υ                       | Υ                   | 2    | 2/1                  | Υ                     | Υ                         | I                    |

| PIC18(L)F57K42 | С                | 128                       | 1024            | 8192              | 44      | 43                              | 1         | 2          | 3                               | Υ                               | Υ                              | 4/4            | 3   | 1   | 4   | Υ                 | 2                                  | Υ                       | Υ                   | 2    | 2/1                  | Υ                     | Υ                         | 1                    |

PIC18(L)F24/25K42

Note 1: I – Debugging integrated on chip.

Note: For other small form-factor package availability and marking information, visit <a href="http://www.microchip.com/packaging">http://www.microchip.com/packaging</a> or contact your local sales office.

# PIC18(L)F24/25K42

# **Table of Contents**

| 1.0 Device Overview                                                           |     |

|-------------------------------------------------------------------------------|-----|

| 2.0 Guidelines for Getting Started with PIC18(L)F24/25K42 Microcontrollers    | 14  |

| 3.0 PIC18 CPU                                                                 | 17  |

| 4.0 Memory Organization                                                       | 24  |

| 5.0 Device Configuration                                                      |     |

| 6.0 Device Information Area                                                   |     |

| 7.0 Device Configuration Information                                          |     |

| 8.0 Resets                                                                    |     |

| 9.0 Oscillator Module (with Fail-Safe Clock Monitor)                          |     |

| 10.0 Reference Clock Output Module                                            |     |

| 11.0 Interrupt Controller                                                     |     |

| 12.0 Power-Saving Operation Modes                                             |     |

| 13.0 Windowed Watchdog Timer (WWDT)                                           |     |

| 14.0 8x8 Hardware Multiplier                                                  |     |

| 15.0 Nonvolatile Memory (NVM) Control                                         |     |

| 16.0 Cyclic Redundancy Check (CRC) Module with Memory Scanner                 |     |

| 17.0 Direct Memory Access (DMA)                                               |     |

| · · · · · · · · · · · · · · · · · · ·                                         |     |

| 18.0 I/O Ports                                                                |     |

|                                                                               |     |

| 20.0 Interrupt-on-Change                                                      |     |

| 21.0 Peripheral Module Disable (PMD)                                          |     |

| 22.0 Timer0 Module                                                            |     |

| 23.0 Timer1/3/5 Module with Gate Control                                      |     |

| 24.0 Timer2/4/6 Module                                                        |     |

| 25.0 Capture/Compare/PWM Module                                               |     |

| 26.0 Pulse-Width Modulation (PWM)                                             |     |

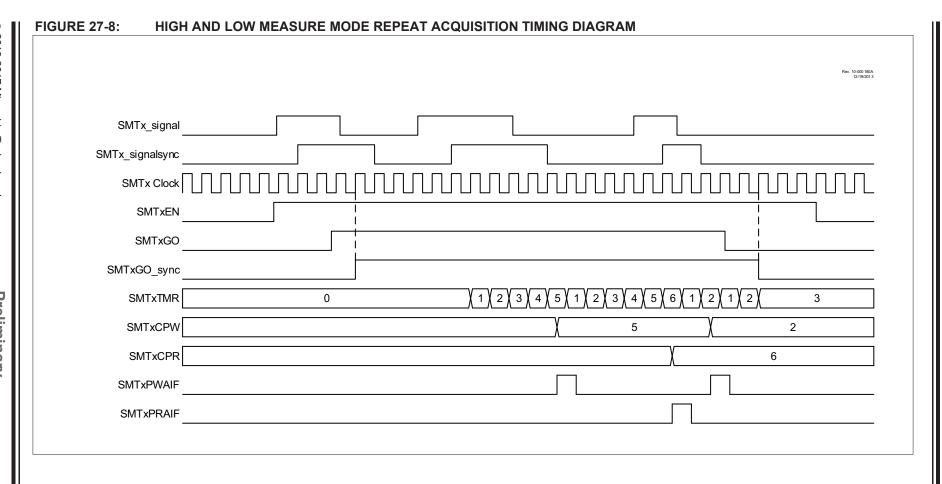

| 27.0 Signal Measurement Timer (SMT)                                           | 364 |

| 28.0 Complementary Waveform Generator (CWG) Module                            |     |

| 29.0 Configurable Logic Cell (CLC)                                            |     |

| 30.0 Numerically Controlled Oscillator (NCO) Module                           |     |

| 31.0 Zero-Cross Detection (ZCD) Module                                        |     |

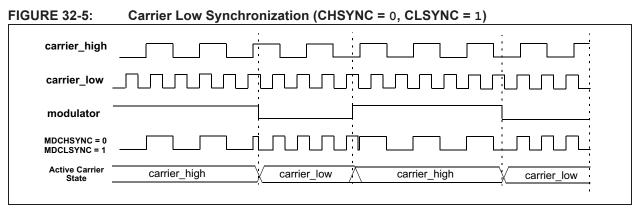

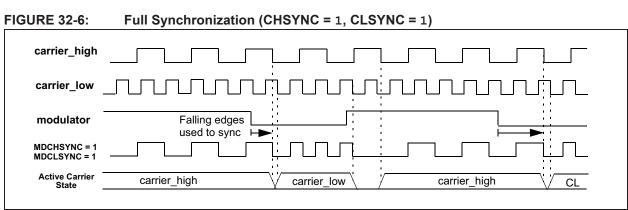

| 32.0 Data Signal Modulator (DSM) Module                                       |     |

| 33.0 Universal Asynchronous Receiver Transmitter (UART) With Protocol Support |     |

| 34.0 Serial Peripheral Interface (SPI) Module                                 |     |

| 35.0 I <sup>2</sup> C Module                                                  | 546 |

| 36.0 Fixed Voltage Reference (FVR)                                            | 599 |

| 37.0 Temperature Indicator Module                                             |     |

| 38.0 Analog-to-Digital Converter with Computation (ADC2) Module               |     |

| 39.0 5-Bit Digital-to-Analog Converter (DAC) Module                           |     |

| 40.0 Comparator Module                                                        | 646 |

| 41.0 High/Low-Voltage Detect (HLVD)                                           | 655 |

| 42.0 In-Circuit Serial Programming™ (ICSP™)                                   | 663 |

| 43.0 Instruction Set Summary                                                  | 665 |

| 44.0 Register Summary                                                         | 719 |

| 45.0 Development Support                                                      |     |

| 46.0 Electrical Specifications                                                |     |

| 47.0 DC and AC Characteristics Graphs and Tables                              |     |

| 48.0 Packaging Information                                                    |     |

| Appendix A. Revision History                                                  |     |

# 8.14 Register Definitions: Power Control

# REGISTER 8-2: PCON0: POWER CONTROL REGISTER 0

| R/W/HS-0/q | R/W/HS-0/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-0/u | R/W/HC-q/u |

|------------|------------|------------|------------|------------|------------|------------|------------|

| STKOVF     | STKUNF     | WDTWV      | RWDT       | RMCLR      | RI         | POR        | BOR        |

| bit 7      |            | •          |            |            |            |            | bit 0      |

| Legend:                      |                      |                                                       |

|------------------------------|----------------------|-------------------------------------------------------|

| HC = Bit is cleared by hardw | are                  | HS = Bit is set by hardware                           |

| R = Readable bit             | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged         | x = Bit is unknown   | -m/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set             | '0' = Bit is cleared | q = Value depends on condition                        |

bit 7 STKOVF: Stack Overflow Flag bit

1 = A Stack Overflow occurred (more CALLs than fit on the stack)

0 = A Stack Overflow has not occurred or set to '0' by firmware

bit 6 STKUNF: Stack Underflow Flag bit

1 = A Stack Underflow occurred (more RETURNS than CALLS)

0 = A Stack Underflow has not occurred or set to '0' by firmware

bit 5 WDTWV: Watchdog Window Violation bit

1 = A WDT window violation has not occurred or set to '1' by firmware

0 = A CLRWDT instruction was issued when the WDT Reset window was closed (set to '0' in hardware when a WDT window violation Reset occurs)

bit 4 RWDT: WDT Reset Flag bit

1 = A WDT overflow/time-out Reset has not occurred or set to '1' by firmware

0 = A WDT overflow/time-out Reset has occurred (set to '0' in hardware when a WDT Reset occurs)

bit 3 RMCLR: MCLR Reset Flag bit

$1 = A \overline{MCLR}$  Reset has not occurred or set to '1' by firmware

$0 = A \overline{MCLR}$  Reset has occurred (set to '0' in hardware when a  $\overline{MCLR}$  Reset occurs)

bit 2 RESET Instruction Flag bit

1 = A RESET instruction has not been executed or set to '1' by firmware

0 = A RESET instruction has been executed (set to '0' in hardware upon executing a RESET instruction)

bit 1 POR: Power-on Reset Status bit

1 = No Power-on Reset occurred or set to '1' by firmware

0 = A Power-on Reset occurred (set to '0' in hardware when a Power-on Reset occurs)

bit 0 **BOR**: Brown-out Reset Status bit

1 = No Brown-out Reset occurred or set to '1' by firmware

0 = A Brown-out Reset occurred (set to '0' in hardware when a Brown-out Reset occurs)

# REGISTER 11-29: IPR4: PERIPHERAL INTERRUPT PRIORITY REGISTER 4

| R/W-1/1 | R/W-1/1 | R/W-1/1 | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|---------|---------|---------|-----|---------|---------|---------|---------|

| CLC1IP  | CWG1IP  | NCO1IP  | _   | CCP1IP  | TMR2IP  | TMR1GIP | TMR1IP  |

| bit 7   |         |         |     |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7 | CLC1IP: CLC1 Interrupt Priority bit       |

|-------|-------------------------------------------|

|       | 1 = High priority                         |

|       | 0 = Low priority                          |

| bit 6 | CWG1IP: CWG1 Interrupt Priority bit       |

|       | 1 = High priority                         |

|       | 0 = Low priority                          |

| bit 5 | NCO1IP: NCO1 Interrupt Priority bit       |

|       | 1 = High priority                         |

|       | 0 = Low priority                          |

| bit 4 | Unimplemented: Read as '0'                |

| bit 3 | CCP1IP: CCP1 Interrupt Priority bit       |

|       | 1 = High priority                         |

|       | 0 = Low priority                          |

| bit 2 | TMR2IP: TMR2 Interrupt Priority bit       |

|       | 1 = High priority                         |

|       | 0 = Low priority                          |

| bit 1 | TMR1GIP: TMR1 Gate Interrupt Priority bit |

|       | 1 = High priority                         |

|       | 0 = Low priority                          |

| bit 0 | TMR1IP: TMR1 Interrupt Priority bit       |

|       | 1 = High priority                         |

|       | 0 = Low priority                          |

# 16.0 CYCLIC REDUNDANCY CHECK (CRC) MODULE WITH MEMORY SCANNER

The Cyclic Redundancy Check (CRC) module provides a software-configurable hardware-implemented CRC checksum generator. This module includes the following features:

- · Any standard CRC up to 16 bits can be used

- · Configurable Polynomial

- · Any seed value up to 16 bits can be used

- · Standard and reversed bit order available

- Augmented zeros can be added automatically or by the user

- Memory scanner for fast CRC calculations on program/Data EEPROM memory user data

- Software loadable data registers for communication CRC's

#### 16.1 CRC Module Overview

The CRC module provides a means for calculating a check value of program/Data EEPROM memory. The CRC module is coupled with a memory scanner for faster CRC calculations. The memory scanner can automatically provide data to the CRC module. The CRC module can also be operated by directly writing data to SFRs, without using a scanner.

#### REGISTER 16-16: SCANHADRH: SCAN HIGH ADDRESS HIGH BYTE REGISTER

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0                | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|---------|---------|---------|------------------------|---------|---------|---------|

|         |         |         | HADR<1  | 5:8> <sup>(1, 2)</sup> |         |         |         |

| bit 7   |         |         |         |                        |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 HADR<15:8>: Scan End Address bits<sup>(1, 2)</sup>

Most Significant bits of the address at the end of the designated scan

**Note 1:** Registers SCANHADRU/H/L form a 22-bit value, but are not guarded for atomic or asynchronous access; registers should only be read or written while SGO = 0 (SCANCON0 register).

2: While SGO = 1 (SCANCON0 register), writing to this register is ignored.

#### REGISTER 16-17: SCANHADRL: SCAN HIGH ADDRESS LOW BYTE REGISTER

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0                | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|---------|---------|---------|------------------------|---------|---------|---------|

|         |         |         | HADR<   | 7:0> <sup>(1, 2)</sup> |         |         |         |

| bit 7   |         |         |         |                        |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 HADR<7:0>: Scan End Address bits<sup>(1, 2)</sup>

Least Significant bits of the address at the end of the designated scan

Note 1: Registers SCANHADRU/H/L form a 22-bit value, but are not guarded for atomic or asynchronous access; registers should only be read or written while SGO = 0 (SCANCON0 register).

2: While SGO = 1 (SCANCON0 register), writing to this register is ignored.

## REGISTER 17-9: DMAxSPTRU – DMAx SOURCE POINTER UPPER REGISTER

|   | U-0   | U-0 | R-0 | R-0 | R-0    | R-0    | R-0 | R-0   |

|---|-------|-----|-----|-----|--------|--------|-----|-------|

|   | _     | _   |     |     | SPTR<2 | 21:16> |     |       |

| ſ | bit 7 |     |     |     |        |        |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n/n = Value at POR and 0 = bit is cleared 1 = bit is set x = bit is unknownu = bit is unchanged

BOR/Value at all other

Resets

bit 7-6 Unimplemented: Read as '0'

bit 5-0 SPTR<21:16>: Current Source Address Pointer

#### REGISTER 17-10: DMAxSSZL – DMAx SOURCE SIZE LOW REGISTER

| R/W-0/0 | R/W-0/0  | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |  |  |  |  |

|---------|----------|---------|---------|---------|---------|---------|---------|--|--|--|--|--|--|

|         | SSZ<7:0> |         |         |         |         |         |         |  |  |  |  |  |  |

| bit 7   |          |         |         |         |         |         |         |  |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n/n = Value at POR and 0 = bit is cleared 1 = bit is set x = bit is unknown

BOR/Value at all other u = bit is unchanged

Resets

bit 7-0 SSZ<7:0>: Source Message Size bits

#### REGISTER 17-11: DMAxSSZH – DMAx SOURCE SIZE HIGH REGISTER

|       | =   |     |     | J J     |         |         |         |

|-------|-----|-----|-----|---------|---------|---------|---------|

| U-0   | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

| _     | _   | _   | _   |         | SSZ<1   | 1:8>    |         |

| bit 7 |     |     |     |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n/n = Value at POR and 1 = bit is set 0 = bit is cleared x = bit is unknown

BOR/Value at all other u = bit is unchanged

Resets

bit 7-4 Unimplemented: Read as '0'

bit 3-0 SSZ<11:8>: Source Message Size bits

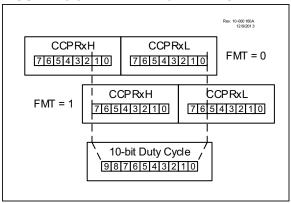

#### 25.4.5 PWM DUTY CYCLE

The PWM duty cycle is specified by writing a 10-bit value to the CCPRxH:CCPRxL register pair. The alignment of the 10-bit value is determined by the FMT bit of the CCPxCON register (see Figure 25-5). The CCPRxH:CCPRxL register pair can be written to at any time; however the duty cycle value is not latched into the 10-bit buffer until after a match between T2PR and T2TMR.

Equation 25-2 is used to calculate the PWM pulse width. Equation 25-3 is used to calculate the PWM duty cycle ratio.

#### FIGURE 25-5: PWM 10-BIT ALIGNMENT

#### **EQUATION 25-2: PULSE WIDTH**

Pulse Width = (CCPRxH:CCPRxL register pair) •

TOSC • (TMR2 Prescale Value)

#### **EQUATION 25-3: DUTY CYCLE RATIO**

$$Duty\ Cycle\ Ratio\ =\ \frac{(CCPRxH:CCPRxL\ register\ pair)}{4(T2PR+1)}$$

CCPRxH:CCPRxL register pair are used to double buffer the PWM duty cycle. This double buffering provides glitchless PWM operation.

The 8-bit timer T2TMR register is concatenated with either the 2-bit internal system clock (Fosc), or two bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2 prescaler is set to 1:1.

When the 10-bit time base matches the CCPRxH:CCPRxL register pair, then the CCPx pin is cleared (see Figure 25-4).

#### 25.4.6 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is ten bits when T2PR is 255. The resolution is a function of the T2PR register value as shown by Equation 25-4.

#### **EQUATION 25-4: PWM RESOLUTION**

Resolution =

$$\frac{log[4(T2PR+1)]}{log(2)}$$

bits

**Note:** If the pulse-width value is greater than the period, the assigned PWM pin(s) will remain unchanged.

## REGISTER 25-5: CCPRxH: CCPx REGISTER HIGH BYTE

| R/W-x/x |  |  |  |  |  |

|---------|---------|---------|---------|---------|---------|---------|---------|--|--|--|--|--|

|         | RH<7:0> |         |         |         |         |         |         |  |  |  |  |  |

| bit 7   |         |         |         |         |         |         |         |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-0 MODE = Capture Mode:

RH<7:0>: MSB of captured TMR1 value

MODE = Compare Mode:

RH<7:0>: MSB compared to TMR1 value

MODE = PWM Mode && FMT = 0:

RH<7:2>: Not used

RH<1:0>: CCPW<9:8> - Pulse-Width MS 2 bits

MODE = PWM Mode && FMT = 1:

RH<7:0>: CCPW<9:2> - Pulse-Width MS 8 bits

#### TABLE 25-5: SUMMARY OF REGISTERS ASSOCIATED WITH CCPx

| Name    | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3       | Bit 2      | Bit 1 | Bit 0 | Register on Page |  |  |

|---------|-------|-------|-------|-------|-------------|------------|-------|-------|------------------|--|--|

| CCPxCON | EN    | _     | OUT   | FMT   |             | MODE<3:0>  |       |       |                  |  |  |

| CCPxCAP | _     | _     | _     | _     | CTS<1:0>    |            |       |       |                  |  |  |

| CCPRxL  |       |       |       |       | CCPRx<7:0>  | CCPRx<7:0> |       |       |                  |  |  |

| CCPRxH  |       |       |       | (     | CCPRx<15:8> |            |       |       | 356              |  |  |

**Legend:** — = Unimplemented location, read as '0'. Shaded cells are not used by the CCP module.

PIC18(L)F24/25K42

# REGISTER 28-5: CWGxSTR<sup>(1)</sup>: CWG STEERING CONTROL REGISTER

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0             | R/W-0/0             | R/W-0/0             | R/W-0/0             |

|---------|---------|---------|---------|---------------------|---------------------|---------------------|---------------------|

| OVRD    | OVRC    | OVRB    | OVRA    | STRD <sup>(2)</sup> | STRC <sup>(2)</sup> | STRB <sup>(2)</sup> | STRA <sup>(2)</sup> |

| bit 7   |         |         |         |                     |                     |                     | bit 0               |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| =     |                                                                                      |

|-------|--------------------------------------------------------------------------------------|

| bit 7 | OVRD: Steering Data D bit                                                            |

| bit 6 | OVRC: Steering Data C bit                                                            |

| bit 5 | OVRB: Steering Data B bit                                                            |

| bit 4 | OVRA: Steering Data A bit                                                            |

| bit 3 | STRD: Steering Enable bit D <sup>(2)</sup>                                           |

|       | 1 = CWGxD output has the CWG data input waveform with polarity control from POLD bit |

|       | 0 = CWGxD output is assigned to value of OVRD bit                                    |

| bit 2 | STRC: Steering Enable bit C <sup>(2)</sup>                                           |

|       | 1 = CWGxC output has the CWG data input waveform with polarity control from POLC bit |

|       | 0 = CWGxC output is assigned to value of OVRC bit                                    |

| bit 1 | STRB: Steering Enable bit B <sup>(2)</sup>                                           |

|       | 1 = CWGxB output has the CWG data input waveform with polarity control from POLB bit |

|       | 0 = CWGxB output is assigned to value of OVRB bit                                    |

| bit 0 | STRA: Steering Enable bit A <sup>(2)</sup>                                           |

|       | 1 = CWGxA output has the CWG data input waveform with polarity control from POLA bit |

|       | 0 = CWGxA output is assigned to value of OVRA bit                                    |

|       |                                                                                      |

Note 1: The bits in this register apply only when MODE<2:0> = 00x (Register 28-1, Steering modes).

2: This bit is double-buffered when MODE<2:0> = 001.

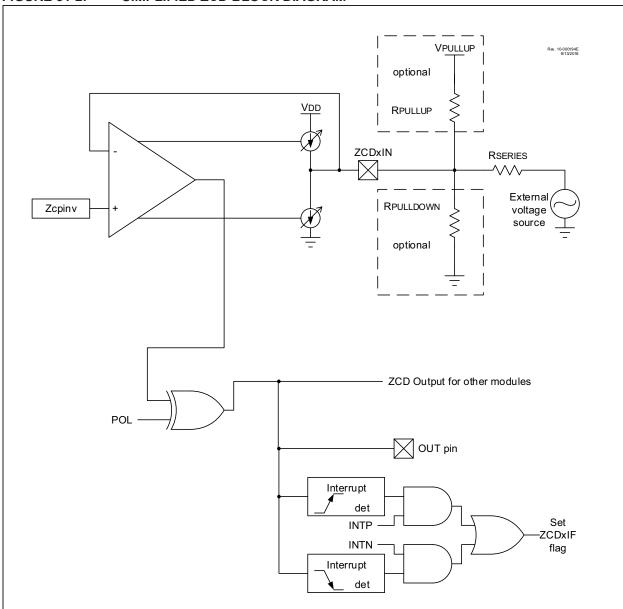

FIGURE 31-2: SIMPLIFIED ZCD BLOCK DIAGRAM

## 31.2 ZCD Logic Output

The ZCD module includes a Status bit, which can be read to determine whether the current source or sink is active. The OUT bit of the ZCDCON register is set when the current sink is active, and cleared when the current source is active. The OUT bit is affected by the polarity bit, even if the module is disabled.

The OUT signal can also be used as input to other modules. This is controlled by the registers of the corresponding module. OUT can be used as follows:

- · Gate source for TMR1/3/5

- · Clock source for TMR2/4/6

- · Reset source for TMR2/4/6

# 31.3 ZCD Logic Polarity

The POL bit of the ZCDCON register inverts the OUT bit relative to the current source and sink output. When the POL bit is set, a OUT high indicates that the current source is active, and a low output indicates that the current sink is active.

The POL bit affects the ZCD interrupts.

# PIC18(L)F24/25K42

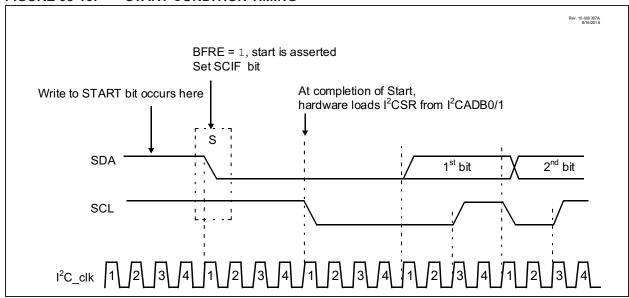

# 35.5.5 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

The user can initiate a Start condition by either writing to the Start bit (S) of the I2CxCON0 register or by writing to the I2CxTXB register based on the ABD bit setting. Master hardware waits for BFRE = 1, before

asserting the Start condition. The action of the SDA being driven low while SCL is high is the Start condition, causing the SCIF bit to be set. One TSCL later the SCL is asserted low, ending the start sequence. Figure 35-15 shows the Start condition timing.

## FIGURE 35-15: START CONDITION TIMING

# 35.5.6 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition occurs when the Start bit of the I2CxCON0 register is set and the master module is waiting from a Restart clock stretch event (RSEN = 1 and I2CxCNT = 0).

When the Start bit is set, the SDA pin is released high for TSCL/2. Then the SCL pin is released floated high) for TSCL/2. If the SDA pin is detected low, bus collision flag (BCLIF) is set and the master goes idle. If SDA is detected high, the SDA pin will be pulled low (Start condition) for TSCL. Last, SCL is asserted low and I2CxADB0/1 is loaded into the shift register. As soon as a Restart condition is detected on the SDA and SCL pins, the RSCIF bit is set. Figure 35-16 shows the timings for repeated Start Condition.

## REGISTER 38-36: ADCP: ADC CHARGE PUMP CONTROL REGISTER

| R/W-0/0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R-0/0 |

|---------|-----|-----|-----|-----|-----|-----|-------|

| CPON    | _   | _   | _   | _   | _   | _   | CPRDY |

| bit 7   |     |     |     |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared HS= Hardware set

bit 7 CPON: Charge Pump On Control bit

1 = Charge Pump On when requested by the ADC

0 = Charge Pump Off

bit 6-1 **Unimplemented:** Read as '0'

bit 0 CPRDY: Charge Pump Ready Status bit

1 = Charge Pump is ready

0 = Charge Pump is not ready (or never started)

## TABLE 38-6: SUMMARY OF REGISTERS ASSOCIATED WITH ADC

| Name    | Bit 7  | Bit 6            | Bit 5      | Bit 4                                          | Bit 3   | Bit 2 | Bit 1      | Bit 0  | Register on Page |

|---------|--------|------------------|------------|------------------------------------------------|---------|-------|------------|--------|------------------|

| ADCON0  | ON     | CONT             | _          | CS                                             | _       | FM    | _          | GO     | 621              |

| ADCON1  | ADPPOL | ADIPEN           | ADGPOL     | _                                              | _       | _     | _          | ADDSEN | 622              |

| ADCON2  | ADPSIS | A                | ADCRS<2:0> |                                                | ADACLR  |       | MD<2:0>    |        | 623              |

| ADCON3  | _      | А                | DCALC<2:0> | >                                              | ADSOI   |       | ADTMD<2:0> | •      | 624              |

| ADSTAT  | ADAOV  | ADUTHR           | ADLTHR     | ADMATH                                         |         | ADSTA | T<3:0>     |        | 625              |

| ADCLK   | _      | _                |            | CS<5:0>                                        |         |       |            | 626    |                  |

| ADREF   | _      | _                | _          | —         ADNREF         —         ADPREF<1:0> |         |       |            |        | 626              |

| ADPCH   | _      | _                |            | ADPCH<5:0>                                     |         |       |            |        |                  |

| ADPREL  |        |                  | PRE<7:0>   |                                                |         |       |            |        | 628              |

| ADPREH  | _      | _                | _          | — PRE<12:8>                                    |         |       |            |        |                  |

| ADACQL  |        |                  |            | ACQ<7:0>                                       |         |       |            |        |                  |

| ADCAP   | _      | — — — ADCAP<4:0> |            |                                                |         |       |            |        | 630              |

| ADRPT   |        |                  |            | RPT·                                           | <7:0>   |       |            |        | 630              |

| ADCNT   |        |                  |            | CNT                                            | <7:0>   |       |            |        | 631              |

| ADFLTRL |        |                  |            | FLTR                                           | <7:0>   |       |            |        | 631              |

| ADFLTRH |        |                  |            | FLTR                                           | <15:8>  |       |            |        | 631              |

| ADRESL  |        |                  |            | ADRES                                          | SL<7:0> |       |            |        | 632, 633         |

| ADRESH  |        |                  |            | ADRES                                          | SH<7:0> |       |            |        | 632, 633         |

| ADPREVH |        |                  |            | PREV-                                          | <15:8>  |       |            |        | 634              |

| ADPREVL |        |                  |            | PREV                                           | /<7:0>  |       |            |        | 634              |

| ADACCH  |        |                  |            | ACC<                                           | <15:8>  |       |            |        | 635              |

| ADACCL  |        |                  |            | ACC-                                           | <7:0>   |       |            |        | 635              |

| ADACCU  | _      | _                | _          | _                                              | _       | _     | ACC<       | 17:16> | 635              |

| ADSTPTL |        |                  |            | STPT                                           | <7:0>   |       |            |        | 636              |

| ADSTPTH |        |                  |            | STPT                                           | <15:8>  |       |            |        | 636              |

| ADERRL  |        |                  |            | ERR                                            | <7:0>   |       |            |        | 637              |

| ADERRH  |        |                  |            | ERR<                                           | :15:8>  |       |            |        | 637              |

#### REGISTER 41-2: HLVDCON0: HIGH/LOW-VOLTAGE DETECT CONTROL REGISTER 0

| R/W-0/0 | U-0 | R-x | R-x | U-0 | U-0 | R/W-0/0 | R/W-0/0 |

|---------|-----|-----|-----|-----|-----|---------|---------|

| EN      | _   | OUT | RDY | _   | _   | INTH    | INTL    |

| bit 7   |     |     |     |     |     |         | bit 0   |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 7 EN: High/Low-voltage Detect Power Enable bit

1 = Enables HLVD, powers up HLVD circuit and supporting reference circuitry

0 = Disables HLVD, powers down HLVD and supporting circuitry

bit 6 **Unimplemented:** Read as '0'

bit 5 OUT: HLVD Comparator Output bit

1 = Voltage ≤ selected detection limit (HLVDL<3:0>)

0 = Voltage ≥ selected detection limit (HLVDL<3:0>)

bit 4 RDY: Band Gap Reference Voltages Stable Status Flag bit

1 = Indicates HLVD Module is ready and output is stable

0 = Indicates HLVD Module is not ready

bit 3-2 Unimplemented: Read as '0'

bit 1 INTH: HLVD Positive going (High Voltage) Interrupt Enable

1 = HLVDIF will be set when voltage ≥ selected detection limit (SEL<3:0>)

0 = HLVDIF will not be set

bit 0 INTL: HLVD Negative going (Low Voltage) Interrupt Enable

1 = HLVDIF will be set when voltage ≤ selected detection limit (SEL<3:0>)

0 = HLVDIF will not be set

TABLE 41-2: SUMMARY OF REGISTERS ASSOCIATED WITH HIGH/LOW-VOLTAGE DETECT MODULE

| Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3    | Bit 2 | Bit 1 | Bit 0 | Register on Page |

|----------|-------|-------|-------|-------|----------|-------|-------|-------|------------------|

| HLVDCON0 | EN    | _     | OUT   | RDY   | -        | _     | INTH  | INTL  | 662              |

| HLVDCON1 | _     | _     | _     | -     | SEL<3:0> |       |       |       | 661              |

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the HLVD module.

| BNOV             | Branch if Not Overflow                                    |  |  |  |  |  |

|------------------|-----------------------------------------------------------|--|--|--|--|--|

| Syntax:          | BNOV n                                                    |  |  |  |  |  |

| Operands:        | $-128 \le n \le 127$                                      |  |  |  |  |  |

| Operation:       | if OVERFLOW bit is '0' (PC) + 2 + 2n $\rightarrow$ PC     |  |  |  |  |  |

| Status Affected: | None                                                      |  |  |  |  |  |

| Encoding:        | 1110 0101 nnnn nnnn                                       |  |  |  |  |  |

| Description:     | If the OVERFLOW bit is '0', then the program will branch. |  |  |  |  |  |

The 2's complement number '2n' is

added to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 2 + 2n. This instruction is then a

2-cycle instruction.

Words: 1 Cycles: 1(2)

Q Cycle Activity: If Jump:

|        | Q1        | Q2           | Q3        | Q4          |  |

|--------|-----------|--------------|-----------|-------------|--|

| Decode |           | Read literal | Process   | Write to PC |  |

|        |           | ʻn'          | Data      |             |  |

|        | No        | No           | No        | No          |  |

|        | operation | operation    | operation | operation   |  |

If No Jump:

| Q1     | Q2           | Q3      | Q4        |  |

|--------|--------------|---------|-----------|--|

| Decode | Read literal | Process | No        |  |

|        | ʻn'          | Data    | operation |  |

Example: HERE BNOV Jump Before Instruction

PC

After Instruction

If OVERFLOW =

address (Jump) If OVERFLOW =

address (HERE + 2)

address (HERE)

**BNZ Branch if Not Zero**

Syntax: BNZ n Operands:  $\text{-}128 \leq n \leq 127$ Operation: if ZERO bit is '0'

$(PC) + 2 + 2n \rightarrow PC$

Status Affected: None

Encoding: 1110 0001 nnnn

Description: If the ZERO bit is '0', then the program

will branch.

The 2's complement number '2n' is added to the PC. Since the PC will have

incremented to fetch the next instruction, the new address will be PC + 2 + 2n. This instruction is then a

2-cycle instruction.

Words: 1 Cycles: 1(2)

Q Cycle Activity: If Jump:

| Q1        | Q2                   | Q3        | Q4          |  |

|-----------|----------------------|-----------|-------------|--|

| Decode    | Read literal Process |           | Write to PC |  |

| 'n'       |                      | Data      |             |  |

| No        | No                   | No        | No          |  |

| operation | operation            | operation | operation   |  |

If No Jump:

| Q1     | Q2           | Q3      | Q4        |  |  |

|--------|--------------|---------|-----------|--|--|

| Decode | Read literal | Process | No        |  |  |

|        | ʻn'          | Data    | operation |  |  |

Example: HERE BNZ Jump

Before Instruction

PC address (HERE)

After Instruction

If ZERO

address (Jump)

=

address (HERE + 2)

TABLE 46-3: POWER-DOWN CURRENT (IPD) (1,2)

| PIC18LF24/25K42 |           |                                           | Standard Operating Conditions (unless otherwise stated)            |       |        |                     |       |                      |                       |

|-----------------|-----------|-------------------------------------------|--------------------------------------------------------------------|-------|--------|---------------------|-------|----------------------|-----------------------|

| PIC18F24/25K42  |           |                                           | Standard Operating Conditions (unless otherwise stated) VREGPM = 1 |       |        |                     |       |                      |                       |

| Param.          |           | Device Observatorists                     | B.41                                                               | T 4   | Max.   | Max.                | 1124  | Conditions           |                       |

| No.             | Symbol    | Device Characteristics                    | Min.                                                               | Typ.† | +85°C  | +125°C              | Units | VDD                  | Nøte                  |

| D200            | IPD       | IPD Base                                  | _                                                                  | 0.07  | 2      | 6                   | μΑ    | 3.0V                 |                       |

| D200            | IPD       | IPD Base                                  | _                                                                  | 0.4   | 4      | 6                   | μΑ    | 3.0V                 |                       |

| D200A           |           |                                           | _                                                                  | 20    | 38     | 42                  | μΑ    | 3.0V                 | VREGPM = 0            |

| D201            | IPD_WDT   | Low-Frequency Internal Oscillator/<br>WDT | _                                                                  | 0.9   | 3.2    | 6                   | μΑ    | 3.0V                 |                       |

| D201            | IPD_WDT   | Low-Frequency Internal Oscillator/<br>WDT | _                                                                  | 1.1   | 3.2    | 6                   | μА    | 3.0V                 |                       |

| D202            | IPD_SOSC  | Secondary Oscillator (Sosc)               | _                                                                  | 0.75  | 5      | 7                   | μΑ    | 3.00                 | LP mode               |

| D202            | IPD_SOSC  | Secondary Oscillator (Sosc)               | _                                                                  | 1.0   | 6.5    | 8                   | γμA   | 3.0V                 | LR mode               |

| D203            | IPD_FVR   | FVR                                       | _                                                                  | 37    | 51     | 55 〈                | μA    | 3:0V_                | FVRCON = 0x81 or 0x84 |

| D203            | IPD_FVR   | FVR                                       | _                                                                  | 30    | 44     | 48                  | \     | <b>3</b> .0 <b>Y</b> | FYRCON = 0x81 or 0x84 |

| D204            | IPD_BOR   | Brown-out Reset (BOR)                     | _                                                                  | 9.4   | 14     | 16                  | MA /  | 3.6V                 | ~                     |

| D204            | IPD_BOR   | Brown-out Reset (BOR)                     | _                                                                  | 9.4   | 15 <   | <b>1</b> 6          | μÀ    | \3.0V                |                       |

| D205            | IPD_LPBOR | Low-Power Brown-out Reset (LPBOR)         | _                                                                  | 0.2   | 3      | 6                   | μΑ    | 3.0V                 |                       |

| D205            | IPD_LPBOR | Low-Power Brown-out Reset (LPBOR)         | _                                                                  | 0.5   | /3     | 5                   | μA    | 3.0V                 |                       |

| D206            | IPD_HLVD  | High/Low Voltage Detect (HLVD)            | _                                                                  | 9.5   | 14.8 = | 18                  | μA    | 3.0V                 |                       |

| D206            | IPD_HLVD  | High/Low Voltage Detect (HLVD)            | _                                                                  | 9.7   | 14.2   | 17                  | μΑ    | 3.0V                 |                       |

| D207            | IPD_ADCA  | ADC - Active                              |                                                                    | 400   | 7      | $\langle - \rangle$ | μΑ    | 3.0V                 | ADC is converting (4) |

| D207            | IPD_ADCA  | ADC - Active                              | _                                                                  | 400   | /-/    |                     | μΑ    | 3.0V                 | ADC is converting (4) |

| D208            | IPD_CMP   | Comparator                                | 7                                                                  | / 33/ | 49     | 50                  | μΑ    | 3.0V                 |                       |

| D208            | IPD_CMP   | Comparator                                |                                                                    | 30    | 49     | 50                  | μΑ    | 3.0V                 |                       |

† Data in "Typ." column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral current is the sum of the base IDD and the additional current consumed when this peripheral is enabled. The peripheral  $\Delta$  current can be determined by subtracting the base IDD or IPD current from this limit. Max. values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode with all I/O pins in high-impedance state and tied to Vss.

3: All peripheral currents listed are on a per-peripheral basis if more than one instance of a peripheral is available.

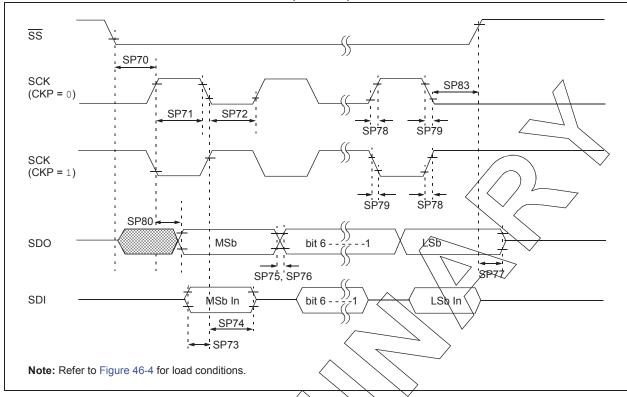

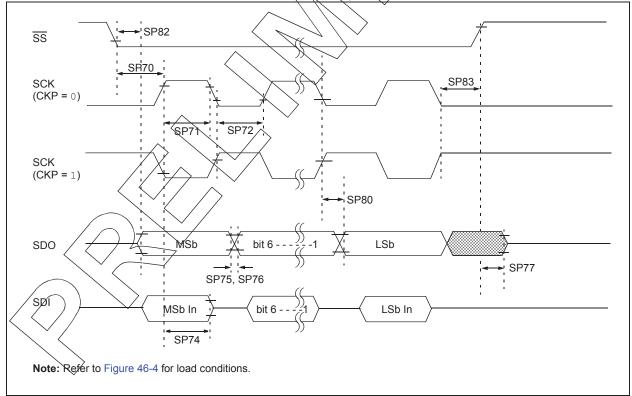

FIGURE 46-16: SPI SLAVE MODE TIMING (CKE = 0)

FIGURE 46-17: SPI SLAVE MODE TIMING (CKE = 1)

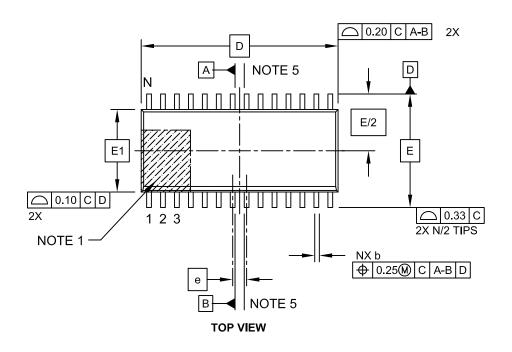

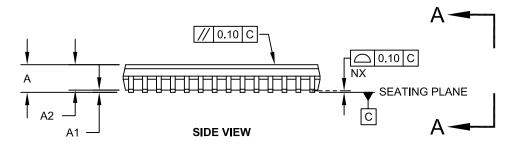

# 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-052C Sheet 1 of 2