#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                           |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f24k42-i-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Bank             | BSR<5:0>    | addr<7:0>     | PIC18(L)F24K42 | PIC18(L)F25K42 | Address<br>addr<13:0> |              |

|------------------|-------------|---------------|----------------|----------------|-----------------------|--------------|

|                  |             | 00h           | Access RAM     | Access RAM     | 0000h<br>005Fh        |              |

| Bank 0           | 00 0000     | FFh           | GPR            | GPR            | 0060h<br>00FFh        |              |

| Bank 1           | 00 0001     | 00h           | GPR            | GPR            | 0100h<br>•            |              |

|                  |             | FFh<br>00h    |                |                |                       |              |

| Bank 2           | 00 0010     | FFh           | GPR            | GPR            |                       |              |

| Bank 3           | 00 0011     | 00h<br>FFh    | GPR            | GPR            | •<br>•<br>03FFh       |              |

|                  | 00 0100     | 00h<br>•      |                |                | 0400h                 | Virtual Bank |

| Banks<br>4 to 7  |             | •             |                | GPR            | •                     | Access RAM   |

|                  |             | FFh<br>00h    | Unimplemented  |                | 07FFh<br>0800h        | SFR          |

| Banks<br>8 to 55 | 00 1000     | •             |                | Unimplemented  | •                     |              |

| 0.000            | 11 0111     | •<br>FFh      |                |                | •<br>37FFh            |              |

| Banks            | 11 1000     | 00h<br>•      |                |                | 3800h<br>•            |              |

| 56 to 62         | <br>11 1110 | •<br>•<br>FFh | SFR            | SFR            | •<br>•<br>3EFFh       |              |

|                  |             | 00h           |                |                | 3F00h                 | 1//          |

| Bank 63          | 11 1111     |               | SFR            | SFR            | 3F5Fh<br>3F60h        | ť /          |

# FIGURE 4-4: DATA MEMORY MAP FOR PIC18(L)F24/25K42 DEVICES

#### **Register Definitions: Status Registers** 4.6

| U-0                                                                | R-1/q                                                                                                                   | R-1/q                                | R/W-0/u         | R/W-0/u                             | R/W-0/u          | R/W-0/u         | R/W-0/u   |  |  |

|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------------|-------------------------------------|------------------|-----------------|-----------|--|--|

| _                                                                  | TO                                                                                                                      | PD                                   | Ν               | OV                                  | Z                | DC              | С         |  |  |

| pit 7                                                              |                                                                                                                         |                                      |                 |                                     |                  |                 | bit       |  |  |

|                                                                    |                                                                                                                         |                                      |                 |                                     |                  |                 |           |  |  |

| _egend:                                                            |                                                                                                                         |                                      |                 |                                     |                  |                 |           |  |  |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0' |                                                                                                                         |                                      |                 |                                     |                  |                 |           |  |  |

| n = Value at PC                                                    | R                                                                                                                       | '1' = Bit is set                     |                 | '0' = Bit is cle                    | ared             | x = Bit is unkr | IOWN      |  |  |

| pit 7                                                              | Unimplemen                                                                                                              | ted: Read as '                       | 0'              |                                     |                  |                 |           |  |  |

| -                                                                  | TO: Time-Out                                                                                                            |                                      | -               |                                     |                  |                 |           |  |  |

|                                                                    | •                                                                                                                       | wer-up or by e<br>me-out occurre     |                 | RWDT <b>or</b> SLEE                 | ₽ instruction    |                 |           |  |  |

|                                                                    | <b>PD</b> : Power-Do                                                                                                    |                                      | eu              |                                     |                  |                 |           |  |  |

|                                                                    | 1 = Set at power-up or by execution of CLRWDT instruction                                                               |                                      |                 |                                     |                  |                 |           |  |  |

|                                                                    | 0 = Set by ex                                                                                                           | ecution of the                       | SLEEP instruc   | tion                                |                  |                 |           |  |  |

|                                                                    | <b>N:</b> Negative bit used for signed arithmetic (2's complement); indicates if the result is negative, (ALU MSb = 1). |                                      |                 |                                     |                  |                 |           |  |  |

|                                                                    | 1 = The resul                                                                                                           |                                      |                 |                                     |                  |                 |           |  |  |

|                                                                    | 0 = The resul                                                                                                           |                                      |                 |                                     |                  |                 |           |  |  |

|                                                                    |                                                                                                                         |                                      |                 |                                     | nent); indicates | an overflow of  | the 7-bit |  |  |

|                                                                    | -                                                                                                                       |                                      |                 | 7) to change st<br>arithmetic oper  |                  |                 |           |  |  |

|                                                                    | 0 = No overfl                                                                                                           |                                      | 5 5 5           |                                     |                  |                 |           |  |  |

|                                                                    | Z: Zero bit                                                                                                             |                                      |                 |                                     |                  |                 |           |  |  |

|                                                                    |                                                                                                                         | lt of an arithme<br>It of an arithme |                 | eration is zero<br>eration is not z | ero              |                 |           |  |  |

|                                                                    |                                                                                                                         |                                      |                 |                                     | F instructions)  | 1)              |           |  |  |

|                                                                    | 1 = A carry-o                                                                                                           | ut from the 4th                      | low-order bit   | of the result or                    |                  |                 |           |  |  |

|                                                                    |                                                                                                                         | out from the 4                       |                 |                                     |                  |                 |           |  |  |

|                                                                    |                                                                                                                         |                                      |                 | w, SUBWF instrubits of the result   |                  |                 |           |  |  |

|                                                                    |                                                                                                                         |                                      |                 |                                     |                  |                 |           |  |  |

|                                                                    | 0 = No carry-                                                                                                           | out from the N                       | lost Significan | t bit of the resu                   | It occurred      |                 |           |  |  |

2: For Rotate (RRF, RLF) instructions, this bit is loaded with either the high or low-order bit of the Source register.

| Name    | Bit 7   | Bit 6   | Bit 5        | Bit 4 | Bit 3  | Bit 2     | Bit 1 | Bit 0 | Register<br>on Page |  |

|---------|---------|---------|--------------|-------|--------|-----------|-------|-------|---------------------|--|

| OSCCON1 |         | N       | OSC<2:0>     |       |        | NDIV<3:0> |       |       |                     |  |

| OSCCON2 | —       | С       | OSC<2:0>     |       |        | CDIV<3:0> |       |       |                     |  |

| OSCCON3 | CSWHOLD | SOSCPWR |              | ORDY  | NOSCR  | _         | _     | _     | 110                 |  |

| OSCSTAT | EXTOR   | HFOR    | MFOR         | LFOR  | SOR    | ADOR      | _     | PLLR  | 111                 |  |

| OSCTUNE | _       | —       | TUN<5:0>     |       |        |           |       |       | 113                 |  |

| OSCFRQ  | —       | —       | — — FRQ<3:0> |       |        |           | 3:0>  |       | 112                 |  |

| OSCEN   | EXTOEN  | HFOEN   | MFOEN        | LFOEN | SOSCEN | ADOEN     | —     | _     | 114                 |  |

TABLE 9-3:

SUMMARY OF REGISTERS ASSOCIATED WITH CLOCK SOURCES

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

## TABLE 9-4:SUMMARY OF CONFIGURATION WORD WITH CLOCK SOURCES

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5   | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1    | Bit 8/0  | Register<br>on Page |

|---------|------|---------|---------|------------|----------|----------|----------|------------|----------|---------------------|

| CONFIG1 | 13:8 | —       |         | FCMEN      | _        | CSWEN    |          | _          | CLKOUTEN | 71                  |

| CONFIGT | 7:0  | —       | F       | RSTOSC<2:0 | >        | _        | F        | EXTOSC<2:0 | >        | 1                   |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

# 15.1 Program Flash Memory

The Program Flash Memory is readable, writable and erasable during normal operation over the entire VDD range.

A read from program memory is executed one byte at a time. A write to program memory or program memory erase is executed on blocks of n bytes at a time. Refer to Table 15-2 for write and erase block sizes. A Bulk Erase operation cannot be issued from user code.

Writing or erasing program memory will cease instruction fetches until the operation is complete. The program memory cannot be accessed during the write or erase, therefore, code cannot execute. An internal programming timer terminates program memory writes and erases.

A value written to program memory does not need to be a valid instruction. Executing a program memory location that forms an invalid instruction results in a NOP.

It is important to understand the PFM memory structure for erase and programming operations. Program memory word size is 16 bits wide. PFM is arranged in rows. A row is the minimum size that can be erased by user software. Refer to Table 15-2 for the row sizes for the these devices.

After a row has been erased, all or a portion of this row can be programmed. Data to be written into the program memory row is written to 8-bit wide data write latches by means of 6 address lines. These latches are not directly accessible, but may be loaded via sequential writes to the TABLAT register.

**Note:** To modify only a portion of a previously programmed row, then the contents of the entire row must be read and saved in RAM prior to the erase. Then, the new data and retained data can be written into the write latches to reprogram the row of PFM. However, any unprogrammed locations can be written without first erasing the row. In this case, it is not necessary to save and rewrite the other previously programmed locations

|  | TABLE 15-2: | FLASH MEMORY ORGANIZATION BY DEVICE |

|--|-------------|-------------------------------------|

|--|-------------|-------------------------------------|

| Device         | Row Erase Size<br>(Words) | Write Latches<br>(Words) | Program Flash<br>Memory (Words) | Data Memory (Bytes) |  |

|----------------|---------------------------|--------------------------|---------------------------------|---------------------|--|

| PIC18(L)F24K42 | 32                        | 64                       | 8192                            | 256                 |  |

| PIC18(L)F25K42 | 32                        | 64                       | 16384                           | 200                 |  |

## 15.3.5 WRITE VERIFY

;

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

## EXAMPLE 15-5: DATA EEPROM READ

| Data | Memory Addres | s to read   |   |                          |

|------|---------------|-------------|---|--------------------------|

|      | CLRF          | NVMCON1     | ; | Setup Data EEPROM Access |

|      | MOVF          | EE_ADDRL, W | ; |                          |

|      | MOVWF         | NVMADRL     | ; | Setup Address            |

|      | BSF           | NVMCON1, RD | ; | Issue EE Read            |

|      | MOVF          | NVMDAT, W   | ; | W = EE_DATA              |

## EXAMPLE 15-6: DATA EEPROM WRITE

| ; Data Mem  | ory Addres | s to write | 9    |   |       |       |        |       |   |  |  |

|-------------|------------|------------|------|---|-------|-------|--------|-------|---|--|--|

|             | CLRF       | NVMCON1    |      | ; | Setup | Data  | EEPROM | Acces | s |  |  |

|             | MOVF       | EE_ADDRL,  | W    | ; |       |       |        |       |   |  |  |

|             | MOVWF      | NVMADRL    |      | ; | Setup | Addre | SS     |       |   |  |  |

| ; Data Mem  | ory Value  | to write   |      |   |       |       |        |       |   |  |  |

|             | MOVF       | EE_DATA,   | W    | ; |       |       |        |       |   |  |  |

|             | MOVWF      | NVMDAT     |      | ; |       |       |        |       |   |  |  |

| ; Enable w  | rites      |            |      |   |       |       |        |       |   |  |  |

|             | BSF        | NVMCON1,   | WREN | ; |       |       |        |       |   |  |  |

| ; Disable   | interrupts |            |      |   |       |       |        |       |   |  |  |

|             | BCF        | INTCON0,   | GIE  | ; |       |       |        |       |   |  |  |

| ; Required  | unlock se  | quence     |      |   |       |       |        |       |   |  |  |

|             | MOVLW      | 55h        |      | ; |       |       |        |       |   |  |  |

|             | MOVWF      | NVMCON2    |      | ; |       |       |        |       |   |  |  |

|             | MOVLW      | AAh        |      | ; |       |       |        |       |   |  |  |

|             | MOVWF      | NVMCON2    |      | ; |       |       |        |       |   |  |  |

| ; Set WR b  | it to begi | n write    |      |   |       |       |        |       |   |  |  |

|             | BSF        | NVMCON1,   | WR   | ; |       |       |        |       |   |  |  |

| ; Enable II | TN         |            |      |   |       |       |        |       |   |  |  |

|             | BSF        | INTCON0,   | GIE  | ; |       |       |        |       |   |  |  |

| ; Wait for  | interrupt  | , write do | one  |   |       |       |        |       |   |  |  |

|             | SLEEP      |            |      | ; |       |       |        |       |   |  |  |

| ; Disable   | writes     |            |      |   |       |       |        |       |   |  |  |

|             | BCF        | NVMCON1,   | WREN | ; |       |       |        |       |   |  |  |

|             |            |            |      |   |       |       |        |       |   |  |  |

## 15.3.6 OPERATION DURING CODE-PROTECT

Data EEPROM Memory has its own code-protect bits in Configuration Words. External read and write operations are disabled if code protection is enabled.

If the Data EEPROM is write-protected or if NVMADR points an invalid address location, the WR bit is cleared without any effect. WRERR is signaled in this scenario.

## 15.3.7 PROTECTION AGAINST SPURIOUS WRITE

There are conditions when the user may not want to write to the Data EEPROM Memory. To protect against spurious EEPROM writes, various mechanisms have been implemented. On power-up, the WREN bit is cleared. In addition, writes to the EEPROM are blocked during the Power-up Timer period (TPWRT).

The unlock sequence and the WREN bit together help prevent an accidental write during brown-out, power glitch or software malfunction.

## REGISTER 16-9: CRCXORH: CRC XOR HIGH BYTE REGISTER

| R/W-x/x         | R/W-x/x                           | R/W-x/x         | R/W-x/x | R/W-x/x                                               | R/W-x/x | R/W-x/x | R/W-x/x |  |  |

|-----------------|-----------------------------------|-----------------|---------|-------------------------------------------------------|---------|---------|---------|--|--|

|                 |                                   |                 | Χ<′     | 5:8>                                                  |         |         |         |  |  |

| bit 7           |                                   |                 |         |                                                       |         |         | bit 0   |  |  |

|                 |                                   |                 |         |                                                       |         |         |         |  |  |

| Legend:         |                                   |                 |         |                                                       |         |         |         |  |  |

| R = Readable    | R = Readable bit W = Writable bit |                 |         | U = Unimplemented bit, read as '0'                    |         |         |         |  |  |

| u = Bit is unch | anged                             | x = Bit is unkr | nown    | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |  |

bit 7-0 X<15:8>: XOR of Polynomial Term X<sup>n</sup> Enable bits

# REGISTER 16-10: CRCXORL: CRC XOR LOW BYTE REGISTER

'0' = Bit is cleared

| R/W-x/x | U-1   |

|---------|---------|---------|---------|---------|---------|---------|-------|

|         |         |         | X<7:1>  |         |         |         | —     |

| bit 7   |         |         |         |         |         |         | bit 0 |

|         |         |         |         |         |         |         |       |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit                                 |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-1 X<7:1>: XOR of Polynomial Term X<sup>n</sup> Enable bits

bit 0 Unimplemented: Read as '1'

'1' = Bit is set

| R/W-1/1          | R/W-1/1       | R/W-1/1           | R/W-1/1     | R/W-1/1                            | R/W-1/1 | R/W-1/1 | R/W-1/1 |  |

|------------------|---------------|-------------------|-------------|------------------------------------|---------|---------|---------|--|

| SLRx7            | SLRx6         | SLRx5             | SLRx4       | SLRx3                              | SLRx2   | SLRx1   | SLRx0   |  |

| bit 7            |               |                   |             |                                    |         |         | bit 0   |  |

|                  |               |                   |             |                                    |         |         |         |  |

| Legend:          |               |                   |             |                                    |         |         |         |  |

| R = Readable     | bit           | W = Writable      | bit         | U = Unimplemented bit, read as '0' |         |         |         |  |

| '1' = Bit is set |               | '0' = Bit is clea | ared        | x = Bit is unkr                    | nown    |         |         |  |

| -n/n = Value at  | t POR and BOR | R/Value at all of | ther Resets |                                    |         |         |         |  |

## REGISTER 18-7: SLRCONX: SLEW RATE CONTROL REGISTER

bit 7-0

- SLRx<7:0>: Slew Rate Control on Pins Rx<7:0>, respectively

- 1 = Port pin slew rate is limited

- 0 = Port pin slews at maximum rate

## TABLE 18-7: SLEW RATE CONTROL REGISTERS

| Name    | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| SLRCONA | SLRA7 | SLRA6 | SLRA5 | SLRA4 | SLRA3 | SLRA2 | SLRA1 | SLRA0 |

| SLRCONB | SLRB7 | SLRB6 | SLRB5 | SLRB4 | SLRB3 | SLRB2 | SLRB1 | SLRB0 |

| SLRCONC | SLRC7 | SLRC6 | SLRC5 | SLRC4 | SLRC3 | SLRC2 | SLRC1 | SLRC0 |

# 20.6 Register Definitions: Interrupt-on-Change Control

| R/W-0/0           | R/W-0/0                                 | R/W-0/0            | R/W-0/0 | R/W-0/0                                               | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|-------------------|-----------------------------------------|--------------------|---------|-------------------------------------------------------|---------|---------|---------|--|

| IOCxP7            | IOCxP6                                  | IOCxP5             | IOCxP4  | IOCxP3                                                | IOCxP2  | IOCxP1  | IOCxP0  |  |

| bit 7             |                                         |                    |         |                                                       |         |         | bit 0   |  |

| •                 |                                         |                    |         |                                                       |         |         |         |  |

| Legend:           |                                         |                    |         |                                                       |         |         |         |  |

| R = Readable bi   | t                                       | W = Writable bi    | t       | U = Unimplemented bit, read as '0'                    |         |         |         |  |

| u = Bit is unchar | u = Bit is unchanged x = Bit is unknown |                    |         | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |

| '1' = Bit is set  |                                         | '0' = Bit is clear | ed      |                                                       |         |         |         |  |

## **REGISTER 20-1:** IOCxP: INTERRUPT-ON-CHANGE POSITIVE EDGE REGISTER EXAMPLE

bit 7-0

IOCxP<7:0>: Interrupt-on-Change Positive Edge Enable bits

1 = Interrupt-on-Change enabled on the IOCx pin for a positive-going edge. Associated Status bit and interrupt flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin.

## REGISTER 20-2: IOCxN: INTERRUPT-ON-CHANGE NEGATIVE EDGE REGISTER EXAMPLE

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| IOCxN7  | IOCxN6  | IOCxN5  | IOCxN4  | IOCxN3  | IOCxN2  | IOCxN1  | IOCxN0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

IOCxN<7:0>: Interrupt-on-Change Negative Edge Enable bits

1 = Interrupt-on-Change enabled on the IOCx pin for a negative-going edge. Associated Status bit and interrupt flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin

## REGISTER 20-3: IOCxF: INTERRUPT-ON-CHANGE FLAG REGISTER EXAMPLE

| R/W/HS-0/0 |

|------------|------------|------------|------------|------------|------------|------------|------------|

| IOCxF7     | IOCxF6     | IOCxF5     | IOCxF4     | IOCxF3     | IOCxF2     | IOCxF1     | IOCxF0     |

| bit 7      |            |            |            |            |            |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 7-0

IOCxF<7:0>: Interrupt-on-Change Flag bits

1 = A enabled change was detected on the associated pin. Set when IOCP[n] = 1 and a positive edge was detected on the IOCn pin, or when IOCN[n] = 1 and a negative edge was detected on the IOCn pin

0 = No change was detected, or the user cleared the detected change

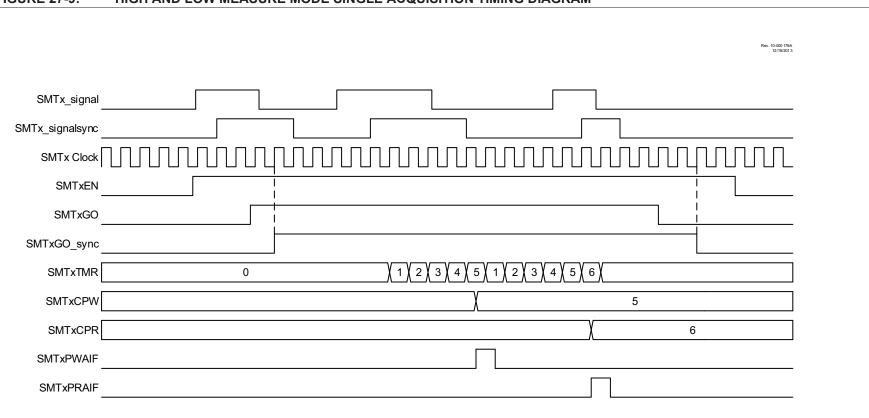

# FIGURE 27-9: HIGH AND LOW MEASURE MODE SINGLE ACQUISITION TIMING DIAGRAM

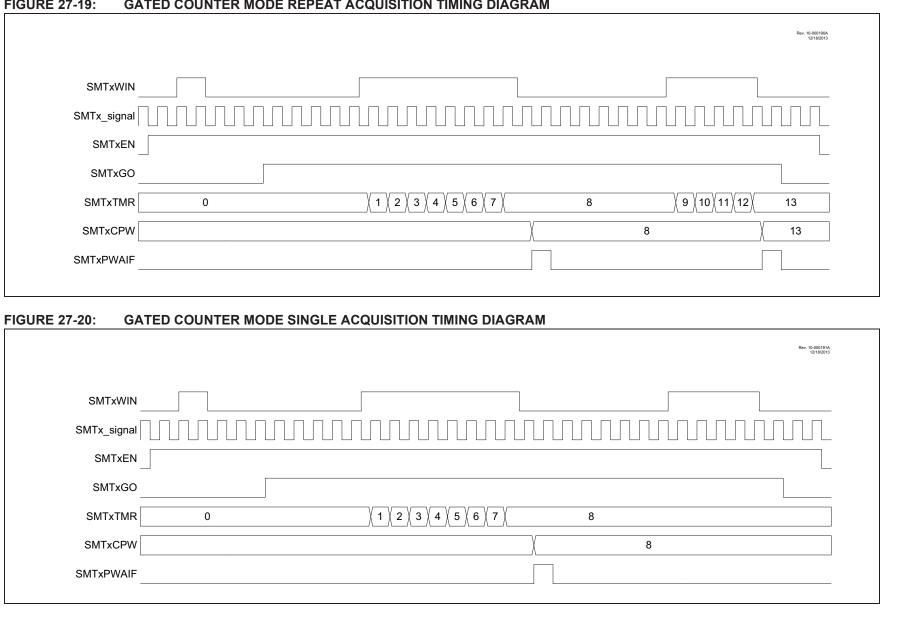

#### FIGURE 27-19: GATED COUNTER MODE REPEAT ACQUISITION TIMING DIAGRAM

Preliminary

| R/W-0/0          | R/W-0/0            | R/W-0/0           | R/W-0/0                              | R/W-0/0                                           | R/W-0/0             | R/W-0/0             | R/W-0/0             |  |  |

|------------------|--------------------|-------------------|--------------------------------------|---------------------------------------------------|---------------------|---------------------|---------------------|--|--|

| OVRD             | OVRC               | OVRB              | OVRA                                 | STRD <sup>(2)</sup>                               | STRC <sup>(2)</sup> | STRB <sup>(2)</sup> | STRA <sup>(2)</sup> |  |  |

| bit 7            |                    |                   | •                                    |                                                   |                     |                     | bit C               |  |  |

|                  |                    |                   |                                      |                                                   |                     |                     |                     |  |  |

| Legend:          |                    |                   |                                      |                                                   |                     |                     |                     |  |  |

| R = Readable     |                    | W = Writable      |                                      | U = Unimplemented bit, read as '0'                |                     |                     |                     |  |  |

| u = Bit is uncl  | 0                  | x = Bit is unkr   |                                      | -n/n = Value at POR and BOR/Value at all other Re |                     |                     |                     |  |  |

| '1' = Bit is set |                    | '0' = Bit is cle  | eared q = Value depends on condition |                                                   |                     |                     |                     |  |  |

| <b>b</b> :+ 7    |                    | ring Data D bit   |                                      |                                                   |                     |                     |                     |  |  |

| bit 7            |                    | ring Data D bit   |                                      |                                                   |                     |                     |                     |  |  |

| bit 6            |                    | ring Data C bit   |                                      |                                                   |                     |                     |                     |  |  |

| bit 5            |                    | ring Data B bit   |                                      |                                                   |                     |                     |                     |  |  |

| bit 4            |                    | ring Data A bit   |                                      |                                                   |                     |                     |                     |  |  |

| bit 3            |                    | ing Enable bit D  |                                      |                                                   |                     |                     |                     |  |  |

|                  |                    | output has the    |                                      |                                                   | th polarity contr   | ol from POLD        | bit                 |  |  |

|                  |                    | output is assigr  |                                      | OVRD bit                                          |                     |                     |                     |  |  |

| bit 2            | STRC: Steer        | ing Enable bit C  | ;(2)                                 |                                                   |                     |                     |                     |  |  |

|                  | 1 = CWGxC          | output has the    | CWG data inp                         | ut waveform wi                                    | th polarity contr   | ol from POLC        | bit                 |  |  |

|                  | 0 = CWGxC          | output is assigr  | ed to value of                       | OVRC bit                                          |                     |                     |                     |  |  |

| bit 1            | STRB: Steer        | ing Enable bit E  | 3(2)                                 |                                                   |                     |                     |                     |  |  |

|                  | 1 = CWGxB          | output has the    | CWG data inpu                        | ut waveform wi                                    | th polarity contr   | ol from POLB I      | oit                 |  |  |

|                  | 0 = CWGxB          | output is assign  | ed to value of                       | OVRB bit                                          |                     |                     |                     |  |  |

| bit 0            | STRA: Steer        | ing Enable bit A  | (2)                                  |                                                   |                     |                     |                     |  |  |

|                  | 1 = CWGxA          | output has the    | CWG data inpi                        | ut waveform wi                                    | th polarity contr   | ol from POLA I      | oit                 |  |  |

|                  | 0 = CWGxA          | output is assigr  | ed to value of                       | OVRA bit                                          |                     |                     |                     |  |  |

| Note 1: Th       | e bits in this reg | gister apply only | when MODE                            | <2:0> = 00x (R                                    | egister 28-1, St    | eering modes)       |                     |  |  |

| 2. Th            | ia hit ia daubla   | hufforod when I   | VODE - 2005 -                        | 0.0.1                                             |                     |                     |                     |  |  |

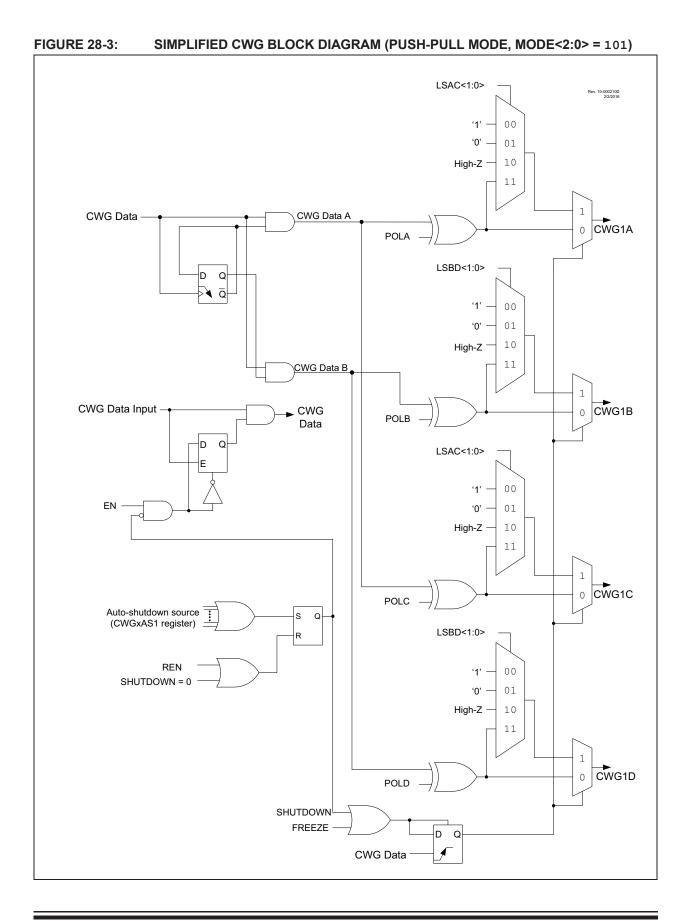

# REGISTER 28-5: CWGxSTR<sup>(1)</sup>: CWG STEERING CONTROL REGISTER

**2:** This bit is double-buffered when MODE < 2:0 > = 0.01.

# 31.0 ZERO-CROSS DETECTION (ZCD) MODULE

The ZCD module detects when an A/C signal crosses through the ground potential. The actual zero-crossing threshold is the zero-crossing reference voltage, VCPINV, which is typically 0.75V above ground.

The connection to the signal to be detected is through a series current-limiting resistor. The module applies a current source or sink to the ZCD pin to maintain a constant voltage on the pin, thereby preventing the pin voltage from forward biasing the ESD protection diodes. When the applied voltage is greater than the reference voltage, the module sinks current. When the applied voltage is less than the reference voltage, the module sources current. The current source and sink action keeps the pin voltage constant over the full range of the applied voltage. The ZCD module is shown in the simplified block diagram Figure 31-2.

The ZCD module is useful when monitoring an A/C waveform for, but not limited to, the following purposes:

- A/C period measurement

- Accurate long term time measurement

- Dimmer phase delayed drive

- Low EMI cycle switching

# 31.1 External Resistor Selection

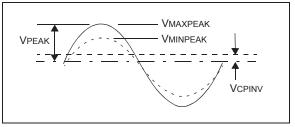

The ZCD module requires a current-limiting resistor in series with the external voltage source. The impedance and rating of this resistor depends on the external source peak voltage. Select a resistor value that will drop all of the peak voltage when the current through the resistor is nominally 300  $\mu$ A. Refer to Equation 31-1 and Figure 31-1. Make sure that the ZCD I/O pin internal weak pull-up is disabled so it does not interfere with the current source and sink.

# EQUATION 31-1: EXTERNAL RESISTOR

$$RSERIES = \frac{V_{PEAK}}{3 \times 10^{-4}}$$

FIGURE 31-1: EXTERNAL VOLTAGE

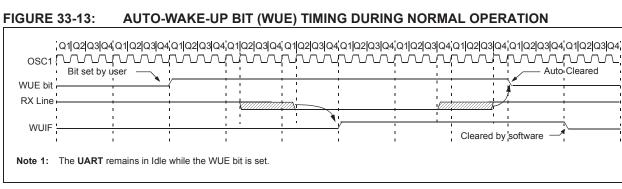

# FIGURE 33-14: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING SLEEP

**<sup>2:</sup>** The **UART** remains in Idle while the WUE bit is set.

# 33.18 Transmitting a Break

The UART module has the capability of sending either a fixed length Break period or a software timed Break period. The fixed length Break consists of a Start bit, followed by 12 '0' bits and a Stop bit. The software timed Break is generated by setting and clearing the BRKOVR bit in the UxCON1 register.

To send the fixed length Break, set the SENDB and TXEN bits in the UxCON0 register. The Break sequence is then initiated by a write to UxTXB. The timed Break will occur first, followed by the character written to UxTXB that initiated the Break. The initiating character is typically the Sync character of the LIN specification.

SENB is disabled in the LIN and DMX modes because those modes generate the Break sequence automatically.

The SENDB bit is automatically reset by hardware after the Break Stop bit is complete.

The TXMTIF bit in the UxERRIR register indicates when the transmit operation is active or idle, just as it does during normal transmission. See Figure 33-15 for the timing of the Break sequence.

# 33.19 Receiving a Break

The UART has counters to detect when the RX input remains in the space state for an extended period of time. When this happens, the RXBKIF bit in the UxERRIR register is set.

A Break is detected when the RX input remains in the space state for 11 bit periods for asynchronous and LIN modes, and 23 bit periods for DMX mode.

The user can select to receive the Break interrupt as soon as the Break is detected or at the end of the Break, when the RX input returns to the Idle state. When the RXBIMD bit in the UxCON1 is '1' then RXBKIF is set immediately upon Break detection. When RXBIMD is '0' then RXBKIF is set when the RX input returns to the Idle state.

# 33.20 UART Operation During Sleep

The UART ceases to operate during Sleep. The safe way to wake the device from Sleep by a serial operation is to use the Wake-on-Break feature of the UART. See Section 33.17.3, Auto-Wake-up on Break

| U-0              | U-0            | U-0                 | U-0               | U-0            | U-0              | U-0              | R/W-0/0          |

|------------------|----------------|---------------------|-------------------|----------------|------------------|------------------|------------------|

| —                | —              | —                   | —                 | _              | _                | —                | P1<8>            |

| bit 7            |                |                     |                   |                |                  |                  | bit 0            |

|                  |                |                     |                   |                |                  |                  |                  |

| Legend:          |                |                     |                   |                |                  |                  |                  |

| R = Readable     | bit            | W = Writable        | bit               | U = Unimpler   | mented bit, read | as '0'           |                  |

| u = Bit is uncha | anged          | x = Bit is unkr     | nown              | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets      |

| '1' = Bit is set |                | '0' = Bit is clea   | ared              |                |                  |                  |                  |

| hit 7 G          | Unimalaman     | ted. Dood oo f      | <u>`</u>          |                |                  |                  |                  |

| bit 7-6          | Unimplemen     | ted: Read as '      | J                 |                |                  |                  |                  |

| bit 0            | P1<8>: Most    | Significant Bit     | of Parameter      | 1              |                  |                  |                  |

|                  | DMX mode:      |                     |                   |                |                  |                  |                  |

|                  | Most Significa | int bit of numbe    | r of bytes to tra | ansmit betwee  | n Start Code and | d automatic Bre  | eak generation   |

|                  | DALI Control   | Device mode:        |                   |                |                  |                  |                  |

|                  | Most Significa | int bit of idle tim | ie delay after v  | which a Forwar | d Frame is sent. | Measured in h    | nalf-bit periods |

|                  | DALI Control   | <u>Gear mode</u> :  |                   |                |                  |                  |                  |

|                  | Most Significa | ant bit of delay    | between the e     | end of a Forwa | rd Frame and th  | e start of the E | Back Frame       |

|                  | Measured in h  | nalf-bit periods    |                   |                |                  |                  |                  |

|                  | Other modes:   |                     |                   |                |                  |                  |                  |

|                  | Not used       |                     |                   |                |                  |                  |                  |

|                  |                |                     |                   |                |                  |                  |                  |

|                  |                |                     |                   |                |                  |                  |                  |

## REGISTER 33-12: UxP1H: UART PARAMETER 1 HIGH REGISTER

## REGISTER 33-13: UxP1L: UART PARAMETER 1 LOW REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | P1<     | 7:0>    |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

|         |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 P

P1<7:0>: Least Significant Bits of Parameter 1

DMX mode:

Least Significant Byte of number of bytes to transmit between Start Code and automatic Break generation

DALI Control Device mode:

Least Significant Byte of idle time delay after which a Forward Frame is sent. Measured in half-bit periods DALI Control Gear mode:

Least Significant Byte of delay between the end of a Forward Frame and the start of the Back Frame Measured in half-bit periods

LIN mode:

PID to transmit (Only Least Significant 6 bits used) <u>Asynchronous Address mode:</u> Address to transmit (9th transmit bit automatically set to '1') <u>Other modes</u>: Not used

|              |              | R/W-0/0                                                        | R/W-0/0                                                            | R/W-0/0                                                                                  | R/W-0/0                                                                                                        |

|--------------|--------------|----------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

|              | TXCH         | K<7:0>                                                         |                                                                    |                                                                                          |                                                                                                                |

|              |              |                                                                |                                                                    |                                                                                          | bit 0                                                                                                          |

|              |              |                                                                |                                                                    |                                                                                          |                                                                                                                |

|              |              |                                                                |                                                                    |                                                                                          |                                                                                                                |

| W = Writat   | ole bit      | U = Unimplen                                                   | nented bit, read                                                   | as '0'                                                                                   |                                                                                                                |

| x = Bit is u | nknown       | -n/n = Value a                                                 | at POR and BO                                                      | R/Value at all o                                                                         | ther Resets                                                                                                    |

| '0' = Bit is | cleared      |                                                                |                                                                    |                                                                                          |                                                                                                                |

|              | x = Bit is u | W = Writable bit<br>x = Bit is unknown<br>'0' = Bit is cleared | W = Writable bit U = Unimplen<br>x = Bit is unknown -n/n = Value a | W = Writable bitU = Unimplemented bit, readx = Bit is unknown-n/n = Value at POR and BOI | W = Writable bitU = Unimplemented bit, read as '0'x = Bit is unknown-n/n = Value at POR and BOR/Value at all o |

## REGISTER 33-18: UxTXCHK: UART TRANSMIT CHECKSUM RESULT REGISTER

| bit 7-0 | TXCHK<7:0>: Checksum calculated from TX bytes |  |  |  |  |

|---------|-----------------------------------------------|--|--|--|--|

|         | LIN mode and COEN = 1:                        |  |  |  |  |

|         | Sum of all transmitted bytes including PID    |  |  |  |  |

|         | LIN mode and COEN = 0:                        |  |  |  |  |

|         | Sum of all transmitted bytes except PID       |  |  |  |  |

|         | All other modes and COEN = 1:                 |  |  |  |  |

|         | Sum of all transmitted bytes since last clear |  |  |  |  |

|         | All other modes and COEN = 0:                 |  |  |  |  |

|         | Not used                                      |  |  |  |  |

# REGISTER 33-19 UXRXCHK: UART RECEIVE CHECKSUM RESULT REGISTER

| ILEOID I EIL 3 | 0-13. OXIV. |         |         |         |         | OTER    |         |  |  |

|----------------|-------------|---------|---------|---------|---------|---------|---------|--|--|

| R/W-0/0        | R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |

| RXCHK<7:0>     |             |         |         |         |         |         |         |  |  |

| bit 7          |             |         |         |         |         |         | bit 0   |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

RXCHK<7:0>: Checksum calculated from RX bytes

LIN mode and COEN = 1:

Sum of all received bytes including PID

LIN mode and COEN = 0:

Sum of all received bytes except PID

All other modes and COEN = 1:

Sum of all received bytes since last clear

All other modes and COEN = 0:

Not used

© 2016-2017 Microchip Technology Inc.

## 40.7 Comparator Response Time

The comparator output is indeterminate for a period of time after the change of an input source or the selection of a new reference voltage. This period is referred to as the response time. The response time of the comparator differs from the settling time of the voltage reference. Therefore, both of these times must be considered when determining the total response time to a comparator input change. See the Comparator and Voltage Reference Specifications in Table 46-15 and Table 46-17 for more details.

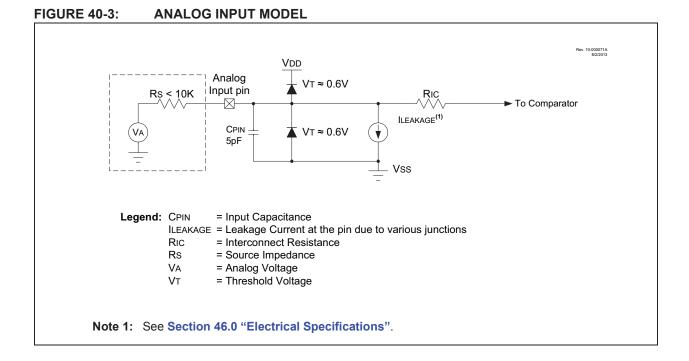

# 40.8 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 40-3. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and VSS. The analog input, therefore, must be between VSS and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

# PIC18(L)F24/25K42

| Mnemonic,                                |                                 | Description                               | Cycles     | 16-  | Bit Inst | ruction V | Vord | Status          | Natas |

|------------------------------------------|---------------------------------|-------------------------------------------|------------|------|----------|-----------|------|-----------------|-------|

| Opera                                    | nds                             | Description                               | Cycles     | MSb  |          |           | LSb  | Affected        | Notes |

| BYTE-ORIENTED FILE REGISTER INSTRUCTIONS |                                 |                                           |            |      |          |           |      |                 |       |

| ADDWF                                    | f, d ,a                         | Add WREG and f                            | 1          | 0010 | 01da     | ffff      | ffff | C, DC, Z, OV, N |       |

| ADDWFC                                   | f, d, a                         | Add WREG and Carry bit to f               | 1          | 0010 | 00da     | ffff      | ffff | C, DC, Z, OV, N |       |

| ANDWF                                    | f, d, a                         | AND WREG with f                           | 1          | 0001 | 01da     | ffff      | ffff | Z, N            |       |

| CLRF                                     | f, a                            | Clear f                                   | 1          | 0110 | 101a     | ffff      | ffff | Z               |       |

| COMF                                     | f, d, a                         | Complement f                              | 1          | 0001 | 11da     | ffff      | ffff | Z, N            |       |

| DECF                                     | f, d, a                         | Decrement f                               | 1          | 0000 | 01da     | ffff      | ffff | C, DC, Z, OV, N |       |

| INCF                                     | f, d, a                         | Increment f                               | 1          | 0010 | 10da     | ffff      | ffff | C, DC, Z, OV, N |       |

| IORWF                                    | f, d, a                         | Inclusive OR WREG with f                  | 1          | 0001 | 00da     | ffff      | ffff | Z, N            |       |

| MOVF                                     | f, d, a                         | Move f to WREG or f                       | 1          | 0101 | 00da     | ffff      | ffff | Z, N            |       |

| MOVFF                                    | f <sub>s</sub> , f <sub>d</sub> | Move f <sub>s</sub> (source) to 1st word  | 2          | 1100 | ffff     | ffff      | ffff | None            | 2, 3  |

|                                          |                                 | f <sub>d</sub> (destination) 2nd word     |            | 1111 | ffff     | ffff      | ffff |                 |       |

| MOVFFL                                   | f <sub>s</sub> , f <sub>d</sub> | Move f <sub>s</sub> (source) to           | 3          | 0000 | 0000     | 0110      | ffff | None            | 2     |

|                                          |                                 | g (full destination)                      |            | 1111 | ffff     | ffff      | ffgg |                 |       |

|                                          |                                 | f <sub>d</sub> (full destination)3rd word |            | 1111 | gggg     | dddd      | dddd |                 |       |

| MOVWF                                    | f, a                            | Move WREG to f                            | 1          | 0110 | 111a     | ffff      | ffff | None            |       |

| MULWF                                    | f, a                            | Multiply WREG with f                      | 1          | 0000 | 001a     | ffff      | ffff | None            |       |

| NEGF                                     | f, a                            | Negate f                                  | 1          | 0110 | 110a     | ffff      | ffff | C, DC, Z, OV, N |       |

| RLCF                                     | f, d, a                         | Rotate Left f through Carry               | 1          | 0011 | 01da     | ffff      | ffff | C, Z, N         |       |

| RLNCF                                    | f, d, a                         | Rotate Left f (No Carry)                  | 1          | 0100 | 01da     | ffff      | ffff | Z, N            |       |

| RRCF                                     | f, d, a                         | Rotate Right f through Carry              | 1          | 0011 | 00da     | ffff      | ffff | C, Z, N         |       |

| RRNCF                                    | f, d, a                         | Rotate Right f (No Carry)                 | 1          | 0100 | 00da     | ffff      | ffff | Z, N            |       |

| SETF                                     | f, a                            | Set f                                     | 1          | 0110 | 100a     | ffff      | ffff | None            |       |

| SUBFWB                                   | f, d, a                         | Subtract f from WREG with                 | 1          | 0101 | 01da     | ffff      | ffff | C, DC, Z, OV, N |       |

|                                          |                                 | borrow                                    |            |      |          |           |      |                 |       |

| SUBWF                                    | f, d, a                         | Subtract WREG from f                      | 1          | 0101 | 11da     | ffff      | ffff | C, DC, Z, OV, N |       |

| SUBWFB                                   | f, d, a                         | Subtract WREG from f with                 | 1          | 0101 | 10da     | ffff      | ffff | C, DC, Z, OV, N |       |

|                                          |                                 | borrow                                    |            |      |          |           |      |                 |       |

| SWAPF                                    | f, d, a                         | Swap nibbles in f                         | 1          | 0011 | 10da     | ffff      | ffff | None            |       |

| XORWF                                    | f, d, a                         | Exclusive OR WREG with f                  | 1          | 0001 | 10da     | ffff      | ffff | Z, N            |       |

| BYTE-ORIE                                | INTED S                         |                                           | I          | 1    |          |           |      | 1               |       |

| CPFSEQ                                   | f, a                            | Compare f with WREG, skip =               | 1 (2 or 3) | 0110 | 001a     | ffff      | ffff | None            | 1     |

| CPFSGT                                   | f, a                            | Compare f with WREG, skip >               | 1 (2 or 3) |      | 010a     | ffff      | ffff | None            | 1     |

| CPFSLT                                   | f, a                            | Compare f with WREG, skip <               | 1 (2 or 3) |      | 000a     | ffff      | ffff | None            | 1     |

| DECFSZ                                   | f, d, a                         | Decrement f, Skip if 0                    | 1 (2 or 3) |      | 11da     | ffff      | ffff | None            | 1     |

| DCFSNZ                                   | f, d, a                         | Decrement f, Skip if Not 0                | 1 (2 or 3) |      | 11da     | ffff      | ffff | None            | 1     |

| INCFSZ                                   | f, d, a                         | Increment f, Skip if 0                    | 1 (2 or 3) |      |          | ffff      | ffff | None            | 1     |

| INFSNZ                                   | f, d, a                         | Increment f, Skip if Not 0                | 1 (2 or 3) |      | 10da     | ffff      | ffff | None            | 1     |

| TSTFSZ                                   | f, a                            | Test f, skip if 0                         | 1 (2 or 3) |      | 011a     | ffff      | ffff | None            | 1     |

| BIT-ORIENTED FILE REGISTER INSTRUCTIONS  |                                 |                                           |            |      |          |           |      |                 |       |

| BCF                                      | f, b, a                         | Bit Clear f                               | 1          | 1001 | bbba     | ffff      | ffff | None            |       |

| BSF                                      | f, b, a                         | Bit Set f                                 | 1          | 1000 | bbba     | ffff      | ffff | None            |       |

| BTG                                      | f, d, a                         | Bit Toggle f                              | 1          |      | bbba     | ffff      | ffff | None            |       |

| BIT-ORIENTED SKIP INSTRUCTIONS           |                                 |                                           |            |      |          |           |      |                 |       |

| BTFSC                                    | f, b, a                         | Bit Test f, Skip if Clear                 | 1 (2 or 3) | 1011 | bbba     | ffff      | ffff | None            | 1     |

| BTFSS                                    | f, b, a                         | Bit Test f, Skip if Set                   | 1 (2 or 3) |      |          | ffff      | ffff | None            | 1     |

|                                          |                                 | Bit Test f, Skip if Set                   | , ,        |      |          |           |      |                 |       |

# TABLE 43-1: PIC18(L)F24/25K42 INSTRUCTION SET

Note 1: If Program Counter (PC) is modified or a conditional test is true, the instruction requires an additional cycle. The extra cycle is executed as a NOP.

2: Some instructions are multi word instructions. The second/third words of these instructions will be decoded as a NOP, unless the first word of the instruction retrieves the information embedded in these 16-bits. This ensures that all program memory locations have a valid instruction.

**3:** f<sub>s</sub> and f<sub>d</sub> do not cover the full memory range. 2 MSBs of bank selection are forced to 'b00 to limit the range of these instructions to lower 4k addressing space.

| CLR          | WDT                                                                                              | Clear Wat                | chdog                                                                                                                               | Time | r   |                |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------|-----|----------------|--|--|--|

| Synta        | ax:                                                                                              | CLRWDT                   | CLRWDT                                                                                                                              |      |     |                |  |  |  |

| Oper         | ands:                                                                                            | None                     | None                                                                                                                                |      |     |                |  |  |  |

| Operation:   |                                                                                                  |                          |                                                                                                                                     |      |     |                |  |  |  |

| Statu        | is Affected:                                                                                     | TO, PD                   |                                                                                                                                     |      |     |                |  |  |  |

| Enco         | oding:                                                                                           | 0000                     | 0000                                                                                                                                | 000  | 0 ( | 0100           |  |  |  |

| Description: |                                                                                                  | Watchdog scaler of the   | CLRWDT instruction resets the<br>Watchdog Timer. It also resets the post-<br>scaler of the WDT. Status bits, TO and<br>PD, are set. |      |     |                |  |  |  |

| Word         | ls:                                                                                              | 1                        |                                                                                                                                     |      |     |                |  |  |  |

| Cycle        | es:                                                                                              | 1                        |                                                                                                                                     |      |     |                |  |  |  |

| QC           | ycle Activity:                                                                                   |                          |                                                                                                                                     |      |     |                |  |  |  |

|              | Q1                                                                                               | Q2                       | Q3                                                                                                                                  |      |     | Q4             |  |  |  |

|              | Decode                                                                                           | No<br>operation          | Process<br>Data                                                                                                                     |      | op  | No<br>peration |  |  |  |

|              | nple:<br>Before Instruc<br>WDT Cor<br>After Instructio<br>WDT Cor<br><u>WD</u> T Pos<br>TO<br>PD | unter =<br>on<br>unter = | ?<br>00h<br>0<br>1<br>1                                                                                                             |      |     |                |  |  |  |

| COMF                  | Complem                                                                                                                                                                     | ent f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |                       |  |  |  |  |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------|--|--|--|--|

| Syntax:               | COMF f                                                                                                                                                                      | COMF f {,d {,a}}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |                       |  |  |  |  |

| Operands:             | 0 ≤ f ≤ 255<br>d ∈ [0,1]<br>a ∈ [0,1]                                                                                                                                       | d ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |                       |  |  |  |  |

| Operation:            | $(\overline{f}) \rightarrow dest$                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |                       |  |  |  |  |

| Status Affected:      | N, Z                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |                       |  |  |  |  |

| Encoding:             | 0001                                                                                                                                                                        | 11da i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ffff | ffff                  |  |  |  |  |