Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                            |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 16KB (8K x 16)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f24k42t-i-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC18(L)F24/25K42

## REGISTER 3-4: DMA2PR: DMA2 PRIORITY REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-1/1 | R/W-1/1 |

|-------|-----|-----|-----|-----|---------|---------|---------|

| —     | —   | —   | —   | —   | DMA2PR2 | DMA2PR1 | DMA2PR0 |

| bit 7 |     |     |     |     |         |         | bit 0   |

#### Legend:

| R = Readable bit     | W = Writable bit   | U = Unimplemented bit, read as '0'                    |

|----------------------|--------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown | -n/n = Value at POR and BOR/Value at all other Resets |

| 1 = bit is set       | 0 = bit is cleared | HS = Hardware set                                     |

#### bit 7-3 Unimplemented: Read as '0'

bit 2-0 DMA2PR<2:0>: DMA2 Priority Selection bits

#### REGISTER 3-5: SCANPR: SCANNER PRIORITY REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-1/1 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|-----|---------|---------|---------|

| —     | —   | —   | —   | —   | SCANPR2 | SCANPR1 | SCANPR0 |

| bit 7 |     |     |     |     |         |         | bit 0   |

| Legend:              |                    |                                                       |

|----------------------|--------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit   | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown | -n/n = Value at POR and BOR/Value at all other Resets |

| 1 = bit is set       | 0 = bit is cleared | HS = Hardware set                                     |

#### bit 7-3 Unimplemented: Read as '0'

bit 2-0 SCANPR<2:0>: DMA2 Priority Selection bits

## REGISTER 3-6: PRLOCK: PRIORITY LOCK REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0  |

|-------|-----|-----|-----|-----|-----|-----|----------|

| _     | —   | —   | —   | —   | —   | —   | PRLOCKED |

| bit 7 |     |     |     |     |     |     | bit 0    |

| Legend:              |                    |                                                       |

|----------------------|--------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit   | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown | -n/n = Value at POR and BOR/Value at all other Resets |

| 1 = bit is set       | 0 = bit is cleared | HS = Hardware set                                     |

bit 7-1 Unimplemented: Read as '0'

bit 0 **PRLOCKED**: PR Register Lock bit<sup>(1, 2)</sup>

0 = Priority Registers can be modified by write operations; Peripherals do not have access to the memory

1 = Priority Registers are locked and cannot be written; Peripherals do not have access to the memory

Note 1: The PRLOCKED bit can only be set or cleared after the unlock sequence.

2: If PR1WAY = 1, the PRLOCKED bit cannot be cleared after it has been set. A system Reset will clear the bit and allow one more set.

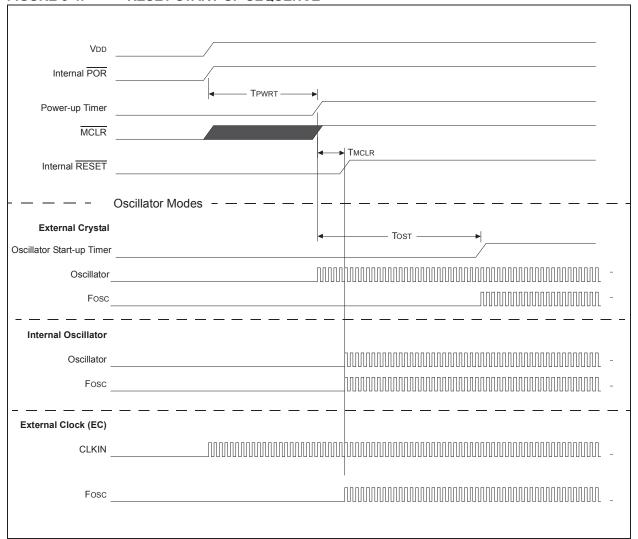

## 8.11 Start-up Sequence

Upon the release of a POR or BOR, the following must occur before the device will begin executing:

- 1. Power-up Timer runs to completion (if enabled).

- 2. Oscillator start-up timer runs to completion (if required for selected oscillator source).

- 3. MCLR must be released (if enabled).

The total time out will vary based on oscillator configuration and Power-up Timer configuration. See Section 9.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for more information.

The Power-up Timer and oscillator start-up timer run independently of MCLR Reset. If MCLR is kept low long enough, the Power-up Timer and oscillator Start-up Timer will expire. Upon bringing MCLR high, the device will begin execution after 10 Fosc cycles (see Figure 8-4). This is useful for testing purposes or to synchronize more than one device operating in parallel.

## FIGURE 8-4: RESET START-UP SEQUENCE

| R/W-1/1         | R/W-1/1                    | R/W-1/1                      | R/W-1/1         | R/W-1/1            | R/W-1/1           | R/W-1/1            | R/W-1/1    |

|-----------------|----------------------------|------------------------------|-----------------|--------------------|-------------------|--------------------|------------|

| I2C1RXIP        | SPI1IP                     | SPI1TXIP                     | SPI1RXIP        | DMA1AIP            | DMA10RIP          | DMA1DCNTIP         | DMA1SCNTIP |

| bit 7           |                            |                              |                 | •                  |                   | ·                  | bit 0      |

|                 |                            |                              |                 |                    |                   |                    |            |

| Legend:         |                            |                              |                 |                    |                   |                    |            |

| R = Readab      | le bit                     | W = Writable                 | bit             | U = Unimplem       | ented bit, read a | as 'O'             |            |

| u = Bit is und  | changed                    | x = Bit is unk               | nown            | -n/n = Value at    | POR and BOR       | /Value at all othe | r Resets   |

| '1' = Bit is se | et                         | '0' = Bit is cle             | eared           |                    |                   |                    |            |

|                 |                            |                              |                 |                    |                   |                    |            |

| bit 7           | I2C1RXIP:                  | I <sup>2</sup> C1 Receive I  | nterrupt Prior  | ity bit            |                   |                    |            |

|                 | 1 = High pr                |                              |                 |                    |                   |                    |            |

|                 | 0 = Low pri                | •                            |                 |                    |                   |                    |            |

| bit 6           |                            | 11 Transmit Inte             | errupt Priority | bit                |                   |                    |            |

|                 | 1 = High pr<br>0 = Low pri |                              |                 |                    |                   |                    |            |

| bit 5           |                            | l <sup>2</sup> C1 Transmit I | nterrunt Prior  | ity bit            |                   |                    |            |

| on o            | 1 = High pr                |                              |                 |                    |                   |                    |            |

|                 | 0 = Low pri                |                              |                 |                    |                   |                    |            |

| bit 4           | SPI1RXIP:                  | SPI1 Receive                 | Interrupt Prior | ity bit            |                   |                    |            |

|                 | 1 = High pr                |                              |                 |                    |                   |                    |            |

|                 | 0 = Low pri                | 2                            |                 |                    |                   |                    |            |

| bit 3           |                            | DMA1 Abort Tr                | ansmit Interru  | upt Priority bit   |                   |                    |            |

|                 | 1 = High pr<br>0 = Low pri |                              |                 |                    |                   |                    |            |

| bit 2           |                            | : DMA1 Overn                 | un Interrunt P  | riority bit        |                   |                    |            |

|                 | 1 = High pr                |                              |                 |                    |                   |                    |            |

|                 | 0 = Low pri                | ,                            |                 |                    |                   |                    |            |

| bit 1           | DMA1DCN1                   | <b>FIP:</b> DMA1 Des         | stination Cour  | nt Interrupt Prior | ity bit           |                    |            |

|                 | 1 = High pr                |                              |                 |                    |                   |                    |            |

|                 | 0 = Low pri                | -                            |                 |                    |                   |                    |            |

| bit 0           |                            |                              | urce Count In   | terrupt Priority b | bit               |                    |            |

|                 | 1 = High pr<br>0 = Low pri |                              |                 |                    |                   |                    |            |

|                 |                            |                              |                 |                    |                   |                    |            |

## REGISTER 11-27: IPR2: PERIPHERAL INTERRUPT Priority REGISTER 2

## 16.8 Scanner Module Overview

The Scanner allows segments of the Program Flash Memory or Data EEPROM, to be read out (scanned) to the CRC Peripheral. The Scanner module interacts with the CRC module and supplies it data one word at a time. Data is fetched from the address range defined by SCANLADR registers up to the SCANHADR registers.

The Scanner begins operation when the SGO bit is set (SCANCON0 Register) and ends when either SGO is cleared by the user or when SCANLADR increments past SCANHADR. The SGO bit is also cleared by clearing the EN bit (CRCCON0 register).

## **16.9** Configuring the Scanner

The scanner module may be used in conjunction with the CRC module to perform a CRC calculation over a range of program memory or Data EEPROM addresses. In order to set up the scanner to work with the CRC, perform the following steps:

- Set up the CRC module (See Section 16.7 "Configuring the CRC") and enable the Scanner module by setting the EN bit in the SCANCON0 register.

- 2. Choose which memory region the Scanner module should operate on and set the MREG bit of the SCANCON0 register appropriately.

- 3. If trigger is used for scanner operation, set the TRIGEN bit of the SCANCON0 register and select the trigger source using SCANTRIG register. Select the trigger source using SCANTRIG register and then set the TRIGEN bit of the SCANCON0 register. See Table 16-2 for Scanner Operation.

- 4. If Burst mode of operation is desired, set the BURSTMD bit (SCANCON0 register). See Table 16-2 for Scanner Operation.

- 5. Set the SCANLADRL/H/U and SCANHADRL/H/ U registers with the beginning and ending locations in memory that are to be scanned.

- Select the priority level for the Scanner module (See Section 3.1 "System Arbitration") and lock the priorities (See Section 3.1.1 "Priority Lock").

- 7. Both CRCEN and CRCGO bits must be enabled to use the scanner. Setting the SGO bit will start the scanner operation.

## 16.10 Scanner Interrupt

The scanner will trigger an interrupt when the SCANLADR increments past SCANHADR. The SCANIF bit can only be cleared in software.

## 16.11 Scanning Modes

The interaction of the scanner with the system operation is controlled by the priority selection in the System Arbiter (see **Section 3.2 "Memory Access Scheme**"). Additionally, BURSTMD and TRIGEN also determine the operation of the Scanner.

**16.11.1 TRIGEN =** 0, **BURSTMD =** 0

In this case, the memory access request is granted to the scanner if no other higher priority source is requesting access.

All sources with lower priority than the scanner will get the memory access cycles that are not utilized by the scanner.

**16.11.2 TRIGEN =** 1, **BURSTMD =** 0

In this case, the memory access request is generated when the CRC module is ready to accept.

The memory access request is granted to the scanner if no other higher priority source is requesting access. All sources with lower priority than the scanner will get the memory access cycles that are not utilized by the scanner.

The memory access request is granted to the scanner if no other higher priority source is requesting access. All sources with lower priority than the scanner will get the memory access cycles that are not utilized by the scanner.

#### 16.11.3 TRIGEN = x, BURSTMD = 1

In this case, the memory access is always requested by the scanner.

The memory access request is granted to the scanner if no other higher priority source is requesting access. The memory access cycles will not be granted to lower priority sources than the scanner until it completes operation i.e. SGO = 0 (SCANCON0 register)

**Note:** If TRIGEN = 1 and BURSTMD = 1, the user should ensure that the trigger source is active for the Scanner operation to complete.

| R/W-0/0                     | R/W-0/0                        | R/W-0/0           | R/W-0/0 | R/W-0/0                                               | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-----------------------------|--------------------------------|-------------------|---------|-------------------------------------------------------|---------|---------|---------|

| LADR<7:0> <sup>(1, 2)</sup> |                                |                   |         |                                                       |         |         |         |

| bit 7                       |                                |                   |         |                                                       |         |         | bit 0   |

|                             |                                |                   |         |                                                       |         |         |         |

| Legend:                     |                                |                   |         |                                                       |         |         |         |

| R = Readable                | eadable bit W = Writable bit   |                   | bit     | U = Unimplemented bit, read as '0'                    |         |         |         |

| u = Bit is uncha            | s unchanged x = Bit is unknown |                   | iown    | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |

| '1' = Bit is set            |                                | '0' = Bit is clea | ared    |                                                       |         |         |         |

#### REGISTER 16-14: SCANLADRL: SCAN LOW ADDRESS LOW BYTE REGISTER

## bit 7-0 LADR<7:0>: Scan Start/Current Address bits<sup>(1, 2)</sup> Least Significant bits of the current address to be fetched from, value increments on each fetch of memory

2: While SGO = 1 (SCANCON0 register), writing to this register is ignored.

#### REGISTER 16-15: SCANHADRU: SCAN HIGH ADDRESS UPPER BYTE REGISTER

| U-0   | U-0 | R/W-1/1     | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|-------------|---------|---------|---------|---------|---------|

| —     | —   | HADR<21:16> |         |         |         |         |         |

| bit 7 |     |             |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | Unimplemented: | Read as '0' |

|---------|----------------|-------------|

|---------|----------------|-------------|

bit 5-0 HADR<21:16>: Scan End Address bits<sup>(1, 2)</sup>

Upper bits of the address at the end of the designated scan

- **Note 1:** Registers SCANHADRU/H/L form a 22-bit value but are not guarded for atomic or asynchronous access; registers should only be read or written while SGO = 0 (SCANCON0 register).

- 2: While SGO = 1 (SCANCON0 register), writing to this register is ignored.

**Note 1:** Registers SCANLADRU/H/L form a 22-bit value, but are not guarded for atomic or asynchronous access; registers should only be read or written while SGO = 0 (SCANCON0 register).

## 17.9.4 TRANSFER FROM SFR TO GPR

The following visual reference describes the sequence of events when copying ADC results to a GPR location. The ADC Interrupt Flag can be chosen as the Source Hardware trigger, the Source address can be set to point to the ADC Result registers at 3EEF, the Destination address can be set to point to any GPR location of our choice (Example 0x100).

| FIGURE 17-8: | SFR SPACE TO GPR | R SPACE TRANSFER |

|--------------|------------------|------------------|

|              |                  |                  |

|                            | (j (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Instruction<br>Clock       | ուստուստուստուստում է Հուստուստում հատուստուստուստուստում է Գևու                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| EN                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SIRQEN                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Source Hardware<br>Trigger |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| DGO                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| DMAxSPTR                   | 0x3EEF         0x3EF0         \$\sqrt{0x3EEF}\$         \$\sqrt{0x3EF}\$         \$\sqrt{0x3EF}\$         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| DMAxDPTR                   | 0x100         0x101         5         0x102         0x103         0x103         5         5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DMAxSCNT                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| DMAxDCNT                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| DMA STATE                  | $ \left( \begin{array}{c} \text{IDLE} \\ \end{array} \right) \left( SR^{(1)} \right) DW^{(2)} \left( SR^{(1)} \right) DW^{(2)} \left( SR^{(1)} \right) \left( SR^{(1)} \right) DW^{(2)} \left( SR^{(1)} \right) DW^{(2)} \left( SR^{(1)} \right) DUE \left( SR^{(1$ |

| DMAxSCNTIF _               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| DMAxDCNTIF -               | <u></u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                            | DMAxSSA 0x3EEF DMAxDSA 0x100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                            | DMAxSSZ 0x2 DMAxDSZ 0xA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                            | SMODE 0x1 DMODE 0x1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Note 1:                    | SR - Source Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2:                         | DW - Destination Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| TABLE 17-6:                               |                         | <br>i                 | 1                                      | i         | 1                                                                                  |

|-------------------------------------------|-------------------------|-----------------------|----------------------------------------|-----------|------------------------------------------------------------------------------------|

| Source Module                             | Source Register(s)      | Destination<br>Module | Destination<br>Register(s)             | DCHxSIRQ  | Comment                                                                            |

| Signal Measure-<br>ment Timer             | SMTxCPW[U:H:L]          | GPR                   | GPR[x,y,z]                             | SMTxPWAIF | Store Captured<br>Pulse-width values                                               |

| (SMT)                                     | SMTxCPR[U:H:L]          |                       |                                        | SMTxPRAIF | Store Captured<br>Period values                                                    |

| GPR/SFR/<br>Program Flash/<br>Data EEPROM | MEMORY[x,y]             | TMR0                  | TMR0[H:L]                              | TMR0IF    | Use as a Timer0<br>reload for custom<br>16-bit value                               |

| GPR/SFR/<br>Program Flash/<br>Data EEPROM | MEMORY[x]               | TMR0                  | PR0                                    | ANY       | Update TMR0 fre-<br>quency based on a<br>specific trigger                          |

| GPR/SFR/<br>Program Flash/<br>Data EEPROM | MEMORY[x,y]             | TMR1                  | TMR1[H:L]                              | TMR1IF    | Use as a Timer1<br>reload for custom<br>16-bit value                               |

| TMR1                                      | TMR1[H:L]               | GPR                   | GPR[x,y]                               | TMR1GIF   | Use TMR1 Gate<br>interrupt flag to read<br>data out of TMR1<br>register            |

| GPR/SFR/<br>Program Flash/<br>Data EEPROM | MEMORY[x]               | TMR2                  | PR2                                    | TMR2IF    |                                                                                    |

| GPR/SFR/<br>Program Flash/<br>Data EEPROM | MEMORY[x,y,z]           | TMR2<br>CCP or PWM    | PR2<br>CCPR[H:L] or<br>PWMDC[H:L]      | ANY       | Frequency genera-<br>tor with 50% duty<br>cycle look up table                      |

| CCP                                       | CCPR[H:L]               | GPR                   | GPR[x,y]                               | CCPxIF    | Move data from CCP<br>16b Capture                                                  |

| GPR/SFR/<br>Program Flash/<br>Data EEPROM | MEMORY[x,y]             | CCP                   | CCPR[H:L]                              | ANY       | Load Compare value<br>or PWM values into<br>the CCP                                |

| GPR/SFR/<br>Program Flash/<br>Data EEPROM | MEMORY<br>[x,y,z,u,v,w] | CCPx<br>CCPy<br>CCPz  | CCPxR[H:L]<br>CCPyR[H:L]<br>CCPzR[H:L] | ANY       | Update multiple<br>PWM values at the<br>same time<br>e.g. 3-phase motor<br>control |

| GPR/SFR/<br>Program Flash/<br>Data EEPROM | MEMORY[x,y,z]           | NCO                   | NCOxINC[U:H:L]                         | ANY       | Frequency Genera-<br>tor look up table                                             |

| GPR/SFR/<br>Program Flash/<br>Data EEPROM | MEMORY[x]               | DAC                   | DACxCON0                               | ANY       | Update DAC values                                                                  |

| GPR/SFR/<br>Program Flash/<br>Data EEPROM | MEMORY[x]               | OSCTUNE               | OSCTUNE                                | ANY       | Automated Fre-<br>quency dithering                                                 |

| TABLE 17-6: | <b>EXAMPLE DMA USE</b> | CASE TABLE |

|-------------|------------------------|------------|

|-------------|------------------------|------------|

### 18.3.4 OPEN-DRAIN CONTROL