Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                           |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f25k42-e-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1.0 Device Overview                                                           | 40  |

|-------------------------------------------------------------------------------|-----|

| <ol> <li>Device Overview</li></ol>                                            |     |

| 3.0 PIC18 CPU                                                                 |     |

| 4.0 Memory Organization                                                       |     |

| 5.0 Device Configuration                                                      |     |

| 6.0 Device Information Area                                                   |     |

| 7.0 Device Configuration Information                                          |     |

| 8.0 Resets                                                                    |     |

| 9.0 Oscillator Module (with Fail-Safe Clock Monitor)                          |     |

| 10.0 Reference Clock Output Module                                            |     |

| 11.0 Interrupt Controller                                                     |     |

| 12.0 Power-Saving Operation Modes                                             |     |

| 13.0 Windowed Watchdog Timer (WWDT)                                           |     |

| 14.0 8x8 Hardware Multiplier                                                  |     |

| 15.0 Nonvolatile Memory (NVM) Control                                         |     |

| 16.0 Cyclic Redundancy Check (CRC) Module with Memory Scanner                 |     |

| 17.0 Direct Memory Access (DMA)                                               |     |

| 18.0 I/O Ports                                                                |     |

| 19.0 Peripheral Pin Select (PPS) Module                                       |     |

| 20.0 Interrupt-on-Change                                                      |     |

| 21.0 Peripheral Module Disable (PMD)                                          |     |

| 22.0 Timer0 Module                                                            | 301 |

| 23.0 Timer1/3/5 Module with Gate Control                                      |     |

| 24.0 Timer2/4/6 Module                                                        |     |

| 25.0 Capture/Compare/PWM Module                                               |     |

| 26.0 Pulse-Width Modulation (PWM)                                             |     |

| 27.0 Signal Measurement Timer (SMT)                                           |     |

| 28.0 Complementary Waveform Generator (CWG) Module                            |     |

| 29.0 Configurable Logic Cell (CLC)                                            |     |

| 30.0 Numerically Controlled Oscillator (NCO) Module                           |     |

| 31.0 Zero-Cross Detection (ZCD) Module                                        |     |

| 32.0 Data Signal Modulator (DSM) Module                                       |     |

| 33.0 Universal Asynchronous Receiver Transmitter (UART) With Protocol Support | 477 |

| 34.0 Serial Peripheral Interface (SPI) Module                                 |     |

| 35.0 I <sup>2</sup> C Module                                                  | 546 |

| 36.0 Fixed Voltage Reference (FVR)                                            | 599 |

| 37.0 Temperature Indicator Module                                             | 601 |

| 38.0 Analog-to-Digital Converter with Computation (ADC2) Module               |     |

| 39.0 5-Bit Digital-to-Analog Converter (DAC) Module                           | 642 |

| 40.0 Comparator Module                                                        |     |

| 41.0 High/Low-Voltage Detect (HLVD)                                           |     |

| 42.0 In-Circuit Serial Programming™ (ICSP™)                                   |     |

| 43.0 Instruction Set Summary                                                  | 665 |

| 44.0 Register Summary                                                         |     |

| 45.0 Development Support                                                      |     |

| 46.0 Electrical Specifications                                                | 738 |

| 47.0 DC and AC Characteristics Graphs and Tables                              | 767 |

| 48.0 Packaging Information                                                    | 768 |

| Appendix A: Revision History                                                  | 781 |

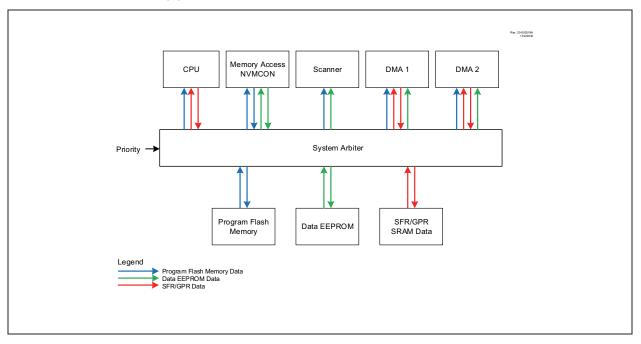

# 3.1 System Arbitration

The System Arbiter resolves memory access between the System Level Selections (i.e., Main, Interrupt Service Routine) and Peripheral Selection (i.e., DMA and Scanner) based on user-assigned priorities. Each of the system level and peripheral selections has its own priority selection registers. Memory access priority is resolved using the number written to the corresponding Priority registers, 0 being the highest priority and 4 being the lowest priority. The Default priorities are listed in Table 3-1.

In case the user wants to change priorities then ensure that each Priority register is written with a unique value from 0 to 4.

# TABLE 3-1: DEFAULT PRIORITIES

| Sele         | Priority register<br>Reset value |   |

|--------------|----------------------------------|---|

| System Level | ISR                              | 0 |

|              | MAIN                             | 1 |

#### TABLE 3-1: DEFAULT PRIORITIES

| Sel        | Priority register<br>Reset value |   |

|------------|----------------------------------|---|

| Peripheral | DMA1                             | 2 |

|            | DMA2                             | 3 |

|            | SCANNER                          | 4 |

# FIGURE 3-2: PIC18(L)F24/25K42 SYSTEM ARBITER BLOCK DIAGRAM

© 2016-2017 Microchip Technology Inc.

#### 11.3.2 NATURAL ORDER (HARDWARE) PRIORITY

When more than one interrupt with the same user specified priority level are requested, the priority conflict is resolved by using a method called "Natural Order Priority". Natural order priority is a fixed priority scheme that is based on the Interrupt Vector Table. Table 11-2 shows the natural order priority and the interrupt vector number assigned for each source.

| TABLE 11-2: | INTERRUPT VECTOR |

|-------------|------------------|

|             | PRIORITY TABLE   |

| Vector<br>Number | Interrupt<br>Source | ] [ | Vector<br>Number | Interrupt<br>Source |

|------------------|---------------------|-----|------------------|---------------------|

| 0                | Software Interrupt  |     | 42               | DMA2SCNT            |

| 1                | HLVD                | 1 [ | 43               | DMA2DCNT            |

| 2                | OSF                 | 1   | 44               | DMA2OR              |

| 3                | CSW                 | 1 [ | 45               | DMA2A               |

| 4                | NVM                 | 1 [ | 46               | I2C2RX              |

| 5                | SCAN                | 1 [ | 47               | I2C2TX              |

| 6                | CRC                 | 1 [ | 48               | 12C2                |

| 7                | IOC                 | 1 [ | 49               | I2C2E               |

| 8                | INT0                | 1 [ | 50               | U2RX                |

| 9                | ZCD                 | 1 [ | 51               | U2TX                |

| 10               | AD                  | 1 [ | 52               | U2E                 |

| 11               | ADT                 | 1 [ | 53               | U2                  |

| 12               | C1                  |     | 54               | TMR3                |

| 13               | SMT1                |     | 55               | TMR3G               |

| 14               | SMT1PRA             | 1 [ | 56               | TMR4                |

| 15               | SMT1PWA             |     | 57               | CCP2                |

| 16               | DMA1SCNT            |     | 58               | —                   |

| 17               | DMA1DCNT            |     | 59               | CWG2                |

| 18               | DMA10R              |     | 60               | CLC2                |

| 19               | DMA1A               |     | 61               | INT2                |

| 20               | SPI1RX              |     | 62               | —                   |

| 21               | SPI1TX              |     | 63               | —                   |

| 22               | SPI1                |     | 64               | —                   |

| 23               | I2C1RX              |     | 65               | —                   |

| 24               | I2C1TX              |     | 66               | —                   |

| 25               | I2C1                |     | 67               | —                   |

| 26               | I2C1E               |     | 68               | —                   |

| 27               | U1RX                |     | 69               | —                   |

| 28               | U1TX                |     | 70               | TMR5                |

| 29               | U1E                 |     | 71               | TMR5G               |

| 30               | U1                  |     | 72               | TMR6                |

| 31               | TMR0                |     | 73               | CCP3                |

| 32               | TMR1                |     | 74               | CWG3                |

| 33               | TMR1G               |     | 75               | CLC3                |

| 34               | TMR2                |     | 76               | —                   |

| 35               | CCP1                |     | 77               | —                   |

| 36               | —                   |     | 78               | —                   |

| 37               | NCO                 |     | 79               | —                   |

| 38               | CWG1                |     | 80               | CCP4                |

| 39               | CLC1                |     | 81               | CLC4                |

| 40               | INT1                |     |                  |                     |

| 41               | C2                  | J   |                  |                     |

The natural order priority scheme has vector interrupt 0 as the highest priority and vector interrupt 81 as the lowest priority.

For example, when two concurrently occurring interrupt sources that are both designated high priority using the IPRx register will be resolved using the natural order priority (i.e., the interrupt with a lower corresponding vector number will preempt the interrupt with the higher vector number).

The ability for the user to assign every interrupt source to high or low priority levels means that the user program can give an interrupt with a low natural order priority a higher overall priority level.

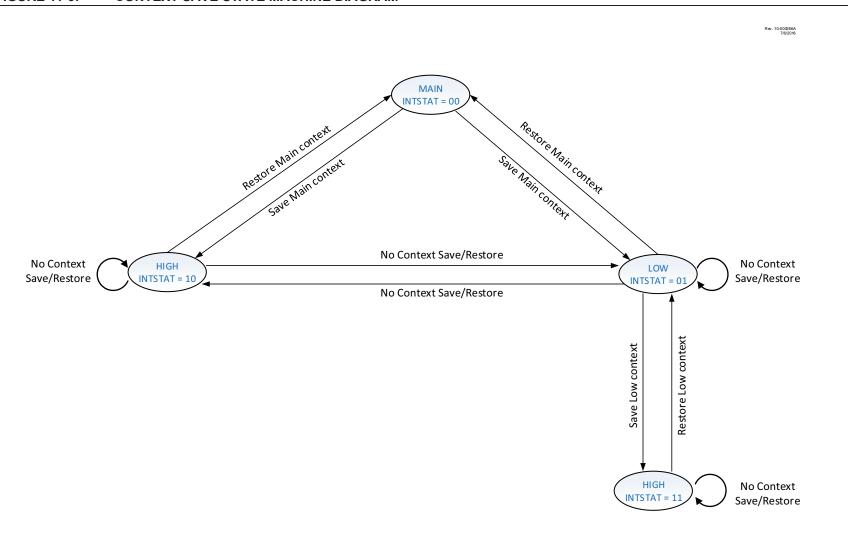

# 11.4 Interrupt Operation

All pending interrupts are indicated by the flag bit being equal to a '1' in the PIRx register. All pending interrupts are resolved using the priority scheme explained in Section 11.3 "Interrupt Priority".

Once the interrupt source to be serviced is resolved, the program execution vectors to the resolved interrupt vector addresses, as explained in **Section 11.2 "Interrupt Vector Table (IVT)**". The vector number is also stored in the WREG register. Most of the flag bits are required to be cleared by the application software, but in some cases, device hardware clears the interrupt automatically. Some flag bits are read-only in the PIRx registers, these flags are a summary of the source interrupts and the corresponding interrupt flags of the source must be cleared.

A valid interrupt can be either a high or low priority interrupt when in main routine or a high priority interrupt when in low priority Interrupt Service Routine. Depending on order of interrupt requests received and their relative timing, the CPU will be in the state of execution indicated by the STAT bits of the INTCON1 register (Register 11-2).

The State machine shown in Figure 11-1 and the subsequent sections detail the execution of interrupts when received in different orders.

Note: The state of GIEH/L is not changed by the hardware when servicing an interrupt. The internal state machine is used to keep track of execution states. These bits can be manipulated in the user code resulting in transferring execution to the main routine and ignoring existing interrupts.

| R/W-0/0                 | R/W-0/0                     | R/W-0/0            | R/W-0/0        | R/W-0/0      | R/W-0/0          | R/W-0/0  | R/W-0/0     |

|-------------------------|-----------------------------|--------------------|----------------|--------------|------------------|----------|-------------|

| IOCIE                   | CRCIE                       | SCANIE             | NVMIE          | CSWIE        | OSFIE            | HLVDIE   | SWIE        |

| bit 7                   |                             |                    |                |              |                  |          | bit         |

| Lagandu                 |                             |                    |                |              |                  |          |             |

| Legend:<br>R = Readable | e bit                       | W = Writable       | bit            | U = Unimpler | nented bit, reac | l as '0' |             |

| u = Bit is unc          |                             | x = Bit is unki    |                |              | at POR and BO    |          | ther Resets |

| '1' = Bit is set        | •                           | '0' = Bit is cle   |                |              |                  |          |             |

|                         |                             |                    |                |              |                  |          |             |

| bit 7                   | IOCIE: Interr               | upt-on-Change      | Enable bit     |              |                  |          |             |

|                         | 1 = Enabled                 |                    |                |              |                  |          |             |

|                         | 0 = Disabled                |                    |                |              |                  |          |             |

| bit 6                   |                             | C Interrupt Enab   | le bit         |              |                  |          |             |

|                         | 1 = Enabled<br>0 = Disabled |                    |                |              |                  |          |             |

| bit 5                   |                             | emory Scanner      | Intorrunt Engh | lo hit       |                  |          |             |

| DIL D                   | 1 = Enabled                 | •                  | interrupt Enac |              |                  |          |             |

|                         | 0 = Disabled                |                    |                |              |                  |          |             |

| bit 4                   | NVMIE: NVN                  | /I Interrupt Enat  | ole bit        |              |                  |          |             |

|                         | 1 = Enabled                 | I                  |                |              |                  |          |             |

|                         | 0 = Disabled                | b                  |                |              |                  |          |             |

| bit 3                   |                             | ck Switch Interro  | upt Enable bit |              |                  |          |             |

|                         | 1 = Enabled<br>0 = Disabled |                    |                |              |                  |          |             |

| bit 2                   |                             | llator Fail Interr | unt Enable hit |              |                  |          |             |

|                         | 1 = Enabled                 |                    |                |              |                  |          |             |

|                         | 0 = Disabled                |                    |                |              |                  |          |             |

| bit 1                   | HLVDIE: HL                  | VD Interrupt En    | able bit       |              |                  |          |             |

|                         | 1 = Enabled                 |                    |                |              |                  |          |             |

|                         | 0 = Disabled                |                    |                |              |                  |          |             |

| bit 0                   |                             | are Interrupt Er   | able bit       |              |                  |          |             |

|                         | 1 = Enabled<br>0 = Disabled |                    |                |              |                  |          |             |

|                         |                             |                    |                |              |                  |          |             |

# REGISTER 11-14: PIE0: PERIPHERAL INTERRUPT Enable Register 0

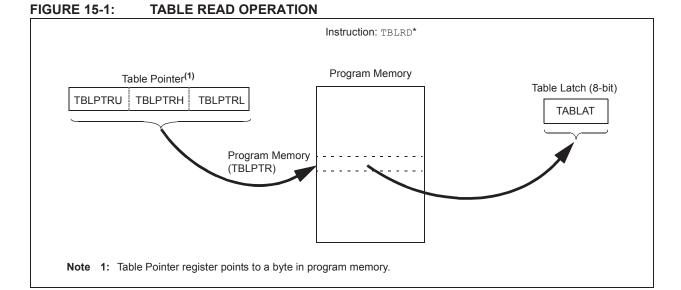

## 15.1.1 TABLE READS AND TABLE WRITES

In order to read and write program memory, there are two operations that allow the processor to move bytes between the program memory space and the data RAM:

- Table Read (TBLRD)

- Table Write (TBLWT)

The program memory space is 16 bits wide, while the data RAM space is eight bits wide. Table reads and table writes move data between these two memory spaces through an 8-bit register (TABLAT).

The table read operation retrieves one byte of data directly from program memory and places it into the TABLAT register. Figure 15-1 shows the operation of a table read.

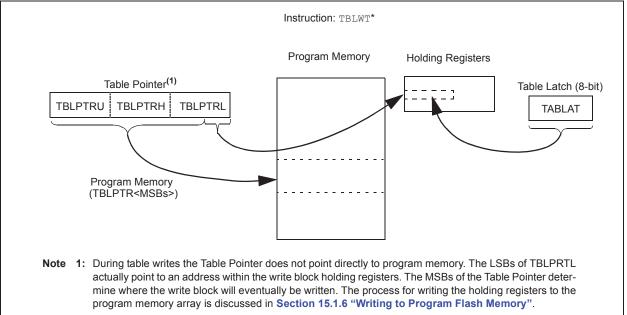

The table write operation stores one byte of data from the TABLAT register into a write block holding register. The procedure to write the contents of the holding registers into program memory is detailed in **Section 15.1.6 "Writing to Program Flash Memory"**. Figure 15-2 shows the operation of a table write with program memory and data RAM.

Table operations work with byte entities. Tables containing data, rather than program instructions, are not required to be word aligned. Therefore, a table can start and end at any byte address. If a table write is being used to write executable code into program memory, program instructions will need to be word aligned.

# FIGURE 15-2: TABLE WRITE OPERATION

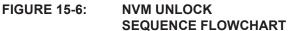

#### 15.1.4 NVM UNLOCK SEQUENCE

The unlock sequence is a mechanism that protects the NVM from unintended self-write programming or erasing. The sequence must be executed and completed without interruption to successfully complete any of the following operations:

- PFM Row Erase

- Write of PFM write latches to PFM memory

- Write of PFM write latches to User IDs

- Write to Data EEPROM Memory

- Write to Configuration Words

The unlock sequence consists of the following steps and must be completed in order:

Write 55h to NVMCON2

EXAMPLE 15-2

- Write AAh to NMVCON2

- · Set the WR bit of NVMCON1

Once the WR bit is set, the processor will stall internal operations until the operation is complete and then resume with the next instruction.

Since the unlock sequence must not be interrupted, global interrupts should be disabled prior to the unlock sequence and re-enabled after the unlock sequence is completed.

NVM LINI OCK SEQUENCE

| EARIVIFLE 13-2. | INVINI UNLOCK SEQUENCE | • |                                            |

|-----------------|------------------------|---|--------------------------------------------|

| BCF             | INTCON0,GIE            | ; | Recommended so sequence is not interrupted |

| BANKSEL         | NVMCON1                |   |                                            |

| BSF             | NVMCON1,WREN           | ; | Enable write/erase                         |

| MOVLW           | 55h                    | ; | Load 55h                                   |

| MOVWF           | NVMCON2                | ; | Step 1: Load 55h into NVMCON2              |

| MOVLW           | AAh                    | ; | Step 2: Load W with AAh                    |

| MOVWF           | NVMCON2                | ; | Step 3: Load AAh into NVMCON2              |

| BSF             | INTCON1,WR             | ; | Step 4: Set WR bit to begin write/erase    |

| BSF             | INTCON0,GIE            | ; | Re-enable interrupts                       |

- Note 1: Sequence begins when NVMCON2 is written; steps 1-4 must occur in the cycle-accurate order shown. If the timing of the steps 1 to 4 is corrupted by an interrupt or a debugger Halt, the action will not take place.

- 2: Opcodes shown are illustrative; any instruction that has the indicated effect may be used.

# 22.8 Register Definitions: Timer0 Control

| R/W-0/0          | U-0                                                                                                                                                                                                                                                                       | R-0                                                                                                                                                                                                                                                                    | R/W-0/0         | R/W-0/0         | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|------------------|------------------|--------------|

| EN               |                                                                                                                                                                                                                                                                           | OUT                                                                                                                                                                                                                                                                    | MD16            |                 |                  | S<3:0>           | 1011 0.0     |

| bit 7            |                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                        |                 |                 |                  |                  | bit (        |

|                  |                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                        |                 |                 |                  |                  |              |

| Legend:          |                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                        |                 |                 |                  |                  |              |

| R = Readable     | bit                                                                                                                                                                                                                                                                       | W = Writable                                                                                                                                                                                                                                                           | bit             |                 | mented bit, read |                  |              |

| u = Bit is unch  | anged                                                                                                                                                                                                                                                                     | x = Bit is unkr                                                                                                                                                                                                                                                        | nown            | -n/n = Value    | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is set |                                                                                                                                                                                                                                                                           | '0' = Bit is clea                                                                                                                                                                                                                                                      | ared            |                 |                  |                  |              |

| bit 7            |                                                                                                                                                                                                                                                                           | able bit<br>ule is enabled<br>ule is disabled                                                                                                                                                                                                                          |                 |                 | de               |                  |              |

| bit 6            | Unimplemen                                                                                                                                                                                                                                                                | ted: Read as '                                                                                                                                                                                                                                                         | כי              |                 |                  |                  |              |

| bit 5            | <b>OUT</b> :TMR0 O<br>TMR0 output                                                                                                                                                                                                                                         | utput bit (read-<br>bit                                                                                                                                                                                                                                                | only)           |                 |                  |                  |              |

| bit 4            | <b>MD16:</b> TMR0<br>1 = TMR0 is<br>0 = TMR0 is                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                        | 16-Bit Timer S  | elect bit       |                  |                  |              |

| bit 3-0          | OUTPS<3:0><br>1111 = 1:16 F<br>1110 = 1:15 F<br>1101 = 1:14 F<br>1100 = 1:13 F<br>1011 = 1:12 F<br>1010 = 1:11 F<br>1001 = 1:10 F<br>1000 = 1:9 PC<br>0111 = 1:8 PC<br>0110 = 1:7 PC<br>0101 = 1:6 PC<br>0101 = 1:6 PC<br>0101 = 1:2 PC<br>0011 = 1:2 PC<br>0001 = 1:2 PC | Postscaler<br>Postscaler<br>Postscaler<br>Postscaler<br>Postscaler<br>Postscaler<br>postscaler<br>postscaler<br>postscaler<br>postscaler<br>postscaler<br>postscaler<br>postscaler<br>postscaler<br>postscaler<br>postscaler<br>postscaler<br>postscaler<br>postscaler | t Postscaler (I | Divider) Select | bits             |                  |              |

## REGISTER 22-1: T0CON0: TIMER0 CONTROL REGISTER 0

# REGISTER 23-4: TxGATE: TIMERx GATE ISM REGISTER

| U-0   | U-0 | U-0 | R/W-0/u | R/W-0/u | R/W-0/u  | R/W-0/u | R/W-0/u |

|-------|-----|-----|---------|---------|----------|---------|---------|

| _     | _   | —   |         |         | GSS<4:0> |         |         |

| bit 7 |     |     |         |         |          |         | bit 0   |

|       |     |     |         |         |          |         |         |

| Legend:           |                  |                                |               |

|-------------------|------------------|--------------------------------|---------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as | s '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared           | u = unchanged |

#### bit 7-5 Unimplemented: Read as '0'

bit 4-0 **GSS<4:0>:** Timerx Gate Source Selection bits

| GSS         | Timer1                 | Timer3                 | Timer5                 |

|-------------|------------------------|------------------------|------------------------|

| 655         | Gate Source            | Gate Source            | Gate Source            |

| 11111-11011 | Reserved               | Reserved               | Reserved               |

| 11010       | CLC4_out               | CLC4_out               | CLC4_out               |

| 11001       | CLC3_out               | CLC3_out               | CLC3_out               |

| 11000       | CLC2_out               | CLC2_out               | CLC2_out               |

| 10111       | CLC1_out               | CLC1_out               | CLC1_out               |

| 10110       | ZCDOUT                 | ZCDOUT                 | ZCDOUT                 |

| 10101       | CMP2OUT                | CMP2OUT                | CMP2OUT                |

| 10100       | CMP1OUT                | CMP1OUT                | CMP1OUT                |

| 10011       | NCO10UT                | NCO10UT                | NCO10UT                |

| 10010-10001 | Reserved               | Reserved               | Reserved               |

| 10000       | PWM8OUT                | PWM8OUT                | PWM8OUT                |

| 01111       | PWM7OUT                | PWM7OUT                | PWM7OUT                |

| 01110       | PWM6OUT                | PWM6OUT                | PWM6OUT                |

| 01101       | PWM5OUT                | PWM5OUT                | PWM5OUT                |

| 01100       | CCP4OUT                | CCP4OUT                | CCP4OUT                |

| 01011       | CCP3OUT                | CCP3OUT                | CCP3OUT                |

| 01010       | CCP2OUT                | CCP2OUT                | CCP2OUT                |

| 01001       | CCP10UT                | CCP1OUT                | CCP10UT                |

| 01000       | SMT1_match             | SMT1_match             | SMT1_match             |

| 00111       | TMR6OUT (post-scaled)  | TMR6OUT (post-scaled)  | TMR6OUT (post-scaled)  |

| 00110       | TMR5 overflow          | TMR5 overflow          | Reserved               |

| 00101       | TMR4OUT (post-scaled)  | TMR4OUT (post-scaled)  | TMR4OUT (post-scaled)  |

| 00100       | TMR3 overflow          | Reserved               | TMR3 overflow          |

| 00011       | TMR2OUT (post-scaled)  | TMR2OUT (post-scaled)  | TMR2OUT (post-scaled)  |

| 00010       | Reserved               | TMR1 overflow          | TMR1 overflow          |

| 00001       | TMR0 overflow          | TMR0 overflow          | TMR0 overflow          |

| 00000       | Pin selected by T1GPPS | Pin selected by T3GPPS | Pin selected by T5GPPS |

| R/W/HC-0/0       | R/W-0/0                                          | R/W-0/0               | R/W-0/0         | R/W-0/0         | R/W-0/0         | R/W-0/0        | R/W-0/0      |  |

|------------------|--------------------------------------------------|-----------------------|-----------------|-----------------|-----------------|----------------|--------------|--|

| ON               |                                                  | CKPS<2:0>             |                 |                 | OUTP            | S<3:0>         |              |  |

| bit 7            |                                                  |                       |                 |                 |                 |                | bit          |  |

| Legend:          |                                                  |                       |                 |                 |                 |                |              |  |

| R = Readable     | bit                                              | W = Writable I        | bit             | U = Unimpler    | nented bit, rea | d as '0'       |              |  |

| u = Bit is unch  | anged                                            | x = Bit is unkn       | iown            | -n/n = Value a  | at POR and BC   | R/Value at all | other Resets |  |

| '1' = Bit is set |                                                  | '0' = Bit is clea     | ared            | HC = Bit is cle | eared by hardv  | vare           |              |  |

|                  |                                                  |                       |                 |                 |                 |                |              |  |

| bit 7            | ON: Timerx                                       | On bit <sup>(1)</sup> |                 |                 |                 |                |              |  |

|                  | 1 = Timerx i                                     |                       |                 |                 |                 |                |              |  |

|                  | 0 = Timerx i                                     | s off: all counter    | s and state m   | achines are res | set             |                |              |  |

| bit 6-4          | CKPS<2:0>:                                       | : Timerx-type Cl      | ock Prescale    | Select bits     |                 |                |              |  |

|                  | 111 = 1:128 Prescaler                            |                       |                 |                 |                 |                |              |  |

|                  | 110 = 1:64 Prescaler                             |                       |                 |                 |                 |                |              |  |

|                  | 101 = 1:32 Prescaler<br>100 = 1:16 Prescaler     |                       |                 |                 |                 |                |              |  |

|                  | 011 = 1:8  Prescaler                             |                       |                 |                 |                 |                |              |  |

|                  | 011 - 1.6 Prescaler                              |                       |                 |                 |                 |                |              |  |

|                  | 001 = 1:2 P                                      |                       |                 |                 |                 |                |              |  |

|                  | 000 = 1:1 P                                      |                       |                 |                 |                 |                |              |  |

| bit 3-0          |                                                  | >: Timerx Outpu       | It Postscaler S | Select bits     |                 |                |              |  |

|                  | 1111 = 1:16                                      |                       |                 |                 |                 |                |              |  |

|                  | 1110 = 1:15  Postscaler                          |                       |                 |                 |                 |                |              |  |

|                  | 1101 = 1:14                                      |                       |                 |                 |                 |                |              |  |

|                  | 1100 = 1:13<br>1011 = 1:12                       |                       |                 |                 |                 |                |              |  |

|                  |                                                  |                       |                 |                 |                 |                |              |  |

|                  | 1010 = 1:11 Postscaler<br>1001 = 1:10 Postscaler |                       |                 |                 |                 |                |              |  |

|                  | 1000 = 1.9 Postscaler                            |                       |                 |                 |                 |                |              |  |

|                  | 0111 = 1:8 Postscaler                            |                       |                 |                 |                 |                |              |  |

|                  | 0110 = 1:7 Postscaler                            |                       |                 |                 |                 |                |              |  |

|                  | 0101 = 1:6                                       |                       |                 |                 |                 |                |              |  |

|                  | 0100 = 1:5                                       |                       |                 |                 |                 |                |              |  |

|                  | 0011 = 1:4  <br>0010 = 1:3                       |                       |                 |                 |                 |                |              |  |

|                  | 0010 = 1.3<br>0001 = 1:2                         |                       |                 |                 |                 |                |              |  |

|                  | 0001 - 1.21<br>0000 = 1.11                       | 031304161             |                 |                 |                 |                |              |  |

## REGISTER 24-5: TxCON: TIMERx CONTROL REGISTER

Note 1: In certain modes, the ON bit will be auto-cleared by hardware. See Section 24.5.1 "One-Shot Mode".

| R/W-0/0         | R/W-0/0 R/W-1/1                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                     | R/W-1/1                          | R/W-0/0                                              | R/W-1/1          | R/W-0/0         | R/W-1/1 |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------------------------------------------------|------------------|-----------------|---------|--|--|

| C4TSEL<1:0>     |                                                                                                                                                                                                                                                                                                                                       | C3TSEL<1:0>                                                                                                                                                                                                                                                                                         |                                  | C2TSEL<1:0>                                          |                  | C1TSE           | L<1:0>  |  |  |

| bit 7           |                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                     |                                  |                                                      |                  |                 | bit (   |  |  |

|                 |                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                     |                                  |                                                      |                  |                 |         |  |  |

| Legend:         | 1.11                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                     | 1.11                             |                                                      |                  | 1               |         |  |  |

| R = Readable    |                                                                                                                                                                                                                                                                                                                                       | W = Writable                                                                                                                                                                                                                                                                                        |                                  |                                                      | nented bit, read |                 |         |  |  |

| -n = Value at I | POR                                                                                                                                                                                                                                                                                                                                   | '1' = Bit is se                                                                                                                                                                                                                                                                                     | t                                | '0' = Bit is clea                                    | ared             | x = Bit is unkr | nown    |  |  |

| bit 7-6         | 10 = CCP4 is                                                                                                                                                                                                                                                                                                                          | s based off Tin<br>s based off Tin<br>s based off Tin                                                                                                                                                                                                                                               | ner5 in Captur<br>ner3 in Captur | s<br>re/Compare mo<br>re/Compare mo<br>e/Compare mo  | de and Timer4    | in PWM mode     |         |  |  |

| bit 5-4         | 10 = CCP3 is                                                                                                                                                                                                                                                                                                                          | s based off Tin<br>s based off Tin<br>s based off Tin                                                                                                                                                                                                                                               | ner5 in Captur<br>ner3 in Captur | s<br>re/Compare mo<br>re/Compare mo<br>re/Compare mo | de and Timer4    | in PWM mode     |         |  |  |

| bit 3-2         | 11 = CCP2 is<br>10 = CCP2 is                                                                                                                                                                                                                                                                                                          | <b>C2TSEL&lt;1:0&gt;:</b> CCP2 Timer Selection bits<br>11 = CCP2 is based off Timer5 in Capture/Compare mode and Timer6 in PWM mode<br>10 = CCP2 is based off Timer3 in Capture/Compare mode and Timer4 in PWM mode<br>01 = CCP2 is based off Timer1 in Capture/Compare mode and Timer2 in PWM mode |                                  |                                                      |                  |                 |         |  |  |

| bit 1-0         | 00 = Reserved<br><b>C1TSEL&lt;1:0&gt;:</b> CCP1 Timer Selection bits<br>11 = CCP1 is based off Timer5 in Capture/Compare mode and Timer6 in PWM mode<br>10 = CCP1 is based off Timer3 in Capture/Compare mode and Timer4 in PWM mode<br>01 = CCP1 is based off Timer1 in Capture/Compare mode and Timer2 in PWM mode<br>00 = Reserved |                                                                                                                                                                                                                                                                                                     |                                  |                                                      |                  |                 |         |  |  |

#### REGISTER 25-2: CCPTMRS0: CCP TIMERS CONTROL REGISTER 0

#### 27.6.10 GATED COUNTER MODE

This mode counts pulses on the SMT1\_signal input, gated by the SMT1WIN input. It begins incrementing the timer upon seeing a rising edge of the SMT1WIN input and updates the SMT1CPW register upon a falling edge on the SMT1WIN input. See Figure 27-19 and Figure 27-20.

# 32.11 Register Definitions: Modulation Control

Long bit name prefixes for the Modulation peripheral is shown in Table 32-1. Refer to **Section 1.4.2.2 "Long Bit Names**" for more information.

# TABLE 32-1:

| Peripheral | Bit Name Prefix |

|------------|-----------------|

| MD1        | MD1             |

#### REGISTER 32-1: MD1CON0: MODULATION CONTROL REGISTER 0

| R/W-0/0 | U-0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | R/W-0/0 |

|---------|-----|---------|---------|-----|-----|-----|---------|

| EN      | —   | OUT     | OPOL    | —   | —   | —   | BIT     |

| bit 7   |     |         |         |     |     |     | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | EN: Modulator Module Enable bit                                                                                                                                                             |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Modulator module is enabled and mixing input signals</li> <li>0 = Modulator module is disabled and has no output</li> </ul>                                                    |

| bit 6   | Unimplemented: Read as '0'                                                                                                                                                                  |

| bit 5   | OUT: Modulator Output bit                                                                                                                                                                   |

|         | Displays the current output value of the Modulator module. <sup>(1)</sup>                                                                                                                   |

| bit 4   | OPOL: Modulator Output Polarity Select bit                                                                                                                                                  |

|         | 1 = Modulator output signal is inverted; idle high output                                                                                                                                   |

|         | 0 = Modulator output signal is not inverted; idle low output                                                                                                                                |

| bit 3-1 | Unimplemented: Read as '0'                                                                                                                                                                  |

| bit 0   | BIT: Allows software to manually set modulation source input to module <sup>(2)</sup>                                                                                                       |

| Note 1: | The modulated output frequency can be greater and asynchronous from the clock that updates this register bit, the bit value may not be valid for higher speed modulator or carrier signals. |

2: BIT must be selected as the modulation source in the MD1SRC register for this operation.

# PIC18(L)F24/25K42

| R-0/0      | R-0/0                                                                                                                                                             | U-0               | U-0                         | U-0                     | R/W-0/0          | R/W-0/0            | R/W-0/0            |  |  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------|-------------------------|------------------|--------------------|--------------------|--|--|

| BUSY       | SSFLT                                                                                                                                                             |                   |                             | _                       | SSET             | TXR <sup>(1)</sup> | RXR <sup>(1)</sup> |  |  |

| bit 7      | ł                                                                                                                                                                 | I                 |                             |                         |                  | •                  | bit (              |  |  |

|            |                                                                                                                                                                   |                   |                             |                         |                  |                    |                    |  |  |

| Legend:    |                                                                                                                                                                   |                   |                             |                         |                  |                    |                    |  |  |

| R = Readab | ole bit                                                                                                                                                           | W = Writable      | bit                         | U = Unimpler            | nented bit, read | l as '0'           |                    |  |  |

| bit 7      | BUSY: SPI M                                                                                                                                                       | /lodule Busy St   | atus bit                    |                         |                  |                    |                    |  |  |

|            | 1 = Data exc                                                                                                                                                      | hange is busy     |                             |                         |                  |                    |                    |  |  |

|            | 0 = Data exc                                                                                                                                                      | hange is not ta   | king place                  |                         |                  |                    |                    |  |  |

| bit 6      | SSFLT: SS(i                                                                                                                                                       | n) Fault Status   | bit                         |                         |                  |                    |                    |  |  |

|            | If SSET = 0:                                                                                                                                                      |                   |                             |                         |                  |                    |                    |  |  |

|            | 1 = SS(in) ei                                                                                                                                                     | nded the transa   | iction unexped              | ctedly, and the o       | data byte being  | received was I     | ost                |  |  |

|            | 0 <b>= SS(in) e</b>                                                                                                                                               | nded normally     |                             |                         |                  |                    |                    |  |  |

|            | If SSET = 1:                                                                                                                                                      |                   |                             |                         |                  |                    |                    |  |  |

|            | This bit is un                                                                                                                                                    | changed.          |                             |                         |                  |                    |                    |  |  |

| bit 5-3    | Unimpleme                                                                                                                                                         | nted: Read as     | 0'                          |                         |                  |                    |                    |  |  |

| bit 2      | SSET: Slave                                                                                                                                                       | Select Enable     | bit                         |                         |                  |                    |                    |  |  |

|            | Master mode                                                                                                                                                       | <u>):</u>         |                             |                         |                  |                    |                    |  |  |

|            | 1 = SS(out)                                                                                                                                                       | is driven to the  | active state co             | ontinuously             |                  |                    |                    |  |  |

|            | 0 = SS(out) is driven to the active state while the transmit counter is not zero                                                                                  |                   |                             |                         |                  |                    |                    |  |  |

|            | Slave mode:                                                                                                                                                       |                   |                             |                         |                  |                    |                    |  |  |

|            | 1 = SS(in) is ignored and data is clocked on all SCK(in) (as though SS = TRUE at all times)                                                                       |                   |                             |                         |                  |                    |                    |  |  |

|            | <ul> <li>0 = SS(in) enables/disables data input and tri-states SDO if the TRIS bit associated with the SDO pir<br/>is set (see Table 30-2 for details)</li> </ul> |                   |                             |                         |                  |                    |                    |  |  |

| bit 1      | TXR: Transn                                                                                                                                                       | nit Data-Requir   | ed Control bit <sup>(</sup> | 1)                      |                  |                    |                    |  |  |

|            | 1 = TxFIFO                                                                                                                                                        | data is required  | l for a transfer            |                         |                  |                    |                    |  |  |

|            | 0 = TxFIFO                                                                                                                                                        | data is not requ  | ired for a tran             | sfer                    |                  |                    |                    |  |  |

| bit 0      | RXR: Receiv                                                                                                                                                       | e FIFO Space-     | Required Cor                | trol bit <sup>(1)</sup> |                  |                    |                    |  |  |

|            | 1 = Data trar                                                                                                                                                     | nsfers are susp   | ended if the R              | xFIFO is full           |                  |                    |                    |  |  |

|            | 0 = Received                                                                                                                                                      | d data is not sto | ored in the FIF             | 0                       |                  |                    |                    |  |  |

|            | See Table 34-1 a pertaining to TXF                                                                                                                                |                   |                             | ter mode" and           | Section 34.6 "   | Slave Mode" fo     | or more detail     |  |  |

| 0.         | This register abo                                                                                                                                                 |                   | on to while a t             | menefor is in ore       |                  |                    | 0 := ==+)          |  |  |

2: This register should not be written to while a transfer is in progress (BUSY bit of SPIxCON2 is set).

# PIC18(L)F24/25K42

#### REGISTER 34-12: SPIxTxB: SPI TRANSMIT BUFFER REGISTER

| W-0   | W-0  | W-0  | W-0  | W-0  | W-0  | W-0  | W-0   |

|-------|------|------|------|------|------|------|-------|

| TXB7  | TXB6 | TXB5 | TXB4 | TXB3 | TXB2 | TXB1 | TXB0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

| Legend:          |                  |                                    |

|------------------|------------------|------------------------------------|

| R = Readable bit | W = Writable bit | U = Unimplemented bit, read as '0' |

bit 7-0 **TXB<7:0>**: Transmit Buffer bits (write only)

If TXFIFO is not full:

Writing to this register adds the data to the top of the TXFIFO and increases the occupancy of the TXFIFO write pointer

If TXFIFO is full:

Writing to this register does not affect the data in the TXFIFO or the write pointer, and the TXWE bit of SPIxSTATUS will be set

#### REGISTER 34-13: SPIxCLK: SPI CLOCK SELECTION REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|---------|---------|---------|---------|

| —     | —   | —   | —   | CLKSEL3 | CLKSEL2 | CLKSEL1 | CLKSEL0 |

| bit 7 |     |     |     |         |         |         | bit 0   |

| Legend:          |                  |                                    |

|------------------|------------------|------------------------------------|

| R = Readable bit | W = Writable bit | U = Unimplemented bit, read as '0' |

bit 7-4 Unimplemented: Read as '0'

bit 3-0 CLKSEL<3:0>: SPI Clock Source Selection bits

1111-1001 **= Reserved**

- 1000 = SMT\_match

- 0111 = TMR6\_Postscaled

- 0110 = TMR4\_Postscaled

- 0101 = TMR2\_Postscaled

- 0100 = TMR0\_overflow

- 0011 = CLKREF

- 0010 = MFINTOSC

- 0001 = HFINTOSC

- 0000 **= FOSC**

| R-0/0            | R-0/0                                                                                   | R-0/0                                                                                                                                                                                           | R/HS/HC-0/0                                                                                                                                  | U-0                  | R-0/0            | R-0/0            | R-0/0        |

|------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------------|------------------|--------------|

| AOV              | UTHR                                                                                    | LTHR                                                                                                                                                                                            | MATH                                                                                                                                         | -                    |                  | STAT<2:0>        |              |

| bit 7            |                                                                                         |                                                                                                                                                                                                 |                                                                                                                                              |                      |                  |                  | bit (        |

|                  |                                                                                         |                                                                                                                                                                                                 |                                                                                                                                              |                      |                  |                  |              |

| Legend:          |                                                                                         |                                                                                                                                                                                                 |                                                                                                                                              |                      |                  |                  |              |

| R = Readable     | e bit                                                                                   | W = Writable                                                                                                                                                                                    | bit                                                                                                                                          |                      | mented bit, read |                  |              |

| u = Bit is unc   | hanged                                                                                  | x = Bit is unk                                                                                                                                                                                  | nown                                                                                                                                         | -n/n = Value         | at POR and BC    | R/Value at all o | other Resets |

| '1' = Bit is set | t                                                                                       | '0' = Bit is cle                                                                                                                                                                                | eared                                                                                                                                        | HS/HC = Bit          | is set/cleared b | y hardware       |              |

| bit 7            | 1 = ADC acc                                                                             |                                                                                                                                                                                                 | verflow bit<br>RR calculation ha<br>ERR calculation                                                                                          |                      |                  |                  |              |

| bit 6            |                                                                                         | Module Greate                                                                                                                                                                                   | er-than Upper Th                                                                                                                             |                      |                  |                  |              |

| bit 5            | <b>LTHR</b> : ADC N<br>1 = ERR <lth<br>0 = ERR≥LTH</lth<br>                             | 4                                                                                                                                                                                               | nan Lower Thres                                                                                                                              | shold Flag bit       |                  |                  |              |

| bit 4            | 1 = Registers                                                                           | ACC, FLTR,                                                                                                                                                                                      | utation Status bi<br>UTH, LTH and th<br>s have not chan                                                                                      | ne AOV bit are       |                  |                  | lated        |

| bit 3            | Unimplemen                                                                              | ted: Read as                                                                                                                                                                                    | 'O'                                                                                                                                          |                      |                  |                  |              |

| bit 2-0          | 111 = ADC n<br>110 = ADC n<br>101 = ADC n<br>100 = Not us<br>011 = ADC n<br>010 = ADC n | nodule is in 2 <sup>n</sup><br>nodule is in 2 <sup>n</sup><br>nodule is in 2 <sup>n</sup><br>ed<br>nodule is in 1 <sup>si</sup><br>nodule is in 1 <sup>si</sup><br>nodule is in 1 <sup>si</sup> | Cycle Multistage<br>d conversion sta<br>d acquisition stage<br>d precharge stage<br>conversion stage<br>acquisition stage<br>precharge stage | ge<br>ge<br>ge<br>ge |                  |                  |              |

### REGISTER 38-5: ADSTAT: ADC STATUS REGISTER

**Note 1:** If CS = 1, and FOSC<FRC, these bits may be invalid.

# 41.0 HIGH/LOW-VOLTAGE DETECT (HLVD)