Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                           |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f25k42-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 1.0 Device Overview                                                           | 40  |

|-------------------------------------------------------------------------------|-----|

| <ol> <li>Device Overview</li></ol>                                            |     |

| 3.0 PIC18 CPU                                                                 |     |

| 4.0 Memory Organization                                                       |     |

| 5.0 Device Configuration                                                      |     |

| 6.0 Device Information Area                                                   |     |

| 7.0 Device Configuration Information                                          |     |

| 8.0 Resets                                                                    |     |

| 9.0 Oscillator Module (with Fail-Safe Clock Monitor)                          |     |

| 10.0 Reference Clock Output Module                                            |     |

| 11.0 Interrupt Controller                                                     |     |

| 12.0 Power-Saving Operation Modes                                             |     |

| 13.0 Windowed Watchdog Timer (WWDT)                                           |     |

| 14.0 8x8 Hardware Multiplier                                                  |     |

| 15.0 Nonvolatile Memory (NVM) Control                                         |     |

| 16.0 Cyclic Redundancy Check (CRC) Module with Memory Scanner                 |     |

| 17.0 Direct Memory Access (DMA)                                               |     |

| 18.0 I/O Ports                                                                |     |

| 19.0 Peripheral Pin Select (PPS) Module                                       |     |

| 20.0 Interrupt-on-Change                                                      |     |

| 21.0 Peripheral Module Disable (PMD)                                          |     |

| 22.0 Timer0 Module                                                            | 301 |

| 23.0 Timer1/3/5 Module with Gate Control                                      |     |

| 24.0 Timer2/4/6 Module                                                        |     |

| 25.0 Capture/Compare/PWM Module                                               |     |

| 26.0 Pulse-Width Modulation (PWM)                                             |     |

| 27.0 Signal Measurement Timer (SMT)                                           |     |

| 28.0 Complementary Waveform Generator (CWG) Module                            |     |

| 29.0 Configurable Logic Cell (CLC)                                            |     |

| 30.0 Numerically Controlled Oscillator (NCO) Module                           |     |

| 31.0 Zero-Cross Detection (ZCD) Module                                        |     |

| 32.0 Data Signal Modulator (DSM) Module                                       |     |

| 33.0 Universal Asynchronous Receiver Transmitter (UART) With Protocol Support | 477 |

| 34.0 Serial Peripheral Interface (SPI) Module                                 |     |

| 35.0 I <sup>2</sup> C Module                                                  | 546 |

| 36.0 Fixed Voltage Reference (FVR)                                            | 599 |

| 37.0 Temperature Indicator Module                                             | 601 |

| 38.0 Analog-to-Digital Converter with Computation (ADC2) Module               |     |

| 39.0 5-Bit Digital-to-Analog Converter (DAC) Module                           | 642 |

| 40.0 Comparator Module                                                        |     |

| 41.0 High/Low-Voltage Detect (HLVD)                                           |     |

| 42.0 In-Circuit Serial Programming™ (ICSP™)                                   |     |

| 43.0 Instruction Set Summary                                                  | 665 |

| 44.0 Register Summary                                                         |     |

| 45.0 Development Support                                                      |     |

| 46.0 Electrical Specifications                                                | 738 |

| 47.0 DC and AC Characteristics Graphs and Tables                              | 767 |

| 48.0 Packaging Information                                                    | 768 |

| Appendix A: Revision History                                                  | 781 |

# PIC18(L)F24/25K42

| R/W-1         | U-1                                                                                                         | R/W-1                                                                                             | R/W-1                                                                | R/W-1                                                   | R/W-1            | R/W-1           | R/W-1                |

|---------------|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------|------------------|-----------------|----------------------|

| XINST         | _                                                                                                           | DEBUG                                                                                             | STVREN                                                               | PPS1WAY                                                 | ZCDDIS           | BORV-           | <1:0> <sup>(1)</sup> |

| bit 7         |                                                                                                             |                                                                                                   | •                                                                    |                                                         |                  |                 | bit (                |

|               |                                                                                                             |                                                                                                   |                                                                      |                                                         |                  |                 |                      |

| Legend:       |                                                                                                             |                                                                                                   |                                                                      |                                                         |                  |                 |                      |

| R = Readabl   | le bit                                                                                                      | W = Writable                                                                                      | bit                                                                  | U = Unimplen                                            | nented bit, read | as '1'          |                      |

| -n = Value fo | or blank device                                                                                             | '1' = Bit is set                                                                                  |                                                                      | '0' = Bit is clea                                       | ared             | x = Bit is unkr | nown                 |

| bit 7         |                                                                                                             | instruction set                                                                                   | and Indexed                                                          | t<br>Addressing mod<br>Addressing mod                   |                  | (Legacy mode    | 9)                   |

| bit 6         | Unimplement                                                                                                 | ed: Read as '1                                                                                    | ,                                                                    |                                                         |                  |                 |                      |

| bit 5         | <b>DEBUG</b> : Debu<br>1 = Backgrour                                                                        | nd debugger is                                                                                    | disabled                                                             |                                                         |                  |                 |                      |

| <b>L:1</b>    | 0 = Backgroun                                                                                               |                                                                                                   |                                                                      | - Enchla hit                                            |                  |                 |                      |

| bit 4         | STVREN: Stac<br>1 = Stack over<br>0 = Stack over                                                            | rflow or underf                                                                                   | ow will cause                                                        | a Reset                                                 |                  |                 |                      |

| bit 3         |                                                                                                             | K bit can be clea                                                                                 | red and set on                                                       | le bit<br>ly once; PPS re<br>repeatedly (sub            |                  |                 | clear/set cycl       |

| bit 2         | <b>ZCDDIS</b> : Zero<br>1 = ZCD is dis<br>0 = ZCD is alv                                                    | abled; ZCD ca                                                                                     |                                                                      | by setting the 2                                        | CDSEN bit of     | the ZCDCON I    | register             |

| bit 1-0       | BORV<1:0>: E<br><u>PIC18FXXK42</u><br>11 = Brown-ou<br>10 = Brown-ou<br>01 = Brown-ou<br><u>PIC18LFXXK4</u> | Devices:<br>ut Reset Voltag<br>ut Reset Voltag<br>ut Reset Voltag<br>ut Reset Voltag<br>2 Device: | e (VBOR) is se<br>e (VBOR) is se<br>e (VBOR) is se<br>e (VBOR) is se | et to 2.45V<br>et to 2.45V<br>et to 2.7V<br>et to 2.85V |                  |                 |                      |

|               | 11 = Brown-ou<br>10 = Brown-ou<br>01 = Brown-ou<br>00 = Brown-ou                                            | ut Reset Voltag<br>ut Reset Voltag                                                                | e (VBOR) is se<br>e (VBOR) is se                                     | et to 2.45V<br>et to 2.7V                               |                  |                 |                      |

- debuggers and programmers. For normal device operation, this bit should be maintained as a '1'.

- 2: A higher voltage setting is recommended for operation at or above 16 MHz.

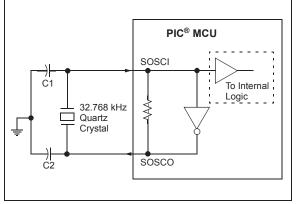

# 9.2.1.5 Secondary Oscillator

The secondary oscillator is a separate oscillator block that can be used as an alternate system clock source. The secondary oscillator is optimized for 32.768 kHz, and can be used with an external crystal oscillator connected to the SOSCI and SOSCO device pins, or an external clock source connected to the SOSCIN pin. The secondary oscillator can be selected during run-time using clock switching. Refer to **Section 9.3 "Clock Switching"** for more information.

Two power modes are available for the secondary oscillator. These modes are selected with the SOSCPWR (OSCCON3<6>). Clearing this bit selects the lower Crystal Gain mode which provides lowest microcontroller power consumption. Setting this bit enables a higher Gain mode to support faster crystal start-up or crystals with higher ESR.

### FIGURE 9-5: QUARTZ CRYSTAL OPERATION (SECONDARY OSCILLATOR)

#### Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- 2: Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Application Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for PIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PIC<sup>®</sup> Oscillator Design" (DS00849)

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

- TB097, "Interfacing a Micro Crystal MS1V-T1K 32.768 kHz Tuning Fork Crystal to a PIC16F690/SS" (DS91097)

- AN1288, "Design Practices for Low-Power External Oscillators" (DS01288)

| R/W-1/1         | R/W-1/1                                                                                     | R/W-1/1                      | R/W-1/1           | R/W-1/1        | R/W-1/1          | R/W-1/1          | R/W-1/1      |  |  |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------|------------------------------|-------------------|----------------|------------------|------------------|--------------|--|--|--|--|--|

| TMR0IP          | U1IP                                                                                        | U1EIP                        | U1TXIP            | U1RXIP         | I2C1EIP          | I2C1IP           | I2C1TXIP     |  |  |  |  |  |

| bit 7           | •                                                                                           | •                            |                   |                |                  |                  | bit (        |  |  |  |  |  |

|                 |                                                                                             |                              |                   |                |                  |                  |              |  |  |  |  |  |

| Legend:         |                                                                                             |                              |                   |                |                  | (0)              |              |  |  |  |  |  |

| R = Readable    |                                                                                             | W = Writable                 |                   |                | nented bit, reac |                  |              |  |  |  |  |  |

| u = Bit is unc  | •                                                                                           | x = Bit is unkr              |                   | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets |  |  |  |  |  |

| '1' = Bit is se | t                                                                                           | '0' = Bit is cle             | ared              |                |                  |                  |              |  |  |  |  |  |

| bit 7           |                                                                                             | ID0 Interrupt Dr             | ority bit         |                |                  |                  |              |  |  |  |  |  |

|                 | TMR0IP: TMR0 Interrupt Priority bit<br>1 = High priority                                    |                              |                   |                |                  |                  |              |  |  |  |  |  |

|                 | 0 = Low priority                                                                            |                              |                   |                |                  |                  |              |  |  |  |  |  |

| bit 6           | U1IP: UART1 Interrupt Priority bit                                                          |                              |                   |                |                  |                  |              |  |  |  |  |  |

|                 | 1 = High priority                                                                           |                              |                   |                |                  |                  |              |  |  |  |  |  |

|                 | 0 = Low price                                                                               | ority                        |                   |                |                  |                  |              |  |  |  |  |  |

| bit 5           |                                                                                             | T1 Framing Err               | or Interrupt Pr   | iority bit     |                  |                  |              |  |  |  |  |  |

|                 | 1 = High priority                                                                           |                              |                   |                |                  |                  |              |  |  |  |  |  |

| L-11-A          | <ul> <li>0 = Low priority</li> <li>U1TXIP: UART1 Transmit Interrupt Priority bit</li> </ul> |                              |                   |                |                  |                  |              |  |  |  |  |  |

| bit 4           |                                                                                             |                              | iterrupt Priority | y Dit          |                  |                  |              |  |  |  |  |  |

|                 | 1 = High priority<br>0 = Low priority                                                       |                              |                   |                |                  |                  |              |  |  |  |  |  |

| bit 3           | <b>U1RXIP:</b> UART1 Receive Interrupt Priority bit                                         |                              |                   |                |                  |                  |              |  |  |  |  |  |

|                 | 1 = High priority                                                                           |                              |                   |                |                  |                  |              |  |  |  |  |  |

|                 | 0 = Low priority                                                                            |                              |                   |                |                  |                  |              |  |  |  |  |  |

| bit 2           | I2C1EIP: I <sup>2</sup> C1 Error Interrupt Priority bit                                     |                              |                   |                |                  |                  |              |  |  |  |  |  |

|                 | 1 = High priority                                                                           |                              |                   |                |                  |                  |              |  |  |  |  |  |

|                 | 0 = Low price                                                                               |                              |                   |                |                  |                  |              |  |  |  |  |  |

| bit 1           |                                                                                             | Interrupt Priori             | ty bit            |                |                  |                  |              |  |  |  |  |  |

|                 | 1 = High prid0 = Low prid                                                                   |                              |                   |                |                  |                  |              |  |  |  |  |  |

| bit 0           |                                                                                             | <sup>2</sup> C1 Transmit Int | errunt Priority   | bit            |                  |                  |              |  |  |  |  |  |

|                 | 1 = High pri                                                                                |                              | Shaper noney      |                |                  |                  |              |  |  |  |  |  |

|                 | 0 = Low price                                                                               |                              |                   |                |                  |                  |              |  |  |  |  |  |

# REGISTER 11-28: IPR3: PERIPHERAL INTERRUPT Priority REGISTER 3

#### 15.3.5 WRITE VERIFY

;

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

#### EXAMPLE 15-5: DATA EEPROM READ

| Data | Memory Addres | s to read   |   |                          |

|------|---------------|-------------|---|--------------------------|

|      | CLRF          | NVMCON1     | ; | Setup Data EEPROM Access |

|      | MOVF          | EE_ADDRL, W | ; |                          |

|      | MOVWF         | NVMADRL     | ; | Setup Address            |

|      | BSF           | NVMCON1, RD | ; | Issue EE Read            |

|      | MOVF          | NVMDAT, W   | ; | W = EE_DATA              |

#### EXAMPLE 15-6: DATA EEPROM WRITE

| ; Data Mem  | ory Addres | s to write | 9    |   |       |       |        |       |   |  |  |

|-------------|------------|------------|------|---|-------|-------|--------|-------|---|--|--|

|             | CLRF       | NVMCON1    |      | ; | Setup | Data  | EEPROM | Acces | s |  |  |

|             | MOVF       | EE_ADDRL,  | W    | ; |       |       |        |       |   |  |  |

|             | MOVWF      | NVMADRL    |      | ; | Setup | Addre | SS     |       |   |  |  |

| ; Data Mem  | ory Value  | to write   |      |   |       |       |        |       |   |  |  |

|             | MOVF       | EE_DATA,   | W    | ; |       |       |        |       |   |  |  |

|             | MOVWF      | NVMDAT     |      | ; |       |       |        |       |   |  |  |

| ; Enable w  | rites      |            |      |   |       |       |        |       |   |  |  |

|             | BSF        | NVMCON1,   | WREN | ; |       |       |        |       |   |  |  |

| ; Disable   | interrupts |            |      |   |       |       |        |       |   |  |  |

|             | BCF        | INTCON0,   | GIE  | ; |       |       |        |       |   |  |  |

| ; Required  | unlock se  | quence     |      |   |       |       |        |       |   |  |  |

|             | MOVLW      | 55h        |      | ; |       |       |        |       |   |  |  |

|             | MOVWF      | NVMCON2    |      | ; |       |       |        |       |   |  |  |

|             | MOVLW      | AAh        |      | ; |       |       |        |       |   |  |  |

|             | MOVWF      | NVMCON2    |      | ; |       |       |        |       |   |  |  |

| ; Set WR b  | it to begi | n write    |      |   |       |       |        |       |   |  |  |

|             | BSF        | NVMCON1,   | WR   | ; |       |       |        |       |   |  |  |

| ; Enable II | TN         |            |      |   |       |       |        |       |   |  |  |

|             | BSF        | INTCON0,   | GIE  | ; |       |       |        |       |   |  |  |

| ; Wait for  | interrupt  | , write do | one  |   |       |       |        |       |   |  |  |

|             | SLEEP      |            |      | ; |       |       |        |       |   |  |  |

| ; Disable   | writes     |            |      |   |       |       |        |       |   |  |  |

|             | BCF        | NVMCON1,   | WREN | ; |       |       |        |       |   |  |  |

|             |            |            |      |   |       |       |        |       |   |  |  |

#### 15.3.6 OPERATION DURING CODE-PROTECT

Data EEPROM Memory has its own code-protect bits in Configuration Words. External read and write operations are disabled if code protection is enabled.

If the Data EEPROM is write-protected or if NVMADR points an invalid address location, the WR bit is cleared without any effect. WRERR is signaled in this scenario.

#### 15.3.7 PROTECTION AGAINST SPURIOUS WRITE

There are conditions when the user may not want to write to the Data EEPROM Memory. To protect against spurious EEPROM writes, various mechanisms have been implemented. On power-up, the WREN bit is cleared. In addition, writes to the EEPROM are blocked during the Power-up Timer period (TPWRT).

The unlock sequence and the WREN bit together help prevent an accidental write during brown-out, power glitch or software malfunction.

| R/W-x/u          | R/W-x/u                              | R/W-x/u           | R/W-x/u      | R/W-x/u            | R/W-x/u | R/W-x/u | R/W-x/u |  |

|------------------|--------------------------------------|-------------------|--------------|--------------------|---------|---------|---------|--|

| LATx7            | LATx6                                | LATx5             | LATx4        | LATx3              | LATx2   | LATx1   | LATx0   |  |

| bit 7            |                                      |                   |              | -                  |         | •       | bit 0   |  |

|                  |                                      |                   |              |                    |         |         |         |  |

| Legend:          |                                      |                   |              |                    |         |         |         |  |

| R = Readable     | = Readable bit W = Writable bit      |                   | U = Unimpler |                    |         |         |         |  |

| '1' = Bit is set | 1' = Bit is set '0' = Bit is cleared |                   |              | x = Bit is unknown |         |         |         |  |

| -n/n = Value a   | t POR and BOI                        | R/Value at all of | ther Resets  |                    |         |         |         |  |

# REGISTER 18-3: LATx: LATx REGISTER<sup>(1)</sup>

bit 7-0 LATx<7:0>: Rx7:Rx0 Output Latch Value bits

**Note 1:** Writes to LATx are equivalent with writes to the corresponding PORTx register. Reads from LATx register return register values, not I/O pin values.

TABLE 18-3: LAT REGISTERS

| Name | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|------|-------|-------|-------|-------|-------|-------|-------|-------|

| LATA | LATA7 | LATA6 | LATA5 | LATA4 | LATA3 | LATA2 | LATA1 | LATA0 |

| LATB | LATB7 | LATB6 | LATB5 | LATB4 | LATB3 | LATB2 | LATB1 | LATB0 |

| LATC | LATC7 | LATC6 | LATC5 | LATC4 | LATC3 | LATC2 | LATC1 | LATC0 |

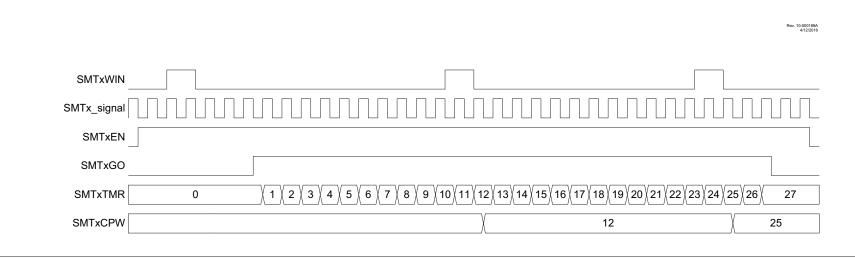

#### 27.6.9 COUNTER MODE

This mode increments the timer on each pulse of the SMT1\_signal input. This mode is asynchronous to the SMT clock and uses the SMT1\_signal as a time source. The SMT1CPW register will be updated with the current SMT1TMR value on the rising edge of the SMT1WIN input. See Figure 27-18.

#### FIGURE 27-18: COUNTER MODE TIMING DIAGRAM

| R/W-x/1          | R/W-x/1 | R/W-x/1           | R/W-x/1 | R/W-x/1                                        | R/W-x/1          | R/W-x/1  | R/W-x/1 |

|------------------|---------|-------------------|---------|------------------------------------------------|------------------|----------|---------|

|                  |         |                   | SMT1F   | PR<7:0>                                        |                  |          |         |

| bit 7            |         |                   |         |                                                |                  |          | bit 0   |

|                  |         |                   |         |                                                |                  |          |         |

| Legend:          |         |                   |         |                                                |                  |          |         |

| R = Readable     | bit     | W = Writable t    | oit     | U = Unimpler                                   | nented bit, read | d as '0' |         |

| u = Bit is unch  | anged   | x = Bit is unkn   | own     | -n/n = Value at POR and BOR/Value at all other |                  |          |         |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                                                |                  |          |         |

#### **REGISTER 27-16: SMT1PRL: SMT PERIOD REGISTER – LOW BYTE**

bit 7-0 SMT1PR<7:0>: Significant bits of the SMT Timer Value for Period Match – Low Byte

#### REGISTER 27-17: SMT1PRH: SMT PERIOD REGISTER – HIGH BYTE

| R/W-x/1      | R/W-x/1 | R/W-x/1          | R/W-x/1 | R/W-x/1      | R/W-x/1          | R/W-x/1  | R/W-x/1 |  |  |  |

|--------------|---------|------------------|---------|--------------|------------------|----------|---------|--|--|--|

| SMT1PR<15:8> |         |                  |         |              |                  |          |         |  |  |  |

| bit 7        |         |                  |         |              |                  |          | bit 0   |  |  |  |

|              |         |                  |         |              |                  |          |         |  |  |  |

| Legend:      |         |                  |         |              |                  |          |         |  |  |  |

| R = Readable | bit     | W = Writable bit |         | U = Unimpler | mented bit, read | d as '0' |         |  |  |  |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SMT1PR<15:8>: Significant bits of the SMT Timer Value for Period Match – High Byte

#### REGISTER 27-18: SMT1PRU: SMT PERIOD REGISTER – UPPER BYTE

| R/W-x/1       | R/W-x/1 | R/W-x/1 | R/W-x/1 | R/W-x/1 | R/W-x/1 | R/W-x/1 | R/W-x/1 |  |  |  |

|---------------|---------|---------|---------|---------|---------|---------|---------|--|--|--|

| SMT1PR<23:16> |         |         |         |         |         |         |         |  |  |  |

| bit 7 bit 0   |         |         |         |         |         |         |         |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SMT1PR<23:16>: Significant bits of the SMT Timer Value for Period Match – Upper Byte

© 2016-2017 Microchip Technology Inc.

# 28.7 Rising Edge and Reverse Dead Band

In Half-Bridge mode, the rising edge dead band delays the turn-on of the CWGxA output after the rising edge of the CWG data input. In Full-Bridge mode, the reverse dead-band delay is only inserted when changing directions from Forward mode to Reverse mode, and only the modulated output CWGxB is affected.

The CWGxDBR register determines the duration of the dead-band interval on the rising edge of the input source signal. This duration is from 0 to 64 periods of the CWG clock.

Dead band is always initiated on the edge of the input source signal. A count of zero indicates that no dead band is present.

If the input source signal reverses polarity before the dead-band count is completed, then no signal will be seen on the respective output.

The CWGxDBR register value is double-buffered. When EN = 0 (Register 28-1), the buffer is loaded when CWGxDBR is written. If EN = 1, then the buffer will be loaded at the rising edge following the first falling edge of the data input, after the LD bit (Register 28-1) is set. Refer to Figure 28-12 for an example.

# 28.8 Falling Edge and Forward Dead Band

In Half-Bridge mode, the falling edge dead band delays the turn-on of the CWGxB output at the falling edge of the CWG data input. In Full-Bridge mode, the forward dead-band delay is only inserted when changing directions from Reverse mode to Forward mode, and only the modulated output CWGxD is affected.

The CWGxDBF register determines the duration of the dead-band interval on the falling edge of the input source signal. This duration is from zero to 64 periods of CWG clock.

Dead-band delay is always initiated on the edge of the input source signal. A count of zero indicates that no dead band is present.

If the input source signal reverses polarity before the dead-band count is completed, then no signal will be seen on the respective output.

The CWGxDBF register value is double-buffered. When EN = 0 (Register 28-1), the buffer is loaded when CWGxDBF is written. If EN = 1, then the buffer will be loaded at the rising edge following the first falling edge of the data input after the LD (Register 28-1) is set. Refer to Figure 28-13 for an example.

# 28.10 Auto-Shutdown

Auto-shutdown is a method to immediately override the CWG output levels with specific overrides that allow for safe shutdown of the circuit. The shutdown state can be either cleared automatically or held until cleared by software. The auto-shutdown circuit is illustrated in Figure 28-14.

#### 28.10.1 SHUTDOWN

The shutdown state can be entered by either of the following two methods:

- Software generated

- External Input

#### 28.10.1.1 Software Generated Shutdown

Setting the SHUTDOWN bit of the CWGxAS0 register will force the CWG into the shutdown state.

When the auto-restart is disabled, the shutdown state will persist as long as the SHUTDOWN bit is set.

When auto-restart is enabled, the SHUTDOWN bit will clear automatically and resume operation on the next rising edge event. The SHUTDOWN bit indicates when a shutdown condition exists. The bit may be set or cleared in software or by hardware.

#### 28.10.1.2 External Input Source

External shutdown inputs provide the fastest way to safely suspend CWG operation in the event of a Fault condition. When any of the selected shutdown inputs goes active, the CWG outputs will immediately go to the specified override levels without software delay. The override levels are selected by the LSBD<1:0> and LSAC<1:0> bits of the CWGxAS0 register (Register ). Several input sources can be selected to cause a shutdown condition. All input sources are active-low. The sources are:

- Pin selected by CWGxPPS

- Timer2 post-scaled output

- Timer4 post-scaled output

- Timer6 post-scaled output

- · Comparator 1 output

- · Comparator 2 output

- CLC2 output

Shutdown input sources are individually enabled by the ASxE bits of the CWGxAS1 register (Register 28-7).

Note: Shutdown inputs are level sensitive, not edge sensitive. The shutdown state cannot be cleared, except by disabling auto-shutdown, as long as the shutdown input level persists.

#### 28.10.1.3 Pin Override Levels

The levels driven to the CWG outputs during an autoshutdown event are controlled by the LSBD<1:0> and LSAC<1:0> bits of the CWGxAS0 register (Register ). The LSBD<1:0> bits control CWGxB/D output levels, while the LSAC<1:0> bits control the CWGxA/C output levels.

#### 28.10.1.4 Auto-Shutdown Interrupts

When an auto-shutdown event occurs, either by software or hardware setting SHUTDOWN, the CWGxIF flag bit of the PIR7 register is set (Register 9-5).

### 28.11 Auto-Shutdown Restart

After an auto-shutdown event has occurred, there are two ways to resume operation:

- Software controlled

- Auto-restart

In either case, the shut-down source must be cleared before the restart can take place. That is, either the shutdown condition must be removed, or the corresponding ASxE bit must be cleared.

#### 28.11.1 SOFTWARE-CONTROLLED RESTART

If the REN bit of the CWGxAS0 register is clear (REN = 0), the CWG module must be restarted after an auto-shutdown event through software.

Once all auto-shutdown sources are removed, the software must clear SHUTDOWN. Once SHUTDOWN is cleared, the CWG module will resume operation upon the first rising edge of the CWG data input.

Note: The SHUTDOWN bit cannot be cleared in software if the auto-shutdown condition is still present.

### 28.11.2 AUTO-RESTART

If the REN bit of the CWGxAS0 register is set (REN = 1), the CWG module will restart from the shutdown state automatically.

Once all auto-shutdown conditions are removed, the hardware will automatically clear SHUTDOWN. Once SHUTDOWN is cleared, the CWG module will resume operation upon the first rising edge of the CWG data input.

Note: The SHUTDOWN bit cannot be cleared in software if the auto-shutdown condition is still present.

| R/W-x/u                                                                                                                                   | R/W-x/u     | R/W-x/u                             | R/W-x/u         | R/W-x/u       | R/W-x/u         | R/W-x/u           | R/W-x/u |

|-------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------|-----------------|---------------|-----------------|-------------------|---------|

| G2D4T                                                                                                                                     | G2D4N       | G2D3T                               | G2D3N           | G2D2T         | G2D2N           | G2D1T             | G2D1N   |

| bit 7                                                                                                                                     |             |                                     |                 |               |                 |                   | bit (   |

|                                                                                                                                           |             |                                     |                 |               |                 |                   |         |

| Legend:<br>P = Peadable                                                                                                                   | , bit       | W = Writable                        | hit             | II – Unimplen | nented hit read | 1 ac 'O'          |         |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value |             |                                     |                 |               |                 | thar Dagata       |         |

| (1) = Bit is uncl(1) = Bit is set                                                                                                         | •           | 0' = Bit is cle                     |                 |               | at FOR and BO   | in value at all u |         |

|                                                                                                                                           |             |                                     | aleu            |               |                 |                   |         |

| bit 7                                                                                                                                     | G2D4T: Gate | e 1 Data 4 True                     | (non-inverted)  | ) bit         |                 |                   |         |

|                                                                                                                                           |             | (true) is gated                     |                 |               |                 |                   |         |

|                                                                                                                                           |             | (true) is not ga                    |                 |               |                 |                   |         |

| bit 6                                                                                                                                     | G2D4N: Gat  | e 1 Data 4 Neg                      | ated (inverted) | ) bit         |                 |                   |         |

|                                                                                                                                           |             | (inverted) is ga                    |                 |               |                 |                   |         |

|                                                                                                                                           |             | (inverted) is no                    | •               |               |                 |                   |         |

| bit 5                                                                                                                                     |             | e 1 Data 3 True                     |                 |               |                 |                   |         |

|                                                                                                                                           |             | (true) is gated<br>(true) is not ga |                 |               |                 |                   |         |

| bit 4                                                                                                                                     |             | e 1 Data 3 Neg                      |                 |               |                 |                   |         |

| DIL 4                                                                                                                                     |             | (inverted) is ga                    | ,               |               |                 |                   |         |

|                                                                                                                                           |             | (inverted) is ga                    |                 |               |                 |                   |         |

| bit 3                                                                                                                                     |             | e 1 Data 2 True                     | •               |               |                 |                   |         |

|                                                                                                                                           |             | (true) is gated                     |                 |               |                 |                   |         |

|                                                                                                                                           | 0 = CLCIN1  | (true) is not ga                    | ted into CLCx   | Gate 1        |                 |                   |         |

| bit 2                                                                                                                                     | G2D2N: Gat  | e 1 Data 2 Neg                      | ated (inverted) | ) bit         |                 |                   |         |

|                                                                                                                                           |             | (inverted) is ga                    |                 |               |                 |                   |         |

|                                                                                                                                           |             | (inverted) is no                    | •               |               |                 |                   |         |

| bit 1                                                                                                                                     |             | e 1 Data 1 True                     |                 |               |                 |                   |         |

|                                                                                                                                           |             | (true) is gated<br>(true) is not ga |                 |               |                 |                   |         |

| bit 0                                                                                                                                     |             | e 1 Data 1 Neg                      |                 |               |                 |                   |         |

|                                                                                                                                           |             | (inverted) is ga                    | ,               |               |                 |                   |         |

|                                                                                                                                           | 0 = CLCINO  | (IIIVELLEU) IS Ya                   |                 |               |                 |                   |         |

## REGISTER 29-8: CLCxGLS1: GATE 1 LOGIC SELECT REGISTER

#### 34.8.3.4 Receiver Overflow and Transmitter Underflow interrupts.

The receiver overflow interrupt triggers if data is received when the RXFIFO is already full and RXR = 1. In this case, the data will be discarded and the RXOIF bit will be set. The receiver overflow interrupt flag is the RXOIF bit of SPIxINTF. The receiver overflow interrupt enable bit is the RXOIE bit of SPIxINTE.

The Transmitter Underflow interrupt flag triggers if a data transfer begins when the TXFIFO is empty and TXR = 1. In this case, the most recently received data will be transmitted and the TXUIF bit will be set. The transmitter underflow interrupt flag is the TXUIF bit of SPIxINTF. The transmitter underflow interrupt enable bit is the TXUIE bit of SPIxINTE.

Both of these interrupts will only occur in Slave mode, as Master mode will not allow the RXFIFO to overflow or the TXFIFO to underflow.

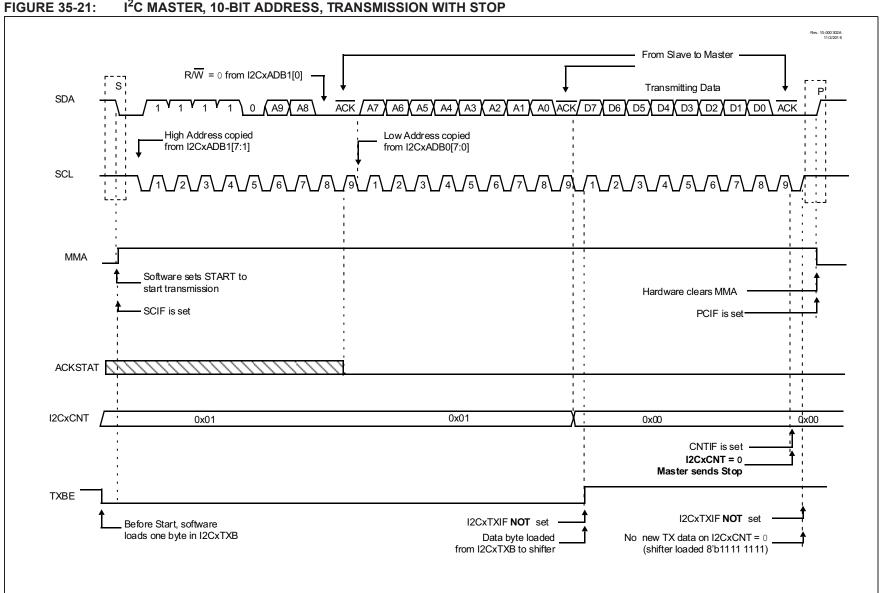

# I<sup>2</sup>C MASTER, 10-BIT ADDRESS, TRANSMISSION WITH STOP

PIC18(L)F24/25K42

| U-0                               | U-0                                                                                 | U-0               | U-0            | U-0                                     | U-0              | R/W-0/0     | R/W-0/0 |  |

|-----------------------------------|-------------------------------------------------------------------------------------|-------------------|----------------|-----------------------------------------|------------------|-------------|---------|--|

| _                                 | _                                                                                   | —                 | —              | —                                       | _                | INTP        | INTN    |  |

| bit 7                             |                                                                                     |                   |                | •                                       | •                |             | bit 0   |  |

|                                   |                                                                                     |                   |                |                                         |                  |             |         |  |

| Legend:                           |                                                                                     |                   |                |                                         |                  |             |         |  |

| R = Readable bit W = Writable bit |                                                                                     |                   |                | U = Unimpler                            | mented bit, read | as '0'      |         |  |

| -n = Value at F                   | POR                                                                                 | '1' = Bit is set  |                | '0' = Bit is cleared x = Bit is unknown |                  |             |         |  |

|                                   |                                                                                     |                   |                |                                         |                  |             |         |  |

| bit 7-2                           | Unimplement                                                                         | ed: Read as '0'   |                |                                         |                  |             |         |  |

| bit 1                             | INTP: Compa                                                                         | rator Interrupt   | on Positive-Go | oing Edge Ena                           | ıble bit         |             |         |  |

|                                   | 1 = The CxI                                                                         | F interrupt flag  | will be set up | on a positive-g                         | oing edge of the | e CxOUT bit |         |  |

|                                   | 0 = No inter                                                                        | rupt flag will be | set on a posi  | tive-going edg                          | e of the CxOUT   | bit         |         |  |

| bit 0                             | pit 0 INTN: Comparator Interrupt on Negative-Going Edge Enable bit                  |                   |                |                                         |                  |             |         |  |

|                                   | 1 = The CxIF interrupt flag will be set upon a negative-going edge of the CxOUT bit |                   |                |                                         |                  |             |         |  |

|                                   | 0 = No interrupt flag will be set on a negative-going edge of the CxOUT bit         |                   |                |                                         |                  |             |         |  |

#### REGISTER 40-2: CMxCON1: COMPARATOR x CONTROL REGISTER 1

#### REGISTER 40-3: CMxNCH: COMPARATOR x INVERTING CHANNEL SELECT REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0  | R/W-0/0 |

|-------|-----|-----|-----|-----|---------|----------|---------|

|       | —   | —   | _   | _   |         | NCH<2:0> |         |

| bit 7 |     |     |     |     |         |          | bit 0   |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### bit 7-3 Unimplemented: Read as '0'

bit 2-0 NCH<2:0>: Comparator Inverting Input Channel Select bits

111 **= V**SS

110 = FVR\_Buffer2

101 = NCH not connected

- 100 = NCH not connected

- 011 = CxIN3-

- 010 = CxIN2-

- 001 = CxIN1-

- 000 = CxIN0-

# PIC18(L)F24/25K42

| DECF                        | Decrement f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 |                      | DECFSZ                          | Decreme                                                                                                                                                                                  | nt f, skip if (                           | D                 |  |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-------------------|--|

| Syntax:                     | DECF f {,d {,a}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | }}              |                      | Syntax:                         | DECFSZ                                                                                                                                                                                   | f {,d {,a}}                               |                   |  |

| Operands:                   | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                 |                      | Operands:                       | 0 ≤ f ≤ 255<br>d ∈ [0,1]<br>a ∈ [0,1]                                                                                                                                                    |                                           |                   |  |

| Operation:                  | $(f)-1 \rightarrow dest$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 |                      | Operation:                      | ( )                                                                                                                                                                                      | $(f) - 1 \rightarrow dest,$               |                   |  |

| Status Affected:            | C, DC, N, OV, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2               |                      |                                 | skip if resu                                                                                                                                                                             | t = 0                                     |                   |  |

| Encoding:                   | 0000 010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | da fff          | f ffff               | Status Affected                 |                                                                                                                                                                                          |                                           |                   |  |

| Description:<br>Words:      | 000001daffffffffDecrement register 'f'. If 'd' is '0', the<br>result is stored in W. If 'd' is '1', the<br>result is stored back in register 'f'<br>(default).If 'a' is '1', the Access Bank is selected.If 'a' is '0', the Access Bank is selected.If 'a' is '1', the BSR is used to select the<br>GPR bank.GPR bank.If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See Sec-<br>tion 43.2.3 "Byte-Oriented and Bit-<br>Oriented Instructions in Indexed Literal Offset Mode" for details.1 |                 |                      | Encoding:<br>Description:       | 001011daffffffffThe contents of register 'f' are<br>decremented. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed back in register 'f' (default).<br> |                                           |                   |  |

| Cycles:                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |                      |                                 |                                                                                                                                                                                          | ever f ≤ 95 (5<br>" <b>Byte-Orien</b>     | Fh). See Sec-     |  |

| Q Cycle Activity:           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 |                      |                                 | Oriented I                                                                                                                                                                               | nstructions in                            | n Indexed Lit-    |  |

| Q1                          | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Q3              | Q4                   |                                 |                                                                                                                                                                                          | Mode" for de                              | etails.           |  |

| Decode                      | Read P<br>register 'f'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Process<br>Data | Write to destination | Words:                          | 1                                                                                                                                                                                        |                                           |                   |  |

| Example:<br>Before Instruct | DECF CNT,<br>tion<br>= 01h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | , 1, 0          |                      | Cycles:<br>Q Cycle Activi       | by a                                                                                                                                                                                     | vcles if skip ar<br>a 2-word instru<br>Q3 |                   |  |

| Z<br>After Instructio       | = 0<br>n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 |                      | Decod                           |                                                                                                                                                                                          | Process                                   | Write to          |  |

| CNT                         | = 00h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 |                      | lf skip:                        | register 'f'                                                                                                                                                                             | Data                                      | destination       |  |

| Z                           | = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                 |                      | Q1                              | Q2                                                                                                                                                                                       | Q3                                        | Q4                |  |

|                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 |                      | No                              | No                                                                                                                                                                                       | No                                        | No                |  |

|                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 |                      | operatio                        |                                                                                                                                                                                          | operation                                 | operation         |  |

|                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 |                      |                                 | owed by 2-word in                                                                                                                                                                        |                                           | 04                |  |

|                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 |                      | Q1<br>No                        | Q2<br>No                                                                                                                                                                                 | Q3<br>No                                  | Q4<br>No          |  |

|                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 |                      | operatio                        |                                                                                                                                                                                          | operation                                 | operation         |  |

|                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 |                      | No                              | No                                                                                                                                                                                       | No                                        | No                |  |

|                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 |                      | operatio                        | n operation                                                                                                                                                                              | operation                                 | operation         |  |