Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                           |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f25k42-i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

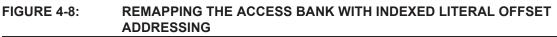

## 4.8.3 MAPPING THE ACCESS BANK IN INDEXED LITERAL OFFSET MODE

The use of Indexed Literal Offset Addressing mode effectively changes how the first 96 locations of Access RAM (00h to 5Fh) are mapped. Rather than containing just the contents of the bottom section of Bank 0, this mode maps the contents from a user defined "window" that can be located anywhere in the data memory space. The value of FSR2 establishes the lower boundary of the addresses mapped into the window, while the upper boundary is defined by FSR2 plus 95 (5Fh). Addresses in the Access RAM above 5Fh are mapped as previously described (see Section 4.5.2 "Access Bank"). An example of Access Bank remapping in this addressing mode is shown in Figure 4-8.

Remapping of the Access Bank applies *only* to operations using the Indexed Literal Offset mode. Operations that use the BSR (Access RAM bit is '1') will continue to use direct addressing as before.

## 4.9 PIC18 Instruction Execution and the Extended Instruction Set

Enabling the extended instruction set adds eight additional commands to the existing PIC18 instruction set. These instructions are executed as described in **Section 43.2 "Extended Instruction Set**".

## 7.0 DEVICE CONFIGURATION INFORMATION

The Device Configuration Information (DCI) is a dedicated region in the Program memory space mapped from 3FFF00h to 3FFF09h. The data stored in these locations is ready-only and cannot be erased or modified.

Refer to Table 7-1: Device Configuration Information for the complete DCI table address and description. The DCI holds information about the device which is useful for programming and Bootloader applications. These locations are read-only and cannot be erased or modified.

## TABLE 7-1: DEVICE CONFIGURATION INFORMATION

| ADDRESS         | Name  | DESCRIPTION             | VALUE         | UNITS |

|-----------------|-------|-------------------------|---------------|-------|

| 3FFF00h-3FFF01h | ERSIZ | Erase Row Size          | 32            | Words |

| 3FFF02h-3FFF03h | WLSIZ | Number of write latches | 64            |       |

| 3FFF04h-3FFF05h | URSIZ | Number of User Rows     | See Table 7-2 | Rows  |

| 3FFF06h-3FFF07h | EESIZ | EE Data memory size     | 256           | Bytes |

| 3FFF08h-3FFF09h | PCNT  | Pin Count               | 28            | Pins  |

### TABLE 7-2:MEMORY SIZE AND NUMBER OF USER ROWS

| Part Name      | Memory size | Number of user rows |

|----------------|-------------|---------------------|

| PIC18(L)F24K42 | 8K          | 256                 |

| PIC18(L)F25K42 | 16K         | 512                 |

## 7.1 DIA and DCI Access

The DIA and DCI addresses are read-only and cannot be erased or modified. See Section 15.2 "Device Information Area, Device Configuration Area, User ID, Device ID and Configuration Word Access" for more information on accessing these memory locations.

Development tools, such as device programmers and debuggers, may be used to read the DIA and DCI regions, similar to the Device ID and Revision ID.

## **REGISTER 17-12: DMAxSCNTL – DMAx SOURCE COUNT LOW REGISTER**

|           |     | -   |     |     |     |     |       |  |

|-----------|-----|-----|-----|-----|-----|-----|-------|--|

| R-0       | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0   |  |

| SCNT<7:0> |     |     |     |     |     |     |       |  |

| bit 7     |     |     |     |     |     |     | bit 0 |  |

|           |     |     |     |     |     |     |       |  |

| Legend:   |     |     |     |     |     |     |       |  |

| Legend:                                                     |                  |                                    |                                            |  |  |

|-------------------------------------------------------------|------------------|------------------------------------|--------------------------------------------|--|--|

| R = Readable bit                                            | W = Writable bit | U = Unimplemented bit, read as '0' |                                            |  |  |

| -n/n = Value at POR and<br>BOR/Value at all other<br>Resets | 1 = bit is set   | 0 = bit is cleared                 | x = bit is unknown<br>u = bit is unchanged |  |  |

### bit 7-0 SCNT<7:0>: Current Source Byte Count

## **REGISTER 17-13: DMAxSCNTH – DMAx SOURCE COUNT HIGH REGISTER**

| U-0   | U-0 | U-0 | U-0 | R-0        | R-0 | R-0 | R-0 |  |

|-------|-----|-----|-----|------------|-----|-----|-----|--|

| _     | —   | —   | —   | SCNT<11:8> |     |     |     |  |

| bit 7 |     |     |     |            |     |     |     |  |

| Legend:                                                     |                  |                        |                                            |  |  |  |

|-------------------------------------------------------------|------------------|------------------------|--------------------------------------------|--|--|--|

| R = Readable bit                                            | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0'         |  |  |  |

| -n/n = Value at POR<br>and BOR/Value at all<br>other Resets | 1 = bit is set   | 0 = bit is cleared     | x = bit is unknown<br>u = bit is unchanged |  |  |  |

#### bit 7-4 Unimplemented: Read as '0'

bit 3-0 SCNT<11:8>: Current Source Byte Count

#### **REGISTER 17-14: DMAxDSAL – DMAx DESTINATION START ADDRESS LOW REGISTER**

| R/W-0/0 | R/W-0/0  | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |  |

|---------|----------|---------|---------|---------|---------|---------|---------|--|--|--|

|         | DSA<7:0> |         |         |         |         |         |         |  |  |  |

| bit 7   |          |         |         |         |         |         | bit 0   |  |  |  |

|         |          |         |         |         |         |         |         |  |  |  |

| Legend: |          |         |         |         |         |         |         |  |  |  |

| R = Readable bit                                            | W = Writable bit | U = Unimplemented bit, read as '0' |                                            |  |

|-------------------------------------------------------------|------------------|------------------------------------|--------------------------------------------|--|

| -n/n = Value at POR and<br>BOR/Value at all other<br>Resets | 1 = bit is set   | 0 = bit is cleared                 | x = bit is unknown<br>u = bit is unchanged |  |

bit 7-0 DSA<7:0>: Destination Start Address bits

© 2016-2017 Microchip Technology Inc.

## **REGISTER 17-21: DMAxDCNTH – DMAx DESTINATION COUNT HIGH REGISTER**

| U-0   | U-0 | U-0 | U-0 | R-0        | R-0 | R-0 | R-0   |

|-------|-----|-----|-----|------------|-----|-----|-------|

| —     | —   | —   | —   | DCNT<11:8> |     |     |       |

| bit 7 |     |     |     |            |     |     | bit 0 |

## Legend:

| Legena.                                                          |                  |                                                              |  |  |  |

|------------------------------------------------------------------|------------------|--------------------------------------------------------------|--|--|--|

| R = Readable bit                                                 | W = Writable bit | U = Unimplemented bit, read as '0'                           |  |  |  |

| -n/n = Value at POR and 1 = bit is set<br>BOR/Value at all other |                  | 0 = bit is cleared x = bit is unknown<br>u = bit is unchange |  |  |  |

| Resets                                                           |                  |                                                              |  |  |  |

#### bit 7-4 Unimplemented: Read as '0'

bit 3-0 DCNT<11:8>: Current Destination Byte Count

#### REGISTER 17-22: DMAxSIRQ – DMAx START INTERRUPT REQUEST SOURCE SELECTION REGISTER

| U-0   | R/W-0/0 |

|-------|---------|---------|---------|---------|---------|---------|---------|

| _     | SIRQ6   | SIRQ5   | SIRQ4   | SIRQ3   | SIRQ2   | SIRQ1   | SIRQ0   |

| bit 7 |         | •       |         |         |         |         | bit 0   |

| Legend:                                                     |                  |                        |                                            |

|-------------------------------------------------------------|------------------|------------------------|--------------------------------------------|

| R = Readable bit                                            | W = Writable bit | U = Unimplemented bit, | read as '0'                                |

| -n/n = Value at POR<br>and BOR/Value at all<br>other Resets | 1 = bit is set   | 0 = bit is cleared     | x = bit is unknown<br>u = bit is unchanged |

## bit 7 Unimplemented: Read as '0'

bit 6-0 **DMAxSIRQ<6:0>:** DMAx Start Interrupt Request Source Selection bits Please refer to Table 17-2 for more information.

## REGISTER 17-23: DMAxAIRQ – DMAx ABORT INTERRUPT REQUEST SOURCE SELECTION REGISTER

| U-0   | R/W-0/0 |

|-------|---------|---------|---------|---------|---------|---------|---------|

| _     | AIRQ6   | AIRQ5   | AIRQ4   | AIRQ3   | AIRQ2   | AIRQ1   | AIRQ0   |

| bit 7 |         | •       | •       | •       | •       |         | bit 0   |

| Legend:                                                     |                  |                        |                                            |

|-------------------------------------------------------------|------------------|------------------------|--------------------------------------------|

| R = Readable bit                                            | W = Writable bit | U = Unimplemented bit, | read as '0'                                |

| -n/n = Value at POR<br>and BOR/Value at all<br>other Resets | 1 = bit is set   | 0 = bit is cleared     | x = bit is unknown<br>u = bit is unchanged |

bit 7 Unimplemented: Read as '0'

bit 6-0 **DMAxAIRQ<6:0>:** DMAx Interrupt Request Source Selection bits Please refer to Table 17-2 for more information.

### REGISTER 23-3: TxCLK: TIMERx CLOCK REGISTER

| U-0     | U-0 | U-0 | R/W-0/u | R/W-0/u | R/W-0/u | R/W-0/u | R/W-0/u |

|---------|-----|-----|---------|---------|---------|---------|---------|

| —       | —   | —   |         |         | CS<4:0> |         |         |

| bit 7   |     |     |         |         |         |         | bit 0   |

|         |     |     |         |         |         |         |         |

| Legend: |     |     |         |         |         |         |         |

| Legena:           |                  |                             |               |

|-------------------|------------------|-----------------------------|---------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | u = unchanged |

### bit 7-5 Unimplemented: Read as '0'

bit 4-0 CS<4:0>: Timerx Clock Source Selection bits

|             | Timer1             | Timer3             | Timer5             |

|-------------|--------------------|--------------------|--------------------|

| CS          | Clock Source       | Clock Source       | Clock Source       |

| 11111-10001 | Reserved           | Reserved           | Reserved           |

| 10000       | CLC4               | CLC4               | CLC4               |

| 01111       | CLC3               | CLC3               | CLC3               |

| 01110       | CLC2               | CLC2               | CLC2               |

| 01101       | CLC1               | CLC1               | CLC1               |

| 01100       | TMR5 overflow      | TMR5 overflow      | Reserved           |

| 01011       | TMR3 overflow      | Reserved           | TMR3 overflow      |

| 01010       | Reserved           | TMR1 overflow      | TMR1 overflow      |

| 01001       | TMR0 overflow      | TMR0 overflow      | TMR0 overflow      |

| 01000       | CLKREF             | CLKREF             | CLKREF             |

| 00111       | SOSC               | SOSC               | SOSC               |

| 00110       | MFINTOSC (32 kHz)  | MFINTOSC (32 kHz)  | MFINTOSC (32 kHz)  |

| 00101       | MFINTOSC (500 kHz) | MFINTOSC (500 kHz) | MFINTOSC (500 kHz) |

| 00100       | LFINTOSC           | LFINTOSC           | LFINTOSC           |

| 00011       | HFINTOSC           | HFINTOSC           | HFINTOSC           |

| 00010       | Fosc               | Fosc               | Fosc               |

| 00001       | Fosc/4             | Fosc/4             | Fosc/4             |

| 00000       | T1CKIPPS           | T3CKIPPS           | T5CKIPPS           |

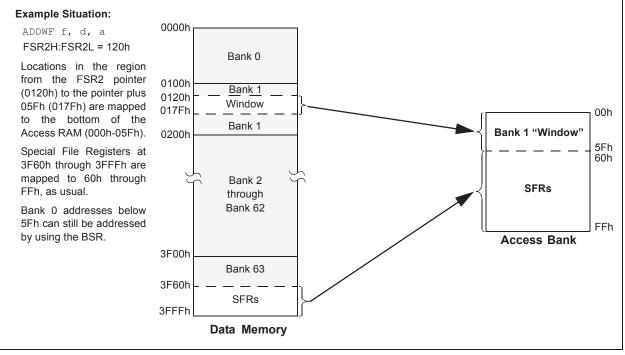

## 28.10 Auto-Shutdown

Auto-shutdown is a method to immediately override the CWG output levels with specific overrides that allow for safe shutdown of the circuit. The shutdown state can be either cleared automatically or held until cleared by software. The auto-shutdown circuit is illustrated in Figure 28-14.

### 28.10.1 SHUTDOWN

The shutdown state can be entered by either of the following two methods:

- Software generated

- External Input

### 28.10.1.1 Software Generated Shutdown

Setting the SHUTDOWN bit of the CWGxAS0 register will force the CWG into the shutdown state.

When the auto-restart is disabled, the shutdown state will persist as long as the SHUTDOWN bit is set.

When auto-restart is enabled, the SHUTDOWN bit will clear automatically and resume operation on the next rising edge event. The SHUTDOWN bit indicates when a shutdown condition exists. The bit may be set or cleared in software or by hardware.

#### 28.10.1.2 External Input Source

External shutdown inputs provide the fastest way to safely suspend CWG operation in the event of a Fault condition. When any of the selected shutdown inputs goes active, the CWG outputs will immediately go to the specified override levels without software delay. The override levels are selected by the LSBD<1:0> and LSAC<1:0> bits of the CWGxAS0 register (Register ). Several input sources can be selected to cause a shutdown condition. All input sources are active-low. The sources are:

- Pin selected by CWGxPPS

- Timer2 post-scaled output

- Timer4 post-scaled output

- Timer6 post-scaled output

- · Comparator 1 output

- · Comparator 2 output

- CLC2 output

Shutdown input sources are individually enabled by the ASxE bits of the CWGxAS1 register (Register 28-7).

Note: Shutdown inputs are level sensitive, not edge sensitive. The shutdown state cannot be cleared, except by disabling auto-shutdown, as long as the shutdown input level persists.

### 28.10.1.3 Pin Override Levels

The levels driven to the CWG outputs during an autoshutdown event are controlled by the LSBD<1:0> and LSAC<1:0> bits of the CWGxAS0 register (Register ). The LSBD<1:0> bits control CWGxB/D output levels, while the LSAC<1:0> bits control the CWGxA/C output levels.

#### 28.10.1.4 Auto-Shutdown Interrupts

When an auto-shutdown event occurs, either by software or hardware setting SHUTDOWN, the CWGxIF flag bit of the PIR7 register is set (Register 9-5).

## 28.11 Auto-Shutdown Restart

After an auto-shutdown event has occurred, there are two ways to resume operation:

- Software controlled

- Auto-restart

In either case, the shut-down source must be cleared before the restart can take place. That is, either the shutdown condition must be removed, or the corresponding ASxE bit must be cleared.

## 28.11.1 SOFTWARE-CONTROLLED RESTART

If the REN bit of the CWGxAS0 register is clear (REN = 0), the CWG module must be restarted after an auto-shutdown event through software.

Once all auto-shutdown sources are removed, the software must clear SHUTDOWN. Once SHUTDOWN is cleared, the CWG module will resume operation upon the first rising edge of the CWG data input.

Note: The SHUTDOWN bit cannot be cleared in software if the auto-shutdown condition is still present.

## 28.11.2 AUTO-RESTART

If the REN bit of the CWGxAS0 register is set (REN = 1), the CWG module will restart from the shutdown state automatically.

Once all auto-shutdown conditions are removed, the hardware will automatically clear SHUTDOWN. Once SHUTDOWN is cleared, the CWG module will resume operation upon the first rising edge of the CWG data input.

Note: The SHUTDOWN bit cannot be cleared in software if the auto-shutdown condition is still present.

## 28.14 Register Definitions: CWG Control

Long bit name prefixes for the CWG peripheral is shown in Table 28-1. Refer to **Section 1.4.2.2 "Long Bit Names"** for more information.

#### TABLE 28-1:

| Peripheral | Bit Name Prefix |

|------------|-----------------|

| CWG1       | CWG1            |

| CWG2       | CWG2            |

| CWG3       | CWG3            |

### REGISTER 28-1: CWGxCON0: CWG CONTROL REGISTER 0

| R/W-0/0 | R/W/HC-0/0        | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0   | R/W-0/0 |

|---------|-------------------|-----|-----|-----|---------|-----------|---------|

| EN      | LD <sup>(1)</sup> | —   | —   | —   |         | MODE<2:0> |         |

| bit 7   |                   |     |     |     |         |           | bit 0   |

I

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HC = Bit is cleared by hardware                       |

#### bit 7 EN: CWGx Enable bit

- 1 = Module is enabled

- 0 = Module is disabled

#### bit 6 LD: CWGx Load Buffers bit<sup>(1)</sup>

- 1 = Dead-band count buffers to be loaded on CWG data rising edge, following first falling edge after this bit is set

- 0 = Buffers remain unchanged

- bit 5-3 Unimplemented: Read as '0'

- bit 2-0 MODE<2:0>: CWGx Mode bits

- 111 = Reserved

- 110 = Reserved

- 101 = CWG outputs operate in Push-Pull mode

- 100 = CWG outputs operate in Half-Bridge mode

- 011 = CWG outputs operate in Reverse Full-Bridge mode

- 010 = CWG outputs operate in Forward Full-Bridge mode

- 001 = CWG outputs operate in Synchronous Steering mode

- 000 = CWG outputs operate in Asynchronous Steering mode

**Note 1:** This bit can only be set after EN = 1; it cannot be set in the same cycle when EN is set.

| Name     | Bit 7    | Bit 6 | Bit 5    | Bit 4 | Bit 3 | Bit 2    | Bit 1     | Bit 0 | Register<br>on Page |

|----------|----------|-------|----------|-------|-------|----------|-----------|-------|---------------------|

| CWGxCON0 | EN       | LD    | —        | _     |       |          | MODE<2:0> |       | 427                 |

| CWGxCON1 | —        | _     | IN       | _     | POLD  | POLC     | POLB      | POLA  | 428                 |

| CWGxCLK  | _        | _     | _        | _     | _     | _        | _         | CS    | 429                 |

| CWGxISM  | —        | _     | —        | _     | _     | ISM<2:0> |           | 430   |                     |

| CWGxSTR  | OVRD     | OVRC  | OVRB     | OVRA  | STRD  | STRC     | STRB      | STRA  | 431                 |

| CWGxAS0  | SHUTDOWN | REN   | LSBD     | <1:0> | LSAC  | <1:0>    | —         | —     | 432                 |

| CWGxAS1  | —        | —     | AS5E     | AS4E  | AS3E  | AS2E     | AS1E      | AS0E  | 433                 |

| CWGxDBR  | —        | _     | DBR<5:0> |       |       |          |           | 434   |                     |

| CWGxDBF  |          | _     |          |       | DBF<  | :5:0>    |           |       | 434                 |

## TABLE 28-2: SUMMARY OF REGISTERS ASSOCIATED WITH CWG

**Legend:** – = unimplemented locations read as '0'. Shaded cells are not used by CWG.

## 30.8 NCO Control Registers

| R/W-0/0                 | U-0                                                        | R-0/0                                                                                                        | R/W-0/0      | U-0            | U-0              | U-0              | R/W-0/0      |

|-------------------------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------|----------------|------------------|------------------|--------------|

| EN                      | —                                                          | OUT                                                                                                          | POL          | —              | —                | —                | PFM          |

| bit 7                   |                                                            | ·                                                                                                            |              |                |                  |                  | bit 0        |

|                         |                                                            |                                                                                                              |              |                |                  |                  |              |

| Legend:                 |                                                            |                                                                                                              |              |                |                  |                  |              |

| R = Readable            | bit                                                        | W = Writable                                                                                                 | bit          | U = Unimpler   | nented bit, read | l as '0'         |              |

| u = Bit is unch         | anged                                                      | x = Bit is unkr                                                                                              | nown         | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is set        |                                                            | '0' = Bit is cle                                                                                             | ared         |                |                  |                  |              |

| bit 7<br>bit 6<br>bit 5 | 0 = NCO1 mc<br>Unimplemen<br>OUT: NCO1 (<br>Displays the c | odule is enable<br>odule is disable<br>odule is disable<br>oted: Read as '<br>Output bit<br>current output v | o'           | CO1 module.    |                  |                  |              |

| bit 4                   |                                                            | Polarity<br>tput signal is ir<br>tput signal is n                                                            |              |                |                  |                  |              |

| bit 3-1                 | Unimplemen                                                 | ted: Read as '                                                                                               | 0'           |                |                  |                  |              |

| bit 0                   | 1 = NCO1 op                                                | Pulse Frequen<br>erates in Pulse<br>erates in Fixed                                                          | Frequency mo |                | 2                |                  |              |

## REGISTER 30-1: NCO1CON: NCO CONTROL REGISTER

| U-0              | U-0            | U-0                 | U-0               | U-0            | U-0              | U-0              | R/W-0/0          |

|------------------|----------------|---------------------|-------------------|----------------|------------------|------------------|------------------|

| —                | —              | —                   | —                 | _              | _                | —                | P1<8>            |

| bit 7            |                |                     |                   |                |                  |                  | bit 0            |

|                  |                |                     |                   |                |                  |                  |                  |

| Legend:          |                |                     |                   |                |                  |                  |                  |

| R = Readable     | bit            | W = Writable        | bit               | U = Unimpler   | mented bit, read | as '0'           |                  |

| u = Bit is uncha | anged          | x = Bit is unkr     | nown              | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets      |

| '1' = Bit is set |                | '0' = Bit is clea   | ared              |                |                  |                  |                  |

| hit 7 G          | Unimalaman     | ted. Dood oo f      | <u>`</u>          |                |                  |                  |                  |

| bit 7-6          | Unimplemen     | ted: Read as '      | J                 |                |                  |                  |                  |

| bit 0            | P1<8>: Most    | Significant Bit     | of Parameter      | 1              |                  |                  |                  |

|                  | DMX mode:      |                     |                   |                |                  |                  |                  |

|                  | Most Significa | int bit of numbe    | r of bytes to tra | ansmit betwee  | n Start Code and | d automatic Bre  | eak generation   |

|                  | DALI Control   | Device mode:        |                   |                |                  |                  |                  |

|                  | Most Significa | int bit of idle tim | ie delay after v  | which a Forwar | d Frame is sent. | Measured in h    | nalf-bit periods |

|                  | DALI Control   | <u>Gear mode</u> :  |                   |                |                  |                  |                  |

|                  | Most Significa | ant bit of delay    | between the e     | end of a Forwa | rd Frame and th  | e start of the E | Back Frame       |

|                  | Measured in h  | nalf-bit periods    |                   |                |                  |                  |                  |

|                  | Other modes:   |                     |                   |                |                  |                  |                  |

|                  | Not used       |                     |                   |                |                  |                  |                  |

|                  |                |                     |                   |                |                  |                  |                  |

|                  |                |                     |                   |                |                  |                  |                  |

## REGISTER 33-12: UxP1H: UART PARAMETER 1 HIGH REGISTER

### REGISTER 33-13: UxP1L: UART PARAMETER 1 LOW REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | P1<     | 7:0>    |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

|         |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 P

P1<7:0>: Least Significant Bits of Parameter 1

DMX mode:

Least Significant Byte of number of bytes to transmit between Start Code and automatic Break generation

DALI Control Device mode:

Least Significant Byte of idle time delay after which a Forward Frame is sent. Measured in half-bit periods DALI Control Gear mode:

Least Significant Byte of delay between the end of a Forward Frame and the start of the Back Frame Measured in half-bit periods

LIN mode:

PID to transmit (Only Least Significant 6 bits used) <u>Asynchronous Address mode:</u> Address to transmit (9th transmit bit automatically set to '1') <u>Other modes</u>: Not used

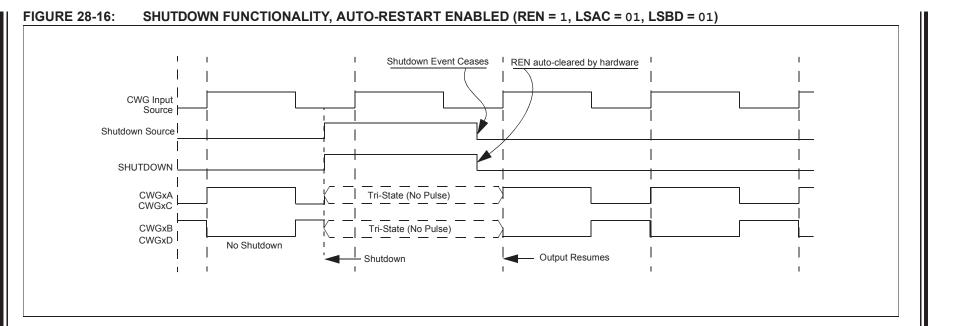

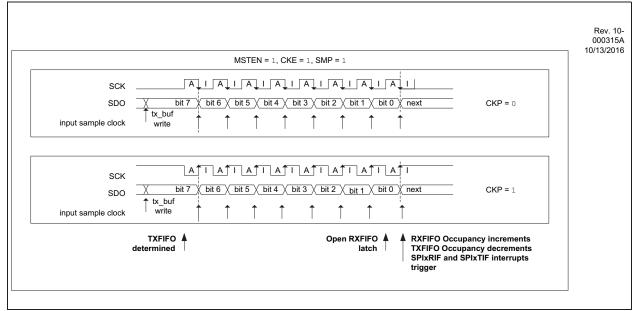

## FIGURE 34-7: CLOCKING DETAIL-MASTER MODE, CKE/SMP = 0/0

FIGURE 34-8: CLOCKING DETAIL - MASTER MODE, CKE/SMP = 1/1

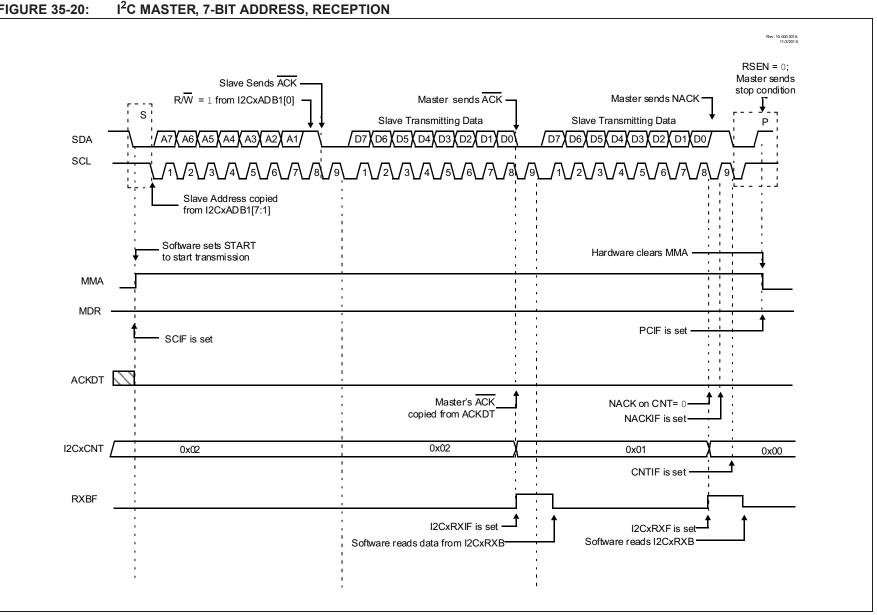

## **FIGURE 35-20:**

PIC18(L)F24/25K42

## PIC18(L)F24/25K42

| R-0                                                                                           | R-0                | R-0                              | R-0                 | R-0                                   | U-0               | U-0                                                       | U-0         |

|-----------------------------------------------------------------------------------------------|--------------------|----------------------------------|---------------------|---------------------------------------|-------------------|-----------------------------------------------------------|-------------|

| BFRE <sup>(3</sup>                                                                            |                    | MMA                              | R <sup>(1, 2)</sup> | D                                     |                   |                                                           |             |

| bit 7                                                                                         | 01111              |                                  | IX. I               | D                                     |                   |                                                           | bit         |

|                                                                                               |                    |                                  |                     |                                       |                   |                                                           | Dit         |

| Legend:                                                                                       |                    |                                  |                     |                                       |                   |                                                           |             |

| R = Reada                                                                                     | able bit           | W = Writable                     | bit                 | U = Unimpler                          | mented bit, rea   | ad as '0'                                                 |             |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets |                    |                                  |                     |                                       |                   |                                                           |             |

| 1' = Bit is                                                                                   | set                | '0' = Bit is cle                 | eared               | HS = Hardwa                           | are set HC        | = Hardware clea                                           | r           |

|                                                                                               |                    |                                  |                     |                                       |                   |                                                           |             |

| oit 7                                                                                         | BFRE: Bus F        | -<br>ree Status bit <sup>(</sup> | 3)                  |                                       |                   |                                                           |             |

|                                                                                               |                    | s the I <sup>2</sup> C bus is    |                     |                                       |                   |                                                           |             |

|                                                                                               |                    |                                  |                     | for time-out se<br>ource for this bit |                   | CON2 <bfret<1< td=""><td>:0&gt;&gt; bits.</td></bfret<1<> | :0>> bits.  |

|                                                                                               |                    |                                  |                     | ected, this bit r                     |                   |                                                           |             |

| oit 6                                                                                         |                    | Nodule Active                    |                     |                                       | ,                 |                                                           |             |

|                                                                                               |                    |                                  |                     | a received mate                       | ching 7-bit sla   | ve address                                                |             |

|                                                                                               |                    |                                  |                     |                                       |                   | lave low addres                                           | S           |

|                                                                                               |                    |                                  |                     |                                       | ching 10-bit sla  | ave <b>high</b> w/ read                                   | address, or |

|                                                                                               |                    | previous match<br>by any Restar  |                     |                                       |                   |                                                           |             |

|                                                                                               |                    | d by BTOIF and                   |                     |                                       |                   |                                                           |             |

| bit 5                                                                                         | MMA: Maste         | r Module Activ                   | e Status bit        |                                       |                   |                                                           |             |

|                                                                                               | 1 = Master         | Mode state ma                    | chine is active     | 9                                     |                   |                                                           |             |

|                                                                                               |                    |                                  |                     | erts a Start on b                     | DUS               |                                                           |             |

|                                                                                               |                    | state machine<br>when BCLIF i    |                     |                                       |                   |                                                           |             |

|                                                                                               |                    | when Stop is                     |                     | master.                               |                   |                                                           |             |

|                                                                                               |                    |                                  | -                   |                                       | essfully shifts o | out a Stop condit                                         | ion.        |

| bit 4                                                                                         | R: Read Info       | rmation bit <sup>(1, 2</sup>     | .)                  |                                       |                   |                                                           |             |

|                                                                                               |                    |                                  | •                   | (high) address                        |                   | equest                                                    |             |

|                                                                                               | 0 = Indicates      | s the last matc                  | ning received       | (high) address                        | was a Write       |                                                           |             |

| bit 3                                                                                         | D: Data bit        |                                  |                     |                                       |                   |                                                           |             |

|                                                                                               |                    |                                  |                     | insmitted was d<br>insmitted was a    |                   |                                                           |             |

| bit 2-0                                                                                       |                    | nted: Read as                    |                     |                                       |                   |                                                           |             |

| Note 1:                                                                                       | This bit holds the |                                  |                     |                                       |                   | h. Addresses tra                                          | nsmitted by |

|                                                                                               | the Master or app  |                                  |                     |                                       |                   |                                                           |             |

| 2:                                                                                            | Clock requests an  | •                                | •                   |                                       |                   | es.                                                       |             |

| 3.                                                                                            | Software must use  | e the EN bit to                  | torce Master o      | or Slave hardwa                       | are to Idle       |                                                           |             |

3: Software must use the EN bit to force Master or Slave hardware to Idle.

## 41.6 Operation During Sleep

When enabled, the HLVD circuitry continues to operate during Sleep. If the device voltage crosses the trip point, the HLVDIF bit will be set and the device will wake up from Sleep. Device execution will continue from the interrupt vector address if interrupts have been globally enabled.

## 41.7 Operation During Idle and Doze Modes

In both Idle and Doze modes, the module is active and events are generated if peripheral is enabled.

## 41.8 Operation During Freeze

When in Freeze mode, no new event or interrupt can be generated. The state of the LRDY bit is frozen.

Register reads and writes through the CPU interface are allowed.

## 41.9 Effects of a Reset

A device Reset forces all registers to their Reset state. This forces the HLVD module to be turned off.

## PIC18(L)F24/25K42

| RCALL Relative Call |                 |                                                                                                        |                                                                                                                                                                                                                                                                                                                                |      |     |               |  |  |  |

|---------------------|-----------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|---------------|--|--|--|

| Synta               | ax:             | RCALL n                                                                                                | RCALL n                                                                                                                                                                                                                                                                                                                        |      |     |               |  |  |  |

| Oper                | ands:           | -1024 ≤ n ≤                                                                                            | 1023                                                                                                                                                                                                                                                                                                                           |      |     |               |  |  |  |

| Oper                | ation:          | · · /                                                                                                  | $\begin{array}{l} (PC) + 2 \rightarrow TOS, \\ (PC) + 2 + 2n \rightarrow PC \end{array}$                                                                                                                                                                                                                                       |      |     |               |  |  |  |

| Statu               | is Affected:    | None                                                                                                   |                                                                                                                                                                                                                                                                                                                                |      |     |               |  |  |  |

| Enco                | oding:          | 1101                                                                                                   | 1nnn                                                                                                                                                                                                                                                                                                                           | nnnı | n   | nnnn          |  |  |  |

| Word                |                 | from the cu<br>address (PC<br>stack. Then<br>number '2n'<br>have incren<br>instruction,<br>PC + 2 + 2r | Subroutine call with a jump up to 1K from the current location. First, return address (PC + 2) is pushed onto the stack. Then, add the 2's complement number '2n' to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 2 + 2n. This instruction is a 2-cycle instruction. |      |     |               |  |  |  |

| ,                   | vcle Activity:  | 2                                                                                                      |                                                                                                                                                                                                                                                                                                                                |      |     |               |  |  |  |

|                     | Q1              | Q2                                                                                                     | Q3                                                                                                                                                                                                                                                                                                                             | 3    |     | Q4            |  |  |  |

|                     | Decode          | Read literal<br>'n'<br>PUSH PC to<br>stack                                                             | Proce<br>Dat                                                                                                                                                                                                                                                                                                                   |      | Wri | te to PC      |  |  |  |

|                     | No<br>operation | No<br>operation                                                                                        | No<br>opera                                                                                                                                                                                                                                                                                                                    | ·    | ор  | No<br>eration |  |  |  |

Example: HERE RCALL Jump

> Before Instruction PC = Address (HERE) After Instruction

PC = TOS= Address (Jump) Address (HERE + 2)

| RESET Reset   |                |                       |                                                                  |           |    |          |  |

|---------------|----------------|-----------------------|------------------------------------------------------------------|-----------|----|----------|--|

| Syntax: RESET |                |                       |                                                                  |           |    |          |  |

| Oper          | ands:          | None                  |                                                                  |           |    |          |  |

| Oper          | ation:         |                       | Reset all registers and flags that are affected by a MCLR Reset. |           |    |          |  |

| Statu         | s Affected:    | All                   |                                                                  |           |    |          |  |

| Enco          | ding:          | 0000                  | 0000                                                             | 1111 1111 |    | 1111     |  |

| Desc          | ription:       | This instru execute a | <u>.</u>                                                         |           |    | ·        |  |

| Word          | ls:            | 1                     |                                                                  |           |    |          |  |

| Cycle         | es:            | 1                     |                                                                  |           |    |          |  |

| QC            | ycle Activity: |                       |                                                                  |           |    |          |  |

|               | Q1             | Q2                    | Q3                                                               | Q3        |    | Q4       |  |

|               | Decode         | Start                 |                                                                  | No        |    | No       |  |

|               |                | Reset                 | opera                                                            | tion      | op | peration |  |

Example:

After Instruction

| Registers = | Reset Value |

|-------------|-------------|

| Flags* =    | Reset Value |

RESET

# PIC18(L)F24/25K42

| SUBWF                                                       | Subtract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | W from f                     |                      |  |  |  |  |

|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----------------------|--|--|--|--|

| Syntax:                                                     | SUBWF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | f {,d {,a}}                  |                      |  |  |  |  |

| Operands:                                                   | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                              |                      |  |  |  |  |

| Operation:                                                  | (f) – (W) –                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $(f) - (W) \rightarrow dest$ |                      |  |  |  |  |

| Status Affected:                                            | N, OV, C, I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | N, OV, C, DC, Z              |                      |  |  |  |  |

| Encoding:                                                   | 0101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11da fff                     | f ffff               |  |  |  |  |

| Description:                                                | Subtract W from register 'f' (2's complement method). If 'd' is '0', the result is stored in W. If 'd' is '1', the result is stored back in register 'f' (default).<br>If 'a' is '0', the Access Bank is selected. If 'a' is '1', the BSR is used to select the GPR bank.<br>If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever $f \le 95$ (5Fh). See Section 43.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode" for details. |                              |                      |  |  |  |  |

| Words:                                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                              |                      |  |  |  |  |

| Cycles:                                                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                              |                      |  |  |  |  |

| Q Cycle Activity:                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                              |                      |  |  |  |  |

| Q1                                                          | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Q3                           | Q4                   |  |  |  |  |

| Decode                                                      | Read<br>register 'f'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Process<br>Data              | Write to destination |  |  |  |  |

| Example 1:                                                  | SUBWF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | REG, 1, 0                    |                      |  |  |  |  |

| Before Instruct<br>REG<br>W<br>C                            | tion<br>= 3<br>= 2<br>= ?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                              |                      |  |  |  |  |

| After Instructio<br>REG<br>W<br>C<br>Z<br>N                 | = 1<br>= 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | esult is positive            | 2                    |  |  |  |  |

| Example 2:                                                  | SUBWF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | REG, 0, 0                    |                      |  |  |  |  |

| Before Instruct<br>REG<br>C<br>After Instructio<br>REG<br>W | = 2<br>= 2<br>= ?<br>n<br>= 2<br>= 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                              |                      |  |  |  |  |

| C<br>Z<br>N                                                 | = 1 ; re<br>= 1<br>= 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | esult is zero                |                      |  |  |  |  |

| Example 3:                                                  | SUBWF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | REG, 1, 0                    |                      |  |  |  |  |

| Before Instruct<br>REG<br>W<br>C                            | tion<br>= 1<br>= 2<br>= ?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                              |                      |  |  |  |  |

| After Instructio<br>REG                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 's complement                | )                    |  |  |  |  |

| W<br>C<br>Z<br>N                                            | = 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | esult is negativ             | ,                    |  |  |  |  |

| SUBWFB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Subtract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | W from f with                                                                                                                                            | h Borrow                                                                   |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--|--|--|--|--|