#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| 2 0 0 0 0 0                |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                            |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-UQFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f25k42t-i-mv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

### REGISTER 3-4: DMA2PR: DMA2 PRIORITY REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-1/1 | R/W-1/1 |

|-------|-----|-----|-----|-----|---------|---------|---------|

| —     | —   | —   | —   | —   | DMA2PR2 | DMA2PR1 | DMA2PR0 |

| bit 7 |     |     |     |     |         |         | bit 0   |

#### Legend:

| R = Readable bit     | W = Writable bit   | U = Unimplemented bit, read as '0'                    |

|----------------------|--------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown | -n/n = Value at POR and BOR/Value at all other Resets |

| 1 = bit is set       | 0 = bit is cleared | HS = Hardware set                                     |

#### bit 7-3 Unimplemented: Read as '0'

bit 2-0 DMA2PR<2:0>: DMA2 Priority Selection bits

#### REGISTER 3-5: SCANPR: SCANNER PRIORITY REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-1/1 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|-----|---------|---------|---------|

| —     | —   | —   | —   | —   | SCANPR2 | SCANPR1 | SCANPR0 |

| bit 7 |     |     |     |     |         |         | bit 0   |

| Legend:              |                    |                                                       |

|----------------------|--------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit   | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown | -n/n = Value at POR and BOR/Value at all other Resets |

| 1 = bit is set       | 0 = bit is cleared | HS = Hardware set                                     |

#### bit 7-3 Unimplemented: Read as '0'

bit 2-0 SCANPR<2:0>: DMA2 Priority Selection bits

#### REGISTER 3-6: PRLOCK: PRIORITY LOCK REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0  |

|-------|-----|-----|-----|-----|-----|-----|----------|

| _     | —   | —   | —   | —   | —   | —   | PRLOCKED |

| bit 7 |     |     |     |     |     |     | bit 0    |

| Legend:              |                    |                                                       |

|----------------------|--------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit   | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown | -n/n = Value at POR and BOR/Value at all other Resets |

| 1 = bit is set       | 0 = bit is cleared | HS = Hardware set                                     |

bit 7-1 Unimplemented: Read as '0'

bit 0 **PRLOCKED**: PR Register Lock bit<sup>(1, 2)</sup>

0 = Priority Registers can be modified by write operations; Peripherals do not have access to the memory

1 = Priority Registers are locked and cannot be written; Peripherals do not have access to the memory

Note 1: The PRLOCKED bit can only be set or cleared after the unlock sequence.

2: If PR1WAY = 1, the PRLOCKED bit cannot be cleared after it has been set. A system Reset will clear the bit and allow one more set.

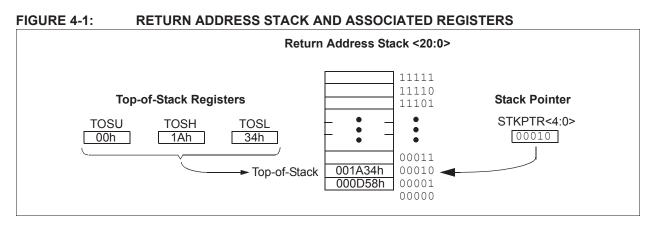

## 4.2.5.2 Return Stack Pointer (STKPTR)

The STKPTR register (Register 4-1) contains the Stack Pointer value. The STKOVF (Stack Overflow) Status bit and the STKUNF (Stack Underflow) Status bit can be accessed using the PCON0 register. The value of the Stack Pointer can be 0 through 31. On Reset, the Stack Pointer value will be zero. The user may read and write the Stack Pointer value. This feature can be used by a Real-Time Operating System (RTOS) for stack maintenance. After the PC is pushed onto the stack 32 times (without popping any values off the stack), the STKOVF bit is set. The STKOVF bit is cleared by software or by a POR. The action that takes place when the stack becomes full depends on the state of the STVREN (Stack Overflow Reset Enable) Configuration bit. (Refer to Section 5.1 "Configuration Words" for a description of the device Configuration bits.)

If STVREN is set (default), a Reset will be generated and a Stack Overflow will be indicated by the STKOVF bit when the 32nd push is initiated. This includes CALL and CALLW instructions, as well as stacking the return address during an interrupt response. The STKOVF bit will remain set and the Stack Pointer will be set to zero.

If STVREN is cleared, the STKOVF bit will be set on the 32nd push and the Stack Pointer will remain at 31 but no Reset will occur. Any additional pushes will overwrite the 31<sup>st</sup> push but the STKPTR will remain at 31.

Setting STKOVF = 1 in software will change the bit, but will not generate a Reset.

The STKUNF bit is set when a stack pop returns a value of zero. The STKUNF bit is cleared by software or by POR. The action that takes place when the stack becomes full depends on the state of the STVREN (Stack Overflow Reset Enable) Configuration bit. (Refer to **Section 5.1 "Configuration Words**" for a description of the device Configuration bits).

If STVREN is set (default) and the stack has been popped enough times to unload the stack, the next pop will return a value of zero to the PC, it will set the STKUNF bit and a Reset will be generated. This condition can be generated by the RETURN, RETLW and RETFIE instructions.

When STVREN = 0, STKUNF will be set but no Reset will occur.

| Note: | Returning a value of zero to the PC on an underflow has the effect of vectoring the                                                                                     |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | program to the Reset vector, where the<br>stack conditions can be verified and<br>appropriate actions can be taken. This is<br>not the same as a Reset, as the contents |

|       | of the SFRs are not affected.                                                                                                                                           |

#### 4.2.5.3 PUSH and POP Instructions

Since the Top-of-Stack is readable and writable, the ability to push values onto the stack and pull values off the stack without disturbing normal program execution is a desirable feature. The PIC18 instruction set includes two instructions, PUSH and POP, that permit the TOS to be manipulated under software control. TOSU, TOSH and TOSL can be modified to place data or a return address on the stack.

The PUSH instruction places the current PC value onto the stack. This increments the Stack Pointer and loads the current PC value onto the stack.

The POP instruction discards the current TOS by decrementing the Stack Pointer. The previous value pushed onto the stack then becomes the TOS value.

| Address          | Name     | Bit 7                                                                                                    | Bit 6                                                                         | Bit 5         | Bit 4          | Bit 3           | Bit 2           | Bit 1           | Bit 0       | <u>Value on</u><br>POR, BOR |

|------------------|----------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|---------------|----------------|-----------------|-----------------|-----------------|-------------|-----------------------------|

| 3FFFh            | TOSU     | —                                                                                                        | _                                                                             | —             |                | Тор             | o of Stack Uppe | er byte         |             | xxxxx                       |

| 3FFEh            | TOSH     |                                                                                                          |                                                                               |               | Top of Stac    | k High byte     |                 |                 |             | XXXXXXXX                    |

| 3FFDh            | TOSL     |                                                                                                          |                                                                               |               | Top of Stac    | k Low byte      |                 |                 |             | XXXXXXXX                    |

| 3FFCh            | STKPTR   | —                                                                                                        | _                                                                             | _             |                |                 | Stack Pointe    | r               |             | 00000                       |

| 3FFBh            | PCLATU   | _                                                                                                        | _                                                                             | —             |                | Holding I       | Register for PC | Upper byte      |             | 00000                       |

| 3FFAh            | PCLATH   |                                                                                                          |                                                                               | Ho            | lding Register | for PC High b   | yte             |                 |             | 00000000                    |

| 3FF9h            | PCL      |                                                                                                          |                                                                               |               | PC Lo          | w byte          |                 |                 |             | 00000000                    |

| 3FF8h            | TBLPTRU  | —                                                                                                        | _                                                                             |               | Progr          | am Memory T     | able Pointer U  | oper byte       |             | 000000                      |

| 3FF7h            | TBLPTRH  |                                                                                                          |                                                                               | Progra        | m Memory Ta    | ble Pointer Hig | gh byte         |                 |             | 00000000                    |

| 3FF6h            | TBLPTRL  |                                                                                                          |                                                                               | Progra        | m Memory Ta    | ble Pointer Lo  | w byte          |                 |             | 00000000                    |

| 3FF5h            | TABLAT   |                                                                                                          |                                                                               |               | Table          | Latch           |                 |                 |             | 00000000                    |

| 3FF4h            | PRODH    |                                                                                                          |                                                                               |               | Product Regis  | ster High byte  |                 |                 |             | XXXXXXXX                    |

| 3FF3h            | PRODL    |                                                                                                          |                                                                               |               | Product Regi   | ster Low byte   |                 |                 |             | XXXXXXXX                    |

| 3FF2h            | _        |                                                                                                          |                                                                               |               | Unimple        | emented         |                 |                 |             | _                           |

| 3FF1h            | PCON1    | —                                                                                                        | _                                                                             | _             | _              | _               | _               | MEMV            | _           | 1-                          |

| 3FF0h            | PCON0    | STKOVF                                                                                                   | STKUNF                                                                        | WDTWV         | RWDT           | RMCLR           | RI              | POR             | BOR         | 0011110q                    |

| 3FEFh            | INDF0    | Uses contents                                                                                            | of FSR0 to add                                                                | ress data men | nory – value o | f FSR0 not ch   | anged           | •               | •           | XXXXXXXX                    |

| 3FEEh            | POSTINC0 | Uses contents                                                                                            | of FSR0 to add                                                                | ress data men | nory – value o | f FSR0 post-ii  | ncremented      |                 |             |                             |

| 3FEDh            | POSTDEC0 | Uses contents                                                                                            | Jses contents of FSR0 to address data memory – value of FSR0 post-decremented |               |                |                 |                 |                 |             |                             |

| 3FECh            | PREINC0  | Uses contents of FSR0 to address data memory – value of FSR0 pre-incremented                             |                                                                               |               |                |                 |                 |                 |             |                             |

| 3FEBh            | PLUSW0   | Uses contents of FSR0 to address data memory – value of FSR0 pre-incremented – value of FSR0 offset by W |                                                                               |               |                |                 |                 |                 |             |                             |

| 3FEAh            | FSR0H    | _                                                                                                        | — Indirect Data Memory Address Pointer 0 High                                 |               |                |                 |                 |                 |             | 000000                      |

| 3FE9h            | FSR0L    |                                                                                                          | Indirect Data Memory Address Pointer 0 Low                                    |               |                |                 |                 |                 |             |                             |

| 3FE8h            | WREG     |                                                                                                          | Working Register                                                              |               |                |                 |                 |                 |             |                             |

| 3FE7h            | INDF1    | Uses contents                                                                                            | of FSR1 to add                                                                | ress data men | nory – value o | f FSR1 not ch   | anged           |                 |             | XXXXXXXX                    |

| 3FE6h            | POSTINC1 | Uses contents                                                                                            | of FSR1 to add                                                                | ress data men | nory – value o | f FSR1 post-ii  | ncremented      |                 |             |                             |

| 3FE5h            | POSTDEC1 | Uses contents                                                                                            | of FSR1 to add                                                                | ress data men | nory – value o | f FSR1 post-d   | lecremented     |                 |             |                             |

| 3FE4h            | PREINC1  | Uses contents                                                                                            | of FSR1 to add                                                                | ress data men | nory – value o | f FSR1 pre-in   | cremented       |                 |             |                             |

| 3FE3h            | PLUSW1   | Uses contents                                                                                            | of FSR1 to add                                                                | ress data men | nory – value o | f FSR1 pre-in   | cremented – va  | alue of FSR1 of | offset by W |                             |

| 3FE2h            | FSR1H    | —                                                                                                        | _                                                                             |               | Indirec        | t Data Memor    | y Address Poir  | nter 1 High     |             | 000000                      |

| 3FE1h            | FSR1L    |                                                                                                          |                                                                               | Indirect [    | Data Memory    | Address Point   | er 1 Low        |                 |             | 00000000                    |

| 3FE0h            | BSR      | —                                                                                                        | _                                                                             |               |                | Bank Se         | lect Register   |                 |             | 000000                      |

| 3FDFh            | INDF2    | Uses contents                                                                                            | of FSR2 to add                                                                | ress data men | nory – value o | f FSR2 not ch   | anged           |                 |             | XXXXXXXX                    |

| 3FDEh            | POSTINC2 | Uses contents                                                                                            | of FSR2 to add                                                                | ress data men | nory – value o | f FSR2 post-ii  | ncremented      |                 |             |                             |

| 3FDDh            | POSTDEC2 | Uses contents                                                                                            | of FSR2 to add                                                                | ress data men | nory – value o | f FSR2 post-d   | lecremented     |                 |             |                             |

| 3FDCh            | PREINC2  | Uses contents                                                                                            | of FSR2 to add                                                                | ress data men | nory – value o | f FSR2 pre-in   | cremented       |                 |             |                             |

| 3FDBh            | PLUSW2   | Uses contents                                                                                            | of FSR2 to add                                                                | ress data men | nory – value o | f FSR2 pre-in   | cremented – va  | alue of FSR2 of | offset by W |                             |

| 3FDAh            | FSR2H    | _                                                                                                        | _                                                                             |               | Indirec        | t Data Memor    | y Address Poir  | ter 2 High      |             | 000000                      |

| 3FD9h            | FSR2L    |                                                                                                          |                                                                               | Indirect [    | Data Memory    | Address Point   | er 2 Low        |                 |             | 00000000                    |

| 3FD8h            | STATUS   | —                                                                                                        | TO                                                                            | PD            | Ν              | OV              | Z               | DC              | С           | -1100000                    |

| 3FD7h            | IVTBASEU | _                                                                                                        | _                                                                             | —             | BASE20         | BASE19          | BASE18          | BASE17          | BASE16      | 00000                       |

| 3FD6h            | IVTBASEH | BASE15                                                                                                   | BASE14                                                                        | BASE13        | BASE12         | BASE11          | BASE10          | BASE9           | BASE8       | 00000000                    |

| 3FD5h            | IVTBASEL | BASE7                                                                                                    | BASE6                                                                         | BASE5         | BASE4          | BASE3           | BASE2           | BASE1           | BASE0       | 00001000                    |

| 3FD4h            | IVTLOCK  | —                                                                                                        |                                                                               | _             | —              | —               | —               | _               | IVTLOCKED   | 0                           |

| 3FD3h            | INTCON1  | ST                                                                                                       | AT                                                                            | _             | _              | _               | _               | _               | _           | 00                          |

| 3FD2h            | INTCON0  | GIE                                                                                                      | GIEL                                                                          | IPEN          | _              | _               | INT2EDG         | INT1EDG         | INT0EDG     | 000111                      |

| 3FD1h -<br>3FCFh | -        |                                                                                                          |                                                                               |               | Unimple        | emented         | ı               |                 |             | —                           |

## TABLE 4-11: REGISTER FILE SUMMARY FOR PIC18(L)F24/25K42 DEVICES

Note 1: Not present in LF devices.

|                 |                              |                              |                    | ,                   |                   |                 |            |

|-----------------|------------------------------|------------------------------|--------------------|---------------------|-------------------|-----------------|------------|

| R/W-1/1         | R/W-1/1                      | R/W-1/1                      | R/W-1/1            | R/W-1/1             | R/W-1/1           | R/W-1/1         | R/W-1/1    |

| I2C2TXIP        | I2C2RXIP                     | DMA2AIP                      | DMA2ORIP           | DMA2DCNTIP          | DMA2SCNTIP        | C2IP            | INT1IP     |

| bit 7           |                              |                              |                    |                     |                   |                 | bit        |

|                 |                              |                              |                    |                     |                   |                 |            |

| Legend:         |                              |                              |                    |                     |                   |                 |            |

| R = Readab      | le bit                       | W = Writable b               | it                 | U = Unimpleme       | ented bit, read a | s '0'           |            |

| u = Bit is un   | changed                      | x = Bit is unkno             | own                | -n/n = Value at     | POR and BOR/      | Value at all ot | her Resets |

| '1' = Bit is se | et                           | '0' = Bit is clea            | red                |                     |                   |                 |            |

|                 |                              |                              |                    |                     |                   |                 |            |

| bit 7           | I2C2TXIP: I                  | <sup>2</sup> C2 Transmit Int | errupt Priority b  | it                  |                   |                 |            |

|                 | 1 = High pri                 |                              |                    |                     |                   |                 |            |

|                 | 0 = Low price                | •                            |                    |                     |                   |                 |            |

| bit 6           |                              | <sup>2</sup> C2 Receive Inte | errupt Priority bi | t                   |                   |                 |            |

|                 | 1 = High pri<br>0 = Low pric |                              |                    |                     |                   |                 |            |

| bit 5           | •                            | DMA2 Abort Inte              | rrupt Drigrity bit |                     |                   |                 |            |

| DIL D           | 1 = High pri                 |                              | παρι Εποπιγ διι    |                     |                   |                 |            |

|                 | 0 = Low price                |                              |                    |                     |                   |                 |            |

| bit 4           | DMA2ORIP:                    | : DMA2 Overrun               | Interrupt Priorit  | y bit               |                   |                 |            |

|                 | 1 = High pri                 | ority                        |                    | -                   |                   |                 |            |

|                 | 0 = Low price                | ority                        |                    |                     |                   |                 |            |

| bit 3           | DMA2DCNT                     | IP: DMA2 Destin              | nation Count Int   | errupt Priority bit |                   |                 |            |

|                 | 1 = High pri                 |                              |                    |                     |                   |                 |            |

| 1.1.0           | 0 = Low price                |                              |                    |                     |                   |                 |            |

| bit 2           |                              | <b>IP:</b> DMA2 Source       | ce Count Interru   | pt Priority bit     |                   |                 |            |

|                 | 1 = High pri<br>0 = Low pric |                              |                    |                     |                   |                 |            |

| bit 1           |                              | errupt Priority bi           | t                  |                     |                   |                 |            |

|                 | 1 = High pri                 |                              | •                  |                     |                   |                 |            |

|                 | 0 = Low price                |                              |                    |                     |                   |                 |            |

| bit 0           | INT1IP: Exte                 | ernal Interrupt 1            | Interrupt Priority | / bit               |                   |                 |            |

|                 | 1 = High pri                 |                              |                    |                     |                   |                 |            |

|                 | 0 = Low price                | ority                        |                    |                     |                   |                 |            |

## REGISTER 11-30: IPR5: PERIPHERAL INTERRUPT Priority REGISTER 5

© 2016-2017 Microchip Technology Inc.

## 20.0 INTERRUPT-ON-CHANGE

PORTA, PORTB, PORTC and pin RE3 of PORTE can be configured to operate as Interrupt-on-Change (IOC) pins on PIC18(L)F2x/4xK42 family devices. An interrupt can be generated by detecting a signal that has either a rising edge or a falling edge. Any individual port pin, or combination of port pins, can be configured to generate an interrupt. The interrupt-on-change module has the following features:

- Interrupt-on-Change enable (Master Switch)

- Individual pin configuration

- · Rising and falling edge detection

- · Individual pin interrupt flags

Figure 20-1 is a block diagram of the IOC module.

### 20.1 Enabling the Module

To allow individual port pins to generate an interrupt, the IOCIE bit of the PIE0 register must be set. If the IOCIE bit is disabled, the edge detection on the pin will still occur, but an interrupt will not be generated.

## 20.2 Individual Pin Configuration

For each port pin, a rising edge detector and a falling edge detector are present. To enable a pin to detect a rising edge, the associated bit of the IOCxP register is set. To enable a pin to detect a falling edge, the associated bit of the IOCxN register is set.

A pin can be configured to detect rising and falling edges simultaneously by setting both associated bits of the IOCxP and IOCxN registers, respectively.

## 20.3 Interrupt Flags

The IOCAFx, IOCBFx, IOCCFx and IOCEF3 bits located in the IOCAF, IOCBF, IOCCF and IOCEF registers respectively, are status flags that correspond to the interrupt-on-change pins of the associated port. If an expected edge is detected on an appropriately enabled pin, then the status flag for that pin will be set, and an interrupt will be generated if the IOCIE bit is set. The IOCIF bit of the PIRO register reflects the status of all IOCAFx, IOCBFx, IOCCFx and IOCEF3 bits.

## 20.4 Clearing Interrupt Flags

The individual status flags, (IOCAFx, IOCBFx, IOCCFx and IOCEF3 bits), can be cleared by resetting them to zero. If another edge is detected during this clearing operation, the associated status flag will be set at the end of the sequence, regardless of the value actually being written.

In order to ensure that no detected edge is lost while clearing flags, only AND operations masking out known changed bits should be performed. The following sequence is an example of what should be performed.

#### EXAMPLE 20-1: CLEARING INTERRUPT FLAGS (PORTA EXAMPLE)

| MOVIW   | 0xff   |    |

|---------|--------|----|

| 110 1 2 | 011111 |    |

| XORWF   | IOCAF, | W  |

|         |        | _  |

| ANDWF   | IOCAF, | F. |

|         |        |    |

## 20.5 Operation in Sleep

The interrupt-on-change interrupt sequence will wake the device from Sleep mode, if the IOCIE bit is set.

If an edge is detected while in Sleep mode, the IOCxF register will be updated prior to the first instruction executed out of Sleep.

#### REGISTER 25-3: CCPxCAP: CAPTURE INPUT SELECTION MULTIPLEXER REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/x | R/W-0/x  | R/W-0/x |

|-------|-----|-----|-----|-----|---------|----------|---------|

| —     | —   | —   | —   | —   |         | CTS<2:0> |         |

| bit 7 |     |     |     |     |         |          | bit 0   |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 7-3 Unimplemented: Read as '0'

bit 2-0 CTS<2:0>: Capture Trigger Input Selection bits

| CTS<1:0> | Connection                 |        |          |      |  |  |

|----------|----------------------------|--------|----------|------|--|--|

| 013<1.02 | CCP1                       | CCP2   | CCP3     | CCP4 |  |  |

| 111      |                            | CLC4   | 4_out    |      |  |  |

| 110      |                            | CLC    | 3_out    |      |  |  |

| 101      | CLC2_out                   |        |          |      |  |  |

| 100      |                            | CLC    | 1_out    |      |  |  |

| 011      |                            | IOC_Ir | iterrupt |      |  |  |

| 010      | CMP2_output                |        |          |      |  |  |

| 001      | CMP1_output                |        |          |      |  |  |

| 000      | Pin selected by<br>CCP1PPS |        |          |      |  |  |

#### REGISTER 25-4: CCPRxL: CCPx REGISTER LOW BYTE

| R/W-x/x |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | RL<     | 7:0>    |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7-0

MODE = Capture Mode:

RL<7:0>: LSB of captured TMR1 value

MODE = Compare Mode:

RL<7:0>: LSB compared to TMR1 value

MODE = PWM Mode && FMT = 0:

RL<7:0>: CCPW<7:0> - Pulse-Width LS 8 bits

MODE = PWM Mode && FMT = 1:

RL<7:6>: CCPW<1:0> - Pulse-Width LS 2 bits

RL<5:0>: Not used

© 2016-2017 Microchip Technology Inc.

| R/W-0/0                                                                                                                                                      | R/W-1/1 | R/W-0/0          | R/W-1/1 | R/W-0/0           | R/W-1/1          | R/W-0/0         | R/W-1/1 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------------|---------|-------------------|------------------|-----------------|---------|

| P8TSEL<1:0>                                                                                                                                                  |         | P7TSEL<1:0>      |         | P6TSEL<1:0>       |                  | P5TSEL<1:0>     |         |

| bit 7                                                                                                                                                        |         |                  |         |                   |                  | ·               | bit 0   |

|                                                                                                                                                              |         |                  |         |                   |                  |                 |         |

| Legend:                                                                                                                                                      |         |                  |         |                   |                  |                 |         |

| R = Readable                                                                                                                                                 | bit     | W = Writable     | bit     | U = Unimplen      | nented bit, read | d as '0'        |         |

| -n = Value at I                                                                                                                                              | POR     | '1' = Bit is set |         | '0' = Bit is clea | ared             | x = Bit is unkr | nown    |

| bit 7-6 <b>P8TSEL&lt;1:0&gt;:</b> PWM8 Timer Selection bit<br>11 = PWM8 based on TMR6<br>10 = PWM8 based on TMR4<br>01 = PWM8 based on TMR2<br>00 = Reserved |         |                  | S       |                   |                  |                 |         |

| bit 5-4 <b>P7TSEL&lt;1:0&gt;:</b> PWM7 Timer Selection bi<br>11 = PWM7 based on TMR6<br>10 = PWM7 based on TMR4<br>01 = PWM7 based on TMR2<br>00 = Reserved  |         |                  | S       |                   |                  |                 |         |

| bit 3-2 P6TSEL<1:0>: PWM6 Timer Selection b 11 = PWM6 based on TMR6 10 = PWM6 based on TMR4 01 = PWM6 based on TMR2 00 = Reserved                            |         |                  | S       |                   |                  |                 |         |

|                                                                                                                                                              |         |                  | s       |                   |                  |                 |         |

## REGISTER 26-2: CCPTMRS1: CCP TIMERS CONTROL REGISTER 1

## 28.0 COMPLEMENTARY WAVEFORM GENERATOR (CWG) MODULE

The Complementary Waveform Generator (CWG) produces half-bridge, full-bridge, and steering of PWM waveforms. It is backwards compatible with previous CCP functions. The PIC18(L)F2x/4xK42 family has three instances of the CWG module.

Each of the CWG modules has the following features:

- Six operating modes:

- Synchronous Steering mode

- Asynchronous Steering mode

- Full-Bridge mode, Forward

- Full-Bridge mode, Reverse

- Half-Bridge mode

- Push-Pull mode

- Output polarity control

- Output steering

- Independent 6-bit rising and falling event deadband timers

- Clocked dead band

- Independent rising and falling dead-band enables

- Auto-shutdown control with:

- Selectable shutdown sources

- Auto-restart option

- Auto-shutdown pin override control

## 28.1 Fundamental Operation

The CWG generates two output waveforms from the selected input source.

The off-to-on transition of each output can be delayed from the on-to-off transition of the other output, thereby, creating a time delay immediately where neither output is driven. This is referred to as dead time and is covered in **Section 28.6 "Dead-Band Control"**.

It may be necessary to guard against the possibility of circuit faults or a feedback event arriving too late or not at all. In this case, the active drive must be terminated before the Fault condition causes damage. This is referred to as auto-shutdown and is covered in **Section 28.10 "Auto-Shutdown"**.

## 28.2 Operating Modes

The CWG module can operate in six different modes, as specified by the MODE<2:0> bits of the CWGxCON0 register:

- · Half-Bridge mode

- Push-Pull mode

- Asynchronous Steering mode

- Synchronous Steering mode

- Full-Bridge mode, Forward

- Full-Bridge mode, Reverse

All modes accept a single pulse data input, and provide up to four outputs as described in the following sections.

All modes include auto-shutdown control as described in Section 28.10 "Auto-Shutdown"

Note: Except as noted for Full-bridge mode (Section 28.2.3 "Full-Bridge Modes"), mode changes should only be performed while EN = 0 (Register 28-1).

#### 28.2.1 HALF-BRIDGE MODE

In Half-Bridge mode, two output signals are generated as true and inverted versions of the input as illustrated in Figure 28-2. A non-overlap (dead-band) time is inserted between the two outputs as described in **Section 28.6 "Dead-Band Control"**. The output steering feature cannot be used in this mode. A basic block diagram of this mode is shown in Figure 28-1.

The unused outputs CWGxC and CWGxD drive similar signals as CWGxA and CWGxB, with polarity independently controlled by the POLC and POLD bits of the CWGxCON1 register, respectively.

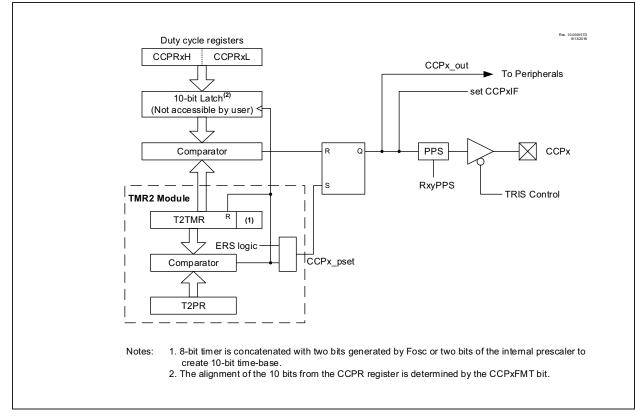

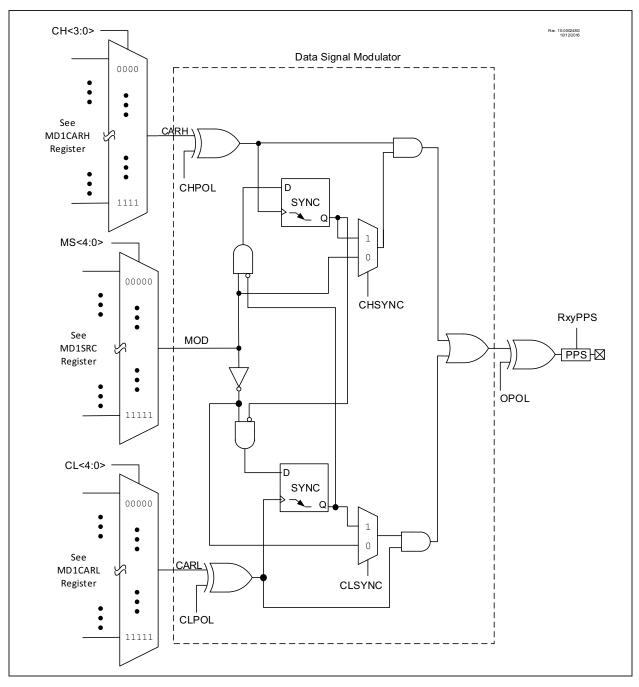

#### FIGURE 32-1: SIMPLIFIED BLOCK DIAGRAM OF THE DATA SIGNAL MODULATOR

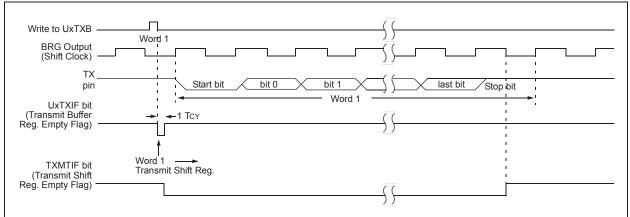

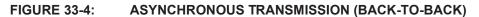

#### 33.2.1.8 Asynchronous Transmission Setup

- Initialize the UxBRGH, UxBRGL register pair and the BRGS bit to achieve the desired baud rate (see Section 33.17 "UART Baud Rate Generator (BRG)").

- 2. Set the MODE<3:0> bits to the desired asynchronous mode.

- 3. Set TXPOL bit if inverted TX output is desired.

- 4. Enable the asynchronous serial port by setting the ON bit.

- 5. Enable the transmitter by setting the TXEN control bit. This will cause the UxTXIF interrupt flag to be set.

- If the device has PPS, configure the desired I/O pin RxyPPS register with the code for TX output.

- If interrupts are desired, set the UxTXIE interrupt enable bit in the respective PIE register. An interrupt will occur immediately provided that the GIE bits in the INTCON0 register are also set.

- 8. Write one byte of data into the UxTXB register. This will start the transmission.

- 9. Subsequent bytes may be written when the UxTXIF bit is '1'.

#### FIGURE 33-3: ASYNCHRONOUS TRANSMISSION

## 33.16 Clock Accuracy with Asynchronous Operation

The factory calibrates the internal oscillator block output (INTOSC). However, the INTOSC frequency may drift as VDD or temperature changes, and this directly affects the asynchronous baud rate. Two methods may be used to adjust the baud rate clock, but both require a reference clock source of some kind.

The first (preferred) method uses the OSCTUNE register to adjust the INTOSC output. Adjusting the value of the OSCTUNE register allows for fine resolution changes to the system clock source. See Section 6.2.2.3 "Internal Oscillator Frequency Adjustment" for more information.

The other method adjusts the value of the Baud Rate Generator. This can be done automatically with the Auto-Baud Detect feature (see Section 33.17.1 "Auto-Baud Detect"). There may not be fine enough resolution when adjusting the Baud Rate Generator to compensate for a gradual change of the peripheral clock frequency.

## 33.17 UART Baud Rate Generator (BRG)

The Baud Rate Generator (BRG) is a 16-bit timer that is dedicated to the support of the UART operation.

The UxBRGH, UxBRGL register pair determines the period of the free running baud rate timer. The multiplier of the baud rate period is determined by the BRGS bit in the UxCON0 register.

Table 33-1 contains the formulas for determining the baud rate. Example 33-1 provides a sample calculation for determining the baud rate and baud rate error.

The high baud rate range (BRGS = 1) is intended to extend the baud rate range up to a faster rate when the desired baud rate is not possible otherwise. Using the normal baud rate range (BRGS = 0) is recommended when the desired baud rate is achievable with either range.

Writing a new value to the UxBRGH, UxBRGL register pair causes the BRG timer to be reset (or cleared). This ensures that the BRG does not wait for a timer overflow before outputting the new baud rate.

If the system clock is changed during an active receive operation, a receive error or data loss may result. To avoid this problem, check the status of the RXIDL bit to make sure that the receive operation is idle before changing the system clock.

#### EXAMPLE 33-1: CALCULATING BAUD RATE ERROR

| For a device with Fosc of 16 MHz, desired baud rate of 9600, Asynchronous mode, BRGS = 0: |

|-------------------------------------------------------------------------------------------|

| Desired Baud Rate = $\frac{Fosc}{16([UxBRG] + 1)}$                                        |

| $X = \frac{FOSC}{\frac{Desired Baud Rate}{16} - 1}$                                       |

| $=\frac{\frac{16000000}{9600}}{\frac{16}{16}}-1$                                          |

| = [103.17] = 103                                                                          |

| Calculated Baud Rate = $\frac{16000000}{16(103+1)}$                                       |

| = 9615                                                                                    |

| Error = $\frac{Calc. Baud Rate - Desired Baud Rate}{Desired Baud Rate}$                   |

| $=\frac{(9615-9600)}{9600}=0.16\%$                                                        |

### TABLE 33-1: BAUD RATE FORMULAS

| BRGS | BRG/UART Mode | Baud Rate Formula |

|------|---------------|-------------------|

| 1    | High Rate     | Fosc/[4 (n+1)]    |

| 0    | Normal Rate   | Fosc/[16(n+1)]    |

**Legend:** n = value of UxBRGH, UxBRGL register pair.

## **39.6 Register Definitions: DAC Control**

Long bit name prefixes for the DAC peripheral is shown in Table 39-1. Refer to **Section 1.4.2.2 "Long Bit Names**" for more information.

#### TABLE 39-1:

| Peripheral | Bit Name Prefix |

|------------|-----------------|

| DAC1       | DAC1            |

## REGISTER 39-1: DAC1CON0: DAC CONTROL REGISTER

| R/W-0/0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | R/W-0/0 |

|---------|-----|---------|---------|---------|---------|-----|---------|

| EN      | —   | OE1     | OE2     | PSS     | <1:0>   | —   | NSS     |

| bit 7   |     |         |         |         |         |     | bit 0   |

|         |     |         |         |         |         |     |         |

L

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | EN: DAC Enable bit<br>1 = DAC is enabled<br>0 = DAC is disabled <sup>(1)</sup>                                                                                                           |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | Unimplemented: Read as '0'                                                                                                                                                               |

| bit 5   | <ul> <li>OE1: DAC Voltage Output Enable bit</li> <li>1 = DAC voltage level is output on the DAC1OUT1 pin</li> <li>0 = DAC voltage level is disconnected from the DAC1OUT1 pin</li> </ul> |

| bit 4   | <ul> <li>OE2: DAC Voltage Output Enable bit</li> <li>1 = DAC voltage level is output on the DAC1OUT2 pin</li> <li>0 = DAC voltage level is disconnected from the DAC1OUT2 pin</li> </ul> |

| bit 3-2 | <pre>PSS&lt;1:0&gt;: DAC Positive Source Select bit 11 = Reserved 10 = FVR buffer 2 01 = VREF+ 00 = VDD</pre>                                                                            |

| bit 1   | Unimplemented: Read as '0'                                                                                                                                                               |

| bit 0   | NSS: DAC Negative Source Select bit<br>1 = VREF-<br>0 = VSS                                                                                                                              |

| Note 1: | DAC1OUTx output pins are still active.                                                                                                                                                   |

© 2016-2017 Microchip Technology Inc.

| NEGF              | Negate f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:           | NEGF f {,a}                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 255 \\ a \in [0,1] \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Operation:        | $(\overline{f}) + 1 \rightarrow f$                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Status Affected:  | N, OV, C, DC, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Encoding:         | 0110 110a ffff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Description:      | Location 'f' is negated using two's complement. The result is placed in the data memory location 'f'.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the GPR bank.<br>If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever $f \le 95$ (5Fh). See Section 43.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode" for details. |

| Words:            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Cycles:           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Q Cycle Activity: |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| NOP               |        | No Operation  |           |     |           |  |  |

|-------------------|--------|---------------|-----------|-----|-----------|--|--|

| Synta             | ax:    | NOP           |           |     |           |  |  |

| Operands:         |        | None          |           |     |           |  |  |

| Operation:        |        | No operation  |           |     |           |  |  |

| Status Affected:  |        | None          |           |     |           |  |  |

| Encoding:         |        | 0000          | 0000      | 000 | 0000 00   |  |  |

|                   |        | 1111          | XXXX      | XXX | XX XXXX   |  |  |

| Description:      |        | No operation. |           |     |           |  |  |

| Words:            |        | 1             |           |     |           |  |  |

| Cycles:           |        | 1             |           |     |           |  |  |

| Q Cycle Activity: |        |               |           |     |           |  |  |

|                   | Q1     | Q2            | Q         | 3   | Q4        |  |  |

|                   | Decode | No            | No        | )   | No        |  |  |

|                   |        | operation     | operation |     | operation |  |  |

Example:

None.

Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4           |

|--------|--------------|---------|--------------|

| Decode | Read         | Process | Write        |

|        | register 'f' | Data    | register 'f' |

Example: NEGF REG, 1

> Before Instruction REG = 0011 1010 [3Ah] After Instruction REG = 1100 0110 [C6h]

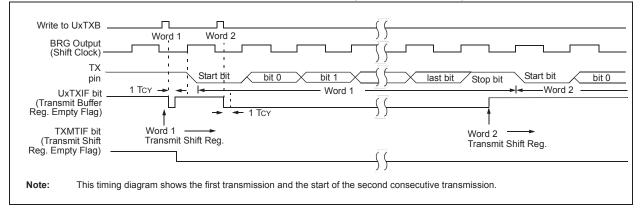

## 28-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

|                          | Units MILLIMETERS |          |       | 6     |  |

|--------------------------|-------------------|----------|-------|-------|--|

| Dimension                | Dimension Limits  |          | NOM   | MAX   |  |

| Number of Pins           | Ν                 | 28       |       |       |  |

| Pitch                    | е                 | 0.65 BSC |       |       |  |

| Overall Height           | Α                 | -        | -     | 2.00  |  |

| Molded Package Thickness | A2                | 1.65     | 1.75  | 1.85  |  |

| Standoff                 | A1                | 0.05     | -     | -     |  |

| Overall Width            | Е                 | 7.40     | 7.80  | 8.20  |  |

| Molded Package Width     | E1                | 5.00     | 5.30  | 5.60  |  |

| Overall Length           | D                 | 9.90     | 10.20 | 10.50 |  |

| Foot Length              | L                 | 0.55     | 0.75  | 0.95  |  |

| Footprint                | L1                | 1.25 REF |       |       |  |

| Lead Thickness           | с                 | 0.09     | -     | 0.25  |  |

| Foot Angle               | φ                 | 0°       | 4°    | 8°    |  |

| Lead Width               | b                 | 0.22     | -     | 0.38  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-073B

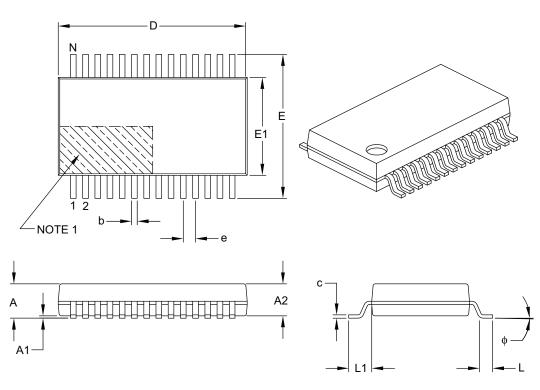

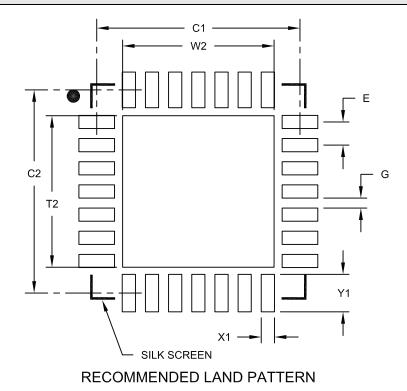

## 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units |      | ETERS    |      |

|----------------------------|-------|------|----------|------|

| Dimension Limits           |       | MIN  | NOM      | MAX  |

| Contact Pitch              | E     |      | 0.65 BSC |      |

| Optional Center Pad Width  | W2    |      |          | 4.25 |

| Optional Center Pad Length | T2    |      |          | 4.25 |

| Contact Pad Spacing        | C1    |      | 5.70     |      |

| Contact Pad Spacing        | C2    |      | 5.70     |      |

| Contact Pad Width (X28)    | X1    |      |          | 0.37 |

| Contact Pad Length (X28)   | Y1    |      |          | 1.00 |

| Distance Between Pads      | G     | 0.20 |          |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2105A