Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                            |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 16KB (8K x 16)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-QFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf24k42-e-ml |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 1-1: DEVICE FEATURES

| Features                                                                         | PIC18(L)F24K42                                                          | PIC18(L)F25K42                                                                     |  |  |  |

|----------------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------|--|--|--|

| Program Memory (Bytes)                                                           | 16384                                                                   | 32768                                                                              |  |  |  |

| Program Memory (Instructions)                                                    | 8192                                                                    | 16384                                                                              |  |  |  |

| Data Memory (Bytes)                                                              | 1024                                                                    | 2048                                                                               |  |  |  |

| Data EEPROM Memory (Bytes)                                                       | 256                                                                     | 256                                                                                |  |  |  |

| I/O Ports                                                                        | A,B,C,E <sup>(1)</sup>                                                  | A,B,C,E <sup>(1)</sup>                                                             |  |  |  |

| Capture/Compare/PWM Modules (CCP)                                                | 4                                                                       | 4                                                                                  |  |  |  |

| 10-Bit Pulse-Width Modulator (PWM)                                               | 4                                                                       | 4                                                                                  |  |  |  |

| 12-Bit Analog-to-Digital Module (ADC <sup>2</sup> ) with Computation Accelerator | 5 internal<br>24 external                                               | 5 internal<br>24 external                                                          |  |  |  |

| Packages                                                                         | 28-pin SPDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin QFN<br>28-pin UQFN | 28-pin SPDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin QFN<br>28-pin UQFN            |  |  |  |

| Timers (16-/8-bit)                                                               |                                                                         | /3                                                                                 |  |  |  |

| Serial Communications                                                            | 2 UART, 2                                                               | 2 I <sup>2</sup> C, 1 SPI                                                          |  |  |  |

| Enhanced Complementary Waveform Generator (ECWG)                                 |                                                                         | 3                                                                                  |  |  |  |

| Zero-Cross Detect (ZCD)                                                          |                                                                         | 1                                                                                  |  |  |  |

| Data Signal Modulator (DSM)                                                      | 1                                                                       |                                                                                    |  |  |  |

| Signal Measurement Timer (SMT)                                                   |                                                                         | 1                                                                                  |  |  |  |

| 5-Bit Digital-to-Analog Converter (DAC)                                          | 1                                                                       |                                                                                    |  |  |  |

| Numerically Controlled Oscillator (NCO)                                          | 1                                                                       |                                                                                    |  |  |  |

| Comparator Module                                                                |                                                                         | 2                                                                                  |  |  |  |

| Direct Memory Access (DMA)                                                       |                                                                         | 2                                                                                  |  |  |  |

| Configurable Logic Cell (CLC)                                                    |                                                                         | 4                                                                                  |  |  |  |

| Peripheral Pin Select (PPS)                                                      | Y                                                                       | es                                                                                 |  |  |  |

| Peripheral Module Disable (PMD)                                                  | Y                                                                       | es                                                                                 |  |  |  |

| 16-bit CRC with Scanner                                                          | Y                                                                       | es                                                                                 |  |  |  |

| Programmable High/Low-Voltage Detect (HLVD)                                      | Y                                                                       | es                                                                                 |  |  |  |

| Programmable Brown-out Reset (BOR)                                               | Y                                                                       | es                                                                                 |  |  |  |

| Resets (and Delays)                                                              | RESET Ir<br>Stack C<br>Stack U<br>(PWR]                                 | BOR,<br>hstruction,<br>Overflow,<br>nderflow<br>r, OST),<br>ry Execution Violation |  |  |  |

| Instruction Set                                                                  |                                                                         | ructions;<br>struction Set enabled                                                 |  |  |  |

| Operating Frequency                                                              | 64                                                                      | MHz                                                                                |  |  |  |

**Note 1:** PORTE contains the single RE3 input-only pin.

| Address          | Name   | Bit 7  | Bit 6         | Bit 5  | Bit 4   | Bit 3   | Bit 2    | Bit 1  | Bit 0  | <u>Value on</u><br>POR, BOR |

|------------------|--------|--------|---------------|--------|---------|---------|----------|--------|--------|-----------------------------|

| 3FCEh            | PORTE  | _      | _             | _      | _       | RE3     | _        | _      | —      | x                           |

| 3FCDh            | _      |        |               |        | Unimple | emented | •        |        |        | -                           |

| 3FCCh            | PORTC  | RC7    | RC6           | RC5    | RC4     | RC3     | RC2      | RC1    | RC0    | *****                       |

| 3FCBh            | PORTB  | RB7    | RB6           | RB5    | RB4     | RB3     | RB2      | RB1    | RB0    | XXXXXXXX                    |

| 3FCAh            | PORTA  | RA7    | RA6           | RA5    | RA4     | RA3     | RA2      | RA1    | RA0    | XXXXXXXX                    |

| 3FC9h -<br>3FC5h | —      |        | Unimplemented |        |         |         |          |        |        |                             |

| 3FC4h            | TRISC  | TRISC7 | TRISC6        | TRISC5 | TRISC4  | TRISC3  | TRISC2   | TRISC1 | TRISC0 | 11111111                    |

| 3FC3h            | TRISB  | TRISB7 | TRISB6        | TRISB5 | TRISB4  | TRISB3  | TRISB2   | TRISB1 | TRISB0 | 11111111                    |

| 3FC2h            | TRISA  | TRISA7 | TRISA6        | TRISA5 | TRISA4  | TRISA3  | TRISA2   | TRISA1 | TRISA0 | 11111111                    |

| 3FC1h -<br>3FBDh | —      |        |               |        | Unimple | emented |          |        |        | —                           |

| 3FBCh            | LATC   | LATC7  | LATC6         | LATC5  | LATC4   | LATC3   | LATC2    | LATC1  | LATC0  | XXXXXXXX                    |

| 3FBBh            | LATB   | LATB7  | LATB6         | LATB5  | LATB4   | LATB3   | LATB2    | LATB1  | LATB0  | XXXXXXXX                    |

| 3FBAh            | LATA   | LATA7  | LATA6         | LATA5  | LATA4   | LATA3   | LATA2    | LATA1  | LATA0  | XXXXXXXX                    |

| 3FB9h            | T0CON1 |        | CS<2:0>       |        | ASYNC   |         | CKPS     | 8<3:0> |        | 00000000                    |

| 3FB8h            | T0CON0 | EN     | —             | OUT    | MD16    |         | OU       | TPS    |        | 0-000000                    |

| 3FB7h            | TMR0H  |        |               |        | TMF     | ROH     |          |        |        | 11111111                    |

| 3FB6h            | TMR0L  |        |               |        | TM      | R0L     |          |        |        | 00000000                    |

| 3FB5h            | T1CLK  |        |               |        | С       | S       |          |        |        | 00000                       |

| 3FB4h            | T1GATE |        |               |        | GS      | SS      |          |        |        | 00000                       |

| 3FB3h            | T1GCON | GE     | GPOL          | GTM    | GSPM    | GGO     | GVAL     | _      | _      | 00000x                      |

| 3FB2h            | T1CON  | —      | —             | CKPS   | <1:0>   | —       | SYNC     | RD16   | ON     | 00-000                      |

| 3FB1h            | TMR1H  |        |               |        | TMF     | R1H     |          |        |        | 00000000                    |

| 3FB0h            | TMR1L  |        |               |        | TM      | R1L     |          |        |        | 00000000                    |

| 3FAFh            | T2RST  | —      | —             | _      |         |         | RSEL     |        |        | 00000                       |

| 3FAEh            | T2CLK  | —      | —             | —      | —       |         | C        | S      |        | 0000                        |

| 3FADh            | T2HLT  | PSYNC  | CKPOL         | CKSYNC |         |         | MODE     |        |        | 00000000                    |

| 3FACh            | T2CON  | ON     |               | CKPS   |         |         | OU       | TPS    |        | 00000000                    |

| 3FABh            | T2PR   |        |               |        | PF      | R2      |          |        |        | 11111111                    |

| 3FAAh            | T2TMR  |        |               |        | TM      | IR2     |          |        |        | 00000000                    |

| 3FA9h            | T3CLK  |        |               |        | С       | S       |          |        |        | 00000                       |

| 3FA8h            | T3GATE |        |               |        | GS      | SS      |          |        |        | 00000                       |

| 3FA7h            | T3GCON | GE     | GPOL          | GTM    | GSPM    | GGO     | GVAL     | —      | —      | 00000x                      |

| 3FA6h            | T3CON  | —      | —             | СК     | PS      | —       | NOT_SYNC | RD16   | ON     | 00-000                      |

| 3FA5h            | TMR3H  |        |               |        | TMF     | R3H     |          |        |        | 00000000                    |

| 3FA4h            | TMR3L  |        |               |        | TM      | R3L     |          |        |        | 00000000                    |

| 3FA3h            | T4RST  | —      | —             | —      |         |         | RSEL     |        |        | 00000                       |

| 3FA2h            | T4CLK  | —      | —             | —      |         |         | C        | S      |        | 0000                        |

| 3FA1h            | T4HLT  | PSYNC  | CKPOL         | CKSYNC |         |         | MODE     |        |        | 00000000                    |

| 3FA0h            | T4CON  | ON     |               | CKPS   |         |         | OU       | TPS    |        | 00000000                    |

| 3F9Fh            | T4PR   |        | PR4           |        |         |         |          |        |        |                             |

| 3F9Eh            | T4TMR  |        |               |        | TM      | IR4     |          |        |        | 00000000                    |

| 3F9Dh            | T5CLK  |        |               |        | С       | S       |          |        |        | 00000                       |

| 3F9Ch            | T5GATE |        |               |        | G       | SS      |          |        |        | 00000                       |

| 3F9Bh            | T5GCON | GE     | GPOL          | GTM    | GSPM    | GGO     | GVAL     | _      | —      | 00000x                      |

| 3F9Ah            | T5CON  | —      | —             | CK     | PS      | —       | NOT_SYNC | RD16   | ON     | 00-000                      |

| 3F99h            | TMR5H  |        |               |        | TMF     | R5H     |          |        |        | 00000000                    |

|                  | TMR5L  | 1      | TMR5L         |        |         |         |          |        |        |                             |

#### TABLE 4-11: REGISTER FILE SUMMARY FOR PIC18(L)F24/25K42 DEVICES (CONTINUED)

$\label{eq:logend: second sec$

Note 1: Not present in LF devices.

# PIC18(L)F24/25K42

| REGISTER 5       | -7: CONFI                                                                             | <b>GURATION V</b>               | VORD 4L (3 | 0 0006h)         |                 |                |       |  |

|------------------|---------------------------------------------------------------------------------------|---------------------------------|------------|------------------|-----------------|----------------|-------|--|

| R/W-1            | U-1                                                                                   | U-1                             | R/W-1      | R/W-1            | R/W-1           | R/W-1          | R/W-1 |  |

| WRTAPP (1)       | —                                                                                     | -                               | SAFEN (2)  | BBEN (2)         |                 | BBSIZE<2:0> (3 | 3)    |  |

| bit 7            |                                                                                       |                                 |            |                  |                 |                | bit 0 |  |

|                  |                                                                                       |                                 |            |                  |                 |                |       |  |

| Legend:          |                                                                                       |                                 |            |                  |                 |                |       |  |

| R = Readable     | bit                                                                                   | W = Writable                    | bit        | U = Unimple      | mented bit, rea | ad as '1'      |       |  |

| -n = Value for I | blank device                                                                          | '1' = Bit is set                | t          | '0' = Bit is cle | eared           | x = Bit is unk | nown  |  |

|                  | 0 = Applicati                                                                         | ion Block NOT<br>on Block write | protected  | a                |                 |                |       |  |

| bit 6-5          | Unimplemen                                                                            | ted: Read as '1                 | Ĺ          |                  |                 |                |       |  |

| bit 4            | 1 = SAF dis                                                                           |                                 |            |                  |                 |                |       |  |

| bit 3            | it 3 BBEN: Boot Block Enable bit<br>1 = Boot Block disabled<br>0 = Boot Block enabled |                                 |            |                  |                 |                |       |  |

| bit 2-0          |                                                                                       |                                 |            |                  |                 |                |       |  |

#### Note 1: Once protection is enabled through ICSP or a self write, it can only be reset through a bulk erase.

- **2:** See Table 4-2 for Program Flash Memory Partition.

- **3:** BBSIZE bits can only be changed when BBEN = 1. Once BBEN = 0, BBSIZE can only be changed through a bulk erase.

| BBEN | BBSIZE<2:0> | Boot Block Size |                  | Device Size <sup>(1)</sup> |           |  |

|------|-------------|-----------------|------------------|----------------------------|-----------|--|

| DDEN | BB3IZE<2:02 | (words)         | END_ADDRESS_BOOT | 8K Words                   | 16K Words |  |

| 1    | XXX         | 0               | —                | Х                          | Х         |  |

| 0    | 111         | 512             | 00 03FFh         | Х                          | Х         |  |

| 0    | 110         | 1024            | 00 07FFh         | Х                          | Х         |  |

| 0    | 101         | 2048            | 00 0FFFh         | Х                          | Х         |  |

| 0    | 100         | 4096            | 00 1FFFh         | Х                          | Х         |  |

| 0    | 011         | 8192            | 00 3FFFh         | —                          | Х         |  |

| 0    | 010         | 16384           | 00 7FFFh         | —                          | —         |  |

| 0    | 001         | 32768           | 00 FFFFh         | No                         | te 2      |  |

| 0    | 000         | 32768           | 00 FFFFh         | —                          | _         |  |

#### TABLE 5-1:BOOT BLOCK SIZE BITS

**Note 1:** See Table 5-1 for Device Size.

2: The maximum boot block size is half the user program memory size. All selections higher than the maximum size default to maximum boot block size of half PFM. For example, all settings of BBSIZE = 000 through BBSIZE = 100, default to a boot block size of 4 kW on a 8 kW device.

| U-0              | U-0   | U-0               | U-0  | U-0                                                   | U-0              | R/W/HC-1/u    | U-0 |  |  |

|------------------|-------|-------------------|------|-------------------------------------------------------|------------------|---------------|-----|--|--|

| —                | _     | _                 | —    | —                                                     | —                | MEMV          | —   |  |  |

| bit 7 bit 0      |       |                   |      |                                                       |                  |               |     |  |  |

|                  |       |                   |      |                                                       |                  |               |     |  |  |

| Legend:          |       |                   |      |                                                       |                  |               |     |  |  |

| R = Readable b   | bit   | W = Writable I    | bit  | U = Unimpler                                          | mented bit, read | <b>as</b> '0' |     |  |  |

| u = Bit is uncha | inged | x = Bit is unkn   | own  | -m/n = Value at POR and BOR/Value at all other Resets |                  |               |     |  |  |

| '1' = Bit is set |       | '0' = Bit is clea | ared | q = Value depends on condition                        |                  |               |     |  |  |

#### REGISTER 8-3: PCON1: POWER CONTROL REGISTER 1

| bit 7-2 | <b>Unimplemented:</b> Read as '0' |

|---------|-----------------------------------|

|         |                                   |

bit 1 **MEMV:** Memory Violation Flag bit

1 = No memory violation Reset occurred or set to '1' by firmware

0 = A memory violation Reset occurred (set to '0' in hardware when a Memory Violation occurs)

bit 0 Unimplemented: Read as '0'

### TABLE 8-4: SUMMARY OF REGISTERS ASSOCIATED WITH RESETS

| Name   | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Register<br>on Page |

|--------|--------|--------|-------|-------|-------|-------|-------|--------|---------------------|

| BORCON | SBOREN |        |       |       | _     |       |       | BORRDY | 90                  |

| PCON0  | STKOVF | STKUNF | WDTWV | RWDT  | RMCLR | RI    | POR   | BOR    | 95                  |

| PCON1  | _      | _      | _     | _     | _     | _     | MEMV  | _      | 96                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Resets.

| R/W-0/0         | R/W-0/0                                                 | R/W-0/0                                             | R/W-0/0          | R/W-0/0         | R/W-0/0            | R/W-0/0         | R/W-0/0    |  |  |  |  |

|-----------------|---------------------------------------------------------|-----------------------------------------------------|------------------|-----------------|--------------------|-----------------|------------|--|--|--|--|

| I2C2TXIE        | I2C2RXIE                                                | DMA2AIE                                             | DMA2ORIE         | DMA2DCNTIE      | DMA2SCNTIE         | C2IE            | INT1IE     |  |  |  |  |

| bit 7           |                                                         |                                                     | •                |                 |                    |                 | bit (      |  |  |  |  |

|                 |                                                         |                                                     |                  |                 |                    |                 |            |  |  |  |  |

| Legend:         |                                                         |                                                     |                  |                 |                    |                 |            |  |  |  |  |

| R = Readab      |                                                         | W = Writable b                                      | it               | -               | ented bit, read as |                 |            |  |  |  |  |

| u = Bit is und  | changed                                                 | x = Bit is unkno                                    | own              | -n/n = Value at | POR and BOR/       | /alue at all ot | her Resets |  |  |  |  |

| '1' = Bit is se | et                                                      | '0' = Bit is clea                                   | red              |                 |                    |                 |            |  |  |  |  |

|                 |                                                         |                                                     |                  |                 |                    |                 |            |  |  |  |  |

| bit 7           |                                                         | <sup>2</sup> C2 Transmit Int                        | errupt Enable b  | it              |                    |                 |            |  |  |  |  |

|                 |                                                         | 1 = Enabled                                         |                  |                 |                    |                 |            |  |  |  |  |

| 1.1.0           | 0 = Disable                                             | _                                                   |                  |                 |                    |                 |            |  |  |  |  |

| bit 6           |                                                         | XIE: I <sup>2</sup> C2 Receive Interrupt Enable bit |                  |                 |                    |                 |            |  |  |  |  |

|                 | 1 = Enabled<br>0 = Disabled                             |                                                     |                  |                 |                    |                 |            |  |  |  |  |

| bit 5           |                                                         | -<br>DMA2 Abort Inte                                | rrupt Enable bit |                 |                    |                 |            |  |  |  |  |

|                 | 1 = Enabled                                             |                                                     |                  |                 |                    |                 |            |  |  |  |  |

|                 | 0 = Disabled                                            |                                                     |                  |                 |                    |                 |            |  |  |  |  |

| bit 4           | DMA2ORIE: DMA2 Overrun Interrupt Enable bit             |                                                     |                  |                 |                    |                 |            |  |  |  |  |

|                 | 1 = Enabled                                             |                                                     |                  |                 |                    |                 |            |  |  |  |  |

|                 | 0 = Disabled                                            |                                                     |                  |                 |                    |                 |            |  |  |  |  |

| bit 3           | DMA2DCNTIE: DMA2 Destination Count Interrupt Enable bit |                                                     |                  |                 |                    |                 |            |  |  |  |  |

|                 | 1 = Enabled                                             |                                                     |                  |                 |                    |                 |            |  |  |  |  |

| L:1 0           | 0 = Disable                                             |                                                     |                  | at Eachte bit   |                    |                 |            |  |  |  |  |

| bit 2           | 1 = Enabled                                             | TE: DMA2 Source                                     | e Count Interru  | pt Enable bit   |                    |                 |            |  |  |  |  |

|                 | 0 = Disable                                             |                                                     |                  |                 |                    |                 |            |  |  |  |  |

| bit 1           |                                                         | errupt Enable bi                                    | t                |                 |                    |                 |            |  |  |  |  |

|                 | 1 = Enabled                                             |                                                     |                  |                 |                    |                 |            |  |  |  |  |

|                 | 0 = Disable                                             | d                                                   |                  |                 |                    |                 |            |  |  |  |  |

| bit 0           | INT1IE: Exte                                            | ernal Interrupt 1                                   | Enable bit       |                 |                    |                 |            |  |  |  |  |

|                 | 1 = Enabled                                             |                                                     |                  |                 |                    |                 |            |  |  |  |  |

|                 | 0 = Disable                                             | -1                                                  |                  |                 |                    |                 |            |  |  |  |  |

# REGISTER 11-19: PIE5: PERIPHERAL INTERRUPT ENABLE REGISTER 5

# 14.0 8x8 HARDWARE MULTIPLIER

# 14.1 Introduction

All PIC18 devices include an 8x8 hardware multiplier as part of the ALU. The multiplier performs an unsigned operation and yields a 16-bit result that is stored in the product register pair, PRODH:PRODL. The multiplier's operation does not affect any flags in the STATUS register.

Making multiplication a hardware operation allows it to be completed in a single instruction cycle. This has the advantages of higher computational throughput and reduced code size for multiplication algorithms and allows the PIC18 devices to be used in many applications previously reserved for digital signal processors. A comparison of various hardware and software multiply operations, along with the savings in memory and execution time, is shown in Table 14-1.

### 14.2 Operation

Example 14-1 shows the instruction sequence for an 8x8 unsigned multiplication. Only one instruction is required when one of the arguments is already loaded in the WREG register.

Example 14-2 shows the sequence to do an 8x8 signed multiplication. To account for the sign bits of the arguments, each argument's Most Significant bit (MSb) is tested and the appropriate subtractions are done.

#### EXAMPLE 14-1: 8x8 UNSIGNED MULTIPLY ROUTINE

| MOVF  | ARG1, | W | ; |       |     |       |    |

|-------|-------|---|---|-------|-----|-------|----|

| MULWF | ARG2  |   | ; | ARG1  | *   | ARG2  | -> |

|       |       |   | ; | PRODE | 1:1 | PRODL |    |

|       |       |   |   |       |     |       |    |

# EXAMPLE 14-2: 8x8 SIGNED MULTIPLY

|       |          | R | JUTINE         |

|-------|----------|---|----------------|

| MOVF  | ARG1, W  |   |                |

| MULWF | ARG2     | ; | ARG1 * ARG2 -> |

|       |          | ; | PRODH: PRODL   |

| BTFSC | ARG2, SB | ; | Test Sign Bit  |

| SUBWF | PRODH, F | ; | PRODH = PRODH  |

|       |          | ; | - ARG1         |

| MOVF  | ARG2, W  |   |                |

| BTFSC | ARG1, SB | ; | Test Sign Bit  |

| SUBWF | PRODH, F | ; | PRODH = PRODH  |

|       |          | ; | - ARG2         |

|       |          |   |                |

|                |                           | Program           | Cycles | Time     |          |          |         |  |

|----------------|---------------------------|-------------------|--------|----------|----------|----------|---------|--|

| Routine        | Multiply Method           | Memory<br>(Words) | (Max)  | @ 64 MHz | @ 40 MHz | @ 10 MHz | @ 4 MHz |  |

| 9v9 uppigpod   | Without hardware multiply | 13                | 69     | 4.3 μs   | 6.9 μs   | 27.6 μs  | 69 μs   |  |

| 8x8 unsigned   | Hardware multiply         | 1                 | 1      | 62.5 ns  | 100 ns   | 400 ns   | 1 μs    |  |

| 9v9 signed     | Without hardware multiply | 33                | 91     | 5.7 μs   | 9.1 μs   | 36.4 μs  | 91 μs   |  |

| 8x8 signed     | Hardware multiply         | 6                 | 6      | 375 ns   | 600 ns   | 2.4 μs   | 6 μs    |  |

| 16v16 unsigned | Without hardware multiply | 21                | 242    | 15.1 μs  | 24.2 μs  | 96.8 μs  | 242 μs  |  |

| 16x16 unsigned | Hardware multiply         | 28                | 28     | 1.8 μs   | 2.8 μs   | 11.2 μs  | 28 μs   |  |

| 16x16 aignod   | Without hardware multiply | 52                | 254    | 15.9 μs  | 25.4 μs  | 102.6 μs | 254 μs  |  |

| 16x16 signed   | Hardware multiply         | 35                | 40     | 2.5 μs   | 4.0 μs   | 16.0 μs  | 40 μs   |  |

### TABLE 14-1: PERFORMANCE COMPARISON FOR VARIOUS MULTIPLY OPERATIONS

#### 17.9.5 OVERRUN INTERRUPT

The Overrun Interrupt flag is set if the DMA receives a trigger to start a new message before the current message is completed.

| Instruction                  | ()<br>111111 | @<br>וחחח             | <u>э</u><br>ПППП       | ()<br>()<br>()    | 9<br>1000         | 6<br>0000         | 0<br>ПППП         | ®<br>ПППП     | 9<br>ПППП | <u>ө</u><br>пппп | <u>ө</u><br>ПППП  | ש<br>וחחחר        | 9<br>1000         | ₪<br>1000         | ₽<br>1000 | 6)<br>ПППП | ₽<br>000000000000000000000000000000000000 | <u>в</u><br>ПППП | Rev. 10-000275E<br>87112016 |

|------------------------------|--------------|-----------------------|------------------------|-------------------|-------------------|-------------------|-------------------|---------------|-----------|------------------|-------------------|-------------------|-------------------|-------------------|-----------|------------|-------------------------------------------|------------------|-----------------------------|

| Clock                        |              |                       |                        |                   |                   |                   |                   |               |           | JUUUL            |                   |                   |                   |                   |           |            |                                           |                  |                             |

| EN                           | ,            |                       |                        |                   |                   |                   |                   |               |           |                  |                   |                   |                   |                   |           |            |                                           |                  |                             |

| SIRQEN                       |              |                       |                        |                   |                   |                   |                   |               |           |                  |                   |                   |                   |                   |           |            |                                           |                  |                             |

| Source Hardware<br>Trigger - |              |                       | ſ                      |                   |                   |                   |                   | 1             |           |                  |                   |                   |                   |                   |           |            |                                           |                  |                             |

| DGO-                         |              |                       |                        |                   |                   |                   |                   |               |           |                  |                   |                   |                   |                   |           |            |                                           |                  |                             |

| DMAxSPTR                     |              |                       | 0x100                  | )                 |                   | ( 0x              | 101               | χ             |           | 0x100            |                   | Х                 | 0x1               | 01                |           |            | 0x100                                     | )                |                             |

| DMAxDPTR                     |              |                       | 0x200                  | )                 |                   | 0x                | 201               | χ             |           | 0x202            |                   | X                 | 0x2               | 03                |           |            | 0x200                                     | )                |                             |

| DMAxSCNT                     |              |                       | 2                      |                   |                   | Χ                 | 1                 | χ             |           | 2                |                   | Х                 | 1                 | . )               |           |            | 2                                         |                  |                             |

| DMAxDCNT                     | $\langle $   |                       | 4                      |                   |                   | Χ                 | 3                 | χ             |           | 2                |                   | Х                 | 1                 | . )               |           |            | 4                                         |                  |                             |

| DMA STATE                    |              | IDLE                  |                        | SR <sup>(1)</sup> | DW <sup>(2)</sup> | SR <sup>(1)</sup> | DW <sup>(2)</sup> | χ             | IDLE      |                  | SR <sup>(1)</sup> | DW <sup>(2)</sup> | SR <sup>(1)</sup> | DW <sup>(2)</sup> |           |            | IDLE                                      |                  |                             |

| DMAxSCNTIF                   |              |                       |                        |                   |                   |                   | ſ                 |               | ]         |                  |                   |                   |                   | Γ                 |           |            |                                           |                  |                             |

|                              |              |                       |                        |                   |                   |                   |                   |               |           |                  |                   |                   |                   |                   |           |            |                                           |                  |                             |

| DMAxORIF                     |              |                       |                        |                   |                   |                   |                   |               |           |                  |                   |                   |                   |                   |           |            |                                           |                  |                             |

|                              | DMA          | xCON1<br>xSSA<br>xSSZ | bits.SM<br>0x10<br>0x2 | 10                |                   | DMAxD<br>DMAxD    |                   | 0x200<br>0x20 |           |                  |                   |                   |                   |                   |           |            |                                           |                  |                             |

| Note 1:                      | SR -         | Sour                  | ce Re                  | ad                |                   |                   |                   |               | -         |                  |                   |                   |                   |                   |           |            |                                           |                  |                             |

| 2:                           | DW -         | Dest                  | inatic                 | on Wr             | ite               |                   |                   |               |           |                  |                   |                   |                   |                   |           |            |                                           |                  |                             |

### FIGURE 17-9: OVERRUN INTERRUPT

#### **REGISTER 17-15: DMAxDSAH – DMAx DESTINATION START ADDRESS HIGH REGISTER**

| R/W-0/0   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |  |

|-----------|---------|---------|---------|---------|---------|---------|---------|--|--|--|

| DSA<15:8> |         |         |         |         |         |         |         |  |  |  |

| bit 7     |         |         |         |         |         |         | bit 0   |  |  |  |

|           |         |         |         |         |         |         |         |  |  |  |

| Legend:   |         |         |         |         |         |         |         |  |  |  |

| Legena.                                                     |                  |                               |                                            |

|-------------------------------------------------------------|------------------|-------------------------------|--------------------------------------------|

| R = Readable bit                                            | W = Writable bit | U = Unimplemented bit, read a | as '0'                                     |

| -n/n = Value at POR and<br>BOR/Value at all other<br>Resets | 1 = bit is set   | 0 = bit is cleared            | x = bit is unknown<br>u = bit is unchanged |

bit 7-0 DSA<15:8>: Destination Start Address bits

# **REGISTER 17-16: DMAxDPTRL – DMAx DESTINATION POINTER LOW REGISTER**

| R-0       | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0   |  |  |  |

|-----------|-----|-----|-----|-----|-----|-----|-------|--|--|--|

| DPTR<7:0> |     |     |     |     |     |     |       |  |  |  |

| bit 7     |     |     |     |     |     |     | bit 0 |  |  |  |

|           |     |     |     |     |     |     |       |  |  |  |

| l edenq.  |     |     |     |     |     |     |       |  |  |  |

| Legend:                                                     |                  |                               |                                            |

|-------------------------------------------------------------|------------------|-------------------------------|--------------------------------------------|

| R = Readable bit                                            | W = Writable bit | U = Unimplemented bit, read a | as 'O'                                     |

| -n/n = Value at POR and<br>BOR/Value at all other<br>Resets | 1 = bit is set   | 0 = bit is cleared            | x = bit is unknown<br>u = bit is unchanged |

bit 7-0 DPTR<7:0>: Current Destination Address Pointer

#### **REGISTER 17-17: DMAxDPTRH – DMAx DESTINATION POINTER HIGH REGISTER**

| R-0        | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0   |  |

|------------|-----|-----|-----|-----|-----|-----|-------|--|

| DPTR<15:8> |     |     |     |     |     |     |       |  |

| bit 7      |     |     |     |     |     |     | bit 0 |  |

| Legend:                                                     |                  |                                    |                                            |  |  |  |

|-------------------------------------------------------------|------------------|------------------------------------|--------------------------------------------|--|--|--|

| R = Readable bit                                            | W = Writable bit | U = Unimplemented bit, read as '0' |                                            |  |  |  |

| -n/n = Value at POR and<br>BOR/Value at all other<br>Resets | 1 = bit is set   | 0 = bit is cleared                 | x = bit is unknown<br>u = bit is unchanged |  |  |  |

bit 7-0 **DPTR<15:8>:** Current Destination Address Pointer

© 2016-2017 Microchip Technology Inc.

Trigger

Source

Level

Triggered

**DMAxSIRQ**

**DMAxAIRQ**

| TABLE 17-2:          | DMAxSIRQ AND DMAxAIRQ |                    |  |  |  |  |  |

|----------------------|-----------------------|--------------------|--|--|--|--|--|

| DMAxSIRQ<br>DMAxAIRQ | Trigger<br>Source     | Level<br>Triggered |  |  |  |  |  |

| 0                    | Reserved              | ·                  |  |  |  |  |  |

| 1                    | LVD                   | No                 |  |  |  |  |  |

| 2                    | OSF                   | No                 |  |  |  |  |  |

| 3                    | CSW                   | No                 |  |  |  |  |  |

| 4                    | NVM                   | No                 |  |  |  |  |  |

| 5                    | SCAN                  | No                 |  |  |  |  |  |

| 6                    | CRC                   | No                 |  |  |  |  |  |

| 7                    | IOC                   | Yes                |  |  |  |  |  |

| 8                    | INT0                  | No                 |  |  |  |  |  |

| 9                    | ZCD                   | No                 |  |  |  |  |  |

| 10                   | AD                    | No                 |  |  |  |  |  |

| 11                   | ADT                   | No                 |  |  |  |  |  |

| 12                   | CMP1                  | No                 |  |  |  |  |  |

| 13                   | SMT1                  | No                 |  |  |  |  |  |

| 14                   | SMT1PRA               | No                 |  |  |  |  |  |

| 15                   | SMT1PWA               | No                 |  |  |  |  |  |

| 16                   | DMA1SCNT              | No                 |  |  |  |  |  |

| 17                   | DMA1DCNT              | No                 |  |  |  |  |  |

| 18                   | DMA10R                | No                 |  |  |  |  |  |

| 19                   | DMA1A                 | No                 |  |  |  |  |  |

| 20                   | SPI1RX                | Yes                |  |  |  |  |  |

| 21                   | SPI1TX                | Yes                |  |  |  |  |  |

| 22                   | SPI1                  | Yes                |  |  |  |  |  |

| 23                   | I2C1RX                | Yes                |  |  |  |  |  |

| 24                   | I2C1TX                | Yes                |  |  |  |  |  |

| 25                   | I2C1                  | Yes                |  |  |  |  |  |

| 26                   | I2C1E                 | Yes                |  |  |  |  |  |

| 27                   | U1RX                  | Yes                |  |  |  |  |  |

| 28                   | U1TX                  | Yes                |  |  |  |  |  |

| 29                   | U1E                   | Yes                |  |  |  |  |  |

| 30                   | U1                    | No                 |  |  |  |  |  |

| 31                   | TMR0                  | No                 |  |  |  |  |  |

| 32                   | TMR1                  | No                 |  |  |  |  |  |

| 33                   | TMR1G                 | No                 |  |  |  |  |  |

| 34                   | TMR2                  | No                 |  |  |  |  |  |

| 35                   | CCP1                  | No                 |  |  |  |  |  |

| 36                   | Reserved              | ·                  |  |  |  |  |  |

| 37                   | NCO                   | No                 |  |  |  |  |  |

| 38                   | CWG1                  | No                 |  |  |  |  |  |

| 39                   | CLC1                  | No                 |  |  |  |  |  |

| 40                   | INT1                  | No                 |  |  |  |  |  |

| 41                   | CMP2                  | No                 |  |  |  |  |  |

|                      |                       |                    |  |  |  |  |  |

| TABLE 17-2: DI | MAXSIRQ AND DMAXAIRQ INTERRUPT SOURCES |

|----------------|----------------------------------------|

|----------------|----------------------------------------|

42 DMA2SCNT No 43 DMA2DCNT No 44 DMA2OR No 45 DMA2A No I2C2RX 46 Yes 47 I2C2TX Yes I2C2 48 Yes 49 I2C2E Yes U2RX 50 Yes 51 U2TX Yes 52 U2E Yes U2 53 No 54 TMR3 No 55 TMR3G No 56 TMR4 No CCP2 57 No 58 Reserved CWG2 59 No CLC2 60 No INT2 61 No 62 Reserved 63 Reserved 64 Reserved 65 Reserved 66 Reserved 67 Reserved 68 Reserved 69 Reserved 70 TMR5 No 71 TMR5G No 72 TMR6 No CCP3 73 No 74 CWG3 No CLC3 75 No 76 Reserved 77 Reserved 78 Reserved 79 Reserved CCP4 80 No 81 CLC4 No Reserved 82 \_ 127

Note 1: All trigger sources that are not Level-triggered are Edge-triggered.

| IADLE 17-5: | JUNINA |              | GISTERS | A33001        |        |        |        |       |                     |

|-------------|--------|--------------|---------|---------------|--------|--------|--------|-------|---------------------|

| Name        | Bit 7  | Bit 6        | Bit 5   | Bit 4         | Bit 3  | Bit 2  | Bit 1  | Bit 0 | Register<br>on Page |

| DMAxCON0    | EN     | SIRQEN       | DGO     | _             | —      | AIRQEN | _      | XIP   | 252                 |

| DMAxCON1    | DMOD   | E<1:0>       | DSTP    | SMR           | <1:0>  | SMOD   | E<1:0> | SSTP  | 253                 |

| DMAxBUF     | DBUF7  | DBUF6        | DBUF5   | DBUF4         | DBUF3  | DBUF2  | DBUF1  | DBUF0 | 254                 |

| DMAxSSAL    |        |              |         | SSA           | <7:0>  |        |        |       | 254                 |

| DMAxSSAH    |        | SSA<15:8>    |         |               |        |        |        | 254   |                     |

| DMAxSSAU    | —      | — SSA<21:16> |         |               |        |        |        |       | 255                 |

| DMAxSPTRL   |        |              |         | SPTR          | <7:0>  |        |        |       | 255                 |

| DMAxSPTRH   |        |              |         | SPTR          | <15:8> |        |        |       | 255                 |

| DMAxSPTRU   | —      | SPTR<21:16>  |         |               |        |        |        | 256   |                     |

| DMAxSSZL    |        | SSZ<7:0>     |         |               |        |        |        |       | 256                 |

| DMAxSSZH    | —      | —            | —       | — — SSZ<11:8> |        |        |        |       |                     |

| DMAxSCNTL   |        |              |         | SCNT          | <7:0>  |        |        |       | 257                 |

| DMAxSCNTH   | —      | —            |         | —             |        | SCNT   | <11:8> |       | 257                 |

| DMAxDSAL    |        |              |         | DSA           | <7:0>  |        |        |       | 257                 |

| DMAxDSAH    |        |              |         | DSA<          | :15:8> |        |        |       | 258                 |

| DMAxDPTRL   |        |              |         | DPTF          | R<7:0> |        |        |       | 258                 |

| DMAxDPTRH   |        |              |         | DPTR          | <15:8> |        |        |       | 258                 |

| DMAxDSZL    |        |              |         | DSZ           | <7:0>  |        |        |       | 259                 |

| DMAxDSZH    |        | —            | _       | —             |        | DSZ<   | :11:8> |       | 259                 |

| DMAxDCNTL   |        |              |         | DCN1          | <7:0>  |        |        |       | 259                 |

| DMAxDCNTH   |        | —            | —       | _             |        | DCNT   | <11:8> |       | 260                 |

| DMAxSIRQ    |        | SIRQ6        | SIRQ5   | SIRQ4         | SIRQ3  | SIRQ2  | SIRQ1  | SIRQ0 | 260                 |

| DMAxAIRQ    | _      | AIRQ6        | AIRQ5   | AIRQ4         | AIRQ3  | AIRQ2  | AIRQ1  | AIRQ0 | 260                 |

| TABLE 17-3: | SUMMARY OF REGISTERS ASSOCIATED WITH DMA |

|-------------|------------------------------------------|

|-------------|------------------------------------------|

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by DMA.

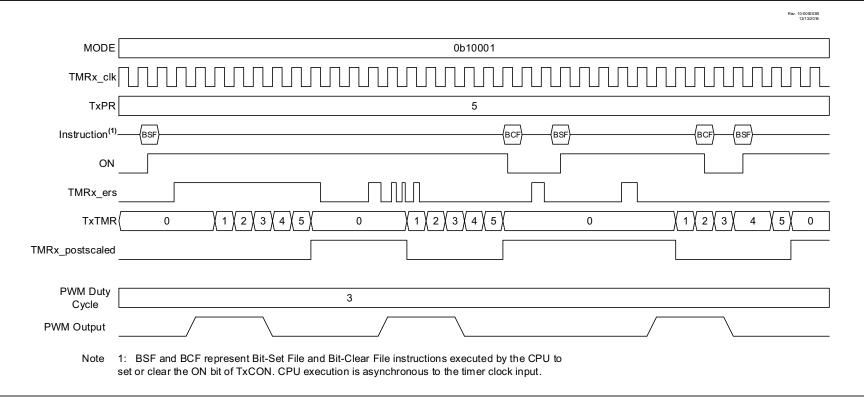

#### 24.5.9 EDGE-TRIGGERED MONOSTABLE MODES

The Edge-Triggered Monostable modes start the timer on an edge from the external Reset signal input, after the ON bit is set, and stop incrementing the timer when the timer matches the T2PR period value. The following edges will start the timer:

- Rising edge (MODE<4:0> = 10001)

- Falling edge (MODE<4:0> = 10010)

- Rising or Falling edge (MODE<4:0> = 10011)

When an Edge-Triggered Monostable mode is used in conjunction with the CCP PWM operation the PWM drive goes active with the external Reset signal edge that starts the timer, but will not go active when the timer matches the T2PR value. While the timer is incrementing, additional edges on the external Reset signal will not affect the CCP PWM.

## FIGURE 24-12: RISING EDGE-TRIGGERED MONOSTABLE MODE TIMING DIAGRAM (MODE = 10001)

#### **REGISTER 29-11: CLCDATA: CLC DATA OUTPUT**

| U-0   | U-0 | U-0 | U-0 | R-0     | R-0     | R-0     | R-0     |

|-------|-----|-----|-----|---------|---------|---------|---------|

| —     | _   | _   | —   | CLC4OUT | CLC3OUT | CLC2OUT | CLC1OUT |

| bit 7 |     |     |     |         |         |         | bit 0   |

# Legend:

| Legenu.              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-4 | Unimplemented: Read as '0'                          |

|---------|-----------------------------------------------------|

| bit 3   | CLC4OUT: Mirror copy of OUT bit of CLC4CON register |

| bit 2   | CLC3OUT: Mirror copy of OUT bit of CLC3CON register |

| bit 1   | CLC2OUT: Mirror copy of OUT bit of CLC2CON register |

| bit 0   | CLC1OUT: Mirror copy of OUT bit of CLC1CON register |

#### TABLE 29-3: SUMMARY OF REGISTERS ASSOCIATED WITH CLCx

| Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4                               | Bit 3   | Bit 2   | Bit 1     | Bit 0   | Register on<br>Page |  |

|----------|-------|-------|-------|-------------------------------------|---------|---------|-----------|---------|---------------------|--|

| CLCxCON  | EN    | _     | OUT   | INTP                                | INTN    |         | MODE<2:0> |         |                     |  |

| CLCxPOL  | POL   | _     | _     | —                                   | G4POL   | G3POL   | G2POL     | G1POL   | 460                 |  |

| CLCxSEL0 | _     | _     |       | D1S<5:0>                            |         |         |           |         |                     |  |

| CLCxSEL1 | _     | _     |       | D2S<5:0>                            |         |         |           |         |                     |  |

| CLCxSEL2 | —     | _     |       | D3S<5:0>                            |         |         |           |         |                     |  |

| CLCxSEL3 | —     | _     |       | D4S<5:0>                            |         |         |           |         |                     |  |

| CLCxGLS0 | G1D4T | G1D4N | G1D3T | G1D3N                               | G1D2T   | G1D2N   | G1D1T     | G1D1N   | 462                 |  |

| CLCxGLS1 | G2D4T | G2D4N | G2D3T | G2D3T G2D3N G2D2T G2D2N G2D1T G2D1N |         |         |           |         |                     |  |

| CLCxGLS2 | G3D4T | G3D4N | G3D3T | G3D3N                               | G3D2T   | G3D2N   | G3D1T     | G3D1N   | 464                 |  |

| CLCxGLS3 | G4D4T | G4D4N | G4D3T | G4D3N                               | G4D2T   | G4D2N   | G4D1T     | G4D1N   | 465                 |  |

| CLCDATA  | _     | _     | _     | _                                   | CLC4OUT | CLC3OUT | CLC2OUT   | CLC10UT | 465                 |  |

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the CLCx modules.

# 33.6 DALI Mode (UART1 only)

DALI is a protocol used to control lighting in large buildings such as offices and factories. It consists of two modes: 'Control Device' and 'Control Gear'. A control device is the main controller that sends out commands to the lighting fixtures. The lighting fixture itself is known as control gear. All bit transmission is done in Manchester encoding, which is done by the hardware.

Manchester encoding contains the clock and data in a single bit stream. A bit always has a transition in the middle of the bit period and may or may not have a transition at the bit period boundaries. When consecutive bits are the same value then there will be a transition at the bit boundary. When the bit value changes then there will not be a transition at the bit boundary.

When ABDEN = 0, the receiver bit rate is determined by the BRG register. Otherwise, when ABDEN = 1, the first bit synchronizes the receiver to the transmitter and sets the receiver bit rate. The Start bit low period is measured and used as the timing reference for all data bits. The ABDOVF bit will be set if the Start bit low period causes the measurement counter to overflow. All bits that follow the Start bit are data bits. The bit stream terminates when there is no transition sensed in the middle of a bit period. See Figure 33-7.

The DALI wire is half-duplex: The transmit and receive lines are electrically tied together through an interface circuit such as a diode bridge. Wait periods between frames ensure that the Forward and Back Frames do not collide.

Unlike all other protocols, DALI is transmitted MSb first. The transaction starts when the 'control device' starts a transmission. A control device transmission is called the 'Forward Frame' and consists of two bytes in DALI 1.0 or three bytes in DALI 2.0. The first byte is the control followed by one or two data bytes. Typical frame timing is shown in Figure 33-8.

When writing code for DALI 2.0 Devices, where three bytes must be transmitted, the software must write the third byte to UxTXB as soon as UxTXIF goes true and before the output shifter becomes empty. This will ensure that three bytes are transmitted back-to-back without interruption.

All control gear on the line receive the 'Forward Frame'. One of the control gear may respond to this with a single byte in reply, called the 'Back Frame'. The DALI protocol requires that the Back Frame must begin to be received between 3.5 to 11 bit periods after the Forward Frame. If a Back Frame is received, the control device is required to wait a minimum of 11 bit periods after the end of the Back Frame. After this time, the control device is free to transmit another Forward Frame. See Figure 33-9. Forward and Back Frames are terminated by two idle bit periods or Stop bits. Normally these start in the first bit period of a byte. If both Stop bits are valid, the byte reception is terminated without further action.

If either Stop bit is invalid, the frame is tagged as invalid by saving a null byte, with the framing error set, in the receive FIFO.

A framing error will also occur when a no-transition is detected in the middle of a bit period and the byte in progress is not complete. In this case, the byte will be saved with the FERIF bit set.

# 33.6.1 DALI DEVICE TRANSMITTER

DALI Control Device mode is configured with the following settings:

- MODE<3:0> = 1000

- TXEN = 1

- RXEN = 1

- UxP1 = Forward Frames are held for transmission this number of half-bit periods after the completion of a Forward or Back Frame.

- UxP2 = Forward/Back Frame threshold delimiter. Any reception that starts this number of half bit periods after the completion of a Forward or Back Frame is detected as Forward Frame and sets the PERIF flag of the corresponding received byte.

- UxBRGH:L = Value to achieve 1200 baud rate

- TXPOL = appropriate polarity for interface circuit

- STP<1:0> = 10 for two Stop bits

- RxyPPS = TX pin selection code

- TX pin TRIS control = 0

- ON = 1

A Forward Frame is initiated by writing the control byte to the UxTXB register. Each data byte after the control byte must be written to the UxTXB register as soon as UxTXIF goes true. It is important that every write is performed after UxTXIF goes true, to ensure the transmit buffer is ready to accept the byte. Each write must also occur before the TXMTIF bit goes true, to ensure the Forward Frame bit stream is generated without interruption.

When TXMTIF goes true, indicating the transmit shift register has completed sending the last byte in the frame, the TX output is held in the Idle state for the number of half-bit periods selected by the STP<1:0> bits in the UxCON2 register.

After the last Stop bit, the TX output is held in the Idle state for an additional wait time determined by the halfbit period count in the UxP1 register. An 11 bit period delay requires a value of 22 in UxP1L.

Any writes to the UxTXB register that occur after TXMTIF goes true, but before the UxP1 wait time, will be held and then transmitted immediately following the wait time. If a Back Frame is received during the wait time, any bytes that may have been written to UxTXB will not be transmitted until after the Back Frame plus the UxP1 wait time.

#### 34.5.1 FULL DUPLEX MODE

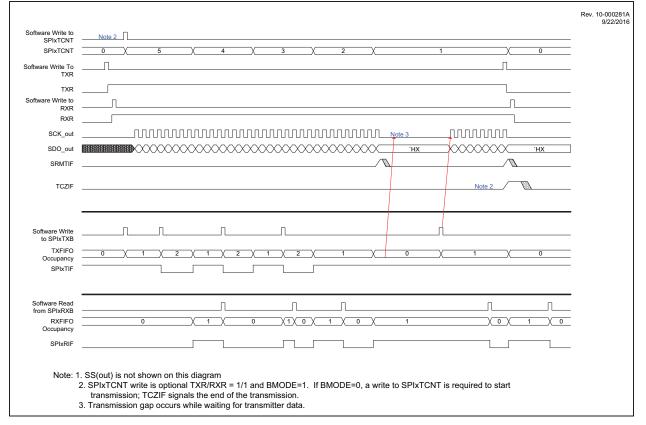

When both TXR and RXR are set, the SPI master is in Full Duplex mode. In this mode, data transfer triggering is affected by the BMODE bit of SPIxCON0.

When BMODE = 1, data transfers will occur whenever both the RXFIFO is not full and there is data present in the TXFIFO. In practice, as long as the RXFIFO is not full, data will be transmitted/received as soon as the SPIxTxB register is written to, matching functionality of SPI (MSSP) modules on older 8-bit Microchip devices. The SPIxTCNT will decrement with each transfer. However, when SPIxTCNT is zero the next transfer is not inhibited and the corresponding SPIxTCNT decrement will cause the count to roll over to the maximum value. Figure 34-3 shows an example of a communication using this mode.

When BMODE = 0, the transfer counter (SPIxTCNTH/ SPIxTCNTL) must also be written to before transfers will occur, and transfers will cease when the transfer counter reaches '0'. For example, if SPIxTXB is written twice and then SPIxTCTL is written with '3' then the transfer will start with the SPIxTCTL write. The two bytes in the TXFIFO will be sent after which the transfer will suspend until the third and last byte is written to SPIxTXB.

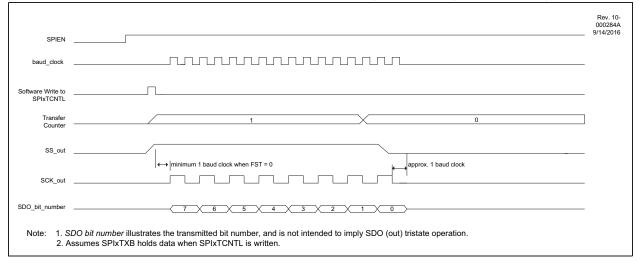

#### 34.5.5 MASTER MODE SLAVE SELECT CONTROL

#### 34.5.5.1 Hardware Slave Select Control

This SPI module allows for direct hardware control of a Slave Select output. The Slave Select output SS(out) is controlled both directly, through the SSET bit of SPIxCON2, as well indirectly by the hardware while the transfer counter is non-zero (see Section 34.4 "Transfer Counter"). SS(out) is steered by the PPS registers to pins (see Section 19.2 "PPS Outputs")

and its polarity is controlled by the SSP bit of SPIxCON1. Setting the SSET bit will also assert SS(out). Clearing the SSET bit will leave SS(out) to be controlled by the Transfer Counter. When the Transfer Counter is loaded, the SPI module will automatically assert the SS. When the Transfer Counter decrements to zero, the SPI module will deassert SS either one baud period after the final SCK pulse of the final transfer (if CKE/SMP = 0/1) or one half baud period otherwise (see Figure 34-6).

#### FIGURE 34-6: SPI MASTER SS OPERATION- CKE = 0, BMODE = 1, TCWIDTH = 0, SSP = 0

#### 34.5.5.2 Software Slave Select Control

Slave Select can also be controlled through software via a general purpose I/O pin. In this case, ensure that the pin in question is configured as a GPIO through PPS (see Section 19.2 "PPS Outputs"), and ensure that the pin is set as an output (clear the appropriate bit in the appropriate TRIS register). In this case, SSET will not affect the slave select, the Transfer Counter will not automatically control the slave select output, and all setting and clearing of the slave select output line must be directly controlled by software.

#### 35.5.10 MASTER RECEPTION IN 7-BIT ADDRESSING MODE

This section describes the sequence of events for the  $I^2C$  module configured as an  $I^2C$  master in 7-bit Addressing mode and is receiving data. Figure 35-20 is used as a visual reference for this description.

- Master software loads slave address in I2CxADB1 with R/W bit = d and number of bytes to be received in one sequence in I2CxCNT register.

- 2. Master hardware waits for BFRE bit to be set; then shifts out start and address with R/W = 1.

- 3. Master sends out the 9<sup>th</sup> SCL pulse for ACK, master hardware clocks in ACK from Slave

- 4. If ABD = 0; i.e. Address buffers are enabled

If NACK, master hardware sends Stop or sets MDR (if RSEN = 1) and waits for user software to write to S bit for restart.

If ABD = 1; i.e. Address buffers are disabled

If NACK, master hardware sends Stop or sets MDR (if RSEN = 1) and waits for user software to load the new address into I2CxTXB. Software writes to the S bit are ignored in this case.

- 5. If ACK, master hardware receives 7-bits of data into the shift register.

- 6. If the receive buffer is full (i.e. RXBF = 1), clock is stretched on 7<sup>th</sup> falling SCL edge.

- 7. Master software must read previous data out of I2CxRXB to clear RXBF.

- Master hardware receives 8th bit of data into the shift register and loads it into I2CxRXB, sets I2CxRXIF and RXBF bits. I2CxCNT is decremented.

- 9. If I2CxCNT! = 0, master hardware clocks out ACKDT as ACK value to slave. If I2CxCNT = 0, master hardware clocks out ACKCNT as ACK value to slave. It is up to the user to set the values of ACKDT and ACKCNT correctly. If the user does not set ACKCNT to '1', the master hardware will never send a NACK when I2CxCNT becomes zero. Since a NACK was not seen on the bus, the master hardware will also not assert a Stop condition.

- 10. Go to step 4.

# PIC18(L)F24/25K42

| R/W-0          | R/W-0                                                  | R/W-0                                                                                                                                               | R/W-0                                                                             | R/W-0                                                   | R/W-0                               | R/W-0                         | R/W-0                            |

|----------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------|-------------------------------------|-------------------------------|----------------------------------|

| ACNT           | GCEN                                                   | FME                                                                                                                                                 | ADB                                                                               | SDAH                                                    | T<1:0>                              | BFRE                          | T<1:0>                           |

| bit 7          | •                                                      |                                                                                                                                                     |                                                                                   | -                                                       |                                     |                               | bit C                            |

|                |                                                        |                                                                                                                                                     |                                                                                   |                                                         |                                     |                               |                                  |

| Legend:        |                                                        |                                                                                                                                                     |                                                                                   |                                                         |                                     |                               |                                  |

| R = Readab     | ole bit                                                | W = Writable b                                                                                                                                      | it                                                                                | U = Unimplen                                            | nented bit, read                    | <b>as</b> '0'                 |                                  |

| u = Bit is un  | changed                                                | x = Bit is unkno                                                                                                                                    | own                                                                               | -n/n = Value a                                          | t POR and BO                        | R/Value at all o              | ther Resets                      |

| '1' = Bit is s | et                                                     | '0' = Bit is clea                                                                                                                                   | red                                                                               | HS = Hardwa                                             | re set HC =                         | Hardware clea                 | r                                |

| bit 7          | 1 = The first<br>ister. T<br>ACKD<br>receive<br>update | -Load I <sup>2</sup> C Count<br>t received or tran<br>'he I2CCNT regis<br>T is used to dete<br>ed message. Th<br>the I2CCNT reg<br>ad of I2CCNT dis | smitted byte af<br>ster is loaded a<br>ermine the ACk<br>is prevents a<br>gister. | ter the address,<br>it the same time<br>(/NACK value fo | e as the value is<br>or the address | moved to/fron bytes and first | n the shifter.<br>data byte of a |

| bit 6          | 1 = Genera                                             | eral Call Addres<br>I call address, 0<br>I call address dis                                                                                         | (00, causes ad                                                                    |                                                         | ,                                   |                               |                                  |

| bit 5          | 1 = SCL is s                                           | Node Enable bit<br>sampled high on<br>sampled high tw                                                                                               |                                                                                   |                                                         | /. (Fscl = Fclk/<br>(Fscl = Fclk    |                               |                                  |

| bit 4          | 1 = Receive<br>Transn<br>0 = Receive                   | ess Data Buffer E<br>ed address data<br>nitted address d<br>ed address data<br>nitted address d                                                     | is loaded into b<br>ata is loaded fr<br>is loaded only i                          | om the I2CTXB<br>into the I2CADE                        | 3                                   |                               |                                  |

| bit 3-2        | 11 = Reserv<br>10 = Minimu<br>01 = Minimu              | SDA Hold Tir<br>ved<br>um of 30 ns hold<br>um of 100 ns hol<br>um of 300 ns hol                                                                     | time on SDA a<br>d time on SDA                                                    | after the falling e after the falling                   | edge of SCL                         |                               |                                  |