Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                            |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 16KB (8K x 16)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-UQFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf24k42-e-mv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 4.4.3 INSTRUCTIONS IN PROGRAM MEMORY

The program memory is addressed in bytes. Instructions are stored as either two bytes or four bytes in program memory. The Least Significant Byte of an instruction word is always stored in a program memory location with an even address (LSb = 0). To maintain alignment with instruction boundaries, the PC increments in steps of two and the LSb will always read '0' (see Section 4.2.4 "Program Counter").

Figure 4-3 shows an example of how instruction words are stored in the program memory.

The CALL and GOTO instructions have the absolute program memory address embedded into the instruction. Since instructions are always stored on word boundaries, the data contained in the instruction is a word address. The word address is written to PC<20:1>, which accesses the desired byte address in program memory. Instruction #2 in Figure 4-3 shows how the instruction GOTO 0006h is encoded in the program memory. Program branch instructions, which encode a relative address offset, operate in the same manner. The offset value stored in a branch instruction represents the number of single-word instructions that the PC will be offset by. Section 43.0 "Instruction set.

#### 4.4.4 MULTI-WORD INSTRUCTIONS

The standard PIC18 instruction set has four two-word instructions: CALL, MOVFF, GOTO and LFSR and two three-word instructions: MOVFL and MOVSFL. In all cases, the second and the third word of the instruction always has '1111' as its four Most Significant bits; the other 12 bits are literal data, usually a data memory address.

The use of '1111' in the 4 MSbs of an instruction specifies a special form of NOP. If the instruction is executed in proper sequence – immediately after the first word – the data in the second word is accessed and used by the instruction sequence. If the first word is skipped for some reason and the second word is executed by itself, a NOP is executed instead. This is necessary for cases when the two-word instruction is preceded by a conditional instruction that changes the PC. Example 4-4 shows how this works.

#### FIGURE 4-3: INSTRUCTIONS IN PROGRAM MEMORY

|                |             |                   | LSB = 1 | LSB = 0 | Word Address $\downarrow$ |

|----------------|-------------|-------------------|---------|---------|---------------------------|

|                | Program M   | emory             |         |         | 000000h                   |

|                | Byte Locati | ons $\rightarrow$ |         |         | 000002h                   |

|                |             |                   |         |         | 000004h                   |

|                |             |                   |         |         | 000006h                   |

| Instruction 1: | MOVLW       | 055h              | 0Fh     | 55h     | 000008h                   |

| Instruction 2: | GOTO        | 0006h             | EFh     | 03h     | 00000Ah                   |

|                |             |                   | F0h     | 00h     | 00000Ch                   |

| Instruction 3: | MOVFF       | 123h, 456h        | C1h     | 23h     | 00000Eh                   |

|                |             |                   | F4h     | 56h     | 000010h                   |

| Instruction 4: | MOVFFL      | 123h, 456h        | 00h     | 60h     | 000012h                   |

|                |             |                   | F4h     | 8Ch     | 000014h                   |

|                |             |                   | F4h     | 56h     | 000016h                   |

|                |             |                   |         |         | 000018h                   |

|                |             |                   |         |         | 00001Ah                   |

| Address          | Name   | Bit 7  | Bit 6               | Bit 5  | Bit 4   | Bit 3   | Bit 2    | Bit 1  | Bit 0    | <u>Value on</u><br>POR, BOR |

|------------------|--------|--------|---------------------|--------|---------|---------|----------|--------|----------|-----------------------------|

| 3FCEh            | PORTE  | _      | _                   | _      | _       | RE3     | _        | _      | —        | x                           |

| 3FCDh            | _      |        |                     |        | Unimple | emented | •        |        |          | -                           |

| 3FCCh            | PORTC  | RC7    | RC6                 | RC5    | RC4     | RC3     | RC2      | RC1    | RC0      | *****                       |

| 3FCBh            | PORTB  | RB7    | RB6                 | RB5    | RB4     | RB3     | RB2      | RB1    | RB0      | XXXXXXXX                    |

| 3FCAh            | PORTA  | RA7    | RA6                 | RA5    | RA4     | RA3     | RA2      | RA1    | RA0      | XXXXXXXX                    |

| 3FC9h -<br>3FC5h | _      |        |                     |        | Unimple | emented |          |        |          | -                           |

| 3FC4h            | TRISC  | TRISC7 | TRISC6              | TRISC5 | TRISC4  | TRISC3  | TRISC2   | TRISC1 | TRISC0   | 11111111                    |

| 3FC3h            | TRISB  | TRISB7 | TRISB6              | TRISB5 | TRISB4  | TRISB3  | TRISB2   | TRISB1 | TRISB0   | 11111111                    |

| 3FC2h            | TRISA  | TRISA7 | TRISA6              | TRISA5 | TRISA4  | TRISA3  | TRISA2   | TRISA1 | TRISA0   | 11111111                    |

| 3FC1h -<br>3FBDh | —      |        | Unimplemented       |        |         |         |          |        |          | —                           |

| 3FBCh            | LATC   | LATC7  | LATC6               | LATC5  | LATC4   | LATC3   | LATC2    | LATC1  | LATC0    | XXXXXXXX                    |

| 3FBBh            | LATB   | LATB7  | LATB6               | LATB5  | LATB4   | LATB3   | LATB2    | LATB1  | LATB0    | XXXXXXXX                    |

| 3FBAh            | LATA   | LATA7  | LATA6               | LATA5  | LATA4   | LATA3   | LATA2    | LATA1  | LATA0    | XXXXXXXX                    |

| 3FB9h            | T0CON1 |        | CS<2:0>             |        | ASYNC   |         | CKPS     | 8<3:0> |          | 00000000                    |

| 3FB8h            | T0CON0 | EN     | EN — OUT MD16 OUTPS |        |         |         |          |        | 0-000000 |                             |

| 3FB7h            | TMR0H  |        | TMR0H               |        |         |         |          |        |          | 11111111                    |

| 3FB6h            | TMR0L  |        | TMR0L               |        |         |         |          |        | 00000000 |                             |

| 3FB5h            | T1CLK  |        |                     |        | С       | S       |          |        |          | 00000                       |

| 3FB4h            | T1GATE |        |                     |        | GS      | SS      |          |        |          | 00000                       |

| 3FB3h            | T1GCON | GE     | GPOL                | GTM    | GSPM    | GGO     | GVAL     | _      | _        | 00000x                      |

| 3FB2h            | T1CON  | —      | —                   | CKPS   | <1:0>   | —       | SYNC     | RD16   | ON       | 00-000                      |

| 3FB1h            | TMR1H  |        | TMR1H               |        |         |         |          |        |          | 00000000                    |

| 3FB0h            | TMR1L  |        | TMR1L               |        |         |         |          |        |          | 00000000                    |

| 3FAFh            | T2RST  | —      | —                   | _      |         |         | RSEL     |        |          | 00000                       |

| 3FAEh            | T2CLK  | —      | —                   | —      | —       |         | C        | S      |          | 0000                        |

| 3FADh            | T2HLT  | PSYNC  | CKPOL               | CKSYNC |         |         | MODE     |        |          | 00000000                    |

| 3FACh            | T2CON  | ON     |                     | CKPS   |         |         | OU       | TPS    |          | 00000000                    |

| 3FABh            | T2PR   |        |                     |        | PF      | R2      |          |        |          | 11111111                    |

| 3FAAh            | T2TMR  |        |                     |        | TM      | IR2     |          |        |          | 00000000                    |

| 3FA9h            | T3CLK  |        |                     |        | С       | S       |          |        |          | 00000                       |

| 3FA8h            | T3GATE |        |                     |        | GS      | SS      |          |        |          | 00000                       |

| 3FA7h            | T3GCON | GE     | GPOL                | GTM    | GSPM    | GGO     | GVAL     | _      | —        | 00000x                      |

| 3FA6h            | T3CON  | —      | —                   | СК     | PS      | —       | NOT_SYNC | RD16   | ON       | 00-000                      |

| 3FA5h            | TMR3H  |        |                     |        | TMF     | R3H     |          |        |          | 00000000                    |

| 3FA4h            | TMR3L  |        |                     |        | TM      | R3L     |          |        |          | 00000000                    |

| 3FA3h            | T4RST  | —      | —                   | —      |         |         | RSEL     |        |          | 00000                       |

| 3FA2h            | T4CLK  | —      | —                   | —      |         |         | C        | S      |          | 0000                        |

| 3FA1h            | T4HLT  | PSYNC  | CKPOL               | CKSYNC |         |         | MODE     |        |          | 00000000                    |

| 3FA0h            | T4CON  | ON     |                     | CKPS   |         |         | OU       | TPS    |          | 00000000                    |

| 3F9Fh            | T4PR   |        |                     |        | PF      | R4      |          |        |          | 11111111                    |

| 3F9Eh            | T4TMR  |        |                     |        | TM      | IR4     |          |        |          | 00000000                    |

| 3F9Dh            | T5CLK  |        | CS                  |        |         |         |          |        | 00000    |                             |

| 3F9Ch            | T5GATE |        |                     |        | G       | SS      |          |        |          | 00000                       |

| 3F9Bh            | T5GCON | GE     | GPOL                | GTM    | GSPM    | GGO     | GVAL     | _      | —        | 00000x                      |

| 3F9Ah            | T5CON  | —      | —                   | CK     | PS      | —       | NOT_SYNC | RD16   | ON       | 00-000                      |

| 3F99h            | TMR5H  |        |                     |        | TMF     | R5H     |          |        |          | 00000000                    |

|                  | TMR5L  | 1      | TMR5L               |        |         |         |          |        | 00000000 |                             |

#### TABLE 4-11: REGISTER FILE SUMMARY FOR PIC18(L)F24/25K42 DEVICES (CONTINUED)

$\label{eq:logend: second sec$

Note 1: Not present in LF devices.

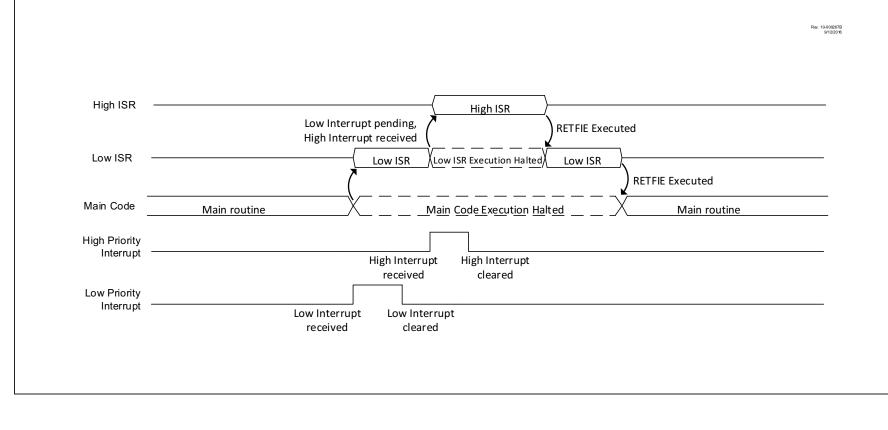

#### 11.4.3 PREEMPTING LOW PRIORITY INTERRUPTS

Low-priority interrupts can be preempted by high priority interrupts. While in the low priority ISR, if a high-priority interrupt arrives, the high priority interrupt request is generated and the low priority ISR is suspended, while the high priority ISR is executed, see Figure 11-4.

After the high priority ISR is complete and if any other high priority interrupt requests are not active, the execution returns to the preempted low priority ISR.

| Note 1: | The   | high   | priority | interrupt  | flag  | must  | be |

|---------|-------|--------|----------|------------|-------|-------|----|

|         | clear | red to | avoid re | ecursive i | nterr | upts. |    |

2: If a low-priority ISR was already serviced halfway before moving on to a high priority ISR, then the low priority ISR is completely serviced even if user code clears GIEL.

#### FIGURE 11-4: INTERRUPT EXECUTION: HIGH PRIORITY INTERRUPT PREEMPTING LOW PRIORITY INTERRUPTS

| R-0/0                | 0 R/W/HS-0/0                                                         | R/W/HS-0/0                                                                                       | R/W/HS-0/0                                                             | R/W/HS-0/0     | R/W/HS-0/0       | R/W/HS-0/0       | R/W/HS-0/0  |  |  |  |  |

|----------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|----------------|------------------|------------------|-------------|--|--|--|--|

| IOCIF                | F CRCIF                                                              | SCANIF                                                                                           | NVMIF                                                                  | CSWIF          | OSFIF            | HLVDIF           | SWIF        |  |  |  |  |

| bit 7                |                                                                      |                                                                                                  |                                                                        |                |                  |                  | bit 0       |  |  |  |  |

|                      |                                                                      |                                                                                                  |                                                                        |                |                  |                  |             |  |  |  |  |

| Legend:              |                                                                      |                                                                                                  |                                                                        |                |                  |                  |             |  |  |  |  |

| R = Read             | lable bit                                                            | W = Writable                                                                                     | bit                                                                    | U = Unimpler   | mented bit, read | as '0'           |             |  |  |  |  |

| u = Bit is unchanged |                                                                      | x = Bit is unkr                                                                                  | nown                                                                   | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |  |  |  |  |

| '1' = Bit is         | s set                                                                | '0' = Bit is cle                                                                                 | ared                                                                   | HS = Bit is se | et in hardware   |                  |             |  |  |  |  |

|                      |                                                                      |                                                                                                  |                                                                        |                |                  |                  |             |  |  |  |  |

| bit 7                |                                                                      | ipt-on-Change                                                                                    | Interrupt Flag                                                         | bit            |                  |                  |             |  |  |  |  |

|                      | 1 = Interrupt                                                        | has occurred<br>event has not                                                                    | agurrad                                                                |                |                  |                  |             |  |  |  |  |

| bit 6                | •                                                                    | Interrupt Flag                                                                                   |                                                                        |                |                  |                  |             |  |  |  |  |

|                      |                                                                      | has occurred (                                                                                   |                                                                        | ad by software | )                |                  |             |  |  |  |  |

|                      |                                                                      | event has not                                                                                    |                                                                        | Su by Soltware | )                |                  |             |  |  |  |  |

| bit 5                | SCANIF: Mer                                                          | mory Scanner I                                                                                   | nterrupt Flag b                                                        | oit            |                  |                  |             |  |  |  |  |

|                      |                                                                      | has occurred (                                                                                   |                                                                        |                | )                |                  |             |  |  |  |  |

|                      | 0 = Interrupt                                                        | event has not                                                                                    | occurred                                                               |                |                  |                  |             |  |  |  |  |

| bit 4                |                                                                      | <b>NVMIF:</b> NVM Interrupt Flag bit<br>1 = Interrupt has occurred (must be cleared by software) |                                                                        |                |                  |                  |             |  |  |  |  |

|                      |                                                                      | •                                                                                                |                                                                        | ed by software | )                |                  |             |  |  |  |  |

| h:+ 0                | •                                                                    | event has not                                                                                    |                                                                        |                |                  |                  |             |  |  |  |  |

| bit 3                |                                                                      |                                                                                                  | Switch Interrupt Flag bit<br>as occurred (must be cleared by software) |                |                  |                  |             |  |  |  |  |

|                      |                                                                      | event has not                                                                                    |                                                                        | eu by soltware | )                |                  |             |  |  |  |  |

| bit 2                | <b>OSFIF:</b> Oscill                                                 | ator Fail Interru                                                                                | upt Flag bit                                                           |                |                  |                  |             |  |  |  |  |

|                      |                                                                      | has occurred (                                                                                   |                                                                        | ed by software | )                |                  |             |  |  |  |  |

|                      | •                                                                    | event has not                                                                                    |                                                                        |                |                  |                  |             |  |  |  |  |

| bit 1                |                                                                      | D Interrupt Fla                                                                                  | •                                                                      |                |                  |                  |             |  |  |  |  |

|                      |                                                                      | has occurred (<br>event has not                                                                  |                                                                        | ed by software | )                |                  |             |  |  |  |  |

| bit 0                | •                                                                    | are Interrupt Fla                                                                                |                                                                        |                |                  |                  |             |  |  |  |  |

| DIL O                |                                                                      | Interrupt Flag                                                                                   | •                                                                      |                |                  |                  |             |  |  |  |  |

|                      |                                                                      | Interrupt Flag                                                                                   |                                                                        |                |                  |                  |             |  |  |  |  |

| Note:                | Interrupt flag bits g<br>enable bit, or the g<br>prior to enabling a | lobal enable bi                                                                                  |                                                                        |                |                  |                  |             |  |  |  |  |

|                      |                                                                      |                                                                                                  |                                                                        |                |                  |                  |             |  |  |  |  |

#### REGISTER 11-3: PIR0: PERIPHERAL INTERRUPT Request Register 0

| R/W/HS-0       | )/0 R/W/HS-0/0                                           | R-0/0                                              | R-0/0            | R-0/0           | R-0/0            | R-0/0             | R-0/0       |  |  |  |  |

|----------------|----------------------------------------------------------|----------------------------------------------------|------------------|-----------------|------------------|-------------------|-------------|--|--|--|--|

| TMR3GI         | F TMR3IF                                                 | U2IF                                               | U2EIF            | U2TXIF          | U2RXIF           | I2C2EIF           | I2C2IF      |  |  |  |  |

| bit 7          |                                                          | ·                                                  |                  |                 |                  |                   | bit (       |  |  |  |  |

|                |                                                          |                                                    |                  |                 |                  |                   |             |  |  |  |  |

| Legend:        |                                                          |                                                    |                  |                 |                  |                   |             |  |  |  |  |

| R = Reada      | ble bit                                                  | W = Writable                                       | bit              | U = Unimpler    | mented bit, read | 1 as '0'          |             |  |  |  |  |

| u = Bit is u   | nchanged                                                 | x = Bit is unkr                                    | nown             | -n/n = Value a  | at POR and BO    | R/Value at all o  | ther Resets |  |  |  |  |

| '1' = Bit is s | set                                                      | '0' = Bit is cle                                   | ared             | HS = Bit is se  | et in hardware   |                   |             |  |  |  |  |

| bit 7          | TMR3GIF: TI                                              | MR3 Gate Inter                                     | rupt Flag bit    |                 |                  |                   |             |  |  |  |  |

| bit i          | 1 = Interrupt has occurred (must be cleared by software) |                                                    |                  |                 |                  |                   |             |  |  |  |  |

|                |                                                          | event has not                                      |                  |                 | /                |                   |             |  |  |  |  |

| bit 6          | TMR3IF: TM                                               | R3 Interrupt Fla                                   | ng bit           |                 |                  |                   |             |  |  |  |  |

|                |                                                          |                                                    |                  | red by software | )                |                   |             |  |  |  |  |

|                | •                                                        | event has not                                      |                  |                 |                  |                   |             |  |  |  |  |

| bit 5          |                                                          | 2 Interrupt Flag                                   | bit              |                 |                  |                   |             |  |  |  |  |

|                |                                                          | has occurred                                       |                  |                 |                  |                   |             |  |  |  |  |

| L:1 4          |                                                          | event has not                                      |                  | a a bit         |                  |                   |             |  |  |  |  |

| bit 4          |                                                          | 2 Framing Error Interrupt Flag bit<br>has occurred |                  |                 |                  |                   |             |  |  |  |  |

|                |                                                          | event has not                                      | occurred         |                 |                  |                   |             |  |  |  |  |

| bit 3          | •                                                        | RT2 Transmit Ir                                    |                  | oit             |                  |                   |             |  |  |  |  |

| bit 0          |                                                          | has occurred                                       | iterrupt i lag i |                 |                  |                   |             |  |  |  |  |

|                |                                                          | event has not                                      | occurred         |                 |                  |                   |             |  |  |  |  |

| bit 2          | U2RXIF: UA                                               | RT2 Receive In                                     | terrupt Flag b   | bit             |                  |                   |             |  |  |  |  |

|                | 1 = Interrupt                                            | has occurred                                       |                  |                 |                  |                   |             |  |  |  |  |

|                | 0 = Interrupt                                            | event has not                                      | occurred         |                 |                  |                   |             |  |  |  |  |

| bit 1          | <b>12C2EIF:</b> 1 <sup>2</sup> C                         | 2 Error Interrup                                   | t Flag bit       |                 |                  |                   |             |  |  |  |  |

|                |                                                          | has occurred                                       |                  |                 |                  |                   |             |  |  |  |  |

| L:1 0          |                                                          | event has not                                      |                  |                 |                  |                   |             |  |  |  |  |

| bit 0          |                                                          | Interrupt Flag b                                   | pit              |                 |                  |                   |             |  |  |  |  |

|                |                                                          | has occurred<br>event has not                      | occurred         |                 |                  |                   |             |  |  |  |  |

| Note:          | Interrupt flag bits                                      |                                                    |                  | ndition occurs  | regardless of t  | he state of its ( | orrespondin |  |  |  |  |

|                | enable bit, or the g                                     |                                                    |                  |                 |                  |                   |             |  |  |  |  |

|                | prior to enabling a                                      |                                                    |                  |                 | 1.11             |                   | ,           |  |  |  |  |

#### REGISTER 11-9: PIR6: PERIPHERAL INTERRUPT REGISTER 6

|                 |                                                                 |                              |                    | ,                   |                   |                 |            |  |  |  |  |  |

|-----------------|-----------------------------------------------------------------|------------------------------|--------------------|---------------------|-------------------|-----------------|------------|--|--|--|--|--|

| R/W-1/1         | R/W-1/1                                                         | R/W-1/1                      | R/W-1/1            | R/W-1/1             | R/W-1/1           | R/W-1/1         | R/W-1/1    |  |  |  |  |  |

| I2C2TXIP        | I2C2RXIP                                                        | DMA2AIP                      | DMA2ORIP           | DMA2DCNTIP          | DMA2SCNTIP        | C2IP            | INT1IP     |  |  |  |  |  |

| bit 7           |                                                                 |                              |                    |                     |                   |                 | bit        |  |  |  |  |  |

|                 |                                                                 |                              |                    |                     |                   |                 |            |  |  |  |  |  |

| Legend:         |                                                                 |                              |                    |                     |                   |                 |            |  |  |  |  |  |

| R = Readab      | le bit                                                          | W = Writable b               | it                 | U = Unimpleme       | ented bit, read a | s '0'           |            |  |  |  |  |  |

| u = Bit is un   | changed                                                         | x = Bit is unkno             | own                | -n/n = Value at     | POR and BOR/      | Value at all ot | her Resets |  |  |  |  |  |

| '1' = Bit is se | et                                                              | '0' = Bit is clea            | red                |                     |                   |                 |            |  |  |  |  |  |

|                 |                                                                 |                              |                    |                     |                   |                 |            |  |  |  |  |  |

| bit 7           | I2C2TXIP: I                                                     | <sup>2</sup> C2 Transmit Int | errupt Priority b  | it                  |                   |                 |            |  |  |  |  |  |

|                 | 1 = High priority                                               |                              |                    |                     |                   |                 |            |  |  |  |  |  |

|                 | 0 = Low priority                                                |                              |                    |                     |                   |                 |            |  |  |  |  |  |

| bit 6           | I2C2RXIP: I <sup>2</sup> C2 Receive Interrupt Priority bit      |                              |                    |                     |                   |                 |            |  |  |  |  |  |

|                 | <ul> <li>1 = High priority</li> <li>0 = Low priority</li> </ul> |                              |                    |                     |                   |                 |            |  |  |  |  |  |

| bit 5           | DMA2AIP: DMA2 Abort Interrupt Priority bit                      |                              |                    |                     |                   |                 |            |  |  |  |  |  |

| DIL D           | 1 = High priority                                               |                              |                    |                     |                   |                 |            |  |  |  |  |  |

|                 | 0 = Low priority                                                |                              |                    |                     |                   |                 |            |  |  |  |  |  |

| bit 4           | DMA2ORIP: DMA2 Overrun Interrupt Priority bit                   |                              |                    |                     |                   |                 |            |  |  |  |  |  |

|                 | 1 = High priority                                               |                              |                    |                     |                   |                 |            |  |  |  |  |  |

|                 | 0 = Low priority                                                |                              |                    |                     |                   |                 |            |  |  |  |  |  |

| bit 3           | DMA2DCNT                                                        | IP: DMA2 Destin              | nation Count Int   | errupt Priority bit |                   |                 |            |  |  |  |  |  |

|                 | 1 = High pri                                                    |                              |                    |                     |                   |                 |            |  |  |  |  |  |

| 1.1.0           | 0 = Low price                                                   |                              |                    |                     |                   |                 |            |  |  |  |  |  |

| bit 2           |                                                                 | <b>IP:</b> DMA2 Source       | ce Count Interru   | pt Priority bit     |                   |                 |            |  |  |  |  |  |

|                 | 1 = High priority<br>0 = Low priority                           |                              |                    |                     |                   |                 |            |  |  |  |  |  |

| bit 1           |                                                                 | errupt Priority bi           | t                  |                     |                   |                 |            |  |  |  |  |  |

|                 | 1 = High pri                                                    |                              | •                  |                     |                   |                 |            |  |  |  |  |  |

|                 | 0 = Low priority                                                |                              |                    |                     |                   |                 |            |  |  |  |  |  |

| bit 0           | INT1IP: Exte                                                    | ernal Interrupt 1            | Interrupt Priority | / bit               |                   |                 |            |  |  |  |  |  |

|                 | 1 = High pri                                                    |                              |                    |                     |                   |                 |            |  |  |  |  |  |

|                 | 0 = Low price                                                   | ority                        |                    |                     |                   |                 |            |  |  |  |  |  |

#### REGISTER 11-30: IPR5: PERIPHERAL INTERRUPT Priority REGISTER 5

#### **REGISTER 17-15: DMAxDSAH – DMAx DESTINATION START ADDRESS HIGH REGISTER**

| R/W-0/0   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |  |

|-----------|---------|---------|---------|---------|---------|---------|---------|--|--|--|

| DSA<15:8> |         |         |         |         |         |         |         |  |  |  |

| bit 7     |         |         |         |         |         |         | bit 0   |  |  |  |

|           |         |         |         |         |         |         |         |  |  |  |

| Legend:   |         |         |         |         |         |         |         |  |  |  |

| Legena.                                                     |                  |                               |                                            |

|-------------------------------------------------------------|------------------|-------------------------------|--------------------------------------------|

| R = Readable bit                                            | W = Writable bit | U = Unimplemented bit, read a | as '0'                                     |

| -n/n = Value at POR and<br>BOR/Value at all other<br>Resets | 1 = bit is set   | 0 = bit is cleared            | x = bit is unknown<br>u = bit is unchanged |

bit 7-0 DSA<15:8>: Destination Start Address bits

#### **REGISTER 17-16: DMAxDPTRL – DMAx DESTINATION POINTER LOW REGISTER**

| R-0       | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0   |  |  |  |

|-----------|-----|-----|-----|-----|-----|-----|-------|--|--|--|

| DPTR<7:0> |     |     |     |     |     |     |       |  |  |  |

| bit 7     |     |     |     |     |     |     | bit 0 |  |  |  |

|           |     |     |     |     |     |     |       |  |  |  |

| l edenq.  |     |     |     |     |     |     |       |  |  |  |

| Legend:                                                     |                  |                               |                                            |

|-------------------------------------------------------------|------------------|-------------------------------|--------------------------------------------|

| R = Readable bit                                            | W = Writable bit | U = Unimplemented bit, read a | as 'O'                                     |

| -n/n = Value at POR and<br>BOR/Value at all other<br>Resets | 1 = bit is set   | 0 = bit is cleared            | x = bit is unknown<br>u = bit is unchanged |

bit 7-0 DPTR<7:0>: Current Destination Address Pointer

#### **REGISTER 17-17: DMAxDPTRH – DMAx DESTINATION POINTER HIGH REGISTER**

| R-0        | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0   |  |  |  |

|------------|-----|-----|-----|-----|-----|-----|-------|--|--|--|

| DPTR<15:8> |     |     |     |     |     |     |       |  |  |  |

| bit 7      |     |     |     |     |     |     | bit 0 |  |  |  |

| Legend:                                                     |                                                                |                    |                                            |  |  |  |

|-------------------------------------------------------------|----------------------------------------------------------------|--------------------|--------------------------------------------|--|--|--|

| R = Readable bit                                            | adable bit W = Writable bit U = Unimplemented bit, read as '0' |                    |                                            |  |  |  |

| -n/n = Value at POR and<br>BOR/Value at all other<br>Resets | 1 = bit is set                                                 | 0 = bit is cleared | x = bit is unknown<br>u = bit is unchanged |  |  |  |

bit 7-0 **DPTR<15:8>:** Current Destination Address Pointer

© 2016-2017 Microchip Technology Inc.

### REGISTER 19-2: RxyPPS: PIN Rxy OUTPUT SOURCE SELECTION REGISTER (CONTINUED)

bit 5-0

| 6'b01 0000 | PWM8    | A | <u> </u> | С |

|------------|---------|---|----------|---|

| 6'b00 1111 | PWM7    | A | _        | С |

| 6'b00 1110 | PWM6    | A | _        | С |

| 6'b00 1101 | PWM5    | А | _        | С |

| 6'b00 1100 | CCP4    | — | В        | С |

| 6'b00 1100 | CCP3    | — | В        | С |

| 6'b00 1010 | CCP2    | — | В        | С |

| 6'b00 1001 | CCP1    | — | В        | С |

| 6'b00 1000 | CWG1D   | — | В        | С |

| 6'b00 0111 | CWG1C   | — | В        | С |

| 6'b00 0110 | CWG1B   | — | В        | С |

| 6'b00 0101 | CWG1A   | — | В        | С |

| 6'b00 0100 | CLC4OUT | — | В        | С |

| 6'b00 0011 | CLC3OUT | — | В        | С |

| 6'b00 0010 | CLC2OUT | A | —        | С |

| 6'b00 0001 | CLC1OUT | A | —        | С |

| 6'b00 0000 | LATxy   | A | В        | С |

#### 23.12 Register Definitions: Timer1/3/5

Long bit name prefixes for the Timer1/3/5 are shown in Table 24-2. Refer to **Section 1.4.2.2 "Long Bit Names**" for more information.

#### TABLE 23-3:

| Peripheral | Bit Name Prefix |

|------------|-----------------|

| Timer1     | T1              |

| Timer3     | Т3              |

| Timer5     | Т5              |

#### REGISTER 23-1: TXCON: TIMERx CONTROL REGISTER

| U-0         | U-0 | R/W-0/u | R/W-0/u | U-0 | R/W-0/u | R/W-0/0 | R/W-0/u |  |

|-------------|-----|---------|---------|-----|---------|---------|---------|--|

| —           | —   | CKPS    | <1:0>   | —   | SYNC    | RD16    | ON      |  |

| bit 7 bit 0 |     |         |         |     |         |         |         |  |

| Legend:           |                  |                                    |               |  |  |

|-------------------|------------------|------------------------------------|---------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |               |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | u = unchanged |  |  |

| bit 7-6 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                          |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5-4 | <b>CKPS&lt;1:0&gt;:</b> Timerx Input Clock Prescale Select bits<br>11 = 1:8 Prescale value<br>10 = 1:4 Prescale value<br>01 = 1:2 Prescale value<br>00 = 1:1 Prescale value                                                                                                                         |

| bit 3   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                          |

| bit 2   | SYNC: Timerx External Clock Input Synchronization Control bit <u>TMRxCLK = Fosc/4 or Fosc</u> :         This bit is ignored. Timer1 uses the incoming clock as is. <u>Else</u> :         1 = Do not synchronize external clock input         0 = Synchronize external clock input with system clock |

| bit 1   | <ul> <li>RD16: 16-Bit Read/Write Mode Enable bit</li> <li>1 = Enables register read/write of Timerx in one 16-bit operation</li> <li>0 = Enables register read/write of Timerx in two 8-bit operation</li> </ul>                                                                                    |

| bit 0   | ON: Timerx On bit<br>1 = Enables Timerx<br>0 = Disables Timerx                                                                                                                                                                                                                                      |

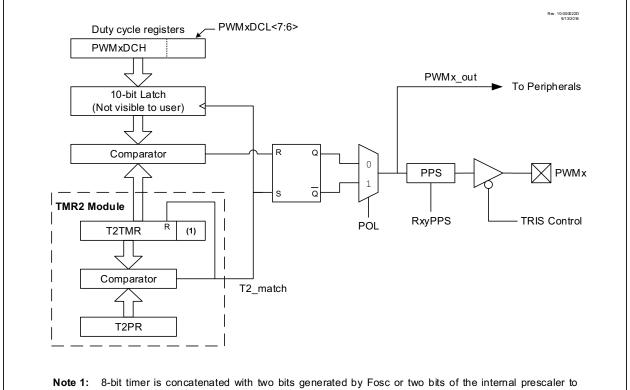

#### 26.0 PULSE-WIDTH MODULATION (PWM)

The PWM module generates a Pulse-Width Modulated signal determined by the duty cycle, period, and resolution that are configured by the following registers:

- TxPR

- TxCON

- PWMxDCH

- PWMxDCL

- PWMxCON

**Note:** The corresponding TRIS bit must be cleared to enable the PWM output on the PWMx pin.

Each PWM module can select the timer source that controls the module. Each module has an independent timer selection which can be accessed using the CCPTMRS1 register (Register 25-2). Please note that the PWM mode operation is described with respect to T2TMR in the following sections.

Figure 26-1 shows a simplified block diagram of PWM operation.

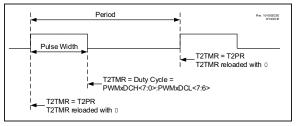

Figure 26-2 shows a typical waveform of the PWM signal.

#### FIGURE 26-1: SIMPLIFIED PWM BLOCK DIAGRAM

create 10-bit time-base.

FIGURE 26-2: PWM OUTPUT

For a step-by-step procedure on how to set up this module for PWM operation, refer to Section 26.1.9 "Setup for PWM Operation using PWMx Pins".

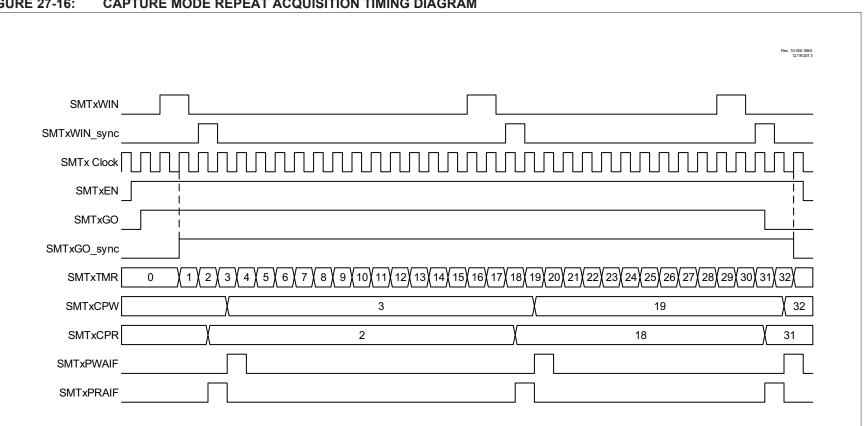

#### FIGURE 27-16: CAPTURE MODE REPEAT ACQUISITION TIMING DIAGRAM

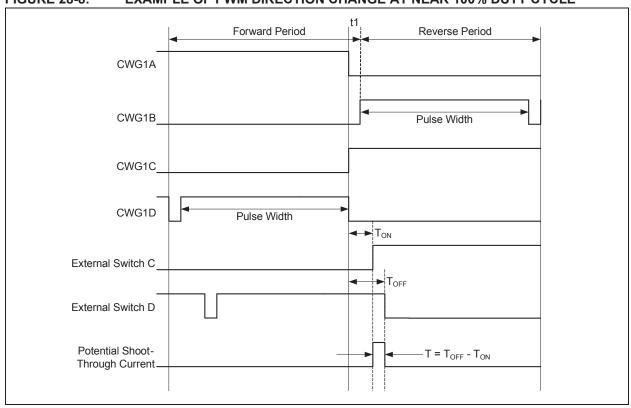

### 28.2.3.1 Direction Change in Full-Bridge Mode

In Full-Bridge mode, changing MODE<2:0> controls the forward/reverse direction. Changes to MODE<2:0> change to the new direction on the next rising edge of the modulated input.

A direction change is initiated in software by changing the MODE<2:0> bits of the CWGxCON0 register. The sequence is illustrated in Figure 28-8.

- The associated active output CWGxA and the inactive output CWGxC are switched to drive in the opposite direction.

- The previously modulated output CWGxD is switched to the inactive state, and the previously inactive output CWGxB begins to modulate.

- CWG modulation resumes after the directionswitch dead band has elapsed.

#### 28.2.3.2 Dead-Band Delay in Full-Bridge Mode

Dead-band delay is important when either of the following conditions is true:

- The direction of the CWG output changes when the duty cycle of the data input is at or near 100%, or

- 2. The turn-off time of the power switch, including the power device and driver circuit, is greater than the turn-on time.

The dead-band delay is inserted only when changing directions, and only the modulated output is affected. The statically-configured outputs (CWGxA and CWGxC) are not afforded dead band, and switch essentially simultaneously.

Figure 28-8 shows an example of the CWG outputs changing directions from forward to reverse, at near 100% duty cycle. In this example, at time t1, the output of CWGxA and CWGxD become inactive, while output CWGxC becomes active. Since the turn-off time of the power devices is longer than the turn-on time, a shoot-through current will flow through power devices QC and QD for the duration of 't'. The same phenomenon will occur to power devices QA and QB for the CWG direction change from reverse to forward.

When changing the CWG direction at high duty cycle is required for an application, two possible solutions for eliminating the shoot-through current are:

- 1. Reduce the CWG duty cycle for one period before changing directions.

- 2. Use switch drivers that can drive the switches off faster than they can drive them on.

#### FIGURE 28-8: EXAMPLE OF PWM DIRECTION CHANGE AT NEAR 100% DUTY CYCLE

© 2016-2017 Microchip Technology Inc.

| R/W/HS-0         | R/W/HS-0                                                 | U-0                                                      | R/W/HS-0         | R/W/HS-0                 | R/W/HS-0               | R/W/HS-0                    | R/W/HS-0      |

|------------------|----------------------------------------------------------|----------------------------------------------------------|------------------|--------------------------|------------------------|-----------------------------|---------------|

| CNTIF            | ACKTIF                                                   | _                                                        | WRIF             | ADRIF                    | PCIF                   | RSCIF                       | SCIF          |

| bit 7            |                                                          | •                                                        |                  | •                        |                        | ·                           | bit           |

|                  |                                                          |                                                          |                  |                          |                        |                             |               |

| Legend:          | 1.11                                                     |                                                          |                  |                          |                        |                             |               |

| R = Readable     |                                                          | W = Writable                                             |                  | U = Unimpler             | ,                      |                             |               |

| u = Bit is unch  | -                                                        | x = Bit is unkr                                          |                  |                          |                        | OR/Value at all c           |               |

| '1' = Bit is set |                                                          | '0' = Bit is clea                                        | ared             | HS = Hardwa              | ire set HC             | = Hardware clea             | r             |

| bit 7            | 1 = When I2                                              | Count Interrupt<br>CCNT = 0, set                         | by the 9th falli | ng edge of SC            | L.                     |                             |               |

|                  | 0 = 12CCNT                                               | condition has n                                          | ot occurred.     |                          |                        |                             |               |

| bit 6            | 1 = Set by th                                            | nowledge Statu<br>e 9th falling ed<br>edge condition     | ge of SCL for    |                          | •                      | = 0xx OR 11x)<br>as a Slave |               |

| bit 5            | Unimplemen                                               | ted: Read as '                                           | ) <b>'</b>       |                          |                        |                             |               |

| bit 4            | WRIF: Data V                                             | Vrite Interrupt F                                        | lag bit (MODI    | =<2:0> = 0 <sub>XX</sub> | <b>OR</b> 11x <b>)</b> |                             |               |

|                  |                                                          | th falling edge te condition not                         |                  | eceived data b           | yte.                   |                             |               |

| bit 3            | 1 = Set the 8                                            | ess Interrupt FI<br>th falling edge<br>condition not d   | of SCL for a n   |                          | ,                      | ) address byte              |               |

| bit 2            | 1 = Set on de                                            | ondition Interru<br>etection of Stop<br>condition detec  | condition        |                          |                        |                             |               |

| bit 1            | 1 = Set on de                                            | art Condition In<br>etection of Rest<br>art condition de | art condition    |                          |                        |                             |               |

| bit 0            | 1 = Set on de                                            | ondition Interru<br>etection of Star<br>condition detec  | t condition      |                          |                        |                             |               |

| <b>2</b> : AC    | abled interrupt f<br>KTIF is not set<br>atching low addr | by a matching,                                           | 10-bit, high a   |                          |                        | t clear. It is only s       | set after the |

#### REGISTER 35-10: I2CxPIR – I2CxIF INTERRUPT FLAG REGISTER

| U-0             | U-0                      | U-0                               | R/W-0/0          | R/W-0/0         | R/W-0/0            | R/W-0/0 | R/W-0/0 |

|-----------------|--------------------------|-----------------------------------|------------------|-----------------|--------------------|---------|---------|

| _               | _                        | _                                 |                  |                 | ACT<4:0>           |         |         |

| oit 7           |                          |                                   | •                |                 |                    |         | bit     |

|                 |                          |                                   |                  |                 |                    |         |         |

| Legend:         |                          |                                   |                  |                 |                    |         |         |

| R = Readable    | e hit                    | W = Writable                      | bit              | U = Unimplem    | ented bit, read as | s 'O'   |         |

|                 |                          | x = Bit is unkr                   |                  |                 | POR and BOR/       |         | Resets  |

| 0               |                          |                                   |                  |                 |                    |         | 1103013 |

| '1' = Bit is se | l                        | '0' = Bit is clea                 | areu             |                 |                    |         |         |

|                 |                          |                                   |                  |                 |                    |         |         |

| bit 7-5         |                          | nted: Read as '0'                 |                  |                 |                    |         |         |

| bit 4-0         |                          | >: Auto-Conversio                 |                  | Bits            |                    |         |         |

|                 | 11111 = Re               | served, do not us                 | 9                |                 |                    |         |         |

|                 | •                        |                                   |                  |                 |                    |         |         |

|                 | •                        |                                   |                  |                 |                    |         |         |

|                 | 11110 <b>= Re</b>        | served, do not us                 | е                |                 |                    |         |         |

|                 | 11101 <b>= So</b>        | ftware write to AD                | РСН              |                 |                    |         |         |

|                 | 11100 <b>= Re</b>        | served, do not us                 | е                |                 |                    |         |         |

|                 | 11011 <b>= So</b>        | ftware read of AD                 | RESH             |                 |                    |         |         |

|                 | 11010 <b>= So</b>        | ftware read of AD                 | ERRH             |                 |                    |         |         |

|                 | 11001 <b>= CL</b>        | C4_out                            |                  |                 |                    |         |         |

|                 | 11000 <b>= CL</b>        | C3_out                            |                  |                 |                    |         |         |

|                 | 10111 <b>= CL</b>        | C2_out                            |                  |                 |                    |         |         |

|                 | 10110 <b>= CL</b>        | C1_out                            |                  |                 |                    |         |         |

|                 | 10101 <b>= Lo</b> g      | gical OR of all Inte              | errupt-on-change | Interrupt Flags |                    |         |         |

|                 | 10100 = CN               | 1P2_out                           |                  |                 |                    |         |         |

|                 | 10011 = CN               | _                                 |                  |                 |                    |         |         |

|                 | 10010 <b>= NC</b>        |                                   |                  |                 |                    |         |         |

|                 | 10001 = PW               |                                   |                  |                 |                    |         |         |

|                 | 10000 = PW<br>01111 = PW | _                                 |                  |                 |                    |         |         |

|                 | 01110 <b>= PW</b>        |                                   |                  |                 |                    |         |         |

|                 | 01101 <b>= CC</b>        |                                   |                  |                 |                    |         |         |

|                 | 01100 = CC               |                                   |                  |                 |                    |         |         |

|                 | 01011 <b>= CC</b>        |                                   |                  |                 |                    |         |         |

|                 | 01010 = CC               |                                   |                  |                 |                    |         |         |

|                 | 01001 = SN               | IR6_postscaled                    |                  |                 |                    |         |         |

|                 |                          | IR5 overflow                      |                  |                 |                    |         |         |

|                 | 00110 <b>= TM</b>        | IR4_postscaled                    |                  |                 |                    |         |         |

|                 |                          | IR3_overflow                      |                  |                 |                    |         |         |

|                 |                          | IR2_postscaled                    |                  |                 |                    |         |         |

|                 |                          | IR1_overflow                      |                  |                 |                    |         |         |

|                 |                          | IR0_overflow<br>a selected by ADA | CTPPS            |                 |                    |         |         |

|                 | 000001 = Fri             |                                   |                  |                 |                    |         |         |

#### REGISTER 38-35: ADACT: ADC AUTO CONVERSION TRIGGER CONTROL REGISTER

| NCF                                    | Increment f                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | INC         | INCFSZ                                                                            |                                      | Increment f, skip if 0             |                                                                                                                                                                                                                   |  |  |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------------------------------------------------------------------------|--------------------------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:                                | INCF f {,d {,a}}                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Synt        | Syntax:                                                                           |                                      | INCFSZ f {,d {,a}}                 |                                                                                                                                                                                                                   |  |  |

| Operands:                              | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                  | 55 Operands: $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |                                                                                   |                                      |                                    |                                                                                                                                                                                                                   |  |  |

| Operation:                             | (f) + 1 $\rightarrow$ dest                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Ope         | ration:                                                                           | (f) + 1 $\rightarrow$ de             | est,                               |                                                                                                                                                                                                                   |  |  |

| Status Affected:                       | C, DC, N, OV, Z                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |                                                                                   | skip if result                       | <b>t =</b> 0                       |                                                                                                                                                                                                                   |  |  |

| Encoding:                              | 0010 10da                                                                                                                                                                                                                                            | ffff fff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Statu       | us Affected:                                                                      | None                                 |                                    |                                                                                                                                                                                                                   |  |  |

| Description:                           | The contents of re                                                                                                                                                                                                                                   | gister 'f' are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Enco        | oding:                                                                            | 0011                                 | 11da ffi                           | ff ffff                                                                                                                                                                                                           |  |  |

| Vords:<br>Cycles:<br>Q Cycle Activity: | placed back in reg<br>If 'a' is '0', the Acc<br>If 'a' is '1', the BSF<br>GPR bank.<br>If 'a' is '0' and the<br>set is enabled, this<br>in Indexed Literal I<br>mode whenever f<br>tion 43.2.3 "Byte-<br>Oriented Instruct<br>eral Offset Mode"<br>1 | If 'a' is '0' and the extended instructionand a NOP is executed instead,<br>it a 2-cycle instruction.iset is enabled, this instruction operatesit a 2-cycle instruction.in Indexed Literal Offset AddressingIf 'a' is '0', the Access Bank is smode whenever $f \le 95$ (5Fh). See Sec-If 'a' is '1', the BSR is used to settion 43.2.3 "Byte-Oriented and Bit-GPR bank.Oriented Instructions in Indexed Literal Offset Mode" for details.If 'a' is '0' and the extended instruction o1in Indexed Literal Offset Address1in Indexed Literal Offset Address1in Indexed Literal Offset Address |             |                                                                                   |                                      |                                    | e result is<br>(default).<br>t instruction,<br>is discarded<br>stead, making<br>hk is selected<br>d to select the<br>ed instruction<br>ction operates<br>Addressing<br>Fh). See Sec<br>ed and Bit-<br>Indexed Lit |  |  |