#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuils                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                            |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 16KB (8K x 16)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Through Hole                                                                |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                     |

| Supplier Device Package    | 28-SPDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf24k42-e-sp |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Pin Allocation Tables**

#### TABLE 1: 28-PIN ALLOCATION TABLE (PIC18(L)F2XK42)

|      |                        |               |                               |                   |                 |                  | •                 |                       | ,                  |                     |                       |                      |                     |                       |                       |     |                        |                              |                |

|------|------------------------|---------------|-------------------------------|-------------------|-----------------|------------------|-------------------|-----------------------|--------------------|---------------------|-----------------------|----------------------|---------------------|-----------------------|-----------------------|-----|------------------------|------------------------------|----------------|

| Q    | 28-Pin SPDIP/SOIC/SSOP | 28-Pin (U)QFN | ADC                           | Voltage Reference | DAC             | Comparators      | Zero Cross Detect | ۱²c                   | Sa                 | UART                | MSD                   | Timers/SMT           | CCP and PWM         | CWG                   | כרכ                   | NCO | Clock Reference (CLKR) | Interrupt-on-Change          | Basic          |

| RA0  | 2                      | 27            | ANA0                          | _                 | -               | C1IN0-<br>C2IN0- | —                 | —                     | _                  | —                   | —                     | _                    | —                   | -                     | CLCIN0 <sup>(1)</sup> | —   | _                      | IOCA0                        | -              |

| RA1  | 3                      | 28            | ANA1                          | —                 | -               | C1IN1-<br>C2IN1- | —                 | —                     | _                  | —                   | —                     | _                    | —                   | —                     | CLCIN1 <sup>(1)</sup> | —   | _                      | IOCA1                        | -              |

| RA2  | 4                      | 1             | ANA2                          | VREF-             | DAC1OUT1        | C1IN0+<br>C2IN0+ | —                 | —                     | —                  | —                   | —                     | _                    | —                   | —                     | —                     | —   | —                      | IOCA2                        | -              |

| RA3  | 5                      | 2             | ANA3                          | VREF+             | _               | C1IN1+           | —                 | _                     | _                  | _                   | MDCARL <sup>(1)</sup> | _                    | _                   | -                     | _                     | _   |                        | IOCA3                        | _              |

| RA4  | 6                      | 3             | ANA4                          | —                 | -               | _                | _                 | _                     | _                  | —                   | MDCARH <sup>(1)</sup> | T0CKI <sup>(1)</sup> | _                   | -                     | _                     | _   | _                      | IOCA4                        | _              |

| RA5  | 7                      | 4             | ANA5                          | _                 | _               | _                | _                 | _                     | SS1 <sup>(1)</sup> | —                   | MDSRC <sup>(1)</sup>  | -                    | —                   | -                     | _                     | _   |                        | IOCA5                        | _              |

| RA6  | 10                     | 7             | ANA6                          | —                 | -               | -                | —                 | -                     | -                  | -                   | —                     | —                    | —                   | —                     | —                     | _   | —                      | IOCA6                        | OSC2<br>CLKOUT |

| RA7  | 9                      | 6             | ANA7                          | —                 | -               | —                | -                 | —                     | -                  | —                   | —                     | —                    | —                   | —                     | —                     | —   | —                      | IOCA7                        | OSC1<br>CLKIN  |

| RB0  | 21                     | 18            | ANB0                          | —                 | -               | C2IN1+           | ZCD               | -                     | -                  | -                   | —                     | —                    | CCP4 <sup>(1)</sup> | CWG1IN <sup>(1)</sup> | —                     | —   | —                      | INT0 <sup>(1)</sup><br>IOCB0 | -              |

| RB1  | 22                     | 19            | ANB1                          | —                 | -               | C1IN3-<br>C2IN3- | —                 | SCL2 <sup>(3,4)</sup> | -                  | -                   | —                     | _                    | —                   | CWG2IN <sup>(1)</sup> | —                     | —   | —                      | INT1 <sup>(1)</sup><br>IOCB1 | -              |

| RB2  | 23                     | 20            | ANB2                          | —                 | -               | -                | —                 | SDA2 <sup>(3,4)</sup> | -                  | -                   | —                     | —                    | —                   | CWG3IN <sup>(1)</sup> | —                     | —   | —                      | INT2 <sup>(1)</sup><br>IOCB2 | -              |

| RB3  | 24                     | 21            | ANB3                          | _                 | -               | C1IN2-<br>C2IN2- | —                 | —                     | _                  | —                   | —                     | _                    | _                   | _                     | _                     | _   | _                      | IOCB3                        | -              |

| RB4  | 25                     | 22            | ANB4<br>ADCACT <sup>(1)</sup> | _                 | -               | —                | —                 | —                     | _                  | —                   | —                     | T5G <sup>(1)</sup>   | -                   | -                     | —                     | —   | _                      | IOCB4                        | -              |

| RB5  | 26                     | 23            | ANB5                          | _                 | _               | _                | —                 | _                     | _                  | DCD2 <sup>(1)</sup> | —                     | T1G <sup>(1)</sup>   | CCP3 <sup>(1)</sup> | _                     | _                     | —   |                        | IOCB5                        | —              |

| RB6  | 27                     | 24            | ANB6                          | —                 | _               | —                | _                 | _                     | —                  | CTS2 <sup>(1)</sup> | —                     | _                    | —                   | -                     | CLCIN2 <sup>(1)</sup> | —   | _                      | IOCB6                        | ICSPCLK        |

| RB7  | 28                     | 25            | ANB7                          | _                 | DAC1OUT2        | _                | —                 | _                     | _                  | RX2 <sup>(1)</sup>  | —                     | T6IN(1)              | —                   | -                     | CLCIN3 <sup>(1)</sup> | _   | _                      | IOCB7                        | ICSPDAT        |

| Note | 1:                     | This          | s is a PPS rem                | appable in        | put signal. The | input functio    | on may            | be moved fror         | n the default      | location show       | wn to one of seve     | eral other PORT      | c pins.             |                       |                       |     |                        |                              |                |

2: All output signals shown in this row are PPS remappable.

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

These pins are configured for I<sup>2</sup>C and SMB<sup>TM</sup> 3.0/2.0 logic levels; The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds. 4:

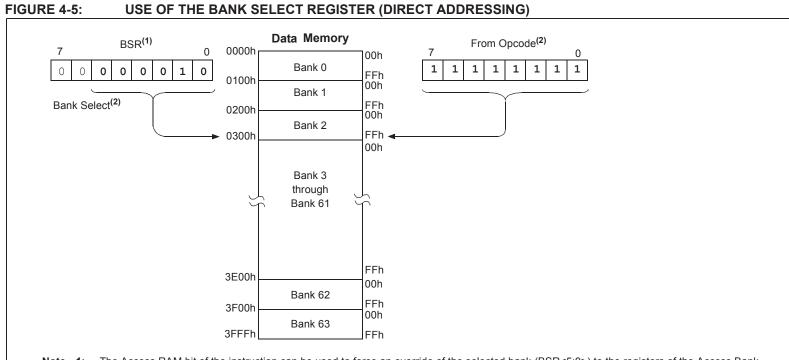

- Note 1: The Access RAM bit of the instruction can be used to force an override of the selected bank (BSR<5:0>) to the registers of the Access Bank.

- $\ensuremath{\text{2:}} \quad \text{The MOVFFL instruction embeds the entire 14-bit address in the instruction.}$

#### TABLE 4-4:SPECIAL FUNCTION REGISTER MAP FOR PIC18(L)F24/25K42 DEVICES BANK 62

|       |         |       |          |       |         | . –   |          |       |   |       |   |       |   | . –   |   |

|-------|---------|-------|----------|-------|---------|-------|----------|-------|---|-------|---|-------|---|-------|---|

| 3EFFh | ADCLK   | 3EDFh | ADLTHH   | 3EBFh | CM1PCH  | 3E9Fh | —        | 3E7Fh | — | 3E5Fh | — | 3E3Fh |   | 3E1Fh | — |

| 3EFEh | ADACT   | 3EDEh | ADLTHL   | 3EBEh | CM1NCH  | 3E9Eh | DAC1CON0 | 3E7Eh | — | 3E5Eh | — | 3E3Eh | — | 3E1Eh | — |

| 3EFDh | ADREF   | 3EDDh | _        | 3EBDh | CM1CON1 | 3E9Dh | —        | 3E7Dh | — | 3E5Dh | _ | 3E3Dh |   | 3E1Dh | — |

| 3EFCh | ADSTAT  | 3EDCh | —        | 3EBCh | CM1CON0 | 3E9Ch | DAC1CON1 | 3E7Ch | — | 3E5Ch | — | 3E3Ch | — | 3E1Ch | — |

| 3EFBh | ADCON3  | 3EDBh | —        | 3EBBh | CM2PCH  | 3E9Bh | —        | 3E7Bh | — | 3E5Bh | — | 3E3Bh | — | 3E1Bh | — |

| 3EFAh | ADCON2  | 3EDAh | —        | 3EBAh | CM2NCH  | 3E9Ah | —        | 3E7Ah | — | 3E5Ah | — | 3E3Ah | — | 3E1Ah | — |

| 3EF9h | ADCON1  | 3ED9h | _        | 3EB9h | CM2CON1 | 3E99h | —        | 3E79h | — | 3E59h | — | 3E39h | — | 3E19h | — |

| 3EF8h | ADCON0  | 3ED8h |          | 3EB8h | CM2CON0 | 3E98h | —        | 3E78h | — | 3E58h | — | 3E38h | — | 3E18h | — |

| 3EF7h | ADPREH  | 3ED7h | ADCP     | 3EB7h | —       | 3E97h | —        | 3E77h | — | 3E57h | — | 3E37h | — | 3E17h | — |

| 3EF6h | ADPREL  | 3ED6h |          | 3EB6h | —       | 3E96h | _        | 3E76h | — | 3E56h | — | 3E36h |   | 3E16h | — |

| 3EF5h | ADCAP   | 3ED5h | —        | 3EB5h | —       | 3E95h | —        | 3E75h | — | 3E55h | — | 3E35h | — | 3E15h | — |

| 3EF4h | ADACQH  | 3ED4h | —        | 3EB4h | —       | 3E94h | —        | 3E74h | — | 3E54h | — | 3E34h | — | 3E14h | — |

| 3EF3h | ADACQL  | 3ED3h | _        | 3EB3h | —       | 3E93h | —        | 3E73h | — | 3E53h | — | 3E33h | — | 3E13h | — |

| 2EF2h | —       | 3ED2h | _        | 3EB2h | —       | 3E92h | —        | 3E72h | — | 3E52h | — | 3E32h | — | 3E12h | — |

| 3EF1h | ADPCH   | 3ED1h | _        | 3EB1h | —       | 3E91h | —        | 3E71h | — | 3E51h | — | 3E31h | — | 3E11h | — |

| 3EF0h | ADRESH  | 3ED0h | _        | 3EB0h | —       | 3E90h | —        | 3E70h | — | 3E50h | — | 3E30h | — | 3E10h | — |

| 3EEFh | ADRESL  | 3ECFh | _        | 3EAFh | _       | 3E8Fh | _        | 3E6Fh | — | 3E4Fh | _ | 3E2Fh |   | 3E0Fh | — |

| 3EEEh | ADPREVH | 3ECEh | —        | 3EAEh | —       | 3E8Eh | —        | 3E6Eh | — | 3E4Eh | — | 3E2Eh | — | 3E0Eh | — |

| 3EEDh | ADPREVL | 3ECDh | —        | 3EADh | —       | 3E8Dh | —        | 3E6Dh | — | 3E4Dh | — | 3E2Dh | — | 3E0Dh | — |

| 3EECh | ADRPT   | 3ECCh | _        | 3EACh | —       | 3E8Ch | —        | 3E6Ch | — | 3E4Ch | — | 3E2Ch | — | 3E0Ch | — |

| 3EEBh | ADCNT   | 3ECBh |          | 3EABh | —       | 3E8Bh | —        | 3E6Bh | — | 3E4Bh | — | 3E2Bh | — | 3E0Bh | — |

| 3EEAh | ADACCU  | 3ECAh | HLVDCON1 | 3EAAh | —       | 3E8Ah | _        | 3E6Ah | — | 3E4Ah | — | 3E2Ah |   | 3E0Ah | — |

| 3EE9h | ADACCH  | 3EC9h | HLVDCON0 | 3EA9h | —       | 3E89h | —        | 3E69h | — | 3E49h | — | 3E29h | — | 3E09h | — |

| 3EE8h | ADACCL  | 3EC8h | —        | 3EA8h | —       | 3E88h | —        | 3E68h | — | 3E48h | — | 3E28h | — | 3E08h | — |

| 3EE7h | ADFLTRH | 3EC7h | —        | 3EA7h | —       | 3E87h | —        | 3E67h | — | 3E47h | — | 3E27h | — | 3E07h | — |

| 3EE6h | ADFLTRL | 3EC6h | _        | 3EA6h | —       | 3E86h | —        | 3E66h | — | 3E46h | — | 3E26h | — | 3E06h | — |

| 3EE5h | ADSTPTH | 3EC5h | _        | 3EA5h | —       | 3E85h | —        | 3E65h | — | 3E45h | — | 3E25h | — | 3E05h | — |

| 3EE4h | ADSTPTL | 3EC4h |          | 3EA4h | —       | 3E84h | —        | 3E64h | — | 3E44h | — | 3E24h | — | 3E04h | — |

| 3EE3h | ADERRH  | 3EC3h | ZCDCON   | 3EA3h | —       | 3E83h | —        | 3E63h | — | 3E43h | — | 3E23h | — | 3E03h | — |

| 3EE2h | ADERRL  | 3EC2h | _        | 3EA2h | —       | 3E82h | —        | 3E62h | — | 3E42h | — | 3E22h | — | 3E02h | — |

| 3EE1h | ADUTHH  | 3EC1h | FVRCON   | 3EA1h | —       | 3E81h | —        | 3E61h | — | 3E41h | — | 3E21h | _ | 3E01h | — |

| 3EE0h | ADUTHL  | 3EC0h | CMOUT    | 3EA0h | —       | 3E80h | —        | 3E60h | — | 3E40h | — | 3E20h | _ | 3E00h | — |

Legend: Unimplemented data memory locations and registers, read as '0'.

#### TABLE 4-6: SPECIAL FUNCTION REGISTER MAP FOR PIC18(L)F24/25K42 DEVICES BANK 60

| _      |             |           |                 |            |                   |       |   |       |          | _     |          |       |   |       |   |

|--------|-------------|-----------|-----------------|------------|-------------------|-------|---|-------|----------|-------|----------|-------|---|-------|---|

| 3CFFh  | —           | 3CDFh     | —               | 3CBFh      | —                 | 3C9Fh | — | 3C7Fh | —        | 3C5Fh | CLC4GLS3 | 3C3Fh | — | 3C1Fh | _ |

| 3CFEh  | MD1CARH     | 3CDEh     | —               | 3CBEh      | —                 | 3C9Eh | — | 3C7Eh | CLCDATA0 | 3C5Eh | CLC4GLS2 | 3C3Eh | — | 3C1Eh | _ |

| 3CFDh  | MD1CARL     | 3CDDh     | —               | 3CBDh      | —                 | 3C9Dh | — | 3C7Dh | CLC1GLS3 | 3C5Dh | CLC4GLS1 | 3C3Dh | — | 3C1Dh | _ |

| 3CFCh  | MD1SRC      | 3CDCh     | —               | 3CBCh      | —                 | 3C9Ch | — | 3C7Ch | CLC1GLS2 | 3C5Ch | CLC4GLS0 | 3C3Ch | — | 3C1Ch | _ |

| 3CFBh  | MD1CON1     | 3CDBh     | —               | 3CBBh      | —                 | 3C9Bh | — | 3C7Bh | CLC1GLS1 | 3C5Bh | CLC4SEL3 | 3C3Bh | — | 3C1Bh | _ |

| 3CFAh  | MD1CON0     | 3CDAh     | —               | 3CBAh      | —                 | 3C9Ah | — | 3C7Ah | CLC1GLS0 | 3C5Ah | CLC4SEL2 | 3C3Ah | — | 3C1Ah | _ |

| 3CF9h  | —           | 3CD9h     | —               | 3CB9h      | —                 | 3C99h | — | 3C79h | CLC1SEL3 | 3C59h | CLC4SEL1 | 3C39h | — | 3C19h | _ |

| 3CF8h  | —           | 3CD8h     | —               | 3CB8h      | —                 | 3C98h | — | 3C78h | CLC1SEL2 | 3C58h | CLC4SEL0 | 3C38h | — | 3C18h | _ |

| 3CF7h  | _           | 3CD7h     | —               | 3CB7h      | —                 | 3C97h | — | 3C77h | CLC1SEL1 | 3C57h | CLC4POL  | 3C37h | — | 3C17h | _ |

| 3CF6h  | —           | 3CD6h     | —               | 3CB6h      | —                 | 3C96h | — | 3C76h | CLC1SEL0 | 3C56h | CLC4CON  | 3C36h | — | 3C16h | _ |

| 3CF5h  | _           | 3CD5h     | —               | 3CB5h      | —                 | 3C95h | — | 3C75h | CLC1POL  | 3C55h | —        | 3C35h | — | 3C15h | _ |

| 3CF4h  | _           | 3CD4h     | —               | 3CB4h      | —                 | 3C94h | — | 3C74h | CLC1CON  | 3C54h | —        | 3C34h | — | 3C14h | _ |

| 3CF3h  | _           | 3CD3h     | —               | 3CB3h      | —                 | 3C93h | — | 3C73h | CLC2GLS3 | 3C53h | —        | 3C33h | — | 3C13h | _ |

| 3CF2h  | _           | 3CD2h     | —               | 3CB2h      | —                 | 3C92h | — | 3C72h | CLC2GLS2 | 3C52h | —        | 3C32h | — | 3C12h | _ |

| 3CF1h  | _           | 3CD1h     | —               | 3CB1h      | —                 | 3C91h | — | 3C71h | CLC2GLS1 | 3C51h | —        | 3C31h | — | 3C11h | _ |

| 3CF0h  | _           | 3CD0h     | —               | 3CB0h      | —                 | 3C90h | — | 3C70h | CLC2GLS0 | 3C50h | —        | 3C30h | — | 3C10h | _ |

| 3CEFh  | _           | 3CCFh     | —               | 3CAFh      | —                 | 3C8Fh | — | 3C6Fh | CLC2SEL3 | 3C4Fh | —        | 3C2Fh | — | 3C0Fh | _ |

| 3CEEh  | _           | 3CCEh     | —               | 3CAEh      | —                 | 3C8Eh | — | 3C6Eh | CLC2SEL2 | 3C4Eh | —        | 3C2Eh | — | 3C0Eh | _ |

| 3CEDh  | _           | 3CCDh     | —               | 3CADh      | —                 | 3C8Dh | — | 3C6Dh | CLC2SEL1 | 3C4Dh | —        | 3C2Dh | — | 3C0Dh | _ |

| 3CECh  | _           | 3CCCh     | —               | 3CACh      | —                 | 3C8Ch | — | 3C6Ch | CLC2SEL0 | 3C4Ch | —        | 3C2Ch | — | 3C0Ch | _ |

| 3CEBh  | _           | 3CCBh     | —               | 3CABh      | —                 | 3C8Bh | — | 3C6Bh | CLC2POL  | 3C4Bh | —        | 3C2Bh | — | 3C0Bh | _ |

| 3CEAh  | _           | 3CCAh     | —               | 3CAAh      | —                 | 3C8Ah | — | 3C6Ah | CLC2CON  | 3C4Ah | —        | 3C2Ah | — | 3C0Ah | _ |

| 3CE9h  | _           | 3CC9h     | —               | 3CA9h      | —                 | 3C89h | — | 3C69h | CLC3GLS3 | 3C49h | —        | 3C29h | — | 3C09h | _ |

| 3CE8h  | _           | 3CC8h     | —               | 3CA8h      | —                 | 3C88h | — | 3C68h | CLC3GLS2 | 3C48h | —        | 3C28h | — | 3C08h | _ |

| 3CE7h  | _           | 3CC7h     | —               | 3CA7h      | —                 | 3C87h | — | 3C67h | CLC3GLS1 | 3C47h | —        | 3C27h | — | 3C07h | _ |

| 3CE6h  | CLKRCLK     | 3CC6h     | —               | 3CA6h      | —                 | 3C86h | — | 3C66h | CLC3GLS0 | 3C46h | —        | 3C26h | — | 3C06h | _ |

| 3CE5h  | CLKRCON     | 3CC5h     | —               | 3CA5h      | —                 | 3C85h | — | 3C65h | CLC3SEL3 | 3C45h | —        | 3C25h | — | 3C05h | _ |

| 3CE4h  | —           | 3CC4h     | —               | 3CA4h      | _                 | 3C84h | _ | 3C64h | CLC3SEL2 | 3C44h | —        | 3C24h | _ | 3C04h | _ |

| 3CE3h  | _           | 3CC3h     | —               | 3CA3h      | _                 | 3C83h | _ | 3C63h | CLC3SEL1 | 3C43h | —        | 3C23h | _ | 3C03h | _ |

| 3CE2h  | _           | 3CC2h     | —               | 3CA2h      | _                 | 3C82h | _ | 3C62h | CLC3SEL0 | 3C42h | —        | 3C22h | _ | 3C02h | _ |

| 3CE1h  | _           | 3CC1h     | —               | 3CA1h      | _                 | 3C81h | _ | 3C61h | CLC3POL  | 3C41h | —        | 3C21h | _ | 3C01h | _ |

| 3CE0h  | _           | 3CC0h     | _               | 3CA0h      | _                 | 3C80h | _ | 3C60h | CLC3CON  | 3C40h | _        | 3C20h | _ | 3C00h | _ |

| Logond | . Unimplomo | ntad data | momony location | a and real | store read as 'o' |       |   |       |          |       |          |       |   |       |   |

Legend: Unimplemented data memory locations and registers, read as '0'.

# PIC18(L)F24/25K42

| REGISTER 5       | -7: CONFI                                          | <b>GURATION V</b>                             | VORD 4L (3      | 0 0006h)         |                 |                |       |

|------------------|----------------------------------------------------|-----------------------------------------------|-----------------|------------------|-----------------|----------------|-------|

| R/W-1            | U-1                                                | U-1                                           | R/W-1           | R/W-1            | R/W-1           | R/W-1          | R/W-1 |

| WRTAPP (1)       | —                                                  | -                                             | SAFEN (2)       | BBEN (2)         |                 | BBSIZE<2:0> (3 | 3)    |

| bit 7            |                                                    |                                               |                 |                  |                 |                | bit 0 |

|                  |                                                    |                                               |                 |                  |                 |                |       |

| Legend:          |                                                    |                                               |                 |                  |                 |                |       |

| R = Readable     | bit                                                | W = Writable                                  | bit             | U = Unimple      | mented bit, rea | ad as '1'      |       |

| -n = Value for I | blank device                                       | '1' = Bit is set                              | t               | '0' = Bit is cle | eared           | x = Bit is unk | nown  |

|                  | 0 = Applicati                                      | ion Block NOT<br>on Block write               | protected       | a                |                 |                |       |

| bit 6-5          | Unimplemen                                         | ted: Read as '1                               | Ĺ               |                  |                 |                |       |

| bit 4            | <b>SAFEN:</b> Stora<br>1 = SAF disa<br>0 = SAF ena |                                               | Enable bit      |                  |                 |                |       |

| bit 3            | 1 = Boot Blo                                       | Block Enable bi<br>ock disabled<br>ck enabled | t               |                  |                 |                |       |

| bit 2-0          | BBSIZE<2:0><br>Refer to Table                      | •: Boot Block S<br>e 5-1.                     | ize Selection b | pits             |                 |                |       |

#### Note 1: Once protection is enabled through ICSP or a self write, it can only be reset through a bulk erase.

- **2:** See Table 4-2 for Program Flash Memory Partition.

- **3:** BBSIZE bits can only be changed when BBEN = 1. Once BBEN = 0, BBSIZE can only be changed through a bulk erase.

| BBEN | BBSIZE<2:0> | Boot Block Size |                  | Device Size <sup>(1)</sup> |           |  |

|------|-------------|-----------------|------------------|----------------------------|-----------|--|

| DDEN | BB3IZE<2:02 | (words)         | END_ADDRESS_BOOT | 8K Words                   | 16K Words |  |

| 1    | XXX         | 0               | —                | Х                          | Х         |  |

| 0    | 111         | 512             | 00 03FFh         | Х                          | Х         |  |

| 0    | 110         | 1024            | 00 07FFh         | Х                          | Х         |  |

| 0    | 101         | 2048            | 00 0FFFh         | Х                          | Х         |  |

| 0    | 100         | 4096            | 00 1FFFh         | Х                          | Х         |  |

| 0    | 011         | 8192            | 00 3FFFh         | —                          | Х         |  |

| 0    | 010         | 16384           | 00 7FFFh         | —                          | —         |  |

| 0    | 001         | 32768           | 00 FFFFh         | Note 2                     |           |  |

| 0    | 000         | 32768           | 00 FFFFh         | —                          | _         |  |

#### TABLE 5-1:BOOT BLOCK SIZE BITS

**Note 1:** See Table 5-1 for Device Size.

2: The maximum boot block size is half the user program memory size. All selections higher than the maximum size default to maximum boot block size of half PFM. For example, all settings of BBSIZE = 000 through BBSIZE = 100, default to a boot block size of 4 kW on a 8 kW device.

| U-0                                                                  | U-0                                                                   | U-0               | U-0        | U-0                         | U-0           | R/W/HS-0/0       | R/W/HS-0/0  |  |  |  |  |

|----------------------------------------------------------------------|-----------------------------------------------------------------------|-------------------|------------|-----------------------------|---------------|------------------|-------------|--|--|--|--|

| —                                                                    | -                                                                     | —                 | —          | —                           | —             | CLC4IF           | CCP4IF      |  |  |  |  |

| bit 7                                                                | ·                                                                     |                   |            |                             |               |                  | bit 0       |  |  |  |  |

|                                                                      |                                                                       |                   |            |                             |               |                  |             |  |  |  |  |

| Legend:                                                              |                                                                       |                   |            |                             |               |                  |             |  |  |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                                                       |                   |            |                             |               |                  |             |  |  |  |  |

| u = Bit is u                                                         | nchanged                                                              | x = Bit is unkr   | iown       | -n/n = Value a              | at POR and BO | R/Value at all o | ther Resets |  |  |  |  |

| '1' = Bit is s                                                       | set                                                                   | '0' = Bit is clea | ared       | HS = Bit is set in hardware |               |                  |             |  |  |  |  |

|                                                                      |                                                                       |                   |            |                             |               |                  |             |  |  |  |  |

| bit 7-2                                                              | Unimplement                                                           | ted: Read as '    | ) <b>'</b> |                             |               |                  |             |  |  |  |  |

| bit 1                                                                | CLC4IF: CLC                                                           | 4 Interrupt Flag  | g bit      |                             |               |                  |             |  |  |  |  |

|                                                                      |                                                                       | has occurred (    |            | ed by software              | )             |                  |             |  |  |  |  |

|                                                                      | 0 = Interrupt                                                         | event has not o   | occurred   |                             |               |                  |             |  |  |  |  |

| bit 0                                                                | CCP4IF: CCF                                                           | 4 Interrupt Fla   | g bit      |                             |               |                  |             |  |  |  |  |

|                                                                      |                                                                       | has occurred (    |            | ed by software              | )             |                  |             |  |  |  |  |

|                                                                      | 0 = Interrupt                                                         | event has not o   | occurred   |                             |               |                  |             |  |  |  |  |

| Note:                                                                | Interrupt flag bits g<br>enable bit, or the g<br>prior to enabling ar | obal enable bi    |            |                             | -             |                  |             |  |  |  |  |

#### REGISTER 11-13: PIR10: PERIPHERAL INTERRUPT REGISTER 10

| R/W-0/0          | R/W-0/0      | U-0               | U-0           | U-0                                                   | U-0              | U-0    | U-0   |  |  |  |

|------------------|--------------|-------------------|---------------|-------------------------------------------------------|------------------|--------|-------|--|--|--|

| TMR5GIE          | TMR5IE       | _                 | —             | -                                                     | —                | —      | —     |  |  |  |

| bit 7            |              |                   |               |                                                       |                  |        | bit 0 |  |  |  |

|                  |              |                   |               |                                                       |                  |        |       |  |  |  |

| Legend:          |              |                   |               |                                                       |                  |        |       |  |  |  |

| R = Readable     | bit          | W = Writable      | bit           | U = Unimpler                                          | mented bit, read | as '0' |       |  |  |  |

| u = Bit is unch  | anged        | x = Bit is unkn   | iown          | -n/n = Value at POR and BOR/Value at all other Resets |                  |        |       |  |  |  |

| '1' = Bit is set |              | '0' = Bit is clea | ared          |                                                       |                  |        |       |  |  |  |

|                  |              |                   |               |                                                       |                  |        |       |  |  |  |

| bit 7            | TMR5GIE: TN  | MR5 Gate Inter    | rupt Enable b | it                                                    |                  |        |       |  |  |  |

|                  | 1 = Enabled  |                   |               |                                                       |                  |        |       |  |  |  |

|                  | 0 = Disabled |                   |               |                                                       |                  |        |       |  |  |  |

| bit 6            | TMR5IE: TMF  | R5 Interrupt En   | able bit      |                                                       |                  |        |       |  |  |  |

|                  | 1 = Enabled  |                   |               |                                                       |                  |        |       |  |  |  |

|                  | 0 = Disabled |                   |               |                                                       |                  |        |       |  |  |  |

| bit 5-0          | Unimplemen   | ted: Read as '    | )'            |                                                       |                  |        |       |  |  |  |

#### REGISTER 11-22: PIE8: PERIPHERAL INTERRUPT ENABLE REGISTER 8

#### REGISTER 11-23: PIE9: PERIPHERAL INTERRUPT ENABLE REGISTER 9

| U-0   | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|---------|---------|---------|---------|

| —     | —   | —   | —   | CLC3IE  | CWG3IE  | CCP3IE  | TMR6IE  |

| bit 7 |     |     |     |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-4 | Unimplemented: Read as '0'        |

|---------|-----------------------------------|

| bit 3   | CLC3IE: CLC3 Interrupt Enable bit |

|         | 1 = Enabled<br>0 = Disabled       |

| bit 2   | CWG3IE: CWG3 Interrupt Enable bit |

|         | 1 = Enabled<br>0 = Disabled       |

| bit 1   | CCP3IE: CCP3 Interrupt Enable bit |

|         | 1 = Enabled                       |

|         | 0 = Disabled                      |

| bit 0   | TMR6IE: TMR6 Interrupt Enable bit |

|         | 1 = Enabled                       |

|         | 0 = Disabled                      |

# PIC18(L)F24/25K42

| R/W-0/u          | R/W/HC/HS-0/0                                                                                                                                                                                         | R/W-0/0            | R/W-0/0        | U-0                    | R/W-0/0         | R/W-0/0         | R/W-0/0         |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------|------------------------|-----------------|-----------------|-----------------|--|

| IDLEN            | DOZEN                                                                                                                                                                                                 | ROI                | DOE            |                        |                 | DOZE<2:0>       |                 |  |

| bit 7            |                                                                                                                                                                                                       |                    | 1              |                        |                 |                 | bit C           |  |

| Legend:          |                                                                                                                                                                                                       |                    |                |                        |                 |                 |                 |  |

| R = Readable     | bit                                                                                                                                                                                                   | W = Writable I     | bit            | U = Unimple            | emented bit, re | ead as '0'      |                 |  |

| u = Bit is unch  | anged                                                                                                                                                                                                 | x = Bit is unkn    | own            | -n/n = Value<br>Resets | e at POR and I  | BOR/Value at a  | III other       |  |

| '1' = Bit is set |                                                                                                                                                                                                       | '0' = Bit is clea  | ared           | HC = Bit is o          | cleared by har  | dware           |                 |  |

| bit 7            | IDLEN: Idle Ena<br>1 = A SLEEP ins<br>0 = A SLEEP ins                                                                                                                                                 | struction inhibits |                | •                      |                 | ock(s)          |                 |  |

| bit 6            | <b>DOZEN:</b> Doze Enable bit <sup>(1,2)</sup><br>1 = The CPU executes instruction cycles according to DOZE setting<br>0 = The CPU executes all instruction cycles (fastest, highest power operation) |                    |                |                        |                 |                 |                 |  |

| bit 5            | ROI: Recover-O<br>1 = Entering the<br>operation<br>0 = Interrupt ent                                                                                                                                  | Interrupt Servi    |                | SR) makes DC           | DZEN = 0 bit, b | pringing the CP | U to full-speed |  |

| bit 4            | <b>DOE:</b> Doze-On-<br>1 = Executing R<br>0 = RETFIE doe                                                                                                                                             | ETFIE makes        |                | pringing the C         | PU to reduced   | d speed operati | ion             |  |

| bit 3            | Unimplemented                                                                                                                                                                                         | I: Read as '0'     |                |                        |                 |                 |                 |  |

| bit 2-0          | DOZE<2:0>: Ra<br>111 =1:256<br>110 =1:128<br>101 =1:64<br>100 =1:32<br>011 =1:16<br>010 =1:8<br>001 =1:4<br>000 =1:2                                                                                  | tio of CPU Inst    | ruction Cycles | to Periphera           | I Instruction C | ycles           |                 |  |

#### **Note 1:** When ROI = 1 or DOE = 1, DOZEN is changed by hardware interrupt entry and/or exit.

2: Entering ICD overrides DOZEN, returning the CPU to full execution speed; this bit is not affected.

#### TABLE 12-1: SUMMARY OF REGISTERS ASSOCIATED WITH POWER-DOWN MODE

| Name    | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1     | Bit 0    | Register on<br>Page |

|---------|-------|-------|-------|-------|-------|-------|-----------|----------|---------------------|

| VREGCON | -     | -     | _     | _     | _     |       | VREGPM    | Reserved | 180                 |

| CPUDOZE | IDLEN | DOZEN | ROI   | DOE   | —     |       | DOZE<2:0> |          | 181                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used in Power-Down mode.

#### 15.1.2 CONTROL REGISTERS

Several control registers are used in conjunction with the TBLRD and TBLWT instructions. These include the following registers:

- NVMCON1 register

- NVMCON2 register

- TABLAT register

- TBLPTR registers

#### 15.1.2.1 NVMCON1 and NVMCON2 Registers

The NVMCON1 register (Register 15-1) is the control register for memory accesses. The NVMCON2 register is not a physical register; it is used exclusively in the memory write and erase sequences. Reading NVMCON2 will read all '0's.

The REG<1:0> control bits determine if the access will be to Data EEPROM Memory locations. PFM locations or User IDs, Configuration bits, Rev ID and Device ID. When REG<1:0> = 00, any subsequent operations will operate on the Data EEPROM Memory. When REG<1:0> = 10, any subsequent operations will operate on the program memory. When REG<1:0> = x1, any subsequent operations will operate on the Configuration bits, User IDs, Rev ID and Device ID.

The FREE bit allows the program memory erase operation. When the FREE bit is set, an erase operation is initiated on the next WR command. When FREE is clear, only writes are enabled. This bit is applicable only to the PFM and not to data EEPROM.

When set, the WREN bit will allow a program/erase operation. The WREN bit is cleared on power-up.

The WRERR bit is set by hardware when the WR bit is set and is cleared when the internal programming timer expires and the write operation is successfully complete.

The WR control bit initiates erase/write cycle operation when the REG<1:0> bits point to the Data EEPROM Memory location, and it initiates a write operation when the REG<1:0> bits point to the PFM location. The WR bit cannot be cleared by firmware; it can only be set by firmware. Then the WR bit is cleared by hardware at the completion of the write operation.

The NVMIF Interrupt Flag bit is set when the write is complete. The NVMIF flag stays set until cleared by firmware.

#### 15.1.2.2 TABLAT – Table Latch Register

The Table Latch (TABLAT) is an 8-bit register mapped into the SFR space. The Table Latch register is used to hold 8-bit data during data transfers between program memory and data RAM.

#### 15.1.2.3 TBLPTR – Table Pointer Register

The Table Pointer (TBLPTR) register addresses a byte within the program memory. The TBLPTR is comprised of three SFR registers: Table Pointer Upper Byte, Table Pointer High Byte and Table Pointer Low Byte (TBLPTRU:TBLPTRH:TBLPTRL). These three registers join to form a 22-bit wide pointer. The low-order 21 bits allow the device to address up to 2 Mbytes of program memory space. The 22<sup>nd</sup> bit allows access to the Device ID, the User ID and the Configuration bits.

The Table Pointer register, TBLPTR, is used by the TBLRD and TBLWT instructions. These instructions can update the TBLPTR in one of four ways based on the table operation. These operations on the TBLPTR affect only the low-order 21 bits.

#### 15.1.2.4 Table Pointer Boundaries

TBLPTR is used in reads, writes and erases of the Program Flash Memory.

When a TBLRD is executed, all 22 bits of the TBLPTR determine which byte is read from program memory directly into the TABLAT register.

When a TBLWT is executed the byte in the TABLAT register is written, not to memory but, to a holding register in preparation for a program memory write. The holding registers constitute a write block which varies depending on the device (see Table 15-3). The 3, 4, or 5 LSbs of the TBLPTRL register determine which specific address within the holding register block is written to. The MSBs of the Table Pointer have no effect during TBLWT operations.

When a program memory write is executed the entire holding register block is written to the memory at the address determined by the MSbs of the TBLPTR. The 3, 4, or 5 LSBs are ignored during memory writes. For more detail, see Section 15.1.6 "Writing to Program Flash Memory".

Figure 15-3 describes the relevant boundaries of TBLPTR based on Program Flash Memory operations.

#### REGISTER 16-3: CRCDATH: CRC DATA HIGH BYTE REGISTER

| R/W-xx                                                              | R/W-x/x | R/W-x/x        | R/W-x/x | R/W-x/x          | R/W-x/x          | R/W-x/x | R/W-x/x |

|---------------------------------------------------------------------|---------|----------------|---------|------------------|------------------|---------|---------|

|                                                                     |         |                | DATA    | <15:8>           |                  |         |         |

| bit 7                                                               |         |                |         |                  |                  |         | bit 0   |

|                                                                     |         |                |         |                  |                  |         |         |

| Legend:                                                             |         |                |         |                  |                  |         |         |

| R = Readable I                                                      | bit     | W = Writable k | oit     | U = Unimpler     | nented bit, read | as '0'  |         |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR |         |                |         | R/Value at all o | ther Resets      |         |         |

bit 7-0 DATA<15:8>: CRC Input/Output Data bits

'1' = Bit is set

#### REGISTER 16-4: CRCDATL: CRC DATA LOW BYTE REGISTER

'0' = Bit is cleared

| R/W-xx    | R/W-x/x |

|-----------|---------|---------|---------|---------|---------|---------|---------|

| DATA<7:0> |         |         |         |         |         |         |         |

| bit 7     |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **DATA<7:0>**: CRC Input/Output Data bits Writing to this register fills the shifter.

#### REGISTER 16-5: CRCACCH: CRC ACCUMULATOR HIGH BYTE REGISTER

| R/W-0/0   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|-----------|---------|---------|---------|---------|---------|---------|---------|--|

| ACC<15:8> |         |         |         |         |         |         |         |  |

| bit 7     |         |         |         |         |         |         | bit 0   |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ACC<15:8>: CRC Accumulator Register bits

### 21.0 PERIPHERAL MODULE DISABLE (PMD)

Sleep, Idle and Doze modes allow users to substantially reduce power consumption by slowing or stopping the CPU clock. Even so, peripheral modules still remain clocked, and thus, consume some amount of power. There may be cases where the application needs what these modes do not provide: the ability to allocate limited power resources to the CPU while eliminating power consumption from the peripherals.

The PIC18(L)F2x/4xK42 family addresses this requirement by allowing peripheral modules to be selectively enabled or disabled, placing them into the lowest possible power mode.

All modules are ON by default following any Reset.

#### 21.1 Disabling a Module

Disabling a module has the following effects:

- All clock and control inputs to the module are suspended; there are no logic transitions, and the module will not function.

- · The module is held in Reset.

- · Any SFR becomes "unimplemented"

- Writing is disabled

- Reading returns 00h

- I/O functionality is prioritized as per Section 18.2, I/O Priorities

- All associated Input Selection registers are also disabled

#### 21.2 Enabling a Module

When the PMD register bit is cleared, the module is re-enabled and will be in its Reset state (Power-on Reset). SFR data will reflect the POR Reset values.

Depending on the module, it may take up to one full instruction cycle for the module to become active. There should be no interaction with the module (e.g., writing to registers) for at least one instruction after it has been re-enabled.

#### 21.3 Effects of a Reset

Following any Reset, each control bit is set to '0', enabling all modules.

#### 21.4 System Clock Disable

Setting SYSCMD (PMD0, Register 21-1) disables the system clock (Fosc) distribution network to the peripherals. Not all peripherals make use of SYSCLK, so not all peripherals are affected. Refer to the specific peripheral description to see if it will be affected by this bit.

#### 23.3 Timer1/3/5 Prescaler

Timer1/3/5 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The CKPS bits of the TxCON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMRxH or TMRxL.

#### 23.4 Timer1/3/5 Operation in Asynchronous Counter Mode

If control bit SYNC of the TxCON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 23.4.1 "Reading and Writing Timer1/3/5 in Asynchronous Counter Mode").

Note: When switching from synchronous to asynchronous operation, it is possible to skip an increment. When switching from asynchronous to synchronous operation, it is possible to produce an additional increment.

#### 23.4.1 READING AND WRITING TIMER1/3/5 IN ASYNCHRONOUS COUNTER MODE

Reading TMRxH or TMRxL while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads. For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMRxH:TMRxL register pair.

#### 23.5 Timer1/3/5 16-Bit Read/Write Mode

Timer1/3/5 can be configured to read and write all 16 bits of data, to and from, the 8-bit TMRxL and TMRxH registers, simultaneously. The 16-bit read and write operations are enabled by setting the RD16 bit of the TxCON register.

To accomplish this function, the TMRxH register value is mapped to a buffer register called the TMRxH buffer register. While in 16-Bit mode, the TMRxH register is not directly readable or writable and all read and write operations take place through the use of this TMRxH buffer register.

When a read from the TMRxL register is requested, the value of the TMRxH register is simultaneously loaded into the TMRxH buffer register. When a read from the TMRxH register is requested, the value is provided from the TMRxH buffer register instead. This provides the user with the ability to accurately read all 16 bits of the Timer1/3/5 value from a single instance in time. Reference the block diagram in Figure 23-2 for more details.

In contrast, when not in 16-Bit mode, the user must read each register separately and determine if the values have become invalid due to a rollover that may have occurred between the read operations.

When a write request of the TMRxL register is requested, the TMRxH buffer register is simultaneously updated with the contents of the TMRxH register. The value of TMRxH must be preloaded into the TMRxH buffer register prior to the write request for the TMRxL register. This provides the user with the ability to write all 16 bits to the TMRxL:TMRxH register pair at the same time.

Any requests to write to the TMRxH directly does not clear the Timer1/3/5 prescaler value. The prescaler value is only cleared through write requests to the TMRxL register.

#### 24.5.2 HARDWARE GATE MODE

The Hardware Gate modes operate the same as the Software Gate mode except the T2TMR\_ers external signal can also gate the timer. When used with the CCP the gating extends the PWM period. If the timer is stopped when the PWM output is high then the duty cycle is also extended.

When MODE<4:0> = 00001 then the timer is stopped when the external signal is high. When MODE<4:0> = 00010 then the timer is stopped when the external signal is low.

Figure 24-5 illustrates the Hardware Gating mode for MODE<4:0>= 00001 in which a high input level starts the counter.

|                   | Rev 10000199C<br>9122016                                                                                                                                                          |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODE              | 0600001                                                                                                                                                                           |

| TMRx_clk          |                                                                                                                                                                                   |

| TMRx_ers          |                                                                                                                                                                                   |

| TxPR              | 5                                                                                                                                                                                 |

| TxTMR 0           | $\left( \begin{array}{c} 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 1 \\ 2 \\ 1 \\ 2 \\ 1 \\ 2 \\ 1 \\ 2 \\ 1 \\ 1$ |

| TMRx_postscaled   |                                                                                                                                                                                   |

| PWM Duty<br>Cycle | 3                                                                                                                                                                                 |

| PWM Output        |                                                                                                                                                                                   |

|                   |                                                                                                                                                                                   |

| R/W-0/0          | R/W-0/0            | R/W-0/0           | R/W-0/0        | R/W-0/0             | R/W-0/0             | R/W-0/0             | R/W-0/0             |

|------------------|--------------------|-------------------|----------------|---------------------|---------------------|---------------------|---------------------|

| OVRD             | OVRC               | OVRB              | OVRA           | STRD <sup>(2)</sup> | STRC <sup>(2)</sup> | STRB <sup>(2)</sup> | STRA <sup>(2)</sup> |

| bit 7            |                    |                   | •              |                     |                     |                     | bit C               |

|                  |                    |                   |                |                     |                     |                     |                     |

| Legend:          |                    |                   |                |                     |                     |                     |                     |

| R = Readable     |                    | W = Writable      |                |                     | nented bit, read    |                     |                     |

| u = Bit is uncl  | 0                  | x = Bit is unkr   |                |                     | at POR and BO       |                     | other Resets        |

| '1' = Bit is set |                    | '0' = Bit is cle  | ared           | q = Value dep       | pends on condit     | ion                 |                     |

| <b>b</b> :+ 7    |                    | ring Data D bit   |                |                     |                     |                     |                     |

| bit 7            |                    | ring Data D bit   |                |                     |                     |                     |                     |

| bit 6            |                    | ring Data C bit   |                |                     |                     |                     |                     |

| bit 5            |                    | ring Data B bit   |                |                     |                     |                     |                     |

| bit 4            |                    | ring Data A bit   |                |                     |                     |                     |                     |

| bit 3            |                    | ing Enable bit D  |                |                     |                     |                     |                     |

|                  |                    | output has the    |                |                     | th polarity contr   | ol from POLD        | bit                 |

|                  |                    | output is assigr  |                | OVRD bit            |                     |                     |                     |

| bit 2            | STRC: Steer        | ing Enable bit C  | ;(2)           |                     |                     |                     |                     |

|                  | 1 = CWGxC          | output has the    | CWG data inp   | ut waveform wi      | th polarity contr   | ol from POLC        | bit                 |

|                  | 0 = CWGxC          | output is assigr  | ed to value of | OVRC bit            |                     |                     |                     |

| bit 1            | STRB: Steer        | ing Enable bit E  | 3(2)           |                     |                     |                     |                     |

|                  | 1 = CWGxB          | output has the    | CWG data inpu  | ut waveform wi      | th polarity contr   | ol from POLB I      | oit                 |

|                  | 0 = CWGxB          | output is assign  | ed to value of | OVRB bit            |                     |                     |                     |

| bit 0            | STRA: Steer        | ing Enable bit A  | (2)            |                     |                     |                     |                     |

|                  | 1 = CWGxA          | output has the    | CWG data inpi  | ut waveform wi      | th polarity contr   | ol from POLA I      | oit                 |

|                  | 0 = CWGxA          | output is assigr  | ed to value of | OVRA bit            |                     |                     |                     |

| Note 1: Th       | e bits in this reg | gister apply only | when MODE      | <2:0> = 00x (R      | egister 28-1, St    | eering modes)       |                     |

| 2. Th            | ia hit ia daubla   | hufforod when I   | VODE - 2005 -  | 0.0.1               |                     |                     |                     |

## REGISTER 28-5: CWGxSTR<sup>(1)</sup>: CWG STEERING CONTROL REGISTER

**2:** This bit is double-buffered when MODE < 2:0 > = 0.01.

| Name       | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3           | Bit 2   | Bit 1   | Bit 0   | Register on page |  |

|------------|--------|-------|-------|-------|-----------------|---------|---------|---------|------------------|--|

| SPIxINTF   | SRMTIF | TCZIF | SOSIF | EOSIF | -               | RXOIF   | TXUIF   | —       | 537              |  |

| SPIxINTE   | SRMTIE | TCZIE | SOSIE | EOSIE | —               | RXOIE   | TXUIE   | _       | 538              |  |

| SPIxTCNTH  | _      | —     | _     | _     | -               | TCNT10  | TCNT9   | TCNT8   | 539              |  |

| SPIxTCNTL  | TCNT7  | TCNT6 | TCNT5 | TCNT4 | TCNT3           | TCNT2   | TCNT1   | TCNT0   | 538              |  |

| SPIxTWIDTH | _      | —     | _     | _     | _               | TWIDTH2 | TWIDTH1 | TWITDH0 | 539              |  |

| SPIxBAUD   | BAUD7  | BAUD6 | BAUD5 | BAUD4 | BAUD3           | BAUD2   | BAUD1   | BAUD0   | 540              |  |

| SPIxCON0   | EN     | —     | _     | _     | _               | LSBF    | MST     | BMODE   | 540              |  |

| SPIxCON1   | SMP    | CKE   | CKP   | FST   | _               | SSP     | SDIP    | SDOP    | 541              |  |

| SPIxCON2   | BUSY   | SSFLT | _     | _     | -               | SSET    | TXR     | RXR     | 542              |  |

| SPIxSTATUS | TXWE   | —     | TXBE  | _     | RXRE            | CLRBF   | _       | RXBF    | 543              |  |

| SPIxRXB    | RXB7   | RXB6  | RXB5  | RXB4  | RXB3            | RXB2    | RXB1    | RXB0    | 543              |  |

| SPIxTXB    | TXB7   | TXB6  | TXB5  | TXB4  | TXB3            | TXB2    | TXB1    | TXB0    | 544              |  |

| SPIxCLK    | _      | —     | _     | _     | CLKSEL3         | CLKSEL2 | CLKSEL1 | CLKSEL0 | 544              |  |

| SPIxSCKPPS | _      | _     | _     |       | SPIxSCKPPS<4:0> |         |         |         |                  |  |

| SPIxSSPPS  | _      | _     | _     |       | SPIxSSPPS<4:0>  |         |         |         |                  |  |

| SPIxSDIPPS | _      | _     | _     |       | SPIxSDIPPS<4:0> |         |         |         |                  |  |

#### TABLE 34-3: SUMMARY OF REGISTERS ASSOCIATED WITH SPI

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the SPI module.

#### 38.6.1 DIGITAL FILTER/AVERAGE

The digital filter/average module consists of an accumulator with data feedback options, and control logic to determine when threshold tests need to be applied. The accumulator is a 16-bit wide register which can be accessed through the ADACCH:ADACCL register pair.

Upon each trigger event (the GO bit set or external event trigger), the ADC conversion result is added to the accumulator. If the accumulated result exceeds  $2^{(accumulator_width)} = 18 = 262143$ , the overflow bit ADAOV in the ADSTAT register is set.

The number of samples to be accumulated is determined by the RPT (A/D Repeat Setting) register. Each time a sample is added to the accumulator, the ADCNT register is incremented. Once RPT samples are accumulated (CNT = RPT), an accumulator clear command can be issued by the software by setting the ADACLR bit in the ADCON2 register. Setting the ADACLR bit will also clear the ADAOV (Accumulator overflow) bit in the ADSTAT register, as well as the

ADCNT register. The ADACLR bit is cleared by the hardware when accumulator clearing action is complete.

# Note: When ADC is operating from FRC, five FRC clock cycles are required to execute the ACC clearing operation.

The ADCRS <2:0> bits in the ADCON2 register control the data shift on the accumulator result, which effectively divides the value in accumulator (ADACCU:ADACCH:ADACCL) register pair. For the Accumulate mode of the digital filter, the shift provides a simple scaling operation. For the Average/Burst Average mode, the shift bits are used to determine the number of logical right shifts to be performed on the accumulated result. For the Low-pass Filter mode, the shift is an integral part of the filter, and determines the cut-off frequency of the filter. Table 38-3 shows the -3 dB cut-off frequency in  $\omega$ T (radians) and the highest signal attenuation obtained by this filter at nyquist frequency ( $\omega$ T =  $\pi$ ).

|  | <b>TABLE 38-3</b> : | LOW-PASS FILTER -3 dB CUT-OFF FREQUENCY |

|--|---------------------|-----------------------------------------|

|--|---------------------|-----------------------------------------|

| ADCRS | ωT (radians) @ -3 dB Frequency | dB @ F <sub>nyquist</sub> =1/(2T) |

|-------|--------------------------------|-----------------------------------|

| 1     | 0.72                           | -9.5                              |

| 2     | 0.284                          | -16.9                             |

| 3     | 0.134                          | -23.5                             |

| 4     | 0.065                          | -29.8                             |

| 5     | 0.032                          | -36.0                             |

| 6     | 0.016                          | -42.0                             |

| 7     | 0.0078                         | -48.1                             |

#### 38.6.2 BASIC MODE

Basic mode (ADMD = 000) disables all additional computation features. In this mode, no accumulation occurs but threshold error comparison is performed. Double sampling, Continuous mode, and all CVD features are still available, but no features involving the digital filter/average features are used.

#### 38.6.3 ACCUMULATE MODE

In Accumulate mode (ADMD = 001), after every conversion, the ADC result is added to the ADACC register. The ADACC register is right-shifted by the value of the ADCRS bits in the ADCON2 register. This right-shifted value is copied in to the ADFLT register. The Formatting mode does not affect the right-justification of the ACC value. Upon each sample, CNT is also incremented, incrementing the number of samples accumulated. After each sample and accumulation, the ACC value has a threshold comparison performed on it (see Section 38.6.7 "Threshold Comparison") and the ADTIF interrupt may trigger.

#### 38.6.4 AVERAGE MODE

In Average mode (ADMD = 010), the ADACC registers accumulate with each ADC sample, much as in Accumulate mode, and the ADCNT register increments with each sample. The ADFLT register is also updated with the right-shifted value of the ADACC register. The value of the ADCRS bits governs the number of right shifts. However, in Average mode, the threshold comparison is performed upon CNT being greater than or equal to a user-defined RPT value. In this mode when RPT =  $2^{CNT}$ , then the final accumulated value will be divided by number of samples, allowing for a threshold comparison operation on the average of all gathered samples.

#### 41.6 Operation During Sleep

When enabled, the HLVD circuitry continues to operate during Sleep. If the device voltage crosses the trip point, the HLVDIF bit will be set and the device will wake up from Sleep. Device execution will continue from the interrupt vector address if interrupts have been globally enabled.

#### 41.7 Operation During Idle and Doze Modes

In both Idle and Doze modes, the module is active and events are generated if peripheral is enabled.

#### 41.8 Operation During Freeze

When in Freeze mode, no new event or interrupt can be generated. The state of the LRDY bit is frozen.

Register reads and writes through the CPU interface are allowed.

#### 41.9 Effects of a Reset

A device Reset forces all registers to their Reset state. This forces the HLVD module to be turned off.

# PIC18(L)F24/25K42

| IORWF                       | Inclusive                                                                                                                                                                                                             | OR W v                                                                                                                                    | vith f                                                                                                                               |                                                                                                                                |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                     | IORWF f                                                                                                                                                                                                               | {,d {,a}}                                                                                                                                 |                                                                                                                                      |                                                                                                                                |

| Operands:                   | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                   |                                                                                                                                           |                                                                                                                                      |                                                                                                                                |

| Operation:                  | (W) .OR. (f)                                                                                                                                                                                                          | $\rightarrow$ dest                                                                                                                        |                                                                                                                                      |                                                                                                                                |

| Status Affected:            | N, Z                                                                                                                                                                                                                  |                                                                                                                                           |                                                                                                                                      |                                                                                                                                |

| Encoding:                   | 0001                                                                                                                                                                                                                  | 00da                                                                                                                                      | ffff                                                                                                                                 | ffff                                                                                                                           |

| Description:                | Inclusive Ol<br>'0', the result is<br>(default).<br>If 'a' is '0', tt<br>If 'a' is '1', tt<br>GPR bank.<br>If 'a' is '0' an<br>set is enabl<br>in Indexed I<br>mode when<br>tion 43.2.3<br>Oriented In<br>eral Offset | It is placed I<br>placed I<br>the Access<br>he BSR i<br>and the ex-<br>ed, this i<br>Literal Of<br>ever f ≤ 1<br>"Byte-O<br>the struction | ed in W. I<br>pack in re<br>as Bank is<br>s used to<br>as used to<br>as used to<br>fiset Addr<br>as (5Fh).<br>riented a<br>ns in Ind | f 'd' is '1',<br>gister 'f'<br>selected.<br>select the<br>astruction<br>operates<br>essing<br>See Sec-<br>nd Bit-<br>exed Lit- |

| Words:                      | 1                                                                                                                                                                                                                     |                                                                                                                                           |                                                                                                                                      |                                                                                                                                |

| Cycles:                     | 1                                                                                                                                                                                                                     |                                                                                                                                           |                                                                                                                                      |                                                                                                                                |