Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                            |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 16KB (8K x 16)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

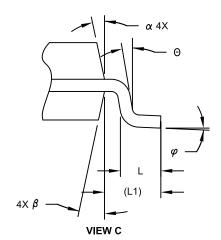

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf24k42-e-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1.0 Device Overview                                                           | 40  |

|-------------------------------------------------------------------------------|-----|

| <ol> <li>Device Overview</li></ol>                                            |     |

| 3.0 PIC18 CPU                                                                 |     |

| 4.0 Memory Organization                                                       |     |

| 5.0 Device Configuration                                                      |     |

| 6.0 Device Information Area                                                   |     |

| 7.0 Device Configuration Information                                          |     |

| 8.0 Resets                                                                    |     |

| 9.0 Oscillator Module (with Fail-Safe Clock Monitor)                          |     |

| 10.0 Reference Clock Output Module                                            |     |

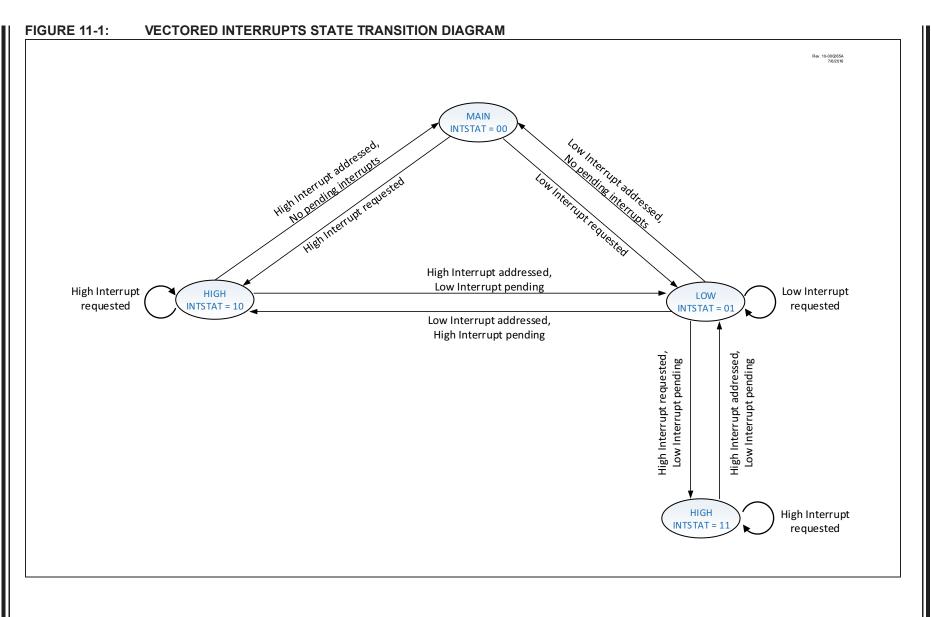

| 11.0 Interrupt Controller                                                     |     |

| 12.0 Power-Saving Operation Modes                                             |     |

| 13.0 Windowed Watchdog Timer (WWDT)                                           |     |

| 14.0 8x8 Hardware Multiplier                                                  |     |

| 15.0 Nonvolatile Memory (NVM) Control                                         |     |

| 16.0 Cyclic Redundancy Check (CRC) Module with Memory Scanner                 |     |

| 17.0 Direct Memory Access (DMA)                                               |     |

| 18.0 I/O Ports                                                                |     |

| 19.0 Peripheral Pin Select (PPS) Module                                       |     |

| 20.0 Interrupt-on-Change                                                      |     |

| 21.0 Peripheral Module Disable (PMD)                                          |     |

| 22.0 Timer0 Module                                                            | 301 |

| 23.0 Timer1/3/5 Module with Gate Control                                      |     |

| 24.0 Timer2/4/6 Module                                                        |     |

| 25.0 Capture/Compare/PWM Module                                               |     |

| 26.0 Pulse-Width Modulation (PWM)                                             |     |

| 27.0 Signal Measurement Timer (SMT)                                           |     |

| 28.0 Complementary Waveform Generator (CWG) Module                            |     |

| 29.0 Configurable Logic Cell (CLC)                                            |     |

| 30.0 Numerically Controlled Oscillator (NCO) Module                           |     |

| 31.0 Zero-Cross Detection (ZCD) Module                                        |     |

| 32.0 Data Signal Modulator (DSM) Module                                       |     |

| 33.0 Universal Asynchronous Receiver Transmitter (UART) With Protocol Support | 477 |

| 34.0 Serial Peripheral Interface (SPI) Module                                 |     |

| 35.0 I <sup>2</sup> C Module                                                  | 546 |

| 36.0 Fixed Voltage Reference (FVR)                                            | 599 |

| 37.0 Temperature Indicator Module                                             | 601 |

| 38.0 Analog-to-Digital Converter with Computation (ADC2) Module               |     |

| 39.0 5-Bit Digital-to-Analog Converter (DAC) Module                           | 642 |

| 40.0 Comparator Module                                                        |     |

| 41.0 High/Low-Voltage Detect (HLVD)                                           |     |

| 42.0 In-Circuit Serial Programming™ (ICSP™)                                   |     |

| 43.0 Instruction Set Summary                                                  | 665 |

| 44.0 Register Summary                                                         |     |

| 45.0 Development Support                                                      |     |

| 46.0 Electrical Specifications                                                | 738 |

| 47.0 DC and AC Characteristics Graphs and Tables                              | 767 |

| 48.0 Packaging Information                                                    | 768 |

| Appendix A: Revision History                                                  | 781 |

## TABLE 1-1: DEVICE FEATURES

| Features                                                                         | PIC18(L)F24K42                                                                                                                 | PIC18(L)F25K42                     |  |  |  |

|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--|--|--|

| Program Memory (Bytes)                                                           | 16384                                                                                                                          | 32768                              |  |  |  |

| Program Memory (Instructions)                                                    | 8192                                                                                                                           | 16384                              |  |  |  |

| Data Memory (Bytes)                                                              | 1024                                                                                                                           | 2048                               |  |  |  |

| Data EEPROM Memory (Bytes)                                                       | 256                                                                                                                            | 256                                |  |  |  |

| I/O Ports                                                                        | A,B,C,E <sup>(1)</sup>                                                                                                         | A,B,C,E <sup>(1)</sup>             |  |  |  |

| Capture/Compare/PWM Modules (CCP)                                                | 4                                                                                                                              | 4                                  |  |  |  |

| 10-Bit Pulse-Width Modulator (PWM)                                               | 4                                                                                                                              | 4                                  |  |  |  |

| 12-Bit Analog-to-Digital Module (ADC <sup>2</sup> ) with Computation Accelerator | 5 internal<br>24 external                                                                                                      | 5 internal<br>24 external          |  |  |  |

| Packages                                                                         | 28-pin SPDIP28-pin SPDIP28-pin SOIC28-pin SOIC28-pin SSOP28-pin SSOP28-pin QFN28-pin QFN28-pin UQFN28-pin UQFN                 |                                    |  |  |  |

| Timers (16-/8-bit)                                                               | 4/3                                                                                                                            |                                    |  |  |  |

| Serial Communications                                                            | 2 UART, 2 I <sup>2</sup> C, 1 SPI                                                                                              |                                    |  |  |  |

| Enhanced Complementary Waveform Generator (ECWG)                                 | 3                                                                                                                              |                                    |  |  |  |

| Zero-Cross Detect (ZCD)                                                          |                                                                                                                                | 1                                  |  |  |  |

| Data Signal Modulator (DSM)                                                      |                                                                                                                                | 1                                  |  |  |  |

| Signal Measurement Timer (SMT)                                                   |                                                                                                                                | 1                                  |  |  |  |

| 5-Bit Digital-to-Analog Converter (DAC)                                          | 1                                                                                                                              |                                    |  |  |  |

| Numerically Controlled Oscillator (NCO)                                          | 1                                                                                                                              |                                    |  |  |  |

| Comparator Module                                                                | 2                                                                                                                              |                                    |  |  |  |

| Direct Memory Access (DMA)                                                       |                                                                                                                                | 2                                  |  |  |  |

| Configurable Logic Cell (CLC)                                                    |                                                                                                                                | 4                                  |  |  |  |

| Peripheral Pin Select (PPS)                                                      | Y                                                                                                                              | es                                 |  |  |  |

| Peripheral Module Disable (PMD)                                                  | Y                                                                                                                              | es                                 |  |  |  |

| 16-bit CRC with Scanner                                                          | Yes                                                                                                                            |                                    |  |  |  |

| Programmable High/Low-Voltage Detect (HLVD)                                      | Y                                                                                                                              | es                                 |  |  |  |

| Programmable Brown-out Reset (BOR)                                               | Y                                                                                                                              | es                                 |  |  |  |

| Resets (and Delays)                                                              | POR, BOR,<br>RESET Instruction,<br>Stack Overflow,<br>Stack Underflow<br>(PWRT, OST),<br>MCLR, WDT, Memory Execution Violation |                                    |  |  |  |

| Instruction Set                                                                  |                                                                                                                                | ructions;<br>struction Set enabled |  |  |  |

| Operating Frequency                                                              | 64                                                                                                                             | MHz                                |  |  |  |

**Note 1:** PORTE contains the single RE3 input-only pin.

## 7.0 DEVICE CONFIGURATION INFORMATION

The Device Configuration Information (DCI) is a dedicated region in the Program memory space mapped from 3FFF00h to 3FFF09h. The data stored in these locations is ready-only and cannot be erased or modified.

Refer to Table 7-1: Device Configuration Information for the complete DCI table address and description. The DCI holds information about the device which is useful for programming and Bootloader applications. These locations are read-only and cannot be erased or modified.

## TABLE 7-1: DEVICE CONFIGURATION INFORMATION

| ADDRESS         | Name  | DESCRIPTION             | VALUE         | UNITS |

|-----------------|-------|-------------------------|---------------|-------|

| 3FFF00h-3FFF01h | ERSIZ | Erase Row Size          | 32            | Words |

| 3FFF02h-3FFF03h | WLSIZ | Number of write latches | 64            |       |

| 3FFF04h-3FFF05h | URSIZ | Number of User Rows     | See Table 7-2 | Rows  |

| 3FFF06h-3FFF07h | EESIZ | EE Data memory size     | 256           | Bytes |

| 3FFF08h-3FFF09h | PCNT  | Pin Count               | 28            | Pins  |

## TABLE 7-2:MEMORY SIZE AND NUMBER OF USER ROWS

| Part Name      | Memory size | Number of user rows |

|----------------|-------------|---------------------|

| PIC18(L)F24K42 | 8K          | 256                 |

| PIC18(L)F25K42 | 16K         | 512                 |

## 7.1 DIA and DCI Access

The DIA and DCI addresses are read-only and cannot be erased or modified. See Section 15.2 "Device Information Area, Device Configuration Area, User ID, Device ID and Configuration Word Access" for more information on accessing these memory locations.

Development tools, such as device programmers and debuggers, may be used to read the DIA and DCI regions, similar to the Device ID and Revision ID.

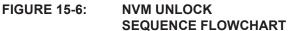

## 15.1.4 NVM UNLOCK SEQUENCE

The unlock sequence is a mechanism that protects the NVM from unintended self-write programming or erasing. The sequence must be executed and completed without interruption to successfully complete any of the following operations:

- PFM Row Erase

- Write of PFM write latches to PFM memory

- Write of PFM write latches to User IDs

- Write to Data EEPROM Memory

- Write to Configuration Words

The unlock sequence consists of the following steps and must be completed in order:

Write 55h to NVMCON2

EXAMPLE 15-2

- Write AAh to NMVCON2

- · Set the WR bit of NVMCON1

Once the WR bit is set, the processor will stall internal operations until the operation is complete and then resume with the next instruction.

Since the unlock sequence must not be interrupted, global interrupts should be disabled prior to the unlock sequence and re-enabled after the unlock sequence is completed.

NVM UNI OCK SEQUENCE

| EARIVIFLE 13-2. | INVINI UNLOCK SEQUENCE | • |                                            |

|-----------------|------------------------|---|--------------------------------------------|

| BCF             | INTCON0,GIE            | ; | Recommended so sequence is not interrupted |

| BANKSEL         | NVMCON1                |   |                                            |

| BSF             | NVMCON1,WREN           | ; | Enable write/erase                         |

| MOVLW           | 55h                    | ; | Load 55h                                   |

| MOVWF           | NVMCON2                | ; | Step 1: Load 55h into NVMCON2              |

| MOVLW           | AAh                    | ; | Step 2: Load W with AAh                    |

| MOVWF           | NVMCON2                | ; | Step 3: Load AAh into NVMCON2              |

| BSF             | INTCON1,WR             | ; | Step 4: Set WR bit to begin write/erase    |

| BSF             | INTCON0,GIE            | ; | Re-enable interrupts                       |

- Note 1: Sequence begins when NVMCON2 is written; steps 1-4 must occur in the cycle-accurate order shown. If the timing of the steps 1 to 4 is corrupted by an interrupt or a debugger Halt, the action will not take place.

- 2: Opcodes shown are illustrative; any instruction that has the indicated effect may be used.

## 16.8 Scanner Module Overview

The Scanner allows segments of the Program Flash Memory or Data EEPROM, to be read out (scanned) to the CRC Peripheral. The Scanner module interacts with the CRC module and supplies it data one word at a time. Data is fetched from the address range defined by SCANLADR registers up to the SCANHADR registers.

The Scanner begins operation when the SGO bit is set (SCANCON0 Register) and ends when either SGO is cleared by the user or when SCANLADR increments past SCANHADR. The SGO bit is also cleared by clearing the EN bit (CRCCON0 register).

## **16.9** Configuring the Scanner

The scanner module may be used in conjunction with the CRC module to perform a CRC calculation over a range of program memory or Data EEPROM addresses. In order to set up the scanner to work with the CRC, perform the following steps:

- Set up the CRC module (See Section 16.7 "Configuring the CRC") and enable the Scanner module by setting the EN bit in the SCANCON0 register.

- 2. Choose which memory region the Scanner module should operate on and set the MREG bit of the SCANCON0 register appropriately.

- 3. If trigger is used for scanner operation, set the TRIGEN bit of the SCANCON0 register and select the trigger source using SCANTRIG register. Select the trigger source using SCANTRIG register and then set the TRIGEN bit of the SCANCON0 register. See Table 16-2 for Scanner Operation.

- 4. If Burst mode of operation is desired, set the BURSTMD bit (SCANCON0 register). See Table 16-2 for Scanner Operation.

- 5. Set the SCANLADRL/H/U and SCANHADRL/H/ U registers with the beginning and ending locations in memory that are to be scanned.

- Select the priority level for the Scanner module (See Section 3.1 "System Arbitration") and lock the priorities (See Section 3.1.1 "Priority Lock").

- 7. Both CRCEN and CRCGO bits must be enabled to use the scanner. Setting the SGO bit will start the scanner operation.

## 16.10 Scanner Interrupt

The scanner will trigger an interrupt when the SCANLADR increments past SCANHADR. The SCANIF bit can only be cleared in software.

## 16.11 Scanning Modes

The interaction of the scanner with the system operation is controlled by the priority selection in the System Arbiter (see **Section 3.2 "Memory Access Scheme**"). Additionally, BURSTMD and TRIGEN also determine the operation of the Scanner.

**16.11.1 TRIGEN =** 0, **BURSTMD =** 0

In this case, the memory access request is granted to the scanner if no other higher priority source is requesting access.

All sources with lower priority than the scanner will get the memory access cycles that are not utilized by the scanner.

**16.11.2 TRIGEN =** 1, **BURSTMD =** 0

In this case, the memory access request is generated when the CRC module is ready to accept.

The memory access request is granted to the scanner if no other higher priority source is requesting access. All sources with lower priority than the scanner will get the memory access cycles that are not utilized by the scanner.

The memory access request is granted to the scanner if no other higher priority source is requesting access. All sources with lower priority than the scanner will get the memory access cycles that are not utilized by the scanner.

## 16.11.3 TRIGEN = x, BURSTMD = 1

In this case, the memory access is always requested by the scanner.

The memory access request is granted to the scanner if no other higher priority source is requesting access. The memory access cycles will not be granted to lower priority sources than the scanner until it completes operation i.e. SGO = 0 (SCANCON0 register)

**Note:** If TRIGEN = 1 and BURSTMD = 1, the user should ensure that the trigger source is active for the Scanner operation to complete.

## 24.5.5 SOFTWARE START ONE-SHOT MODE

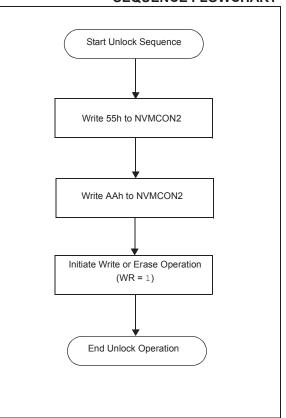

In One-Shot mode the timer resets and the ON bit is cleared when the timer value matches the T2PR period value. The ON bit must be set by software to start another timer cycle. Setting MODE<4:0> = 01000 selects One-Shot mode which is illustrated in Figure 24-8. In the example, ON is controlled by BSF and BCF instructions. In the first case, a BSF instruction sets ON and the counter runs to completion and clears ON. In the second case, a BSF instruction starts the cycle, BCF/BSF instructions turn the counter off and on during the cycle, and then it runs to completion.

When One-Shot mode is used in conjunction with the CCP PWM operation the PWM pulse drive starts concurrent with setting the ON bit. Clearing the ON bit while the PWM drive is active will extend the PWM drive. The PWM drive will terminate when the timer value matches the CCPRx pulse width value. The PWM drive will remain off until software sets the ON bit to start another cycle. If software clears the ON bit after the CCPRx match but before the T2PR match then the PWM drive will be extended by the length of time the ON bit remains cleared. Another timing cycle can only be initiated by setting the ON bit after it has been cleared by a T2PR period count match.

FIGURE 24-8: SOFTWARE START ONE-SHOT MODE TIMING DIAGRAM (MODE = 01000)

#### 25.5 **Register Definitions: CCP Control**

Long bit name prefixes for the CCP peripherals are shown in Table 25-4. Refer to Section 1.4.2.2 "Long Bit Names" for more information.

### **TABLE 25-4:**

| Peripheral | Bit Name Prefix |

|------------|-----------------|

| CCP1       | CCP1            |

| CCP2       | CCP2            |

| CCP3       | CCP3            |

| CCP4       | CCP4            |

## REGISTER 25-1: CCPxCON: CCPx CONTROL REGISTER

| R/W-0/0     | U-0 | R-x | R/W-0/0 | R/W-0/0   | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|-------------|-----|-----|---------|-----------|---------|---------|---------|--|

| EN          | —   | OUT | FMT     | MODE<3:0> |         |         |         |  |

| bit 7 bit ( |     |     |         |           |         |         |         |  |

| Legend:           |                                                                                                               |                             |                    |

|-------------------|---------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit                                                                                              | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set                                                                                              | '0' = Bit is cleared        | x = Bit is unknown |

| pit 7             | EN: CCP Module Enable bit<br>1 = CCP is enabled<br>0 = CCP is disabled                                        |                             |                    |

| oit 6             | Unimplemented: Read as '0'                                                                                    |                             |                    |

| oit 5             | OUT: CCPx Output Data bit (read-only)                                                                         |                             |                    |

| bit 4             | FMT: CCPW (pulse-width) Alignment bit<br><u>MODE = Capture mode:</u><br>Unused<br><u>MODE = Compare mode:</u> |                             |                    |

Unused

MODE = PWM mode:

Left-aligned format 1 = 0 = Right-aligned format

MODE<3:0>: CCPx Mode Select bits

bit 3-0

MODE **Operating Mode** Operation Set CCPxIF PWM Yes PWM operation 11xx Pulse output; clear TMR1(2) Yes 1011 Pulse output Yes 1010 Compare Clear output(1) 1001 Yes Set output<sup>(1)</sup> 1000 Yes Every 16th rising edge of CCPx input 0111 Yes 0110 Every 4th rising edge of CCPx input Yes Every rising edge of CCPx input 0101 Capture Yes 0100 Every falling edge of CCPx input Yes 0011 Every edge of CCPx input Yes Toggle output 0010 Yes Compare Toggle output; clear TMR1<sup>(2)</sup> 0001 Yes 0000 Disabled

Note 1:

The set and clear operations of the Compare mode are reset by setting MODE = 4'b0000 or EN = 0. When MODE = 0001 or 1011, then the timer associated with the CCP module is cleared. TMR1 is the default selection for the CCP 2: module, so it is used for indication purpose only.

## REGISTER 27-13: SMT1CPWL: SMT CAPTURED PULSE WIDTH REGISTER – LOW BYTE

| R-x/x            | R-x/x | R-x/x             | R-x/x | R-x/x          | R-x/x            | R-x/x            | R-x/x        |

|------------------|-------|-------------------|-------|----------------|------------------|------------------|--------------|

|                  |       |                   | SMT10 | CPW<7:0>       |                  |                  |              |

| bit 7            |       |                   |       |                |                  |                  | bit 0        |

|                  |       |                   |       |                |                  |                  |              |

| Legend:          |       |                   |       |                |                  |                  |              |

| R = Readable     | bit   | W = Writable b    | oit   | U = Unimpler   | nented bit, read | d as '0'         |              |

| u = Bit is unch  | anged | x = Bit is unkno  | own   | -n/n = Value a | at POR and BC    | R/Value at all o | other Resets |

| '1' = Bit is set |       | '0' = Bit is clea | red   |                |                  |                  |              |

bit 7-0 SMT1CPW<7:0>: Significant bits of the SMT PW Latch - Low Byte

## REGISTER 27-14: SMT1CPWH: SMT CAPTURED PULSE WIDTH REGISTER – HIGH BYTE

| R-x/x            | R-x/x                                 | R-x/x          | R-x/x | R-x/x          | R-x/x            | R-x/x            | R-x/x        |

|------------------|---------------------------------------|----------------|-------|----------------|------------------|------------------|--------------|

|                  |                                       |                | SMT1C | PW<15:8>       |                  |                  |              |

| bit 7            |                                       |                |       |                |                  |                  | bit 0        |

|                  |                                       |                |       |                |                  |                  |              |

| Legend:          |                                       |                |       |                |                  |                  |              |

| R = Readable b   | it                                    | W = Writable b | oit   | U = Unimpler   | mented bit, read | 1 as '0'         |              |

| u = Bit is uncha | = Bit is unchanged x = Bit is unknown |                |       | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets |

'1' = Bit is set '0' = Bit is cleared

bit 7-0 SMT1CPW<15:8>: Significant bits of the SMT PW Latch - High Byte

## REGISTER 27-15: SMT1CPWU: SMT CAPTURED PULSE WIDTH REGISTER – UPPER BYTE

|     | R-x/x          | R-x/x | R-x/x | R-x/x | R-x/x | R-x/x | R-x/x | R-x/x |  |

|-----|----------------|-------|-------|-------|-------|-------|-------|-------|--|

|     | SMT1CPW<23:16> |       |       |       |       |       |       |       |  |

| bit | bit 7 bit 0    |       |       |       |       |       |       |       |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SMT1CPW<23:16>: Significant bits of the SMT PW Latch - Upper Byte

© 2016-2017 Microchip Technology Inc.

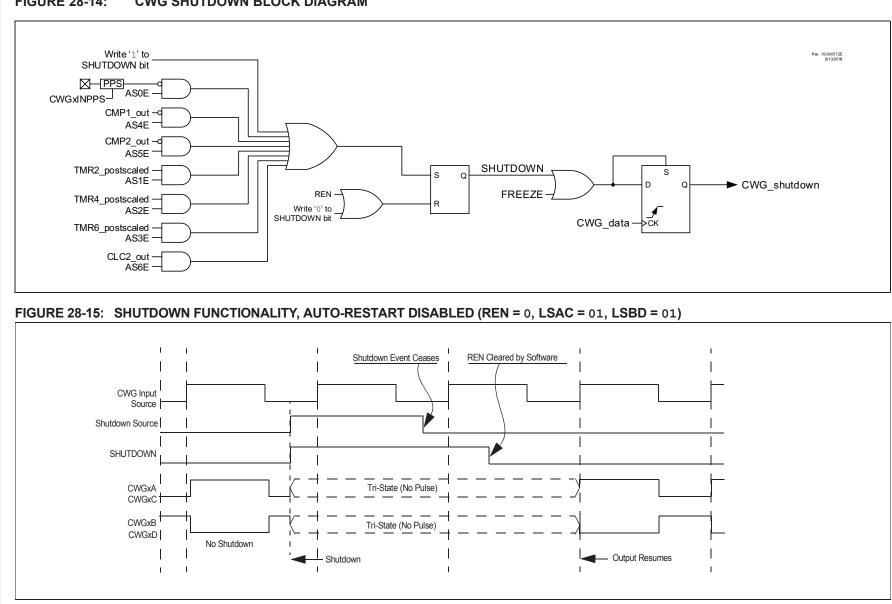

## FIGURE 28-14: CWG SHUTDOWN BLOCK DIAGRAM

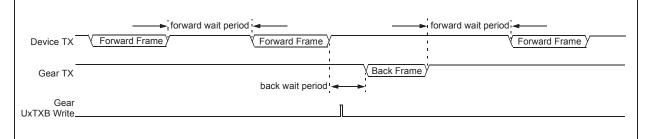

## FIGURE 33-9: DALI FORWARD/BACK FRAME TIMING

## 33.7 General Purpose Manchester (UART1 only)

General purpose Manchester is a subset of the DALI mode. When the UxP1L register is cleared, there is no minimum wait time between frames. This allows full and half-duplex operation because writes to the UxTXB are not held waiting for a receive operation to complete.

General purpose Manchester operation maintains all other aspects of DALI mode such as:

- Single-pulse Start bit

- Most Significant bit first

- No stop periods between back-to-back bytes

General purpose Manchester mode is configured with the following settings:

- MODE<3:0> = 1000

- TXEN = 1

- RXEN = 1

- UxP1 = 0h

- UxBRGH:L = desired baud rate

- TXPOL and RXPOL = desired Idle state

- STP = desired number of stop periods

- RxyPPS = TX pin selection code

- TX pin TRIS control = 0

- RXPPS = RX pin selection code

- RX pin TRIS control = 1

- Input pin ANSEL bit = 0

- ON = 1

The Manchester bit stream timing is shown in Figure 33-7.

## 33.8 Polarity

Receive and transmit polarity is user selectable and affects all modes of operation.

The idle level is programmable with the polarity control bits in the UxCON2 register. The control bits default to '0', which select a high idle level. The low level Idle state is selected by setting the control bit to '1'. TXPOL controls the TX idle level. RXPOL controls the RX idle level.

```

© 2016-2017 Microchip Technology Inc.

```

## 33.17.2 AUTO-BAUD OVERFLOW

During the course of automatic baud detection, the ABDOVF bit in the UxERRIR register will be set if the baud rate counter overflows before the fifth falling edge is detected on the RX pin. The ABDOVF bit indicates that the counter has exceeded the maximum count that can fit in the 16 bits of the UxBRGH:UxBRGL register pair. After the ABDOVF bit has been set, the state machine continues to search until the fifth falling edge is detected on the RX pin. Upon detecting the fifth falling RX edge, the hardware will set the ABDIF interrupt flag and clear the ABDEN bit in the UxCON0 register. The UxBRGH and UxBRGL register values retain their previous value. The ABDIF flag in the UxUIR register and ABDOVF flag in the UxERRIR register can be cleared by software directly. To generate an interrupt on an auto-baud overflow condition, all the following bits must be set:

- ABDOVE bit in the UxERRIE register

- UxEIE bit in the PIEx register

- PIE and GIE bits in the INTCON register

To terminate the auto-baud process before the ABDIF flag is set, clear the ABDEN bit, then clear the ABDOVF bit in the UxERRIR register.

## 33.17.3 AUTO-WAKE-UP ON BREAK

During Sleep mode, all clocks to the UART are suspended. Because of this, the Baud Rate Generator is inactive and a proper character reception cannot be performed. The Auto-Wake-up feature allows the controller to wake-up due to activity on the RX line.

The Auto-Wake-up feature is enabled by setting both the WUE bit in the UxCON1 register and the UxIE bit in the PIEx register. Once set, the normal receive sequence on RX is disabled, and the UART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a transition out of the Idle state on the RX line. (This coincides with the start of a Break or a wake-up signal character for the LIN protocol.)

The UART module generates a WUIF interrupt coincident with the wake-up event. The interrupt is generated synchronously to the Q clocks in normal CPU operating modes (Figure 33-13), and asynchronously, if the device is in Sleep mode (Figure 33-14). The interrupt condition is cleared by clearing the WUIF bit in the UxUIR register. To generate an interrupt on a wake-up event, all the following bits must be set:

- UxIE bit in the PIEx register

- PIE and GIE bits in the INTCON register

The WUE bit is automatically cleared by the transition to the Idle state on the RX line at the end of the Break. This signals to the user that the Break event is over. At this point, the UART module is in Idle mode, waiting to receive the next character.

## 33.17.3.1 Special Considerations

### **Break Character**

To avoid character errors or character fragments during a wake-up event, the wake-up character must be all zeros.

When the wake-up is enabled, the function works independent of the low time on the data stream. If the WUE bit is set and a valid non-zero character is received, the low time from the Start bit to the first rising edge will be interpreted as the wake-up event. The remaining bits of the character will be received as a fragmented character and subsequent characters can result in framing or overrun errors.

Therefore, the initial character of the transmission must be all zeros. This must be eleven or more bit times, 13bit times recommended for LIN bus, or any number of bit times for standard RS-232 devices.

## **Oscillator Start-up Time**

Oscillator start-up time must be considered, especially in applications using oscillators with longer start-up intervals (i.e., LP, XT or HS/PLL modes). The Sync Break (or wake-up signal) character must be of sufficient length, and be followed by a sufficient interval, to allow enough time for the selected oscillator to start and provide proper initialization of the UART.

## WUE Bit

To ensure that no actual data is lost, check the RXIDL bit to verify that a receive operation is not in process before setting the WUE bit. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

### REGISTER 34-2: SPIXINTE: SPI INTERRUPT ENABLE REGISTER

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | R/W-0/0 | R/W-0/0 | U-0   |

|---------|---------|---------|---------|-----|---------|---------|-------|

| SRMTIE  | TCZIE   | SOSIE   | EOSIE   | —   | RXOIE   | TXUIE   | —     |

| bit 7   |         |         |         |     |         |         | bit 0 |

| Legend:        |                                                              |  |

|----------------|--------------------------------------------------------------|--|

| R = Readable b | bit W = Writable bit U = Unimplemented bit, read as '0'      |  |

| bit 7          | SRMTIE: Shift Register Empty Interrupt Enable bit            |  |

| bit i          | 1 = Enables the Shift Register Empty Interrupt               |  |

|                | 0 = Disables the Shift Register Empty Interrupt              |  |

| bit 6          | <b>TCZIE</b> : Transfer Counter is Zero Interrupt Enable bit |  |

|                | 1 = Enables the Transfer Counter is Zero Interrupt           |  |

|                | 0 = Disables the Transfer Counter is Zero Interrupt          |  |

| bit 5          | SOSIE: Start of Slave Select Interrupt Enable bit            |  |

|                | 1 = Enables the Start of Slave Select Interrupt              |  |

|                | 0 = Disables the Start of Slave Select Interrupt             |  |

| bit 4          | EOSIE: End of Slave Select Interrupt Enable bit              |  |

|                | 1 = Enables the End of Slave Select Interrupt                |  |

|                | 0 = Disables the End of Slave Select Interrupt               |  |

| bit 3          | Unimplemented: Read as '0'                                   |  |

| bit 2          | RXOIE: Receiver Overflow Interrupt Enable bit                |  |

|                | 1 = Enables the Receiver Overflow Interrupt                  |  |

|                | 0 = Disables the Receiver Overflow Interrupt                 |  |

| bit 1          | TXUIE: Transmitter Underflow Interrupt Enable bit            |  |

|                | 1 = Enables the Transmitter Underflow Interrupt              |  |

|                | 0 = Disables the Transmitter Underflow Interrupt             |  |

| bit 0          | Unimplemented: Read as '0'                                   |  |

## **REGISTER 34-3:** SPIXTCNTL – SPI TRANSFER COUNTER LSB REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TCNT7   | TCNT6   | TCNT5   | TCNT4   | TCNT3   | TCNT2   | TCNT1   | TCNT0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:   |            |                  |                                    |  |

|-----------|------------|------------------|------------------------------------|--|

| R = Reada | able bit   | W = Writable bit | U = Unimplemented bit, read as '0' |  |

| bit 7-0   | TCNT<7:0>  |                  |                                    |  |

|           | BMODE = 0: |                  |                                    |  |

|           |            |                  |                                    |  |

Bits 10-3 of the Transfer Counter, counting the total number of bits to transfer

BMODE = 1:

Bits 7-0 of the Transfer Counter, counting the total number of bytes to transfer

Note: This register should not be written to while a transfer is in progress (BUSY bit of SPIxCON2 is set).

| Name      | Bit 7    | Bit 6  | Bit 5   | Bit 4  | Bit 3   | Bit 2 | Bit 1     | Bit 0  | Register<br>on page |

|-----------|----------|--------|---------|--------|---------|-------|-----------|--------|---------------------|

| I2CxBTO   | —        | _      | _       | _      | —       |       | BTO<2:0>  |        | 584                 |

| I2CxCLK   | —        | _      | —       | _      | —       |       | CLK<2:0>  |        | 583                 |

| I2CxPIE   | CNTIE    | ACKTIE | —       | WRIE   | ADRIE   | PCIE  | RSCIE     | SCIE   | 590                 |

| I2CxPIR   | CNTIF    | ACKTIF | —       | WRIF   | ADRIF   | PCIF  | RSCIF     | SCIF   | 589                 |

| I2CxERR   | —        | BTOIF  | BCLIF   | NACKIF | —       | BTOIE | BCLIE     | NACKIE | 587                 |

| I2CxSTAT0 | BFRE     | SMA    | MMA     | R      | D       | —     | —         | —      | 585                 |

| I2CxSTAT1 | TXWE     | _      | TXBE    | _      | RXRE    | CLRBF | —         | RXBF   | 586                 |

| I2CxCON0  | EN       | RSEN   | S       | CSTR   | MDR     |       | MODE<2:0> | •      | 579                 |

| I2CxCON1  | ACKCNT   | ACKDT  | ACKSTAT | ACKT   |         | RXOV  | TXU       | CSD    | 581                 |

| I2CxCON2  | ACNT     | GCEN   | FME     | ADB    | SDAHT   | <3:2> | BFRE      | T<1:0> | 582                 |

| I2CxADR0  |          |        |         | AI     | DR<7:0> |       |           |        | 591                 |

| I2CxADR1  |          |        |         | A      | DR<7:1> |       |           | _      | 592                 |

| I2CxADR2  |          |        |         | A      | DR<7:0> |       |           |        | 593                 |

| I2CxADR3  |          |        |         | A      | DR<7:1> |       |           |        | 594                 |

| I2CxADB0  |          |        |         | A      | DB<7:0> |       |           |        | 595                 |

| I2CxADB1  |          |        |         | A      | DB<7:0> |       |           |        | 596                 |

| I2CxCNT   | CNT<7:0> |        |         |        |         |       |           | 588    |                     |

| I2CxRXB   | RXB<7:0> |        |         |        |         |       |           |        | 597                 |

| I2CxTXB   |          |        |         | T      | XB<7:0> |       |           |        | 597                 |

## TABLE 35-19: SUMMARY OF REGISTERS FOR I<sup>2</sup>C 8-BIT MACRO

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the  $I^2C$  module.

| U-0                                     | U-0                 | U-0            | R/W-0/0      | R/W-0/0            | R/W-0/0          | R/W-0/0        | R/W-0/0      |

|-----------------------------------------|---------------------|----------------|--------------|--------------------|------------------|----------------|--------------|

| _                                       | _                   | _              |              |                    | ADCAP<4:0>       |                |              |

| bit 7                                   |                     |                |              |                    |                  |                | bit 0        |

|                                         |                     |                |              |                    |                  |                |              |

| Legend:                                 |                     |                |              |                    |                  |                |              |

| R = Readable bit W = Writable bit       |                     |                |              | U = Unimpler       | nented bit, read | l as '0'       |              |

| u = Bit is unchanged x = Bit is unknown |                     |                | iown         | -n/n = Value a     | at POR and BO    | R/Value at all | other Resets |

| '1' = Bit is set '0' = Bit is cleared   |                     |                |              |                    |                  |                |              |

|                                         |                     |                |              |                    |                  |                |              |

| bit 7-5                                 | Unimplemen          | ted: Read as ' | )'           |                    |                  |                |              |

| bit 4-0                                 | ADCAP<4:0>          | . ADC Addition | al Sample Ca | apacitor Selection | on bits          |                |              |

|                                         | 11111 <b>= 31</b> p | νF             |              |                    |                  |                |              |

|                                         | 11110 <b>= 30 p</b> | νF             |              |                    |                  |                |              |

|                                         | 11101 <b>= 29 p</b> | νF             |              |                    |                  |                |              |

|                                         | •                   |                |              |                    |                  |                |              |

|                                         | •                   |                |              |                    |                  |                |              |

|                                         | •                   | _              |              |                    |                  |                |              |

|                                         | 00011 <b>= 3 pF</b> |                |              |                    |                  |                |              |

|                                         | 00010 <b>= 2 pF</b> | -              |              |                    |                  |                |              |

## REGISTER 38-13: ADCAP: ADC ADDITIONAL SAMPLE CAPACITOR SELECTION REGISTER

## **REGISTER 38-14: ADRPT: ADC REPEAT SETTING REGISTER**

'0' = Bit is cleared

00000 = No additional capacitance

| REGISTER 30      | D-14. AURP | I. ADC REFE      | AISEIIIN | G REGISTER     | (                |                |              |

|------------------|------------|------------------|----------|----------------|------------------|----------------|--------------|

| R/W-0/0          | R/W-0/0    | R/W-0/0          | R/W-0/0  | R/W-0/0        | R/W-0/0          | R/W-0/0        | R/W-0/0      |

|                  |            |                  | RPT      | <7:0>          |                  |                |              |

| bit 7            |            |                  |          |                |                  |                | bit 0        |

|                  |            |                  |          |                |                  |                |              |

| Legend:          |            |                  |          |                |                  |                |              |

| R = Readable I   | bit        | W = Writable b   | it       | U = Unimpler   | nented bit, read | d as '0'       |              |

| u = Bit is uncha | anged      | x = Bit is unkno | own      | -n/n = Value a | at POR and BO    | R/Value at all | other Resets |

### bit 7-0 **RPT<7:0>**: ADC Repeat Threshold bits

'1' = Bit is set

00001 = 1 pF

Counts the number of times that the ADC has been triggered and is used along with CNT to determine when the error threshold is checked when the computation is Low-pass Filter, Burst Average, or Average modes. See Table 38-2 for more details.

| BRA         | L L                            | Unconditional Branch                                                                   |                                                     |                                         |  |  |  |  |

|-------------|--------------------------------|----------------------------------------------------------------------------------------|-----------------------------------------------------|-----------------------------------------|--|--|--|--|

| Synta       | ax:                            | BRA n                                                                                  |                                                     |                                         |  |  |  |  |

| Oper        | ands:                          | $-1024 \le n \le 10$                                                                   | )23                                                 |                                         |  |  |  |  |

| Oper        | ation:                         | (PC) + 2 + 2n                                                                          | $\rightarrow$ PC                                    |                                         |  |  |  |  |

| Statu       | s Affected:                    | None                                                                                   |                                                     |                                         |  |  |  |  |

| Enco        | ding:                          | 1101 0                                                                                 | )nnn nnni                                           | n nnnn                                  |  |  |  |  |

| Desc        | ription:                       | Add the 2's co<br>the PC. Since<br>mented to fetc<br>new address w<br>instruction is a | the PC will ha<br>h the next inst<br>vill be PC + 2 | ve incre-<br>ruction, the<br>+ 2n. This |  |  |  |  |

| Word        | ls:                            | 1                                                                                      |                                                     |                                         |  |  |  |  |

| Cycle       | es:                            | 2                                                                                      |                                                     |                                         |  |  |  |  |

| QC          | ycle Activity:                 |                                                                                        |                                                     |                                         |  |  |  |  |

|             | Q1                             | Q2                                                                                     | Q3                                                  | Q4                                      |  |  |  |  |

|             | Decode                         | Read literal<br>'n'                                                                    | Process<br>Data                                     | Write to PC                             |  |  |  |  |

|             | No<br>operation                | No<br>operation                                                                        | No<br>operation                                     | No<br>operation                         |  |  |  |  |

| <u>Exan</u> | <u>nple</u> :<br>Before Instru | HERE                                                                                   | BRA Jump                                            |                                         |  |  |  |  |

|             | PC                             |                                                                                        | dress (HERE)                                        | 1                                       |  |  |  |  |

|             | After Instructi                | on                                                                                     |                                                     |                                         |  |  |  |  |

| BSF                            | B                                         | it Set f                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                           |                                    |  |  |  |

|--------------------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------------------------|--|--|--|

| Syntax:                        | В                                         | SF f, b                                                                                                             | {,a}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                           |                                    |  |  |  |

| Operands:                      | 0                                         | $\begin{array}{l} 0 \leq f \leq 255 \\ 0 \leq b \leq 7 \\ a \in [0,1] \end{array}$                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                           |                                    |  |  |  |

| Operation:                     | 1                                         | $\rightarrow$ f <b></b>                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                           |                                    |  |  |  |

| Status Affected                | : N                                       | one                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                           |                                    |  |  |  |

| Encoding:                      |                                           | 1000                                                                                                                | bbba                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ffff                                                                                                                      | ffff                               |  |  |  |

| Description:                   | lf<br>G<br>If<br>se<br>in<br>m<br>ti<br>O | 'a' is '0',<br>'a' is '1',<br>PR bank<br>'a' is '0' a<br>et is enab<br>Indexed<br>ode whe<br>on 43.2.3<br>riented I | the BSR is the BSR is the BSR is the BSR is the second state of t | ss Bank is<br>is used to<br>ktended in<br>nstructior<br>ffset Addr<br>95 (5Fh).<br><b>Priented a</b><br><b>ons in Inc</b> | See Sec-<br>and Bit-<br>lexed Lit- |  |  |  |

| Words:                         | 1                                         |                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                           |                                    |  |  |  |

| Cycles:                        | 1                                         |                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                           |                                    |  |  |  |

| Q Cycle Activi                 | ty:                                       |                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                           |                                    |  |  |  |