Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

|                            | 64MHz                                                                        |

| Speed                      | · · · · · ·                                                                  |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                             |

| Number of I/O              | 25                                                                           |

| Program Memory Size        | 16KB (8K x 16)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 256 x 8                                                                      |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-VQFN Exposed Pad                                                          |

| Supplier Device Package    | 28-QFN (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf24k42t-i-ml |

#### **Analog Peripherals**

- Analog-to-Digital Converter with Computation (ADC2):

- 12-bit with up to 35 external channels

- Automated post-processing

- Automates math functions on input signals: averaging, filter calculations, oversampling and threshold comparison

- Operates in Sleep

- Integrated charge pump for low-voltage operation

- Hardware Capacitive Voltage Divider (CVD):

- Automates touch sampling and reduces software size and CPU usage when touch or proximity sensing is required

- Adjustable sample and hold capacitor array

- Two guard ring output drives

- · Temperature Sensor

- Internal connection to ADC

- Can be calibrated for improved accuracy

- · Two Comparator:

- Low-Power/High-Speed mode

- Fixed voltage reference at noninverting input(s)

- Comparator outputs externally accessible

- 5-bit Digital-to-Analog Converter (DAC):

- 5-bit resolution, rail-to-rail

- Positive Reference Selection

- Unbuffered I/O pin output

- Internal connections to ADCs and comparators

- Voltage Reference

- Fixed voltage reference with 1.024V, 2.048V and 4.096V output levels

#### **Flexible Oscillator Structure**

- · High-Precision Internal Oscillator

- Selectable frequency range up to 64 MHz

- ±1% at calibration (nominal)

- Low-Power Internal 32 kHz Oscillator (LFIN-TOSC)

- External 32 kHz Crystal Oscillator (SOCS)

- External Oscillator Block with:

- x4 PLL with external sources

- Three crystal/resonator modes up to 20 MHz

- Three external clock modes up to 20 MHz

- · Fail-Safe Clock Monitor

- Allows for safe shutdown if peripherals clock stops

- Oscillator Start-up Timer (OST)

- Ensures stability of crystal oscillator sources

#### 5.0 DEVICE CONFIGURATION

Device configuration consists of the Configuration Words, User ID, Device ID, Rev ID, Device Information Area (DIA), (see Section 6.0 "Device Information Area"), and the Device Configuration Information (DCI) regions, (see Section 7.0 "Device Configuration Information").

### **5.1** Configuration Words

There are five Configuration Word bits that allow the user to setup the device with several choices of oscillators, Resets and memory protection options. These are implemented as Configuration Word 1 through Configuration Word 5 at 300000h through 300008h.

## 9.0 OSCILLATOR MODULE (WITH FAIL-SAFE CLOCK MONITOR)

#### 9.1 Overview

The oscillator module has multiple clock sources and selection features that allow it to be used in a wide range of applications while maximizing performance and minimizing power consumption. Figure 9-1 illustrates a block diagram of the oscillator module.

Clock sources can be supplied from external oscillators, quartz-crystal resonators and ceramic resonators. In addition, the system clock source can be supplied from one of two internal oscillators and PLL circuits, with a choice of speeds selectable via software. Additional clock features include:

- Selectable system clock source between external or internal sources via software.

- Fail-Safe Clock Monitor (FSCM) designed to detect a failure of the external clock source (LP, XT, HS, ECH, ECM, ECL) and switch automatically to the internal oscillator.

- Oscillator Start-up Timer (OST) ensures stability of crystal oscillator sources.

The RSTOSC bits of Configuration Word 1 (Register 5-1) determine the type of oscillator that will be used when the device runs after Reset, including when it is first powered up.

If an external clock source is selected, the FEXTOSC bits of Configuration Word 1 must be used in conjunction with the RSTOSC bits to select the External Clock mode.

The external oscillator module can be configured in one of the following clock modes, by setting the FEXTOSC<2:0> bits of Configuration Word 1:

- ECL External Clock Low-Power mode (below 100 kHz)

- ECM External Clock Medium Power mode (100 kHz to 8 MHz)

- 3. ECH External Clock High-Power mode (above 8 MHz)

- 4. LP 32 kHz Low-Power Crystal mode.

- XT Medium Gain Crystal or Ceramic Resonator Oscillator mode (between 100 kHz and 8 MHz)

- HS High Gain Crystal or Ceramic Resonator mode (above 4 MHz)

The ECH, ECM, and ECL Clock modes rely on an external logic level signal as the device clock source. The LP, XT, and HS Clock modes require an external crystal or resonator to be connected to the device. Each mode is optimized for a different frequency range. The internal oscillator block produces low and high-frequency clock sources, designated LFINTOSC and HFINTOSC. (see Internal Oscillator Block, Figure 9-1). Multiple device clock frequencies may be derived from these clock sources.

#### REGISTER 11-19: PIE5: PERIPHERAL INTERRUPT ENABLE REGISTER 5

| R/W-0/0  | R/W-0/0  | R/W-0/0 | R/W-0/0  | R/W-0/0    | R/W-0/0    | R/W-0/0 | R/W-0/0 |

|----------|----------|---------|----------|------------|------------|---------|---------|

| I2C2TXIE | I2C2RXIE | DMA2AIE | DMA2ORIE | DMA2DCNTIE | DMA2SCNTIE | C2IE    | INT1IE  |

| bit 7    |          |         |          |            |            |         | bit 0   |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

bit 7 **I2C2TXIE:** I<sup>2</sup>C2 Transmit Interrupt Enable bit 1 = Enabled 0 = Disabled **I2C2RXIE:** I<sup>2</sup>C2 Receive Interrupt Enable bit bit 6 1 = Enabled 0 = Disabled bit 5 DMA2AIE: DMA2 Abort Interrupt Enable bit 1 = Enabled 0 = Disabled bit 4 DMA2ORIE: DMA2 Overrun Interrupt Enable bit 1 = Enabled 0 = Disabled bit 3 **DMA2DCNTIE:** DMA2 Destination Count Interrupt Enable bit 1 = Enabled 0 = Disabled bit 2 DMA2SCNTIE: DMA2 Source Count Interrupt Enable bit 1 = Enabled 0 = Disabled bit 1 C2IE: C2 Interrupt Enable bit 1 = Enabled 0 = Disabled bit 0 INT1IE: External Interrupt 1 Enable bit 1 = Enabled 0 = Disabled

#### REGISTER 18-7: SLRCONx: SLEW RATE CONTROL REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| SLRx7   | SLRx6   | SLRx5   | SLRx4   | SLRx3   | SLRx2   | SLRx1   | SLRx0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

'1' = Bit is set 0' = Bit is cleared 0' = Bit is unknown

-n/n = Value at POR and BOR/Value at all other Resets

bit 7-0 **SLRx<7:0>**: Slew Rate Control on Pins Rx<7:0>, respectively

1 = Port pin slew rate is limited0 = Port pin slews at maximum rate

#### TABLE 18-7: SLEW RATE CONTROL REGISTERS

| Name    | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| SLRCONA | SLRA7 | SLRA6 | SLRA5 | SLRA4 | SLRA3 | SLRA2 | SLRA1 | SLRA0 |

| SLRCONB | SLRB7 | SLRB6 | SLRB5 | SLRB4 | SLRB3 | SLRB2 | SLRB1 | SLRB0 |

| SLRCONC | SLRC7 | SLRC6 | SLRC5 | SLRC4 | SLRC3 | SLRC2 | SLRC1 | SLRC0 |

#### 22.1 Timer0 Operation

Timer0 can operate as either an 8-bit timer/counter or a 16-bit timer/counter. The mode is selected with the MD16 bit of the T0CON register.

#### 22.1.1 16-BIT MODE

The register pair TMR0H:TMR0L increments on the rising edge of the clock source. A 15-bit prescaler on the clock input gives several prescale options (see prescaler control bits, CKPS<3:0> in the T0CON1 register).

### 22.1.1.1 Timer0 Reads and Writes in 16-Bit Mode

In 16-bit mode, in order to avoid rollover between reading high and low registers, the TMR0H register is a buffered copy of the actual high byte of Timer0, which is neither directly readable, nor writable (see Figure 22-1). TMR0H is updated with the contents of the high byte of Timer0 during a read of TMR0L. This provides the ability to read all 16 bits of Timer0 without having to verify that the read of the high and low byte was valid, due to a rollover between successive reads of the high and low byte.

Similarly, a write to the high byte of Timer0 must also take place through the TMR0H Buffer register. The high byte is updated with the contents of TMR0H when a write occurs to TMR0L. This allows all 16 bits of Timer0 to be updated at once.

#### 22.1.2 8-BIT MODE

In 8-bit mode, the value of TMR0L is compared to that of the Period buffer, a copy of TMR0H, on each clock cycle. When the two values match, the following events happen:

- TMR0\_out goes high for one prescaled clock period

- TMR0L is reset

- The contents of TMR0H are copied to the period buffer

In 8-bit mode, the TMR0L and TMR0H registers are both directly readable and writable. The TMR0L register is cleared on any device Reset, while the TMR0H register initializes at FFh.

Both the prescaler and postscaler counters are cleared on the following events:

- · A write to the TMR0L register

- A write to either the T0CON0 or T0CON1 registers

- Any device Reset Power-on Reset (POR), MCLR Reset, Watchdog Timer Reset (WDTR) or

- Brown-out Reset (BOR)

#### 22.1.3 COUNTER MODE

In Counter mode, the prescaler is normally disabled by setting the CKPS bits of the T0CON1 register to '0000'. Each rising edge of the clock input (or the output of the prescaler if the prescaler is used) increments the counter by '1'.

#### 22.1.4 TIMER MODE

In Timer mode, the Timer0 module will increment every instruction cycle as long as there is a valid clock signal and the CKPS bits of the T0CON1 register (Register 22-2) are set to '0000'. When a prescaler is added, the timer will increment at the rate based on the prescaler value.

#### 22.1.5 ASYNCHRONOUS MODE

When the ASYNC bit of the T0CON1 register is set (ASYNC = '1'), the counter increments with each rising edge of the input source (or output of the prescaler, if used). Asynchronous mode allows the counter to continue operation during Sleep mode provided that the clock also continues to operate during Sleep.

#### 22.1.6 SYNCHRONOUS MODE

When the ASYNC bit of the TOCON1 register is clear (ASYNC = '0'), the counter clock is synchronized to the system clock (Fosc/4). When operating in Synchronous mode, the counter clock frequency cannot exceed Fosc/4.

#### 22.2 Clock Source Selection

The CS<2:0> bits of the T0CON1 register are used to select the clock source for Timer0. Register 22-2 displays the clock source selections.

#### 22.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected, Timer0 operates as a timer and will increment on multiples of the clock source, as determined by the Timer0 prescaler.

#### 22.2.2 EXTERNAL CLOCK SOURCE

When an external clock source is selected, Timer0 can operate as either a timer or a counter. Timer0 will increment on multiples of the rising edge of the external clock source, as determined by the Timer0 prescaler.

#### 23.1 Timer1/3/5 Operation

The Timer1/3/5 module is a 16-bit incrementing counter which is accessed through the TMRxH:TMRxL register pair. Writes to TMRxH or TMRxL directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

Timer1/3/5 is enabled by configuring the ON and GE bits in the TxCON and TxGCON registers, respectively. Table 23-1 displays the Timer1/3/5 enable selections.

TABLE 23-1: TIMER1/3/5 ENABLE SELECTIONS

| ON | GE | Timer1/3/5<br>Operation |

|----|----|-------------------------|

| 1  | 1  | Count Enabled           |

| 1  | 0  | Always On               |

| 0  | 1  | Off                     |

| 0  | 0  | Off                     |

#### 23.2 Clock Source Selection

The CS<4:0> bits of the TMRxCLK register (Register 23-3) are used to select the clock source for Timer1/3/5. The five TMRxCLK bits allow the selection of several possible synchronous and asynchronous clock sources. Register 23-3 displays the clock source selections.

#### 23.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected the TMRxH:TMRxL register pair will increment on multiples of Fosc as determined by the Timer1/3/5 prescaler.

When the Fosc internal clock source is selected, the Timer1/3/5 register value will increment by four counts every instruction clock cycle. Due to this condition, a 2 LSB error in resolution will occur when reading the Timer1/3/5 value. To utilize the full resolution of Timer1/3/5, an asynchronous input signal must be used to gate the Timer1/3/5 clock input.

The following asynchronous sources may be used at the Timer1/3/5 gate:

- · Asynchronous event on the TxGPPS pin

- TMR0OUT

- TMR1/3/5OUT (excluding the TMR for which it is being used)

- TMR 2/4/6OUT (post-scaled)

- CMP1/2OUT

- SMT1 match

- NCO10UT

- PWM5/6/7/8 OUT

- CCP1/2/3/4 OUT

- CLC1/2/3/4 OUT

- ZCDOUT

Note: In Co

In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge after any one or more of the following conditions:

- · Timer1/3/5 enabled after POR

- Write to TMRxH or TMRxI

- · Timer1/3/5 is disabled

- Timer1/3/5 is disabled (TMRxON = 0) when TxCKI is high then Timer1/3/5 is enabled (TMRxON = 1) when TxCKI is low.

#### 23.2.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1/3/5 module may work as a timer or a counter.

When enabled to count, Timer1/3/5 is incremented on the rising edge of the external clock input of the TxCKIPPS pin. This external clock source can be synchronized to the microcontroller system clock or it can run asynchronously.

When used as a timer with a clock oscillator, an external 32.768 kHz crystal can be used in conjunction with the dedicated secondary internal oscillator circuit.

## 24.5.7 EDGE-TRIGGERED HARDWARE LIMIT ONE-SHOT MODE

In Edge-Triggered Hardware Limit One-Shot modes the timer starts on the first external signal edge after the ON bit is set and resets on all subsequent edges. Only the first edge after the ON bit is set is needed to start the timer. The counter will resume counting automatically two clocks after all subsequent external Reset edges. Edge triggers are as follows:

Rising edge Start and Reset (MODE<4:0> = 01100)

Falling edge Start and Reset (MODE<4:0> = 01101)

The timer resets and clears the ON bit when the timer value matches the T2PR period value. External signal edges will have no effect until after software sets the ON bit. Figure 24-10 illustrates the rising edge hardware limit one-shot operation.

When this mode is used in conjunction with the CCP then the first starting edge trigger, and all subsequent Reset edges, will activate the PWM drive. The PWM drive will deactivate when the timer matches the CCPRx pulse width value and stay deactivated until the timer halts at the T2PR period match unless an external signal edge resets the timer before the match occurs.

PIC18(L)F24/25K42

FIGURE 24-10: EDGE TRIGGERED HARDWARE LIMIT ONE-SHOT MODE TIMING DIAGRAM (MODE = 01100))

#### 29.1.2 DATA GATING

Outputs from the input multiplexers are directed to the desired logic function input through the data gating stage. Each data gate can direct any combination of the four selected inputs.

**Note:** Data gating is undefined at power-up.

The gate stage is more than just signal direction. The gate can be configured to direct each input signal as inverted or non-inverted data. Directed signals are ANDed together in each gate. The output of each gate can be inverted before going on to the logic function stage.

The gating is in essence a 1-to-4 input AND/NAND/OR/NOR gate. When every input is inverted and the output is inverted, the gate is an OR of all enabled data inputs. When the inputs and output are not inverted, the gate is an AND or all enabled inputs.

Table 29-2 summarizes the basic logic that can be obtained in gate 1 by using the gate logic select bits. The table shows the logic of four input variables, but each gate can be configured to use less than four. If no inputs are selected, the output will be zero or one, depending on the gate output polarity bit.

TABLE 29-2: DATA GATING LOGIC

| CLCxGLSy | GyPOL | Gate Logic |

|----------|-------|------------|

| 0x55     | 1     | AND        |

| 0x55     | 0     | NAND       |

| 0xAA     | 1     | NOR        |

| 0xAA     | 0     | OR         |

| 0x00     | 0     | Logic 0    |

| 0x00     | 1     | Logic 1    |

It is possible (but not recommended) to select both the true and negated values of an input. When this is done, the gate output is zero, regardless of the other inputs, but may emit logic glitches (transient-induced pulses). If the output of the channel must be zero or one, the recommended method is to set all gate bits to zero and use the gate polarity bit to set the desired level.

Data gating is configured with the logic gate select registers as follows:

- Gate 1: CLCxGLS0 (Register 29-18)

- Gate 2: CLCxGLS1 (Register 29-19)

- Gate 3: CLCxGLS2 (Register 29-20)

- Gate 4: CLCxGLS3 (Register 29-21)

Register number suffixes are different than the gate numbers because other variations of this module have multiple gate selections in the same register.

Data gating is indicated in the right side of Figure 29-2. Only one gate is shown in detail. The remaining three gates are configured identically with the exception that the data enables correspond to the enables for that gate.

#### 29.1.3 LOGIC FUNCTION

There are eight available logic functions including:

- AND-OR

- OR-XOR

- AND

- S-R Latch

- · D Flip-Flop with Set and Reset

- · D Flip-Flop with Reset

- · J-K Flip-Flop with Reset

- · Transparent Latch with Set and Reset

Logic functions are shown in Figure 29-2. Each logic function has four inputs and one output. The four inputs are the four data gate outputs of the previous stage. The output is fed to the inversion stage and from there to other peripherals, an output pin, and back to the CLCx itself.

#### 29.1.4 OUTPUT POLARITY

The last stage in the Configurable Logic Cell is the output polarity. Setting the POL bit of the CLCxPOL register inverts the output signal from the logic stage. Changing the polarity while the interrupts are enabled will cause an interrupt for the resulting output transition.

#### REGISTER 33-5: UXERRIE: UART ERROR INTERRUPT ENABLE REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TXMTIE  | PERIE   | ABDOVE  | CERIE   | FERIE   | RXBKIE  | RXFOIE  | TXCIE   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7 | TXMTIE: Transmit Shift Register Empty Interrupt Enable bit |

|-------|------------------------------------------------------------|

|       | 1 = Interrupt enabled                                      |

|       | 0 = Interrupt not enabled                                  |

| bit 6 | PERIE: Parity Error Interrupt Enable bit                   |

|       | 1 = Interrupt enabled                                      |

|       | 0 = Interrupt not enabled                                  |

| bit 5 | ABDOVE: Auto-baud Detect Overflow Interrupt Enable bit     |

|       | 1 = Interrupt enabled                                      |

|       | 0 = Interrupt not enabled                                  |

| bit 4 | CERIE: Checksum Error Interrupt Enable bit                 |

|       | 1 = Interrupt enabled                                      |

|       | 0 = Interrupt not enabled                                  |

| bit 3 | FERIE: Framing Error Interrupt Enable bit                  |

|       | 1 = Interrupt enabled                                      |

|       | 0 = Interrupt not enabled                                  |

| bit 2 | RXBKIE: Break Reception Interrupt Enable bit               |

|       | 1 = Interrupt enabled                                      |

|       | 0 = Interrupt not enabled                                  |

| bit 1 | RXFOIE: Receive FIFO Overflow Interrupt Enable bit         |

|       | 1 = Interrupt enabled                                      |

|       | 0 = Interrupt not enabled                                  |

| bit 0 | TXCIE: Transmit Collision Interrupt Enable bit             |

|       | 1 = Interrupt enabled                                      |

|       | 0 = Interrupt not enabled                                  |

## 34.8.3.4 Receiver Overflow and Transmitter Underflow interrupts.

The receiver overflow interrupt triggers if data is received when the RXFIFO is already full and RXR = 1. In this case, the data will be discarded and the RXOIF bit will be set. The receiver overflow interrupt flag is the RXOIF bit of SPIxINTF. The receiver overflow interrupt enable bit is the RXOIE bit of SPIxINTE.

The Transmitter Underflow interrupt flag triggers if a data transfer begins when the TXFIFO is empty and TXR = 1. In this case, the most recently received data will be transmitted and the TXUIF bit will be set. The transmitter underflow interrupt flag is the TXUIF bit of SPIxINTF. The transmitter underflow interrupt enable bit is the TXUIE bit of SPIxINTE.

Both of these interrupts will only occur in Slave mode, as Master mode will not allow the RXFIFO to overflow or the TXFIFO to underflow.

#### REGISTER 38-6: ADCLK: ADC CLOCK SELECTION REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |  |

|-------|-----|---------|---------|---------|---------|---------|---------|--|--|--|

| _     | _   |         | CS<5:0> |         |         |         |         |  |  |  |

| bit 7 |     |         |         |         |         |         | bit 0   |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-6 **Unimplemented**: Read as '0'

bit 5-0 CS<5:0>: ADC Conversion Clock Select bits

111111 = Fosc/128 111110 = Fosc/126 111101 = Fosc/124

•

•

000000 = Fosc/2

#### REGISTER 38-7: ADREF: ADC REFERENCE SELECTION REGISTER

| U-0   | U-0 | U-0 | R/W-0/0 | U-0 | U-0 | R/W-0/0   | R/W-0/0 |

|-------|-----|-----|---------|-----|-----|-----------|---------|

| _     | _   | _   | NREF    | _   | _   | PREF<1:0> |         |

| bit 7 |     |     |         |     |     |           | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-5 **Unimplemented**: Read as '0'

bit 4 NREF: ADC Negative Voltage Reference Selection bit

1 = VREF- is connected to external VREF-

0 = VREF- is connected to VSS

bit 3-2 **Unimplemented**: Read as '0'

bit 1-0 PREF: ADC Positive Voltage Reference Selection bits

11 = VREF+ is connected to internal Fixed Voltage Reference (FVR) module

10 = VREF+ is connected to external VREF+

01 = Reserved

00 = VREF+ is connected to VDD

#### **REGISTER 38-18: ADRESH: ADC RESULT REGISTER HIGH, FM = 0**

| R/W-x/u     | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |  |  |

|-------------|---------|---------|---------|---------|---------|---------|---------|--|--|--|

| ADRES<11:4> |         |         |         |         |         |         |         |  |  |  |

| bit 7       |         |         |         |         |         |         | bit 0   |  |  |  |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

bit 7-0 **ADRES<11:4>**: ADC Result Register bits Upper eight bits of 12-bit conversion result.

#### REGISTER 38-19: ADRESL: ADC RESULT REGISTER LOW, FM = 0

| R/W-x/u R/W-x/u R/W-x/u |  |  |  | U-0 | U-0 | U-0 | U-0   |

|-------------------------|--|--|--|-----|-----|-----|-------|

| ADRES<3:0>              |  |  |  | _   | _   | _   | _     |

| bit 7                   |  |  |  |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 ADRES<3:0>: ADC Result Register bits. Lower four bits of 12-bit conversion result.

bit 3-0 Reserved

#### BRA Unconditional Branch

Syntax: BRA n

Operands:  $-1024 \le n \le 1023$ Operation:  $(PC) + 2 + 2n \rightarrow PC$

Status Affected: None

Encoding: 1101 Onnn nnnn nnnn

Description: Add the 2's complement number '2n' to

the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 2 + 2n. This instruction is a 2-cycle instruction.

Words: 1 Cycles: 2

Q Cycle Activity:

|   | Q1                  | Q2           | Q3        | Q4          |  |

|---|---------------------|--------------|-----------|-------------|--|

| ſ | Decode              | Read literal | Process   | Write to PC |  |

| L |                     | ʻn'          | Data      |             |  |

| ſ | No                  | No           | No        | No          |  |

| L | operation operation |              | operation | operation   |  |

Example: HERE BRA Jump

Before Instruction

PC = address (HERE)

After Instruction

PC = address (Jump)

| Syntax: BSF f, b {,a}  Operands: $0 \le f \le 255$ $0 \le b \le 7$ $a \in [0,1]$ Operation: $1 \to f < b >$ Status Affected: None  Encoding: $1000$ bbba fffff ffff | BSF              | Bit Set f               |      |      |      |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------|------|------|------|--|--|

| $0 \le b \le 7$ $a \in [0,1]$ Operation: $1 \to f < b >$ Status Affected: None                                                                                      | Syntax:          | BSF f, b {,a}           |      |      |      |  |  |

| Status Affected: None                                                                                                                                               | Operands:        | $0 \le b \le 7$         |      |      |      |  |  |

|                                                                                                                                                                     | Operation:       | $1 \rightarrow f < b >$ |      |      |      |  |  |

| Encoding: 1000 bbba ffff ffff                                                                                                                                       | Status Affected: | None                    |      |      |      |  |  |

|                                                                                                                                                                     | Encoding:        | 1000                    | bbba | ffff | ffff |  |  |

Description: Bit 'b' in register 'f' is set.

If 'a' is '0', the Access Bank is selected. If 'a' is '1', the BSR is used to select the

GPR bank.

If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever f ≤ 95 (5Fh). See Section 43.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode" for details.

Words: 1

Cycles: 1

Q Cycle Activity:

| Q1         | Q2   | Q3      | Q4           |  |

|------------|------|---------|--------------|--|

| Decode     | Read | Process | Write        |  |

| register " |      | Data    | register 'f' |  |

Example: BSF FLAG REG, 7, 1

Before Instruction

FLAG\_REG = 0Ah

After Instruction

FLAG\_REG = 8Ah

#### XORWF Exclusive OR W with f

Syntax: XORWF f {,d {,a}}

$0 \le f \le 255$   $d \in [0,1]$  $a \in [0,1]$

Operation: (W) .XOR. (f)  $\rightarrow$  dest

Status Affected: N, Z

Operands:

Encoding: 0001 10da ffff ffff

Description: Exclusive OR the contents of W with

register 'f'. If 'd' is '0', the result is stored in W. If 'd' is '1', the result is stored back

in the register 'f' (default).

If 'a' is '0', the Access Bank is selected. If 'a' is '1', the BSR is used to select the

GPR bank.

If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever  $f \le 95$  (5Fh). See Section 43.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode" for details.

Words: 1 Cycles: 1

Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4          |  |

|--------|--------------|---------|-------------|--|

| Decode | Read         | Process | Write to    |  |

|        | register 'f' | Data    | destination |  |

Example: XORWF REG, 1, 0

Before Instruction

REG = AFh W = B5h

After Instruction

REG = 1AhW = B5h

#### 45.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- · Flexible macro language

- · MPLAB X IDE compatibility

#### 45.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel® standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

## 45.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 45.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- · Flexible macro language

- · MPLAB X IDE compatibility

## 45.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM™ and dsPICDEM™ demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELoQ® security ICs, CAN, IrDA®, PowerSmart battery management, SEEVAL® evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

#### 45.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

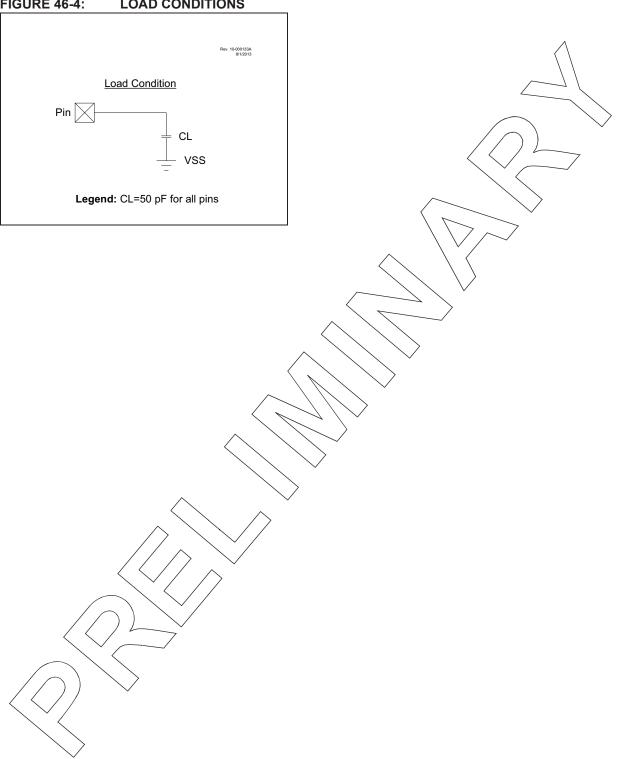

#### 46.4 **AC Characteristics**

LOAD CONDITIONS **FIGURE 46-4:**

TABLE 46-8: INTERNAL OSCILLATOR PARAMETERS(1)

| Standar      | Standard Operating Conditions (unless otherwise stated) |                                                 |              |                                |              |                          |            |  |

|--------------|---------------------------------------------------------|-------------------------------------------------|--------------|--------------------------------|--------------|--------------------------|------------|--|

| Param<br>No. | Sym.                                                    | Characteristic                                  | Min.         | Тур†                           | Max.         | Units                    | Conditions |  |

| OS50         | FHFOSC                                                  | Precision Calibrated HFINTOSC Frequency         | _            | 4<br>8<br>12<br>16<br>48<br>64 | _            | MHz                      | (Note 2)   |  |

| OS51         | FHFOSCLP                                                | Low-Power Optimized HFINTOSC Frequency          | 0.93<br>1.86 | 1<br>2                         | 1.07<br>2.14 | MHz<br>MHz               |            |  |

| OS53*        | FLFOSC                                                  | Internal LFINTOSC Frequency                     | _            | 31                             | _            | kHz                      |            |  |

| OS54*        | THFOSCST                                                | HFINTOSC<br>Wake-up from Sleep Start-up<br>Time | _            | 11<br>50                       | 20<br>—      | μ <b>S</b><br>μ <b>S</b> | VREGPM = 1 |  |

| OS56         | TLFOSCST                                                | LFINTOSC<br>Wake-up from Sleep Start-up Time    | _            | 0.2                            | _            | ms                       |            |  |

- These parameters are characterized but not tested.

- † Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- **Note 1:** To ensure these oscillator frequency tolerances, VDD and VSS must be capacitively decoupled as close to the device as possible.  $0.1~\mu F$  and  $0.01~\mu F$  values in parallel are recommended.

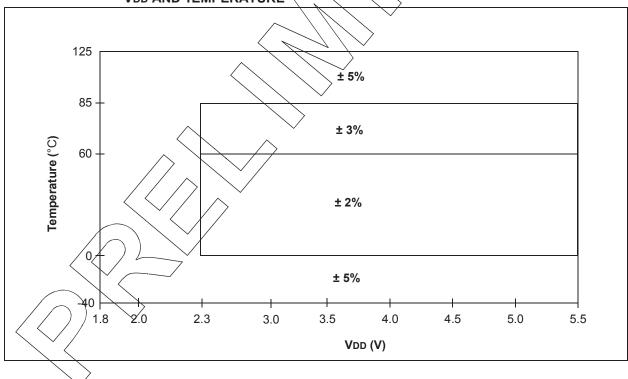

- 2: See Figure 46-6: Precision Calibrated HFINTOSC Frequency Accuracy Over Device VDD and Temperature.

FIGURE 46-6: PRECISION CALIBRATED HEINTOSC FREQUENCY ACCURACY OVER DEVICE VDD AND TEMPERATURE