Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Dectano                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 64MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                             |

| Number of I/O              | 25                                                                           |

| Program Memory Size        | 32KB (16K x 16)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 256 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

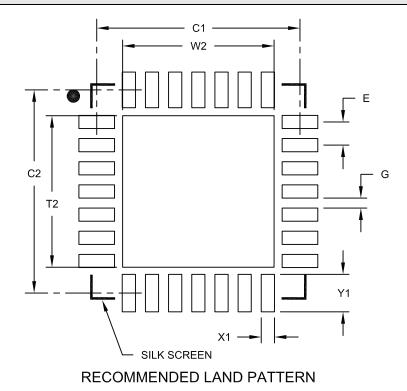

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 28-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf25k42t-i-so |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

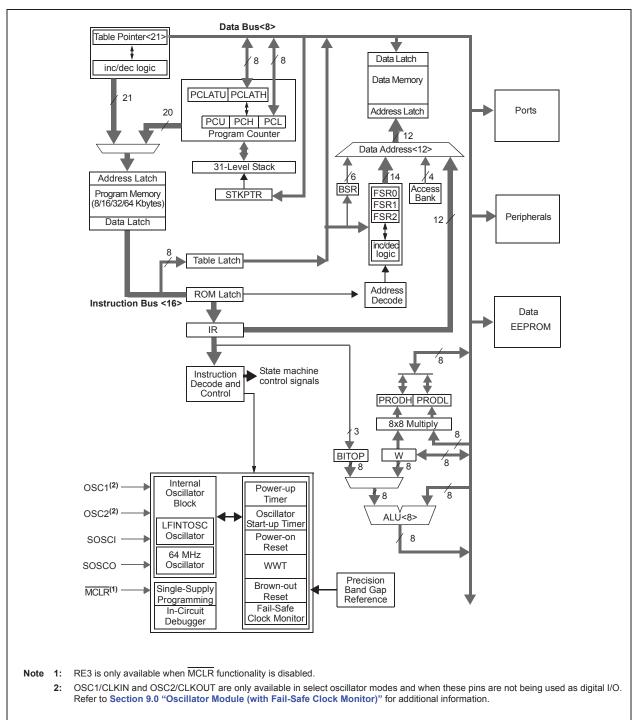

#### FIGURE 3-1: PIC18(L)F24/25K42 FAMILY BLOCK DIAGRAM

# PIC18(L)F24/25K42

# REGISTER 3-4: DMA2PR: DMA2 PRIORITY REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-1/1 | R/W-1/1 |

|-------|-----|-----|-----|-----|---------|---------|---------|

| —     | —   | —   | —   | —   | DMA2PR2 | DMA2PR1 | DMA2PR0 |

| bit 7 |     |     |     |     |         |         | bit 0   |

#### Legend:

| R = Readable bit     | W = Writable bit   | U = Unimplemented bit, read as '0'                    |

|----------------------|--------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown | -n/n = Value at POR and BOR/Value at all other Resets |

| 1 = bit is set       | 0 = bit is cleared | HS = Hardware set                                     |

#### bit 7-3 Unimplemented: Read as '0'

bit 2-0 DMA2PR<2:0>: DMA2 Priority Selection bits

#### REGISTER 3-5: SCANPR: SCANNER PRIORITY REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-1/1 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|-----|---------|---------|---------|

| —     | —   | —   | —   | —   | SCANPR2 | SCANPR1 | SCANPR0 |

| bit 7 |     |     |     |     |         |         | bit 0   |

| Legend:              |                    |                                                       |

|----------------------|--------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit   | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown | -n/n = Value at POR and BOR/Value at all other Resets |

| 1 = bit is set       | 0 = bit is cleared | HS = Hardware set                                     |

#### bit 7-3 Unimplemented: Read as '0'

bit 2-0 SCANPR<2:0>: DMA2 Priority Selection bits

# REGISTER 3-6: PRLOCK: PRIORITY LOCK REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0  |

|-------|-----|-----|-----|-----|-----|-----|----------|

| —     | —   | —   | —   | —   | —   | —   | PRLOCKED |

| bit 7 |     |     |     |     |     |     | bit 0    |

| Legend:              |                    |                                                       |

|----------------------|--------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit   | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown | -n/n = Value at POR and BOR/Value at all other Resets |

| 1 = bit is set       | 0 = bit is cleared | HS = Hardware set                                     |

bit 7-1 Unimplemented: Read as '0'

bit 0 **PRLOCKED**: PR Register Lock bit<sup>(1, 2)</sup>

0 = Priority Registers can be modified by write operations; Peripherals do not have access to the memory

1 = Priority Registers are locked and cannot be written; Peripherals do not have access to the memory

Note 1: The PRLOCKED bit can only be set or cleared after the unlock sequence.

2: If PR1WAY = 1, the PRLOCKED bit cannot be cleared after it has been set. A system Reset will clear the bit and allow one more set.

#### **TABLE 4-5**: SPECIAL FUNCTION REGISTER MAP FOR PIC18(L)F24/25K42 DEVICES BANK 61

| © 2016-20  |  |

|------------|--|

| 017        |  |

| Microchip  |  |

| Technology |  |

| Inc.       |  |

| 3DFFh   | _         | 3DDFh      | U2FIFO          | 3DBFh      | —                     | 3D9Fh | _ | 3D7Fh | —         | 3D5Fh | I2C2CON2 | 3D3Fh | _ | 3D1Fh | —          |

|---------|-----------|------------|-----------------|------------|-----------------------|-------|---|-------|-----------|-------|----------|-------|---|-------|------------|

| 3DFEh   | —         | 3DDEh      | U2BRGH          | 3DBEh      | —                     | 3D9Eh |   | 3D7Eh | —         | 3D5Eh | I2C2CON1 | 3D3Eh | — | 3D1Eh | —          |

| 3DFDh   | —         | 3DDDh      | U2BRGL          | 3DBDh      | —                     | 3D9Dh | — | 3D7Dh | —         | 3D5Dh | I2C2CON0 | 3D3Dh | — | 3D1Dh | —          |

| 3DFCh   | —         | 3DDCh      | U2CON2          | 3DBCh      | —                     | 3D9Ch | — | 3D7Ch | I2C1BTO   | 3D5Ch | I2C2ADR3 | 3D3Ch | — | 3D1Ch | SPI1CLK    |

| 3DFBh   | —         | 3DDBh      | U2CON1          | 3DBBh      | —                     | 3D9Bh | — | 3D7Bh | I2C1CLK   | 3D5Bh | I2C2ADR2 | 3D3Bh | — | 3D1Bh | SPI1INTE   |

| 3DFAh   | U1ERRIE   | 3DDAh      | U2CON0          | 3DBAh      | —                     | 3D9Ah | — | 3D7Ah | I2C1PIE   | 3D5Ah | I2C2ADR1 | 3D3Ah | — | 3D1Ah | SPI1INTF   |

| 3DF9h   | U1ERRIR   | 3DD9h      | —               | 3DB9h      | —                     | 3D99h | — | 3D79h | I2C1PIR   | 3D59h | I2C2ADR0 | 3D39h | — | 3D19h | SPI1BAUD   |

| 3DF8h   | U1UIR     | 3DD8h      | U2P3L           | 3DB8h      | —                     | 3D98h | — | 3D78h | I2C1STAT1 | 3D58h | I2C2ADB1 | 3D38h | — | 3D18h | SPI1TWIDTH |

| 3DF7h   | U1FIFO    | 3DD7h      | —               | 3DB7h      | —                     | 3D97h | — | 3D77h | I2C1STAT0 | 3D57h | I2C2ADB0 | 3D37h | — | 3D17h | SPI1STATUS |

| 3DF6h   | U1BRGH    | 3DD6h      | U2P2L           | 3DB6h      | —                     | 3D96h | — | 3D76h | I2C1ERR   | 3D56h | I2C2CNT  | 3D36h | — | 3D16h | SPI1CON2   |

| 3DF5h   | U1BRGL    | 3DD5h      | —               | 3DB5h      | —                     | 3D95h | — | 3D75h | I2C1CON2  | 3D55h | I2C2TXB  | 3D35h | — | 3D15h | SPI1CON1   |

| 3DF4h   | U1CON2    | 3DD4h      | U2P1L           | 3DB4h      | —                     | 3D94h | — | 3D74h | I2C1CON1  | 3D54h | I2C2RXB  | 3D34h | — | 3D14h | SPI1CON0   |

| 3DF3h   | U1CON1    | 3DD3h      | _               | 3DB3h      | —                     | 3D93h | _ | 3D73h | I2C1CON0  | 3D53h | _        | 3D33h | _ | 3D13h | SPI1TCNTH  |

| 3DF2h   | U1CON0    | 3DD2h      | U2TXB           | 3DB2h      | —                     | 3D92h | — | 3D72h | I2C1ADR3  | 3D52h | —        | 3D32h | — | 3D12h | SPI1TCNTL  |

| 3DF1h   | U1P3H     | 3DD1h      | —               | 3DB1h      | —                     | 3D91h | — | 3D71h | I2C1ADR2  | 3D51h | —        | 3D31h | — | 3D11h | SPI1TXB    |

| 3DF0h   | U1P3L     | 3DD0h      | U2RXB           | 3DB0h      | —                     | 3D90h | — | 3D70h | I2C1ADR1  | 3D50h | —        | 3D30h | — | 3D10h | SPI1RXB    |

| 3DEFh   | U1P2H     | 3DCFh      | —               | 3DAFh      | —                     | 3D8Fh | — | 3D6Fh | I2C1ADR0  | 3D4Fh | —        | 3D2Fh | — | 3D0Fh | —          |

| 3DEEh   | U1P2L     | 3DCEh      | —               | 3DAEh      | —                     | 3D8Eh | — | 3D6Eh | I2C1ADB1  | 3D4Eh | —        | 3D2Eh | — | 3D0Eh | —          |

| 3DEDh   | U1P1H     | 3DCDh      | —               | 3DADh      | —                     | 3D8Dh | — | 3D6Dh | I2C1ADB0  | 3D4Dh | —        | 3D2Dh | — | 3D0Dh | —          |

| 3DECh   | U1P1L     | 3DCCh      | —               | 3DACh      | —                     | 3D8Ch | — | 3D6Ch | I2C1CNT   | 3D4Ch | —        | 3D2Ch | — | 3D0Ch | —          |

| 3DEBh   | U1TXCHK   | 3DCBh      | —               | 3DABh      | —                     | 3D8Bh | — | 3D6Bh | I2C1TXB   | 3D4Bh | —        | 3D2Bh | — | 3D0Bh | —          |

| 3DEAh   | U1TXB     | 3DCAh      | —               | 3DAAh      | —                     | 3D8Ah | — | 3D6Ah | I2C1RXB   | 3D4Ah | —        | 3D2Ah | — | 3D0Ah | —          |

| 3DE9h   | U1RXCHK   | 3DC9h      | —               | 3DA9h      | —                     | 3D89h | — | 3D69h | —         | 3D49h | —        | 3D29h | — | 3D09h | —          |

| 3DE8h   | U1RXB     | 3DC8h      | —               | 3DA8h      | —                     | 3D88h | — | 3D68h | —         | 3D48h | —        | 3D28h | — | 3D08h | —          |

| 3DE7h   | —         | 3DC7h      | —               | 3DA7h      | —                     | 3D87h | — | 3D67h | —         | 3D47h | —        | 3D27h | — | 3D07h | —          |

| 3DE6h   | —         | 3DC6h      | —               | 3DA6h      | —                     | 3D86h | — | 3D66h | I2C2BTO   | 3D46h | —        | 3D26h | — | 3D06h | —          |

| 3DE5h   | —         | 3DC5h      | —               | 3DA5h      | —                     | 3D85h | — | 3D65h | I2C2CLK   | 3D45h | —        | 3D25h | — | 3D05h | —          |

| 3DE4h   | —         | 3DC4h      | —               | 3DA4h      | —                     | 3D84h | — | 3D64h | I2C2PIE   | 3D44h | —        | 3D24h | — | 3D04h | —          |

| 3DE3h   | _         | 3DC3h      | _               | 3DA3h      | —                     | 3D83h | _ | 3D63h | I2C2PIR   | 3D43h |          | 3D23h | — | 3D03h | —          |

| 3DE2h   | U2ERRIE   | 3DC2h      |                 | 3DA2h      | —                     | 3D82h |   | 3D62h | I2C2STAT1 | 3D42h |          | 3D22h | — | 3D02h | —          |

| 3DE1h   | U2ERRIR   | 3DC1h      |                 | 3DA1h      | —                     | 3D81h |   | 3D61h | I2C2STAT0 | 3D41h |          | 3D21h | — | 3D01h | —          |

| 3DE0h   | U2UIR     | 3DC0h      | _               | 3DA0h      | —                     | 3D80h | _ | 3D60h | I2C2ERR   | 3D40h | _        | 3D20h | — | 3D00h | —          |

| _eaend: | Unimpleme | ented data | memory location | ns and red | disters, read as '0'. |       |   |       |           | · -   |          |       |   |       |            |

Legend: Unimplemented data memory locations and registers, read as '0'.

# TABLE 4-8: SPECIAL FUNCTION REGISTER MAP FOR PIC18(L)F24/25K42 DEVICES BANK 58

| -     |            |       |                  |            |                     |       |        |       |         |       |         |       |   |       |        |

|-------|------------|-------|------------------|------------|---------------------|-------|--------|-------|---------|-------|---------|-------|---|-------|--------|

| 3AFFh | —          | 3ADFh | SPI1SDIPPS       | 3ABFh      | PPSLOCK             | 3A9Fh | —      | 3A7Fh | —       | 3A5Fh | —       | 3A3Fh | — | 3A1Fh | —      |

| 3AFEh | _          | 3ADEh | SPI1SCKPPS       | 3ABEh      | CCDCON              | 3A9Eh | _      | 3A7Eh | _       | 3A5Eh | _       | 3A3Eh | _ | 3A1Eh | —      |

| 3AFDh | —          | 3ADDh | ADACTPPS         | 3ABDh      | —                   | 3A9Dh | —      | 3A7Dh | —       | 3A5Dh | —       | 3A3Dh | — | 3A1Dh | —      |

| 3AFCh | —          | 3ADCh | CLCIN3PPS        | 3ABCh      | —                   | 3A9Ch | —      | 3A7Ch | —       | 3A5Ch | —       | 3A3Ch | — | 3A1Ch | —      |

| 3AFBh | —          | 3ADBh | CLCIN2PPS        | 3ABBh      | —                   | 3A9Bh | —      | 3A7Bh | —       | 3A5Bh | RB2I2C  | 3A3Bh | — | 3A1Bh | —      |

| 3AFAh | —          | 3ADAh | CLCIN1PPS        | 3ABAh      | —                   | 3A9Ah | —      | 3A7Ah | —       | 3A5Ah | RB1I2C  | 3A3Ah | — | 3A1Ah | —      |

| 3AF9h | —          | 3AD9h | <b>CLCIN0PPS</b> | 3AB9h      | —                   | 3A99h | —      | 3A79h | —       | 3A59h | CCDNB   | 3A39h | — | 3A19h | —      |

| 3AF8h | —          | 3AD8h | MD1SRCPPS        | 3AB8h      | —                   | 3A98h | —      | 3A78h | —       | 3A58h | CCDPB   | 3A38h | — | 3A18h | —      |

| 3AF7h | —          | 3AD7h | MD1CARHPPS       | 3AB7h      | —                   | 3A97h | —      | 3A77h | —       | 3A57h | IOCBF   | 3A37h | — | 3A17h | RC7PPS |

| 3AF6h | —          | 3AD6h | MD1CARLPPS       | 3AB6h      | —                   | 3A96h | —      | 3A76h | —       | 3A56h | IOCBN   | 3A36h | — | 3A16h | RC6PPS |

| 3AF5h | —          | 3AD5h | CWG3INPPS        | 3AB5h      | —                   | 3A95h | —      | 3A75h | —       | 3A55h | IOCBP   | 3A35h | — | 3A15h | RC5PPS |

| 3AF4h | —          | 3AD4h | CWG2INPPS        | 3AB4h      | —                   | 3A94h | —      | 3A74h | —       | 3A54h | INLVLB  | 3A34h | — | 3A14h | RC4PPS |

| 3AF3h | —          | 3AD3h | CWG1INPPS        | 3AB3h      | —                   | 3A93h | —      | 3A73h | —       | 3A53h | SLRCONB | 3A33h | — | 3A13h | RC3PPS |

| 3AF2h | —          | 3AD2h | SMT1SIGPPS       | 3AB2h      | —                   | 3A92h | —      | 3A72h | —       | 3A52h | ODCONB  | 3A32h | — | 3A12h | RC2PPS |

| 3AF1h | —          | 3AD1h | SMT1WINPPS       | 3AB1h      | —                   | 3A91h | —      | 3A71h | —       | 3A51h | WPUB    | 3A31h | — | 3A11h | RC1PPS |

| 3AF0h | —          | 3AD0h | CCP4PPS          | 3AB0h      | —                   | 3A90h | —      | 3A70h | —       | 3A50h | ANSELB  | 3A30h | — | 3A10h | RC0PPS |

| 3AEFh | —          | 3ACFh | CCP3PPS          | 3AAFh      | —                   | 3A8Fh | —      | 3A6Fh | —       | 3A4Fh | —       | 3A2Fh | — | 3A0Fh | RB7PPS |

| 3AEEh | —          | 3ACEh | CCP2PPS          | 3AAEh      | —                   | 3A8Eh | —      | 3A6Eh | —       | 3A4Eh | —       | 3A2Eh | — | 3A0Eh | RB6PPS |

| 3AEDh | —          | 3ACDh | CCP1PPS          | 3AADh      | —                   | 3A8Dh | —      | 3A6Dh | —       | 3A4Dh | —       | 3A2Dh | — | 3A0Dh | RB5PPS |

| 3AECh | —          | 3ACCh | T6INPPS          | 3AACh      | —                   | 3A8Ch | —      | 3A6Ch | —       | 3A4Ch | —       | 3A2Ch | — | 3A0Ch | RB4PPS |

| 3AEBh | —          | 3ACBh | T4INPPS          | 3AABh      | —                   | 3A8Bh | —      | 3A6Bh | RC4I2C  | 3A4Bh | —       | 3A2Bh | — | 3A0Bh | RB3PPS |

| 3AEAh | —          | 3ACAh | T2INPPS          | 3AAAh      | —                   | 3A8Ah | —      | 3A6Ah | RC3I2C  | 3A4Ah | —       | 3A2Ah | — | 3A0Ah | RB2PPS |

| 3AE9h | U2CTSPPS   | 3AC9h | T5GPPS           | 3AA9h      | —                   | 3A89h | —      | 3A69h | CCDNC   | 3A49h | CCDNA   | 3A29h | — | 3A09h | RB1PPS |

| 3AE8h | U2RXPPS    | 3AC8h | T5CKIPPS         | 3AA8h      | —                   | 3A88h | —      | 3A68h | CCDPC   | 3A48h | CCDPA   | 3A28h | — | 3A08h | RB0PPS |

| 3AE7h | —          | 3AC7h | T3GPPS           | 3AA7h      | —                   | 3A87h | IOCEF  | 3A67h | IOCCF   | 3A47h | IOCAF   | 3A27h | — | 3A07h | RA7PPS |

| 3AE6h | U1CTSPPS   | 3AC6h | T3CKIPPS         | 3AA6h      | —                   | 3A86h | IOCEN  | 3A66h | IOCCN   | 3A46h | IOCAN   | 3A26h | — | 3A06h | RA6PPS |

| 3AE5h | U1RXPPS    | 3AC5h | T1GPPS           | 3AA5h      | —                   | 3A85h | IOCEP  | 3A65h | IOCCP   | 3A45h | IOCAP   | 3A25h | — | 3A05h | RA5PPS |

| 3AE4h | I2C2SDAPPS | 3AC4h | T1CKIPPS         | 3AA4h      | —                   | 3A84h | INLVLE | 3A64h | INLVLC  | 3A44h | INLVLA  | 3A24h | — | 3A04h | RA4PPS |

| 3AE3h | I2C2SCLPPS | 3AC3h | <b>T0CKIPPS</b>  | 3AA3h      | —                   | 3A83h | —      | 3A63h | SLRCONC | 3A43h | SLRCONA | 3A23h | — | 3A03h | RA3PPS |

| 3AE2h | I2C1SDAPPS | 3AC2h | INT2PPS          | 3AA2h      | —                   | 3A82h | —      | 3A62h | ODCONC  | 3A42h | ODCONA  | 3A22h |   | 3A02h | RA2PPS |

| 3AE1h | I2C1SCLPPS | 3AC1h | INT1PPS          | 3AA1h      | —                   | 3A81h | WPUE   | 3A61h | WPUC    | 3A41h | WPUA    | 3A21h |   | 3A01h | RA1PPS |

| 3AE0h | SPI1SSPPS  | 3AC0h | INT0PPS          | 3AA0h      | —                   | 3A80h | —      | 3A60h | ANSELC  | 3A40h | ANSELA  | 3A20h | _ | 3A00h | RA0PPS |

|       | L L - C L  |       | momonylocations  | and an air | teres in a dise tot |       |        |       |         |       |         |       |   |       |        |

Legend: Unimplemented data memory locations and registers, read as '0'.

| Address          | Name              | Bit 7         | Bit 6  | Bit 5  | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | <u>Value on</u><br>POR, BOR |

|------------------|-------------------|---------------|--------|--------|---------|---------|--------|--------|--------|-----------------------------|

| 3967h            | CRCXORH           | X15           | X14    | X13    | X12     | X11     | X10    | X9     | X8     | XXXXXXXX                    |

| 3966h            | CRCXORL           | X7            | X6     | X5     | X4      | X3      | X2     | X1     | —      | xxxxxxx1                    |

| 3965h            | CRCSHIFTH         | SHFT15        | SHFT14 | SHFT13 | SHFT12  | SHFT11  | SHFT10 | SHFT9  | SHFT8  | 00000000                    |

| 3964h            | CRCSHIFTL         | SHFT7         | SHFT6  | SHFT5  | SHFT4   | SHFT3   | SHFT2  | SHFT1  | SHFT0  | 00000000                    |

| 3963h            | CRCACCH           | ACC15         | ACC14  | ACC13  | ACC12   | ACC11   | ACC10  | ACC9   | ACC8   | 00000000                    |

| 3962h            | CRCACCL           | ACC7          | ACC6   | ACC5   | ACC4    | ACC3    | ACC2   | ACC1   | ACC0   | 00000000                    |

| 3961h            | CRCDATH           | DATA15        | DATA14 | DATA13 | DATA12  | DATA11  | DATA10 | DATA9  | DATA8  | XXXXXXXX                    |

| 3960h            | CRCDATL           | DATA7         | DATA6  | DATA5  | DATA4   | DATA3   | DATA2  | DATA1  | DATA0  | XXXXXXXX                    |

| 395Fh            | WDTTMR            |               |        | WDTTMR | •       |         | STATE  | PS     | SCNT   | 00000000                    |

| 395Eh            | WDTPS             |               |        |        | PSG     | CNT     |        |        |        | 00000000                    |

| 395Dh            | WDTPS             |               |        |        | PSG     | CNT     |        |        |        | 00000000                    |

| 395Ch            | WDTCON1           | _             |        | CS     |         | —       |        | WINDOW |        | -000-000                    |

| 395Bh            | WDTCON0           | _             | _      |        |         | PS      |        |        | SEN    | ddddd0                      |

| 395Ah -<br>38A0h | —                 |               | I      | 1      | Unimple | emented |        |        |        | -                           |

| 389Fh            | IVTADU            |               | AD     |        |         |         |        |        |        |                             |

| 389Eh            | IVTADH            | AD            |        |        |         |         |        |        |        | XXXXXXXX                    |

| 389Dh            | IVTADL            | AD            |        |        |         |         |        |        |        | XXXXXXXX                    |

| 389Ch -<br>3891h | —                 | Unimplemented |        |        |         |         |        |        |        | -                           |

| 3890h            | PRODH_SHAD        |               | PRODH  |        |         |         |        |        |        |                             |

| 388Fh            | PRODL_SHAD        |               |        |        | PRO     | DDL     |        |        |        | XXXXXXXX                    |

| 388Eh            | FSR2H_SHAD        | _             | —      |        |         | F       | SR2H   |        |        | 000000                      |

| 388Dh            | FSR2L_SHAD        |               | •      |        | FSI     | R2L     |        |        |        | 00000000                    |

| 388Ch            | FSR1H_SHAD        | _             | —      |        |         | F       | SR1H   |        |        | 000000                      |

| 388Bh            | FSR1L_SHAD        |               | •      |        | FSI     | R1L     |        |        |        | 00000000                    |

| 388Ah            | FSR0H_SHAD        | _             | _      |        |         | F       | SR0H   |        |        | 000000                      |

| 3889h            | FSR0L_SHAD        |               |        |        | FSI     | ROL     |        |        |        | 00000000                    |

| 3888h            | PCLATU<br>SHAD    | —             | —      | —      |         |         | PCU    |        |        | 00000                       |

| 3887h            | PCLATH<br>SHAD    |               | L      | I      | PC      | СН      |        |        |        | 00000000                    |

| 3886h            | BSR_SHAD          | _             | _      |        |         |         | BSR    |        |        | 000000                      |

| 3885h            | WREG_SHAD         |               | I      |        | WR      | EG      |        |        |        | XXXXXXXX                    |

| 3884h            | STATUS<br>SHAD    | —             | TO     | PD     | N       | OV      | Z      | DC     | С      | -1100000                    |

| 3883h            | SHADCON           | _             | _      | —      | _       | _       | —      | _      | SHADLO | 0                           |

| 3882h            | BSR_CSHAD         | _             | — BSR  |        |         |         |        |        |        | 000000                      |

| 3881h            | WREG_C-<br>SHAD   |               |        |        | WR      | EG      |        |        |        | *****                       |

| 3880h            | STATUS_C-<br>SHAD | _             | TO     | PD     | Ν       | OV      | Z      | DC     | С      | -1100000                    |

| 387Fh -<br>3800h | —                 | Unimplemented |        |        |         |         |        |        | —      |                             |

| TABLE 4-11: | REGISTER FILE SUMMARY FOR PIC18(L)F24/25K42 DEVICES (CONTINUED) |

|-------------|-----------------------------------------------------------------|

|             |                                                                 |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition

Note 1: Not present in LF devices.

# 10.1 Clock Source

The input to the reference clock output can be selected using the CLKRCLK register.

#### 10.1.1 CLOCK SYNCHRONIZATION

Once the reference clock enable (EN) is set, the module is ensured to be glitch-free at start-up.

When the reference clock output is disabled, the output signal will be disabled immediately.

Clock dividers and clock duty cycles can be changed while the module is enabled, but glitches may occur on the output. To avoid possible glitches, clock dividers and clock duty cycles should be changed only when the CLKREN is clear.

# **10.2 Programmable Clock Divider**

The module takes the clock input and divides it based on the value of the DIV<2:0> bits of the CLKRCON register (Register 10-1).

The following configurations can be made based on the DIV<2:0> bits:

- · Base Fosc value

- · Fosc divided by 2

- Fosc divided by 4

- Fosc divided by 8

- Fosc divided by 16

- Fosc divided by 32

- Fosc divided by 64

- Fosc divided by 128

The clock divider values can be changed while the module is enabled; however, in order to prevent glitches on the output, the DIV<2:0> bits should only be changed when the module is disabled (EN = 0).

# 10.3 Selectable Duty Cycle

The DC<1:0> bits of the CLKRCON register can be used to modify the duty cycle of the output clock. A duty cycle of 25%, 50%, or 75% can be selected for all clock rates, with the exception of the undivided base Fosc value.

The duty cycle can be changed while the module is enabled; however, in order to prevent glitches on the output, the DC<1:0> bits should only be changed when the module is disabled (EN = 0).

**Note:** The DC1 bit is reset to '1'. This makes the default duty cycle 50% and not 0%.

# 10.4 Operation in Sleep Mode

The reference clock output module clock is based on the system clock. When the device goes to Sleep, the module outputs will remain in their current state. This will have a direct effect on peripherals using the reference clock output as an input signal. No change should occur in the module from entering or exiting from Sleep.

| R-0/0                                   | R-0/0          | U-0 | U-0                                                   | U-0                            | U-0 | U-0 | U-0   |  |

|-----------------------------------------|----------------|-----|-------------------------------------------------------|--------------------------------|-----|-----|-------|--|

| STAT<1:0>                               |                | —   | —                                                     | —                              | —   | —   | —     |  |

| bit 7                                   |                |     |                                                       |                                |     |     | bit 0 |  |

|                                         |                |     |                                                       |                                |     |     |       |  |

| Legend:                                 |                |     |                                                       |                                |     |     |       |  |

| HC = Bit is clea                        | ared by hardwa | ire |                                                       |                                |     |     |       |  |

| R = Readable bit W = Writable bit       |                | bit | U = Unimplemented bit, read as '0'                    |                                |     |     |       |  |

| u = Bit is unchanged x = Bit is unknown |                | own | -n/n = Value at POR and BOR/Value at all other Resets |                                |     |     |       |  |

| '1' = Bit is set '0' = Bit is cleared   |                |     | ared                                                  | q = Value depends on condition |     |     |       |  |

#### REGISTER 11-2: INTCON1: INTERRUPT CONTROL REGISTER 1

#### bit 7-6 STAT<1:0>: Interrupt State Status bits

11 =High priority ISR executing, high priority interrupt was received while a low priority ISR was executing

10 =High priority ISR executing, high priority interrupt was received in main routine

01 =Low priority ISR executing, low priority interrupt was received in main routine

00 = Main routine executing

bit 5-0 **Unimplemented**: Read as '0'

# 14.0 8x8 HARDWARE MULTIPLIER

# 14.1 Introduction

All PIC18 devices include an 8x8 hardware multiplier as part of the ALU. The multiplier performs an unsigned operation and yields a 16-bit result that is stored in the product register pair, PRODH:PRODL. The multiplier's operation does not affect any flags in the STATUS register.

Making multiplication a hardware operation allows it to be completed in a single instruction cycle. This has the advantages of higher computational throughput and reduced code size for multiplication algorithms and allows the PIC18 devices to be used in many applications previously reserved for digital signal processors. A comparison of various hardware and software multiply operations, along with the savings in memory and execution time, is shown in Table 14-1.

# 14.2 Operation

Example 14-1 shows the instruction sequence for an 8x8 unsigned multiplication. Only one instruction is required when one of the arguments is already loaded in the WREG register.

Example 14-2 shows the sequence to do an 8x8 signed multiplication. To account for the sign bits of the arguments, each argument's Most Significant bit (MSb) is tested and the appropriate subtractions are done.

#### EXAMPLE 14-1: 8x8 UNSIGNED MULTIPLY ROUTINE

| MOVF  | ARG1, | W | ; |       |     |       |    |

|-------|-------|---|---|-------|-----|-------|----|

| MULWF | ARG2  |   | ; | ARG1  | *   | ARG2  | -> |

|       |       |   | ; | PRODE | 1:1 | PRODL |    |

|       |       |   |   |       |     |       |    |

# EXAMPLE 14-2: 8x8 SIGNED MULTIPLY

|       |          | R | JUTINE         |

|-------|----------|---|----------------|

| MOVF  | ARG1, W  |   |                |

| MULWF | ARG2     | ; | ARG1 * ARG2 -> |

|       |          | ; | PRODH:PRODL    |

| BTFSC | ARG2, SB | ; | Test Sign Bit  |

| SUBWF | PRODH, F | ; | PRODH = PRODH  |

|       |          | ; | - ARG1         |

| MOVF  | ARG2, W  |   |                |

| BTFSC | ARG1, SB | ; | Test Sign Bit  |

| SUBWF | PRODH, F | ; | PRODH = PRODH  |

|       |          | ; | - ARG2         |

|       |          |   |                |

|                |                           | Program           | Cycles | Time     |          |          |         |  |

|----------------|---------------------------|-------------------|--------|----------|----------|----------|---------|--|

| Routine        | Multiply Method           | Memory<br>(Words) | (Max)  | @ 64 MHz | @ 40 MHz | @ 10 MHz | @ 4 MHz |  |

| 9v9 uppigpod   | Without hardware multiply | 13                | 69     | 4.3 μs   | 6.9 μs   | 27.6 μs  | 69 μs   |  |

| 8x8 unsigned   | Hardware multiply         | 1                 | 1      | 62.5 ns  | 100 ns   | 400 ns   | 1 μs    |  |

| 9v9 signed     | Without hardware multiply | 33                | 91     | 5.7 μs   | 9.1 μs   | 36.4 μs  | 91 μs   |  |

| 8x8 signed     | Hardware multiply         | 6                 | 6      | 375 ns   | 600 ns   | 2.4 μs   | 6 μs    |  |

| 16v16 unsigned | Without hardware multiply | 21                | 242    | 15.1 μs  | 24.2 μs  | 96.8 μs  | 242 μs  |  |

| 16x16 unsigned | Hardware multiply         | 28                | 28     | 1.8 μs   | 2.8 μs   | 11.2 μs  | 28 μs   |  |

|                | Without hardware multiply | 52                | 254    | 15.9 μs  | 25.4 μs  | 102.6 μs | 254 μs  |  |

| 16x16 signed   | Hardware multiply         | 35                | 40     | 2.5 μs   | 4.0 μs   | 16.0 μs  | 40 μs   |  |

# TABLE 14-1: PERFORMANCE COMPARISON FOR VARIOUS MULTIPLY OPERATIONS

Example 14-3 shows the sequence to do a 16 x 16 unsigned multiplication. Equation 14-1 shows the algorithm that is used. The 32-bit result is stored in four registers (RES<3:0>).

#### EQUATION 14-1: 16 x 16 UNSIGNED MULTIPLICATION ALGORITHM

| RES3:RES0 | = | into ini. into i e i into zna into ze    |

|-----------|---|------------------------------------------|

|           | = | $(ARG1H \bullet ARG2H \bullet 2^{16}) +$ |

|           |   | $(ARG1H \bullet ARG2L \bullet 2^8) +$    |

|           |   | $(ARG1L \bullet ARG2H \bullet 2^8) +$    |

|           |   | $(ARG1L \bullet ARG2L)$                  |

|           |   |                                          |

# EXAMPLE 14-3: 16 x 16 UNSIGNED MULTIPLY ROUTINE

|   | MOVF   | ARG1L, W    |                        |

|---|--------|-------------|------------------------|

|   | MULWF  | ARG2L       | ; ARG1L * ARG2L->      |

|   |        |             | ; PRODH:PRODL          |

|   |        | PRODH, RES1 | ;                      |

|   | MOVFF  | PRODL, RESO | ;                      |

| ; |        |             |                        |

|   |        | ARG1H, W    |                        |

|   | MULWF  | ARG2H       | ; ARG1H * ARG2H->      |

|   |        |             | ; PRODH:PRODL          |

|   |        | PRODH, RES3 | ;                      |

|   | MOVFF  | PRODL, RES2 | ;                      |

| ; |        |             |                        |

|   |        | ARG1L, W    |                        |

|   | MULWF  | ARGZH       | ; ARG1L * ARG2H->      |

|   | NOTE   | DDODT N     | ; PRODH:PRODL          |

|   |        | PRODL, W    | ;<br>; Add cross       |

|   |        | ,           |                        |

|   |        | PRODH, W    | ; products             |

|   | CLRF   | RES2, F     | ;                      |

|   |        | RES3, F     | ,                      |

|   | ADDWFC | RESS, F     | ,                      |

| ; | MOVE   | ARG1H, W    | ;                      |

|   | MULWF  | ,           | ,<br>; ARG1H * ARG2L-> |

|   | HODME  | 111(021)    | ; PRODH: PRODL         |

|   | MOVE   | PRODL, W    | ;                      |

|   |        | RES1, F     | ; Add cross            |

|   |        | PRODH, W    | ; products             |

|   |        | RES2, F     | ;                      |

|   | CLRF   |             | ;                      |

|   | ADDWFC | RES3, F     | ;                      |

|   | -      |             |                        |

Example 14-4 shows the sequence to do a 16 x 16 signed multiply. Equation 14-2 shows the algorithm used. The 32-bit result is stored in four registers (RES<3:0>). To account for the sign bits of the arguments, the MSb for each argument pair is tested and the appropriate subtractions are done.

# EQUATION 14-2: 16 x 16 SIGNED MULTIPLICATION ALGORITHM

| $RES3:RES0 = ARG1H:ARG1L \bullet ARG2H:ARG2L$                    |

|------------------------------------------------------------------|

| $= (ARG1H \bullet ARG2H \bullet 2^{16}) +$                       |

| $(ARG1H \bullet ARG2L \bullet 2^8) +$                            |

| $(ARG1L \bullet ARG2H \bullet 2^8) +$                            |

| $(ARG1L \bullet ARG2L) +$                                        |

| $(-1 \bullet ARG2H < 7 > \bullet ARG1H: ARG1L \bullet 2^{16}) +$ |

| $(-1 \bullet ARG1H < 7 > \bullet ARG2H:ARG2L \bullet 2^{16})$    |

|                                                                  |

#### EXAMPLE 14-4: 16 x 16 SIGNED MULTIPLY ROUTINE

|     |           | INCE                |                                        |

|-----|-----------|---------------------|----------------------------------------|

|     | MOVF      | ARG1L, W            |                                        |

|     | MULWF     |                     | ; ARG1L * ARG2L ->                     |

|     |           |                     | ; PRODH:PRODL                          |

|     | MOVFF     | PRODH, RES1         | ;                                      |

|     | MOVFF     | PRODL, RESO         | ;                                      |

| ;   | 110 1 1 1 | 110000, 11000       | ,                                      |

| l ' | MOVF      | ARG1H, W            |                                        |

|     | MULWF     |                     | ; ARG1H * ARG2H ->                     |

|     | MOLWE     | ARGZII              | ; PRODH: PRODL                         |

|     | MOVFF     | PRODH, RES3         |                                        |

|     | MOVEE     |                     | ;                                      |

|     | MOVEE     | PRODL, RES2         | ;                                      |

| ;   | MOVE      | ADC1T W             |                                        |

|     | MOVE      | ARG1L, W            | • ADC11 * ADC211 >                     |

|     | MULWF     | ARGZH               | ; ARG1L * ARG2H ->                     |

| 1   | MOUTE     | DDODI W             | ; PRODH:PRODL                          |

| 1   | MOVE      | PRODL, W            | ;                                      |

|     | ADDWF     | RES1, F             | ; Add cross                            |

| 1   | MOVE      | PRODH, W<br>RES2, F | ; products                             |

|     |           |                     | ;                                      |

|     | CLRF      | WREG<br>RES3, F     | ;                                      |

|     | ADDWF.C   | RESJ, F             | ;                                      |

| ;   |           | anotu               |                                        |

|     |           | ARG1H, W            | ;                                      |

| 1   | MULWF     | ARG2L               | ; ARG1H * ARG2L ->                     |

|     |           |                     | ; PRODH:PRODL                          |

| 1   | MOVF      | PRODL, W            | ;                                      |

|     |           | RES1, F             | ; Add cross                            |

|     | MOVF      | PRODH, W            | ; products                             |

| 1   |           | RES2, F             | ;                                      |

| 1   | CLRF      | WREG                | ;                                      |

|     | ADDWFC    | RES3, F             | ;                                      |

| ;   |           |                     |                                        |

| 1   |           | ARG2H, 7            | ; ARG2H:ARG2L neg?<br>; no, check ARG1 |

|     | BRA       | _                   | ; no, check ARG1                       |

|     | MOVF      | ARG1L, W            | ;                                      |

|     | SUBWF     | RES2                | ;                                      |

|     | MOVF      | ARG1H, W            | ;                                      |

|     | SUBWFB    | RES3                |                                        |

| ;   |           |                     |                                        |

| SIG | N_ARG1    |                     |                                        |

|     |           | ARG1H, 7            | ; ARG1H:ARG1L neg?<br>; no, done       |

|     | BRA       |                     | ; no, done                             |

|     | MOVF      | ARG2L, W            | ;                                      |

|     | SUBWF     | RES2                | ;                                      |

|     | MOVF      | ARG2H, W            | ;                                      |

|     | SUBWFB    | RES3                |                                        |

| ;   |           |                     |                                        |

| CON | r_code    |                     |                                        |

|     | :         |                     |                                        |

|     |           |                     |                                        |

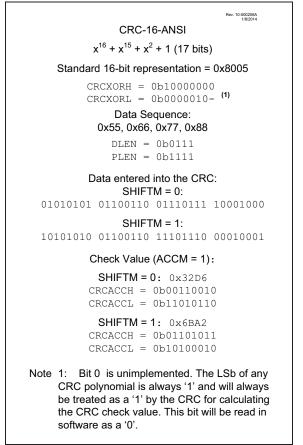

# 16.2 CRC Functional Overview

The CRC module can be used to detect bit errors in the program memory using the built-in memory scanner or through user input RAM memory. The CRC module can accept up to a 16-bit polynomial with up to a 16-bit seed value. A CRC calculated check value (or checksum) will then be generated into the CRCACC<15:0> registers for user storage. The CRC module uses an XOR shift register implementation to perform the polynomial division required for the CRC calculation.

# EXAMPLE 16-1: CRC EXAMPLE

| IADLE 17-3: | SUMMART OF REGISTERS ASSOCIATED WITH DMA |                 |       |       |        |         |        |       |                     |

|-------------|------------------------------------------|-----------------|-------|-------|--------|---------|--------|-------|---------------------|

| Name        | Bit 7                                    | Bit 6           | Bit 5 | Bit 4 | Bit 3  | Bit 2   | Bit 1  | Bit 0 | Register<br>on Page |

| DMAxCON0    | EN                                       | SIRQEN          | DGO   | _     | —      | AIRQEN  | _      | XIP   | 252                 |

| DMAxCON1    | DMOD                                     | E<1:0>          | DSTP  | SMR   | <1:0>  | SMOD    | E<1:0> | SSTP  | 253                 |

| DMAxBUF     | DBUF7                                    | DBUF6           | DBUF5 | DBUF4 | DBUF3  | DBUF2   | DBUF1  | DBUF0 | 254                 |

| DMAxSSAL    |                                          |                 |       | SSA   | <7:0>  |         |        |       | 254                 |

| DMAxSSAH    |                                          |                 |       | SSA<  | :15:8> |         |        |       | 254                 |

| DMAxSSAU    | —                                        | _               |       |       | SSA<   | 21:16>  |        |       | 255                 |

| DMAxSPTRL   |                                          |                 |       | SPTR  | <7:0>  |         |        |       | 255                 |

| DMAxSPTRH   |                                          |                 |       | SPTR  | <15:8> |         |        |       | 255                 |

| DMAxSPTRU   | —                                        | —               |       |       | SPTR<  | <21:16> |        |       | 256                 |

| DMAxSSZL    |                                          |                 |       | SSZ   | <7:0>  |         |        |       | 256                 |

| DMAxSSZH    | —                                        | —               | —     | —     |        | SSZ<    | 11:8>  |       | 256                 |

| DMAxSCNTL   |                                          |                 |       | SCNT  | <7:0>  |         |        |       | 257                 |

| DMAxSCNTH   | —                                        | —               |       | —     |        | SCNT    | <11:8> |       | 257                 |

| DMAxDSAL    |                                          |                 |       | DSA   | <7:0>  |         |        |       | 257                 |

| DMAxDSAH    |                                          |                 |       | DSA<  | :15:8> |         |        |       | 258                 |

| DMAxDPTRL   |                                          |                 |       | DPTF  | R<7:0> |         |        |       | 258                 |

| DMAxDPTRH   |                                          |                 |       | DPTR  | <15:8> |         |        |       | 258                 |

| DMAxDSZL    |                                          | DSZ<7:0>        |       |       |        |         |        | 259   |                     |

| DMAxDSZH    | —                                        | — — — DSZ<11:8> |       |       |        |         |        | 259   |                     |

| DMAxDCNTL   | DCNT<7:0>                                |                 |       |       |        |         | 259    |       |                     |

| DMAxDCNTH   |                                          | —               | —     | _     |        | DCNT    | <11:8> |       | 260                 |

| DMAxSIRQ    |                                          | SIRQ6           | SIRQ5 | SIRQ4 | SIRQ3  | SIRQ2   | SIRQ1  | SIRQ0 | 260                 |

| DMAxAIRQ    | _                                        | AIRQ6           | AIRQ5 | AIRQ4 | AIRQ3  | AIRQ2   | AIRQ1  | AIRQ0 | 260                 |

| TABLE 17-3: | SUMMARY OF REGISTERS ASSOCIATED WITH DMA |

|-------------|------------------------------------------|

|-------------|------------------------------------------|

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by DMA.

| R/W-x/x      | R/W-x/x           | R/W-x/x      | R/W-x/x | R/W-x/x           | R/W-x/x          | R/W-x/x         | R/W-x/x |

|--------------|-------------------|--------------|---------|-------------------|------------------|-----------------|---------|

|              |                   |              | RH      | <7:0>             |                  |                 |         |

| bit 7        |                   |              |         |                   |                  |                 | bit (   |

|              |                   |              |         |                   |                  |                 |         |

| Legend:      |                   |              |         |                   |                  |                 |         |

| R = Readable | bit               | W = Writable | bit     | U = Unimplem      | nented bit, read | l as '0'        |         |

|              | -n = Value at POR |              |         | '0' = Bit is clea | arod             | x = Bit is unkr |         |

# REGISTER 25-5: CCPRxH: CCPx REGISTER HIGH BYTE

| bit 7-0 | MODE = Capture Mode:                       |

|---------|--------------------------------------------|

|         | RH<7:0>: MSB of captured TMR1 value        |

|         | MODE = Compare Mode:                       |

|         | RH<7:0>: MSB compared to TMR1 value        |

|         | MODE = PWM Mode && FMT = 0:                |

|         | RH<7:2>: Not used                          |

|         | RH<1:0>: CCPW<9:8> – Pulse-Width MS 2 bits |

|         | MODE = PWM Mode && FMT = 1:                |

|         | RH<7:0>: CCPW<9:2> - Pulse-Width MS 8 bits |

# TABLE 25-5: SUMMARY OF REGISTERS ASSOCIATED WITH CCPx

| Name    | Bit 7       | Bit 6      | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0 | Register<br>on Page |

|---------|-------------|------------|-------|-------|-------|-------|--------|-------|---------------------|

| CCPxCON | EN          | _          | OUT   | FMT   |       | MODE  | =<3:0> |       | 353                 |

| CCPxCAP | _           | _          | _     | _     | —     | _     | CTS<   | <1:0> | 355                 |

| CCPRxL  |             | CCPRx<7:0> |       |       |       |       |        |       | 355                 |

| CCPRxH  | CCPRx<15:8> |            |       |       |       |       | 356    |       |                     |

**Legend:** — = Unimplemented location, read as '0'. Shaded cells are not used by the CCP module.

|                 |       | -                 | -     |                |                  |                  |              |

|-----------------|-------|-------------------|-------|----------------|------------------|------------------|--------------|

| R-x/x           | R-x/x | R-x/x             | R-x/x | R-x/x          | R-x/x            | R-x/x            | R-x/x        |

|                 |       |                   | SMT10 | CPR<7:0>       |                  |                  |              |

| bit 7           |       |                   |       |                |                  |                  | bit 0        |

|                 |       |                   |       |                |                  |                  |              |

| Legend:         |       |                   |       |                |                  |                  |              |

| R = Readable    | bit   | W = Writable bit  |       | U = Unimpler   | nented bit, read | d as '0'         |              |

| u = Bit is unch | anged | x = Bit is unknow | n     | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets |

# REGISTER 27-10: SMT1CPRL: SMT CAPTURED PERIOD REGISTER – LOW BYTE

bit 7-0 SMT1CPR<7:0>: Significant bits of the SMT Period Latch – Low Byte

'0' = Bit is cleared

'1' = Bit is set

'1' = Bit is set

#### REGISTER 27-11: SMT1CPRH: SMT CAPTURED PERIOD REGISTER - HIGH BYTE

| R-x/x            | R-x/x | R-x/x           | R-x/x  | R-x/x          | R-x/x            | R-x/x            | R-x/x        |

|------------------|-------|-----------------|--------|----------------|------------------|------------------|--------------|

|                  |       |                 | SMT1CF | PR<15:8>       |                  |                  |              |

| bit 7            |       |                 |        |                |                  |                  | bit 0        |

|                  |       |                 |        |                |                  |                  |              |

| Legend:          |       |                 |        |                |                  |                  |              |

| R = Readable b   | bit   | W = Writable I  | bit    | U = Unimplen   | nented bit, read | l as '0'         |              |

| u = Bit is uncha | anged | x = Bit is unkn | iown   | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets |

bit 7-0 SMT1CPR<15:8>: Significant bits of the SMT Period Latch – High Byte

'0' = Bit is cleared

#### **REGISTER 27-12: SMT1CPRU: SMT CAPTURED PERIOD REGISTER – UPPER BYTE**

| R-x/x | R-x/x | R-x/x | R-x/x   | R-x/x    | R-x/x | R-x/x | R-x/x |

|-------|-------|-------|---------|----------|-------|-------|-------|

|       |       |       | SMT1CPF | R<23:16> |       |       |       |

| bit 7 |       |       |         |          |       |       | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SMT1CPR<23:16>: Significant bits of the SMT Period Latch – Upper Byte

PIC18(L)F24/25K42

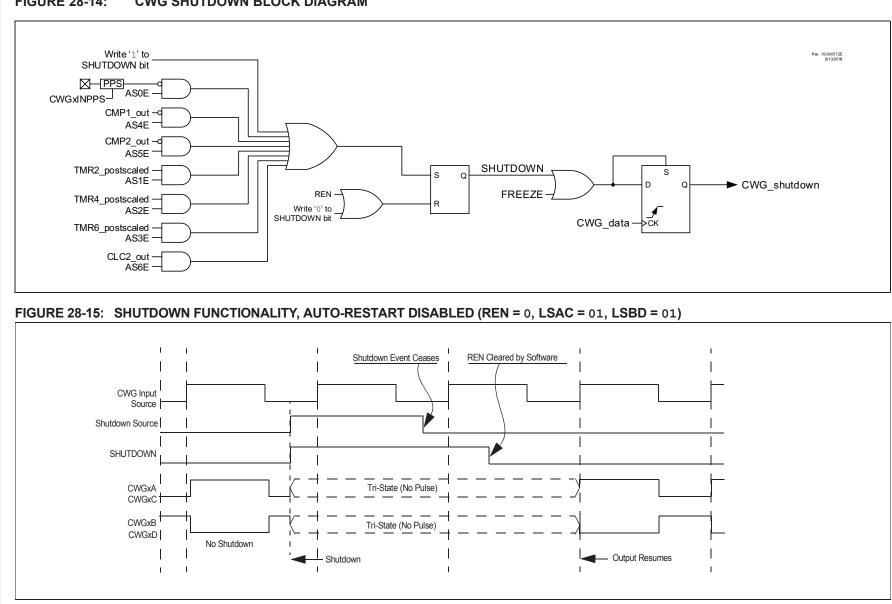

# FIGURE 28-14: CWG SHUTDOWN BLOCK DIAGRAM

| R/W-x/u          | R/W-x/u                                                                                            | R/W-x/u                              | R/W-x/u         | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u     |  |

|------------------|----------------------------------------------------------------------------------------------------|--------------------------------------|-----------------|----------------|------------------|------------------|-------------|--|

| G4D4T            | G4D4N                                                                                              | G4D3T                                | G4D3N           | G4D2T          | G4D2N            | G4D1T            | G4D1N       |  |

| bit 7            | ·                                                                                                  | ·                                    | ·               | · · · · · ·    |                  |                  | bit (       |  |

| Legend:          |                                                                                                    |                                      |                 |                |                  |                  |             |  |

| R = Readable     | bit                                                                                                | W = Writable                         | bit             | U = Unimplen   | nented bit, read | l as '0'         |             |  |

| u = Bit is unch  | nanged                                                                                             | x = Bit is unki                      | nown            | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |  |

| '1' = Bit is set |                                                                                                    | '0' = Bit is cle                     | ared            |                |                  |                  |             |  |

|                  |                                                                                                    |                                      |                 |                |                  |                  |             |  |

| bit 7            |                                                                                                    | e 3 Data 4 True                      | •               |                |                  |                  |             |  |

|                  |                                                                                                    | (true) is gated                      |                 |                |                  |                  |             |  |

|                  |                                                                                                    | (true) is not ga                     |                 |                |                  |                  |             |  |

| bit 6            |                                                                                                    | e 3 Data 4 Neg                       |                 |                |                  |                  |             |  |

|                  |                                                                                                    | (inverted) is ga<br>(inverted) is no |                 |                |                  |                  |             |  |

| bit 5            |                                                                                                    | . ,                                  | •               |                |                  |                  |             |  |

| DIL 5            | <b>G4D3T:</b> Gate 3 Data 3 True (non-inverted) bit<br>1 = CLCIN2 (true) is gated into CLCx Gate 3 |                                      |                 |                |                  |                  |             |  |

|                  |                                                                                                    | (true) is not ga                     |                 |                |                  |                  |             |  |

| bit 4            |                                                                                                    | e 3 Data 3 Neg                       |                 |                |                  |                  |             |  |

|                  |                                                                                                    | (inverted) is ga                     |                 |                |                  |                  |             |  |

|                  | 0 = CLCIN2                                                                                         | (inverted) is no                     | t gated into Cl | LCx Gate 3     |                  |                  |             |  |

| bit 3            | G4D2T: Gate                                                                                        | e 3 Data 2 True                      | (non-inverted)  | ) bit          |                  |                  |             |  |

|                  |                                                                                                    | (true) is gated                      |                 |                |                  |                  |             |  |

|                  |                                                                                                    | (true) is not ga                     |                 |                |                  |                  |             |  |

| bit 2            |                                                                                                    | e 3 Data 2 Neg                       | . ,             |                |                  |                  |             |  |

|                  |                                                                                                    | (inverted) is ga<br>(inverted) is no |                 |                |                  |                  |             |  |

| bit 1            | G4D1T: Gate                                                                                        | e 4 Data 1 True                      | (non-inverted)  | ) bit          |                  |                  |             |  |

|                  |                                                                                                    | (true) is gated into CLCx Gate 3     |                 |                |                  |                  |             |  |

|                  | 0 = CLCINO                                                                                         | (true) is not ga                     | ted into CLCx   | Gate 3         |                  |                  |             |  |

| bit 0            | G4D1N: Gat                                                                                         | e 3 Data 1 Neg                       | ated (inverted) | ) bit          |                  |                  |             |  |

|                  |                                                                                                    | (inverted) is ga                     |                 |                |                  |                  |             |  |

|                  | 0 = CLCIN0                                                                                         | (inverted) is no                     | t gated into Cl | LCx Gate 3     |                  |                  |             |  |

# REGISTER 29-10: CLCxGLS3: GATE 3 LOGIC SELECT REGISTER

# 34.3.3 TRANSMIT AND RECEIVE FIFOS

The transmission and reception of data from the SPI module is handled by two FIFOs, one for reception and one for transmission (addressed by the SFRs SPIxRXB and SPIxTXB, respectively.). The TXFIFO is written by software and is read by the SPI module to shift the data onto the SDO pin. The RXFIFO is written by the SPI module as it shifts in the data from the SDI pin and is read by software. Setting the CLRBF bit of SPIxSTATUS resets the occupancy for both FIFOs, emptying both buffers. The FIFOs are also reset by disabling the SPI module.

Note: TXFIFO occupancy and RXFIFO occupancy simply refer to the number of bytes that are currently being stored in each FIFO. These values are used in this chapter to illustrate the function of these FIFOs and are not directly accessible through software.

The SPIxRXB register addresses the receive FIFO and is read-only. Reading from this register will read from the first FIFO location that was written to by hardware and decrease the RXFIFO occupancy. If the FIFO is empty, reading from this register will instead return a value of zero and set the RXRE (Receive Buffer Read Error) bit of the SPIxSTATUS register. The RXRE bit must then be cleared in software in order to properly reflect the status of the read error. When RXFIFO is full, the RXBF bit of the SPIxSTATUS register will be set. When the device receives data on the SDI pin, the receive FIFO may be written to by hardware and the occupancy increased, depending on the mode and receiver settings, as summarized in Table 34-1.

The SPIxTXB register addresses the transmit FIFO and is write-only. Writing to the register will write to the first empty FIFO location and increase the occupancy. If the FIFO is full, writing to this register will not affect the data and will set the TXWE bit of the SPIxSTATUS register. When the TXFIFO is empty, the TXBE bit of SPIxSTATUS will be set. When a data transfer occurs, data may be read from the first FIFO location written to and the occupancy decreases, depending on mode and transmitter settings, as summarized in Table 34-1 and Section 34.6.1 "Slave Mode Transmit options".

# 34.3.4 LSB VS. MSB-FIRST OPERATION

Typically, SPI communication is output Most-Significant bit first, but some devices/buses may not conform to this standard. In this case, the LSBF bit may be used to alter the order in which bits are shifted out during the data exchange. In both Master and Slave mode, the LSBF bit of SPIxCON0 controls if data is shifted MSb or LSb first. Clearing the bit (default) configures the data to transfer MSb first, which is traditional SPI operation, while setting the bit configures the data to transfer LSb first.

#### 34.3.5 INPUT AND OUTPUT POLARITY BITS

SPIxCON1 has three bits that control the polarity of the SPI inputs and outputs. The SDIP bit controls the polarity of the SDI input, the SDOP bit controls the polarity of the SDO output, and the SSP bit controls the polarity of both the slave SS input and the master SS output. For all three bits, when the bit is clear, the input or output is active-high, and when the bit is set, the input or output is active-low. When the EN bit of SPIxCON0 is cleared, SS(out) and SCK(out) both revert to the inactive state dictated by their polarity bits. The SDO output state when the EN bit of SPIxCON0 is cleared is determined by several factors.

- When the associated TRIS bit for the SDO pin is cleared, and the SPI goes Idle after a transmission, the SDO output will remain at the last bit level. The SDO pin will revert to the Idle state if EN is cleared.

- When the associated TRIS bit for the SDO pin is set, behavior varies in Slave and Master mode.

- In Slave mode, the SDO pin tri-states when:

- Slave Select is inactive,

- the EN bit of SPIxCON0 is cleared, or when

- the TXR bit of SPIxCON2 is cleared.

- In Master mode, the SDO pin tri-states when TXR = 0. When TXR = 1 and the SPI goes Idle after a transmission, the SDO output will remain at the last bit level. The SDO pin will revert to the Idle state if EN is cleared.

| R/W-0/0          | R/W-0/0 | R/W-0/0             | R/W-0/0 | R/W-0/0        | R/W-0/0       | R/W-0/0        | R/W-0/0      |

|------------------|---------|---------------------|---------|----------------|---------------|----------------|--------------|

|                  |         |                     | STPT    | <15:8>         |               |                |              |

| bit 7            |         |                     |         |                |               |                | bit 0        |

|                  |         |                     |         |                |               |                |              |

| Legend:          |         |                     |         |                |               |                |              |

| R = Readable     | bit     | W = Writable bit    |         | U = Unimplemer |               | d as '0'       |              |

| u = Bit is unch  | anged   | x = Bit is unknow   | wn      | -n/n = Value a | at POR and BO | R/Value at all | other Resets |

| '1' = Bit is set |         | '0' = Bit is cleare | ed      |                |               |                |              |

# REGISTER 38-27: ADSTPTH: ADC THRESHOLD SETPOINT REGISTER HIGH

bit 7-0 **STPT<15:8>**: ADC Threshold Setpoint MSB. Upper byte of ADC threshold setpoint, depending on ADCALC, may be used to determine ERR, see Register 38-29 for more details.

#### REGISTER 38-28: ADSTPTL: ADC THRESHOLD SETPOINT REGISTER LOW

| R/W-0/0   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-----------|---------|---------|---------|---------|---------|---------|---------|

| STPT<7:0> |         |         |         |         |         |         |         |

| bit 7     |         |         |         |         |         |         | bit 0   |

|           |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **STPT<7:0>**: ADC Threshold Setpoint LSB. Lower byte of ADC threshold setpoint, depending on ADCALC, may be used to determine ERR, see Register 38-30 for more details.

# PIC18(L)F24/25K42

| RET   | FIE                                                                                          | Return fro                                                                                                                                                                                                                                                       | om Interru                                                                                                                                                                                                             | upt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                          |

|-------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Synta | ax:                                                                                          | RETFIE {s                                                                                                                                                                                                                                                        | ;}                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                          |