Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 64 x 8                                                                    |

| RAM Size                   | 68 × 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 18-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f84a-04-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 DEVICE OVERVIEW

This document contains device specific information for the operation of the PIC16F84A device. Additional information may be found in the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023), which may be downloaded from the Microchip website. The Reference Manual should be considered a complementary document to this data sheet, and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules.

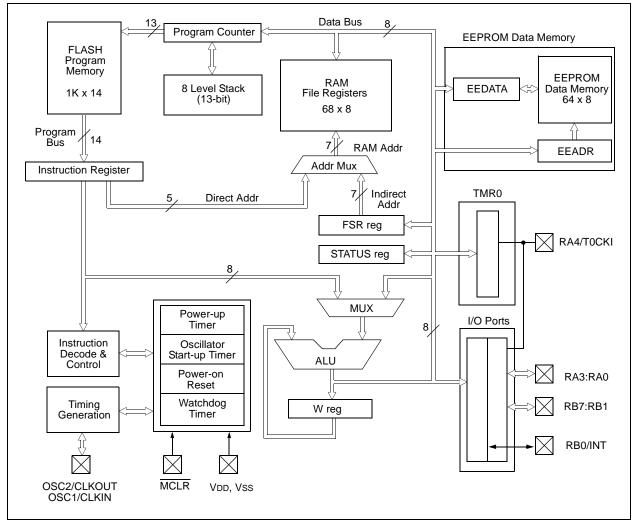

The PIC16F84A belongs to the mid-range family of the  $PIC^{\textcircled{R}}$  microcontroller devices. A block diagram of the device is shown in Figure 1-1.

The program memory contains 1K words, which translates to 1024 instructions, since each 14-bit program memory word is the same width as each device instruction. The data memory (RAM) contains 68 bytes. Data EEPROM is 64 bytes.

There are also 13 I/O pins that are user-configured on a pin-to-pin basis. Some pins are multiplexed with other device functions. These functions include:

- External interrupt

- · Change on PORTB interrupt

- Timer0 clock input

Table 1-1 details the pinout of the device with descriptions and details for each pin.

FIGURE 1-1: PIC16F84A BLOCK DIAGRAM

# 2.2 Data Memory Organization

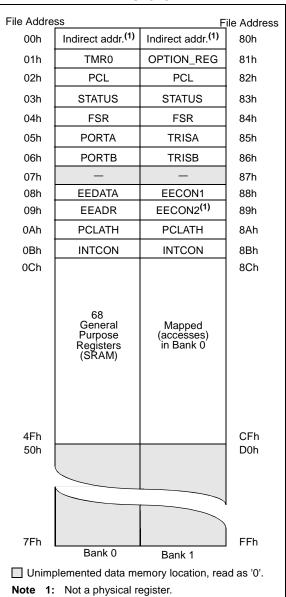

The data memory is partitioned into two areas. The first is the Special Function Registers (SFR) area, while the second is the General Purpose Registers (GPR) area. The SFRs control the operation of the device.

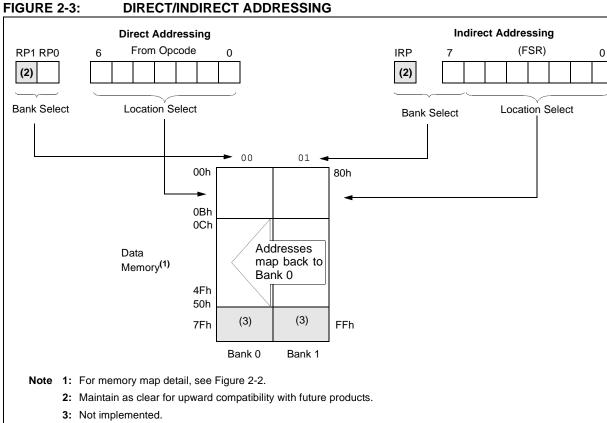

Portions of data memory are banked. This is for both the SFR area and the GPR area. The GPR area is banked to allow greater than 116 bytes of general purpose RAM. The banked areas of the SFR are for the registers that control the peripheral functions. Banking requires the use of control bits for bank selection. These control bits are located in the STATUS Register. Figure 2-2 shows the data memory map organization.

Instructions MOVWF and MOVF can move values from the W register to any location in the register file ("F"), and vice-versa.

The entire data memory can be accessed either directly using the absolute address of each register file or indirectly through the File Select Register (FSR) (Section 2.5). Indirect addressing uses the present value of the RP0 bit for access into the banked areas of data memory.

Data memory is partitioned into two banks which contain the general purpose registers and the special function registers. Bank 0 is selected by clearing the RP0 bit (STATUS<5>). Setting the RP0 bit selects Bank 1. Each Bank extends up to 7Fh (128 bytes). The first twelve locations of each Bank are reserved for the Special Function Registers. The remainder are General Purpose Registers, implemented as static RAM.

#### 2.2.1 GENERAL PURPOSE REGISTER FILE

Each General Purpose Register (GPR) is 8-bits wide and is accessed either directly or indirectly through the FSR (Section 2.5).

The GPR addresses in Bank 1 are mapped to addresses in Bank 0. As an example, addressing location 0Ch or 8Ch will access the same GPR.

#### FIGURE 2-2: REGISTER FILE MAP -PIC16F84A

## 2.3.1 STATUS REGISTER

The STATUS register contains the arithmetic status of the ALU, the RESET status and the bank select bit for data memory.

As with any register, the STATUS register can be the destination for any instruction. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as  $000u \ uluu$  (where u = unchanged).

Only the BCF, BSF, SWAPF and MOVWF instructions should be used to alter the STATUS register (Table 7-2), because these instructions do not affect any status bit.

- Note 1: The IRP and RP1 bits (STATUS<7:6>) are not used by the PIC16F84A and should be programmed as cleared. Use of these bits as general purpose R/W bits is NOT recommended, since this may affect upward compatibility with future products.

- 2: The C and DC bits operate as a borrow and digit borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

- 3: When the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. The specified bit(s) will be updated according to device logic

# REGISTER 2-1: STATUS REGISTER (ADDRESS 03h, 83h)

|         | R/W-0         | R/W-0                            | R/W-0         | R-1           | R-1            | R/W-x         | R/W-x          | R/W-x        |

|---------|---------------|----------------------------------|---------------|---------------|----------------|---------------|----------------|--------------|

|         | IRP           | RP1                              | RP0           | TO            | PD             | Z             | DC             | С            |

|         | bit 7         |                                  |               |               |                |               |                | bit 0        |

|         |               |                                  |               |               |                |               |                |              |

| bit 7-6 | -             | ented: Maint                     |               |               |                |               |                |              |

| bit 5   | -             | ster Bank Sel                    | -             | ed for direct | addressing     | g)            |                |              |

|         |               | 1 (80h - FFh<br>0 (00h - 7Fh     | ,             |               |                |               |                |              |

| bit 4   | TO: Time-o    | out bit                          |               |               |                |               |                |              |

|         | •             | ower-up, CLI                     |               | ction, or SLI | EEP instruc    | tion          |                |              |

|         |               | F time-out oc                    | curred        |               |                |               |                |              |

| bit 3   | PD: Power     |                                  |               |               |                |               |                |              |

|         | •             | ower-up or b                     | •             |               | n              |               |                |              |

|         | -             | ecution of the                   | SLEEP INST    | ruction       |                |               |                |              |

| bit 2   | Z: Zero bit   | oult of on original              | thratic or la |               | n in Toro      |               |                |              |

|         |               | sult of an ari<br>sult of an ari |               |               |                | ro            |                |              |

| bit 1   |               | arry/borrow b                    |               | •             |                |               | (for borrow,   | the polarity |

|         | is reversed   |                                  |               |               |                |               |                |              |

|         | •             | /-out from the<br>ry-out from t  |               |               |                | urred         |                |              |

| bit 0   |               | orrow bit (AD                    |               |               |                | ructions) (fo | horrow the     | onlarity is  |

| bit 0   | reversed)     | SHOW DR (AD                      |               | , 3080, 5     |                |               | borrow, the    | polarity is  |

|         |               | /-out from the                   |               |               |                |               |                |              |

|         |               | ry-out from t                    | 0             |               |                |               |                |              |

|         | Note:         | A subtraction                    |               |               |                | -             |                | -            |

|         |               | For rotate (R<br>bit of the sou  | , ,           | ,             | his bit is loa | ded with eith | ier the high o | or low order |

|         |               |                                  | arce register |               |                |               |                |              |

|         | Legend:       |                                  |               |               |                |               |                |              |

|         | R = Reada     | ble bit                          | W = W         | ritable bit   | U = Unir       | mplemented    | bit, read as   | ʻ0'          |

|         | - n = Value a | at POR                           | '1' = Bit     | is set        | '0' = Bit is   | s cleared     | x = Bit is un  | known        |

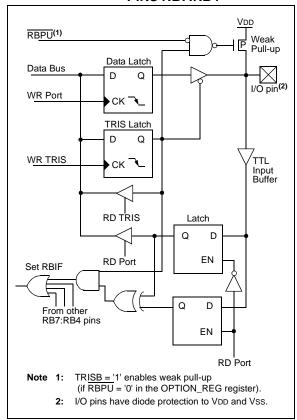

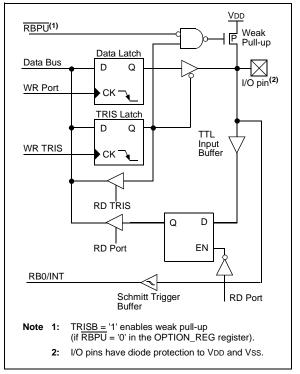

# 4.2 PORTB and TRISB Registers

PORTB is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

EXAMPLE 4-2: INITIALIZING PORTB

| BCF   | STATUS, RPO | ; |                       |

|-------|-------------|---|-----------------------|

| CLRF  | PORTB       | ; | Initialize PORTB by   |

|       |             | ; | clearing output       |

|       |             | ; | data latches          |

| BSF   | STATUS, RPO | ; | Select Bank 1         |

| MOVLW | 0xCF        | ; | Value used to         |

|       |             | ; | initialize data       |

|       |             | ; | direction             |

| MOVWF | TRISB       | ; | Set RB<3:0> as inputs |

|       |             | ; | RB<5:4> as outputs    |

|       |             | ; | RB<7:6> as inputs     |

| 1     |             |   |                       |

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (OPTION<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of PORTB's pins, RB7:RB4, have an interrupt-onchange feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupton-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

#### FIGURE 4-3: BLOCK DIAGRAM OF PINS RB7:RB4

FIGURE 4-4:

BLOCK DIAGRAM OF PINS RB3:RB0

| Name    | Bit  | Buffer Type           | I/O Consistency Function                                                                                               |

|---------|------|-----------------------|------------------------------------------------------------------------------------------------------------------------|

| RB0/INT | bit0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input.<br>Internal software programmable weak pull-up.                          |

| RB1     | bit1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                         |

| RB2     | bit2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                         |

| RB3     | bit3 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                         |

| RB4     | bit4 | TTL                   | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up.                           |

| RB5     | bit5 | TTL                   | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up.                           |

| RB6     | bit6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up. Serial programming clock. |

| RB7     | bit7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up. Serial programming data.  |

# TABLE 4-3:PORTB FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger.

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

#### TABLE 4-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address | Name       | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0   | Value on<br>Power-on<br>Reset | Value on<br>all other<br>RESETS |

|---------|------------|--------|--------|--------|--------|--------|--------|--------|---------|-------------------------------|---------------------------------|

| 06h     | PORTB      | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0/INT | xxxx xxxx                     | uuuu uuuu                       |

| 86h     | TRISB      | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0  | 1111 1111                     | 1111 1111                       |

| 81h     | OPTION_REG | RBPU   | INTEDG | TOCS   | T0SE   | PSA    | PS2    | PS1    | PS0     | 1111 1111                     | 1111 1111                       |

| 0Bh,8Bh | INTCON     | GIE    | EEIE   | TOIE   | INTE   | RBIE   | T0IF   | INTF   | RBIF    | 0000 000x                     | 0000 000u                       |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTB.

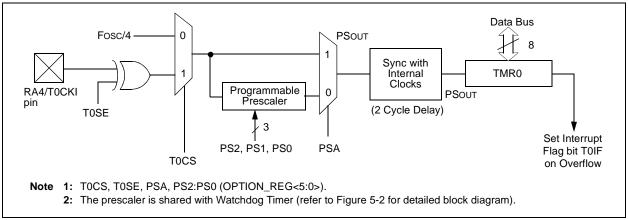

# 5.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- · Internal or external clock select

- Edge select for external clock

- 8-bit software programmable prescaler

- Interrupt-on-overflow from FFh to 00h

Figure 5-1 is a simplified block diagram of the Timer0 module.

Additional information on timer modules is available in the PIC<sup>®</sup> Mid-Range Reference Manual (DS33023).

# 5.1 Timer0 Operation

Timer0 can operate as a timer or as a counter.

Timer mode is selected by clearing bit TOCS (OPTION\_REG<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit TOCS (OPTION\_REG<5>). In Counter mode, Timer0 will increment, either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit, TOSE (OPTION\_REG<4>). Clearing bit TOSE selects the rising edge. Restrictions on the external clock input are discussed below.

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization. Additional information on external clock requirements is available in the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023).

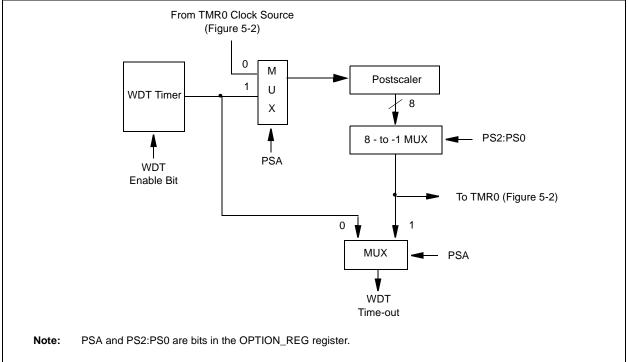

#### 5.2 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 5-2). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that there is only one prescaler available which is mutually exclusively shared between the Timer0 module and the Watchdog Timer. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa.

The prescaler is not readable or writable.

The PSA and PS2:PS0 bits (OPTION\_REG<3:0>) determine the prescaler assignment and prescale ratio.

Clearing bit PSA will assign the prescaler to the Timer0 module. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4, ..., 1:256 are selectable.

Setting bit PSA will assign the prescaler to the Watchdog Timer (WDT). When the prescaler is assigned to the WDT, prescale values of 1:1, 1:2, ..., 1:128 are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT.

Note: Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count, but will not change the prescaler assignment.

### FIGURE 5-1: TIMER0 BLOCK DIAGRAM

# 6.0 SPECIAL FEATURES OF THE CPU

What sets a microcontroller apart from other processors are special circuits to deal with the needs of real time applications. The PIC16F84A has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These features are:

- OSC Selection

- RESET

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- Code Protection

- ID Locations

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

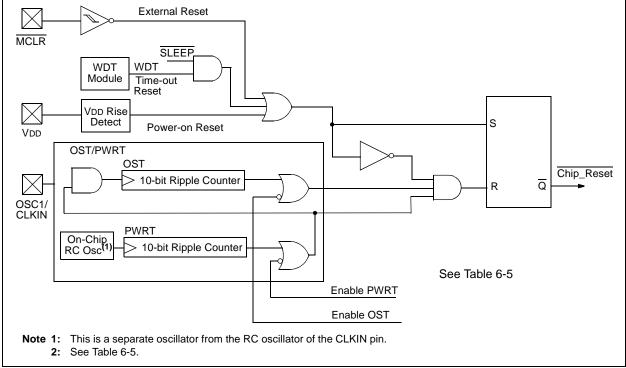

The PIC16F84A has a Watchdog Timer which can be shut-off only through configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only. This design keeps the device in RESET while the power supply stabilizes. With these two timers on-chip, most applications need no external RESET circuitry.

SLEEP mode offers a very low current power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer Time-out or through an interrupt. Several oscillator options are provided to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select the various options.

Additional information on special features is available in the PIC<sup>®</sup> Mid-Range Reference Manual (DS33023).

# 6.1 Configuration Bits

The configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. These bits are mapped in program memory location 2007h.

Address 2007h is beyond the user program memory space and it belongs to the special test/configuration memory space (2000h - 3FFFh). This space can only be accessed during programming.

### REGISTER 6-1: PIC16F84A CONFIGURATION WORD

| R/P-u    | R/P-u | R/P-u                      | R/P-u                                                     | R/P-u                                | R/P-u     | R/P-u     | R/P-u | R/P-u | R/P-u | R/P-u | R/P-u | R/P-u | R/P-u |

|----------|-------|----------------------------|-----------------------------------------------------------|--------------------------------------|-----------|-----------|-------|-------|-------|-------|-------|-------|-------|

| CP       | CP    | СР                         | СР                                                        | CP                                   | СР        | СР        | СР    | СР    | CP    | PWRTE | WDTE  | F0SC1 | F0SC0 |

| bit13    |       |                            |                                                           |                                      |           |           |       |       |       |       |       |       | bit0  |

| bit 13-4 |       | 1 = Co                     | de prote                                                  | ection bi<br>ction dis<br>n memor    | abled     | e protec  | ted   |       |       |       |       |       |       |

| bit 3    |       | 1 = Pov                    | wer-up 7                                                  | r-up Tim<br>Timer is (<br>Timer is ( | disablec  | I         |       |       |       |       |       |       |       |

| bit 2    |       | 1 = WD                     | Watcho<br>T enabl<br>T disab                              |                                      | er Enabl  | e bit     |       |       |       |       |       |       |       |

| bit 1-0  |       | 11 = R<br>10 = H<br>01 = X | :FOSC<br>C oscilla<br>S oscilla<br>T oscilla<br>P oscilla | tor<br>tor                           | ator Sele | ection bi | ts    |       |       |       |       |       |       |

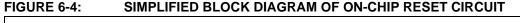

# 6.3 RESET

The PIC16F84A differentiates between various kinds of RESET:

- Power-on Reset (POR)

- MCLR during normal operation

- MCLR during SLEEP

- WDT Reset (during normal operation)

- WDT Wake-up (during SLEEP)

Figure 6-4 shows a simplified block diagram of the On-Chip RESET Circuit. The  $\overline{\text{MCLR}}$  Reset path has a noise filter to ignore small pulses. The electrical specifications state the pulse width requirements for the  $\overline{\text{MCLR}}$  pin.

Some registers are not affected in any RESET condition; their status is unknown on a POR and unchanged in any other RESET. Most other registers are reset to a "RESET state" on POR, MCLR or WDT Reset during normal operation and on MCLR during SLEEP. They are not affected by a WDT Reset during SLEEP, since this RESET is viewed as the resumption of normal operation.

Table 6-3 gives a description of RESET conditions for the program counter (PC) and the STATUS register. Table 6-4 gives a full description of RESET states for all registers.

The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are set or cleared differently in different RESET situations (Section 6.7). These bits are used in software to determine the nature of the RESET.

# TABLE 6-3: RESET CONDITION FOR PROGRAM COUNTER AND THE STATUS REGISTER

| Condition                           | Program Counter       | STATUS Register |

|-------------------------------------|-----------------------|-----------------|

| Power-on Reset                      | 000h                  | 0001 1xxx       |

| MCLR during normal operation        | 000h                  | 000u uuuu       |

| MCLR during SLEEP                   | 000h                  | 0001 0uuu       |

| WDT Reset (during normal operation) | 000h                  | 0000 luuu       |

| WDT Wake-up                         | PC + 1                | uuu0 0uuu       |

| Interrupt wake-up from SLEEP        | PC + 1 <sup>(1)</sup> | uuul Ouuu       |

Legend: u = unchanged, x = unknown

Note 1: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

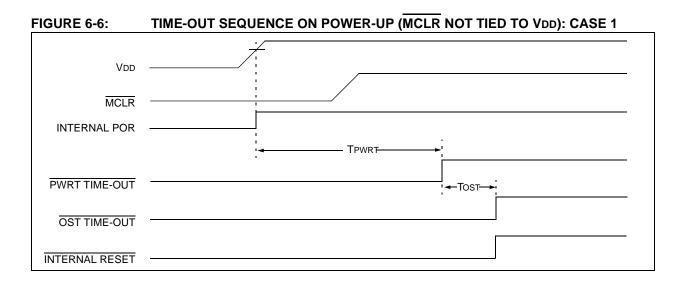

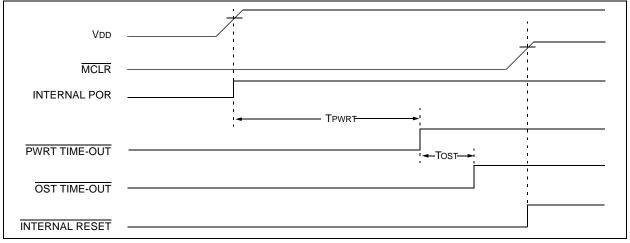

FIGURE 6-7: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

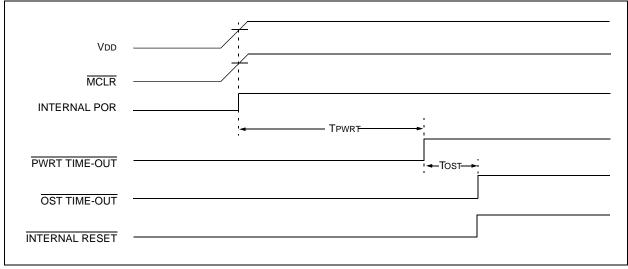

FIGURE 6-8: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD): FAST VDD RISE TIME

#### 6.10.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken into account that under worst case conditions (VDD = Min., Temperature = Max., Max. WDT Prescaler), it may take several seconds before a WDT time-out occurs.

TABLE 6-7: SUMMARY OF REGISTERS ASSOCIATED WITH THE WATCHDOG TIMER

| Addr  | Name         | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on all<br>other<br>RESETS |

|-------|--------------|-------|--------|-------|-------|----------------------|-------|-------|-------|-------------------------------|---------------------------------|

| 2007h | Config. bits | (2)   | (2)    | (2)   | (2)   | PWRTE <sup>(1)</sup> | WDTE  | FOSC1 | FOSC0 | (2)                           |                                 |

| 81h   | OPTION_REG   | RBPU  | INTEDG | TOCS  | T0SE  | PSA                  | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                       |

Legend: x = unknown. Shaded cells are not used by the WDT.

**Note 1:** See Register 6-1 for operation of the PWRTE bit.

2: See Register 6-1 and Section 6.12 for operation of the code and data protection bits.

# 9.0 ELECTRICAL CHARACTERISTICS

#### Absolute Maximum Ratings †

| Ambient temperature under bias                                                                                |                         |

|---------------------------------------------------------------------------------------------------------------|-------------------------|

| Storage temperature                                                                                           | 65°C to +150°C          |

| Voltage on any pin with respect to Vss (except VDD, MCLR, and RA4)                                            |                         |

| Voltage on VDD with respect to VSS                                                                            | 0.3 to +7.5V            |

| Voltage on MCLR with respect to Vss <sup>(1)</sup>                                                            |                         |

| Voltage on RA4 with respect to Vss                                                                            | 0.3 to +8.5V            |

| Total power dissipation <sup>(2)</sup>                                                                        | 800 mW                  |

| Maximum current out of Vss pin                                                                                |                         |

| Maximum current into Vod pin                                                                                  | 100 mA                  |

| Input clamp current, Iк (Vi < 0 or Vi > VDD)                                                                  | ± 20 mA                 |

| Output clamp current, loк (Vo < 0 or Vo > VDD)                                                                | ± 20 mA                 |

| Maximum output current sunk by any I/O pin                                                                    | 25 mA                   |

| Maximum output current sourced by any I/O pin                                                                 | 25 mA                   |

| Maximum current sunk by PORTA                                                                                 | 80 mA                   |

| Maximum current sourced by PORTA                                                                              | 50 mA                   |

| Maximum current sunk by PORTB                                                                                 | 150 mA                  |

| Maximum current sourced by PORTB                                                                              | 100 mA                  |

| <b>Note 1:</b> Voltage spikes below Vss at the $\overline{\text{MCLR}}$ pin inducing currents greater than 80 | ) mA may cause latch-up |

- **Note 1:** Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80 mA, <u>may</u> cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR pin rather than pulling this pin directly to Vss.

- **2:** Power dissipation is calculated as follows: Pdis = VDD x {IDD  $\sum$  IOH} +  $\sum$  {(VDD-VOH) x IOH} +  $\sum$ (VOI x IOL).

**†** NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

# PIC16F84A

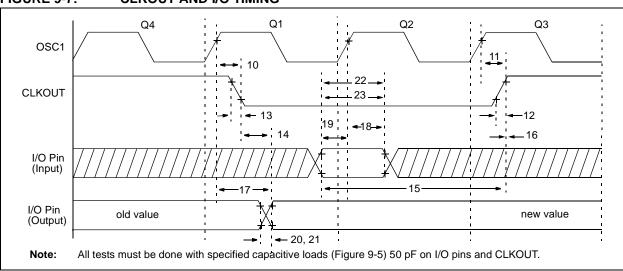

#### **CLKOUT AND I/O TIMING** FIGURE 9-7:

| Param<br>No. | Sym      | Characteristic                        | ;             | Min          | Тур† | Мах        | Units | Conditions |

|--------------|----------|---------------------------------------|---------------|--------------|------|------------|-------|------------|

| 10           | TosH2ckL | OSC1↑ to CLKOUT↓                      | Standard      | _            | 15   | 30         | ns    | (Note 1)   |

| 10A          |          |                                       | Extended (LF) |              | 15   | 120        | ns    | (Note 1)   |

| 11           | TosH2ckH | OSC1↑ to CLKOUT↑                      | Standard      |              | 15   | 30         | ns    | (Note 1)   |

| 11A          |          |                                       | Extended (LF) | —            | 15   | 120        | ns    | (Note 1)   |

| 12           | TckR     | CLKOUT rise time                      | Standard      | —            | 15   | 30         | ns    | (Note 1)   |

| 12A          |          |                                       | Extended (LF) |              | 15   | 100        | ns    | (Note 1)   |

| 13           | TckF     | CLKOUT fall time                      | Standard      | —            | 15   | 30         | ns    | (Note 1)   |

| 13A          |          |                                       | Extended (LF) | —            | 15   | 100        | ns    | (Note 1)   |

| 14           | TckL2ioV | CLKOUT $\downarrow$ to Port out valid | •             |              | _    | 0.5Tcy +20 | ns    | (Note 1)   |

| 15           | TioV2ckH | Port in valid before                  | Standard      | 0.30Tcy + 30 | _    | _          | ns    | (Note 1)   |

|              |          | CLKOUT ↑                              | Extended (LF) | 0.30Tcy + 80 | _    | _          | ns    | (Note 1)   |

| 16           | TckH2iol | Port in hold after CLKOUT 1           | •             | 0            | —    | _          | ns    | (Note 1)   |

| 17           | TosH2ioV | OSC1 <sup>↑</sup> (Q1 cycle) to       | Standard      | —            | _    | 125        | ns    |            |

|              |          | Port out valid                        | Extended (LF) | —            | _    | 250        | ns    |            |

| 18           | TosH2iol | OSC1 <sup>↑</sup> (Q2 cycle) to Port  | Standard      | 10           | _    | _          | ns    |            |

|              |          | input invalid (I/O in hold time)      | Extended (LF) | 10           | _    | _          | ns    |            |

| 19           | TioV2osH | Port input valid to OSC1↑             | Standard      | -75          | _    | _          | ns    |            |

|              |          | (I/O in setup time)                   | Extended (LF) | -175         | _    | _          | ns    |            |

| 20           | TioR     | Port output rise time                 | Standard      | —            | 10   | 35         | ns    |            |

| 20A          |          |                                       | Extended (LF) | —            | 10   | 70         | ns    |            |

| 21           | TioF     | Port output fall time                 | Standard      | —            | 10   | 35         | ns    |            |

| 21A          |          |                                       | Extended (LF) | —            | 10   | 70         | ns    |            |

| 22           | TINP     | INT pin high                          | Standard      | 20           | —    | _          | ns    |            |

| 22A          |          | or low time                           | Extended (LF) | 55           | _    | _          | ns    |            |

| 23           | Trbp     | RB7:RB4 change INT                    | Standard      | Tosc§        | —    | _          | ns    |            |

| 23A          |          | high or low time                      | Extended (LF) | Tosc§        | _    |            | ns    |            |

Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested. † §

By design.

Note 1: Measurements are taken in RC mode where CLKOUT output is 4 x Tosc.

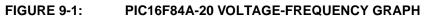

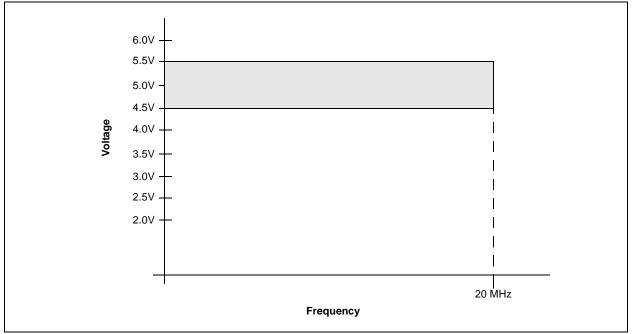

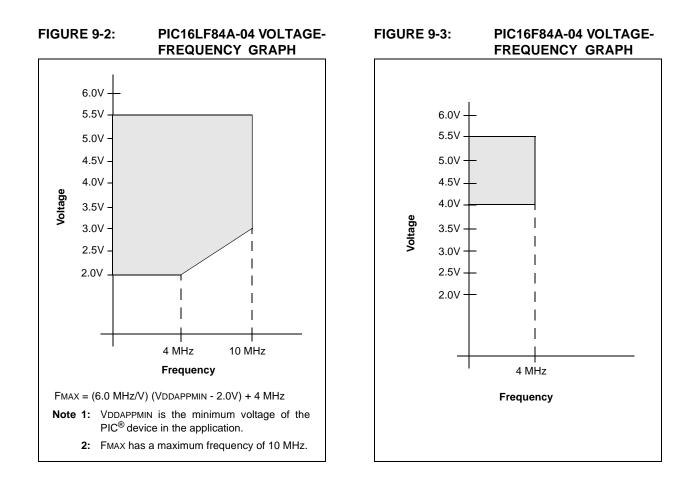

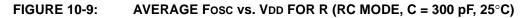

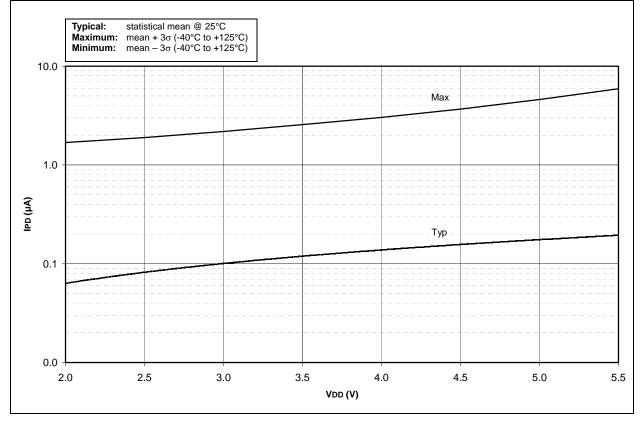

# 10.0 DC/AC CHARACTERISTIC GRAPHS

The graphs provided in this section are for **design guidance** and are **not tested**.

In some graphs, the data presented are **outside specified operating range** (i.e., outside specified VDD range). This is for **information only** and devices are ensured to operate properly only within the specified range.

The data presented in this section is a **statistical summary** of data collected on units from different lots over a period of time and matrix samples. 'Typical' represents the mean of the distribution at 25°C. 'Max' or 'Min' represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ), respectively, where  $\sigma$  is a standard deviation over the whole temperature range.

# PIC16F84A

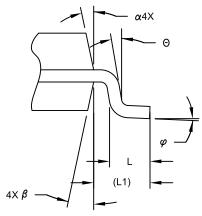

# 18-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

VIEW C

|                          | N    | <b>ILLIMETER</b> | S         |      |  |  |  |

|--------------------------|------|------------------|-----------|------|--|--|--|

| Dimension Lin            | nits | MIN              | NOM       | MAX  |  |  |  |

| Number of Pins           | N    |                  | 18        |      |  |  |  |

| Pitch                    | е    |                  | 1.27 BSC  |      |  |  |  |

| Overall Height           | Α    | I                | -         | 2.65 |  |  |  |

| Molded Package Thickness | A2   | 2.05             | -         | -    |  |  |  |

| Standoff §               | A1   | 0.10             | -         | 0.30 |  |  |  |

| Overall Width            | E    |                  | 10.30 BSC |      |  |  |  |

| Molded Package Width     | E1   |                  | 7.50 BSC  |      |  |  |  |

| Overall Length           | D    | 11.55 BSC        |           |      |  |  |  |

| Chamfer (Optional)       | h    | 0.25             | -         | 0.75 |  |  |  |

| Foot Length              | L    | 0.40             | -         | 1.27 |  |  |  |

| Footprint                | L1   |                  | 1.40 REF  |      |  |  |  |

| Lead Angle               | Θ    | 0°               | -         | -    |  |  |  |

| Foot Angle               | φ    | 0°               | -         | 8°   |  |  |  |

| Lead Thickness           | С    | 0.20             | -         | 0.33 |  |  |  |

| Lead Width               | b    | 0.31             | -         | 0.51 |  |  |  |

| Mold Draft Angle Top     | α    | 5°               | -         | 15°  |  |  |  |

| Mold Draft Angle Bottom  | β    | 5°               | -         | 15°  |  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- 3. Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- Dimensioning and tolerancing per ASME Y14.5M BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-051C Sheet 2 of 2

# TABLE 1: CONVERSION CONSIDERATIONS - PIC16C84, PIC16F83/F84, PIC16CR83/CR84, PIC16F84A (CONTINUED)

| Difference                                                 | PIC16C84                                                                                                                                                                                                                   | PIC16F83/F84       | PIC16CR83/<br>CR84 | PIC16F84A          |

|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|--------------------|

| EEADR<7:6> and IDD                                         | It is recommended that<br>the EEADR<7:6> bits be<br>cleared. When either of<br>these bits is set, the maxi-<br>mum IDD for the device is<br>higher than when both are<br>cleared.                                          | N/A                | N/A                | N/A                |

| The polarity of the<br>PWRTE bit                           | PWRTE                                                                                                                                                                                                                      | PWRTE              | PWRTE              | PWRTE              |

| Recommended value of<br>REXT for RC oscillator<br>circuits | Rext = 3kΩ - 100kΩ                                                                                                                                                                                                         | Rext = 5kΩ - 100kΩ | Rext = 5kΩ - 100kΩ | Rext = 3kΩ - 100kΩ |

| GIE bit unintentional<br>enable                            | If an interrupt occurs while<br>the Global Interrupt<br>Enable (GIE) bit is being<br>cleared, the GIE bit may<br>unintentionally be re-<br>enabled by the user's<br>Interrupt Service Routine<br>(the RETFIE instruction). | N/A                | N/A                | N/A                |

| Packages                                                   | PDIP, SOIC                                                                                                                                                                                                                 | PDIP, SOIC         | PDIP, SOIC         | PDIP, SOIC, SSOP   |

| Open Drain High<br>Voltage (VoD)                           | 14V                                                                                                                                                                                                                        | 12V                | 12V                | 8.5V               |

# **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| S35007C                                                                                       |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------|--|--|--|--|--|

|                                                                                               |  |  |  |  |  |

|                                                                                               |  |  |  |  |  |

|                                                                                               |  |  |  |  |  |

| <ol> <li>How does this document meet your hardware and software development needs?</li> </ol> |  |  |  |  |  |

|                                                                                               |  |  |  |  |  |

|                                                                                               |  |  |  |  |  |

| 3. Do you find the organization of this document easy to follow? If not, why?                 |  |  |  |  |  |

|                                                                                               |  |  |  |  |  |

|                                                                                               |  |  |  |  |  |

| 4. What additions to the document do you think would enhance the structure and subject?       |  |  |  |  |  |

|                                                                                               |  |  |  |  |  |

| 5. What deletions from the document could be made without affecting the overall usefulness?   |  |  |  |  |  |

|                                                                                               |  |  |  |  |  |

|                                                                                               |  |  |  |  |  |

| 6. Is there any incorrect or misleading information (what and where)?                         |  |  |  |  |  |

|                                                                                               |  |  |  |  |  |

|                                                                                               |  |  |  |  |  |

|                                                                                               |  |  |  |  |  |

|                                                                                               |  |  |  |  |  |

|                                                                                               |  |  |  |  |  |

DS35007C-page 86

# Worldwide Sales and Service

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney Tel: 61-2-9868-6733

Fax: 61-2-9868-6755 China - Beijing

Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Osaka** Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7828 Fax: 886-7-330-9305

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Fax: 45-4485-2829

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

11/29/12