#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 13                                                                       |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64 x 8                                                                   |

| RAM Size                   | 68 × 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 18-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f84a-20-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

## 4.0 I/O PORTS

Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Additional information on I/O ports may be found in the PIC<sup>®</sup> Mid-Range Reference Manual (DS33023).

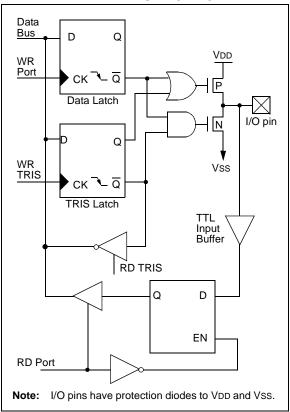

## 4.1 PORTA and TRISA Registers

PORTA is a 5-bit wide, bi-directional port. The corresponding data direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin).

| Note: | On a Power-on Reset, these pins are con- |

|-------|------------------------------------------|

|       | figured as inputs and read as '0'.       |

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read. This value is modified and then written to the port data latch.

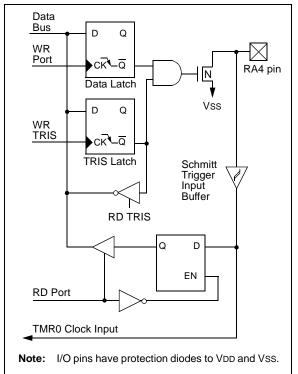

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers.

| BCF   | STATUS, RPO | ; |                       |

|-------|-------------|---|-----------------------|

| CLRF  | PORTA       | ; | Initialize PORTA by   |

|       |             | ; | clearing output       |

|       |             | ; | data latches          |

| BSF   | STATUS, RPO | ; | Select Bank 1         |

| MOVLW | 0x0F        | ; | Value used to         |

|       |             | ; | initialize data       |

|       |             | ; | direction             |

| MOVWF | TRISA       | ; | Set RA<3:0> as inputs |

|       |             | ; | RA4 as output         |

|       |             | ; | TRISA<7:5> are always |

|       |             | ; | read as '0'.          |

|       |             |   |                       |

#### FIGURE 4-1:

#### BLOCK DIAGRAM OF PINS RA3:RA0

FIGURE 4-2:

BLOCK DIAGRAM OF PIN RA4

#### TABLE 4-1: PORTA FUNCTIONS

| Name      | Bit0 | Buffer Type | Function                                                                     |

|-----------|------|-------------|------------------------------------------------------------------------------|

| RA0       | bit0 | TTL         | Input/output                                                                 |

| RA1       | bit1 | TTL         | Input/output                                                                 |

| RA2       | bit2 | TTL         | Input/output                                                                 |

| RA3       | bit3 | TTL         | Input/output                                                                 |

| RA4/T0CKI | bit4 | ST          | Input/output or external clock input for TMR0.<br>Output is open drain type. |

Legend: TTL = TTL input, ST = Schmitt Trigger input

## TABLE 4-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4     | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>Power-on<br>Reset | Value on all<br>other<br>RESETS |

|---------|-------|-------|-------|-------|-----------|--------|--------|--------|--------|-------------------------------|---------------------------------|

| 05h     | PORTA | _     | _     |       | RA4/T0CKI | RA3    | RA2    | RA1    | RA0    | x xxxx                        | u uuuu                          |

| 85h     | TRISA | _     | _     |       | TRISA4    | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111                        | 1 1111                          |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are unimplemented, read as '0'.

| Name    | Bit  | Buffer Type           | I/O Consistency Function                                                                                               |

|---------|------|-----------------------|------------------------------------------------------------------------------------------------------------------------|

| RB0/INT | bit0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input.<br>Internal software programmable weak pull-up.                          |

| RB1     | bit1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                         |

| RB2     | bit2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                         |

| RB3     | bit3 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                         |

| RB4     | bit4 | TTL                   | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up.                           |

| RB5     | bit5 | TTL                   | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up.                           |

| RB6     | bit6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up. Serial programming clock. |

| RB7     | bit7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up. Serial programming data.  |

## TABLE 4-3:PORTB FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger.

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

#### TABLE 4-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address | Name       | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0   | Value on<br>Power-on<br>Reset | Value on<br>all other<br>RESETS |

|---------|------------|--------|--------|--------|--------|--------|--------|--------|---------|-------------------------------|---------------------------------|

| 06h     | PORTB      | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0/INT | xxxx xxxx                     | uuuu uuuu                       |

| 86h     | TRISB      | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0  | 1111 1111                     | 1111 1111                       |

| 81h     | OPTION_REG | RBPU   | INTEDG | TOCS   | T0SE   | PSA    | PS2    | PS1    | PS0     | 1111 1111                     | 1111 1111                       |

| 0Bh,8Bh | INTCON     | GIE    | EEIE   | TOIE   | INTE   | RBIE   | T0IF   | INTF   | RBIF    | 0000 000x                     | 0000 000u                       |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTB.

# TABLE 6-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR

| Mode  | Freq                                                                                                                                            | OSC1/C1                                                                                                                                                             | OSC2/C2                                                                                                                                                                                              |  |  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| LP    | 32 kHz                                                                                                                                          | 68 - 100 pF                                                                                                                                                         | 68 - 100 pF                                                                                                                                                                                          |  |  |

|       | 200 kHz                                                                                                                                         | 15 - 33 pF                                                                                                                                                          | 15 - 33 pF                                                                                                                                                                                           |  |  |

| XT    | 100 kHz                                                                                                                                         | 100 - 150 pF                                                                                                                                                        | 100 - 150 pF                                                                                                                                                                                         |  |  |

|       | 2 MHz                                                                                                                                           | 15 - 33 pF                                                                                                                                                          | 15 - 33 pF                                                                                                                                                                                           |  |  |

|       | 4 MHz                                                                                                                                           | 15 - 33 pF                                                                                                                                                          | 15 - 33 pF                                                                                                                                                                                           |  |  |

| HS    | 4 MHz                                                                                                                                           | 15 - 33 pF                                                                                                                                                          | 15 - 33 pF                                                                                                                                                                                           |  |  |

|       | 20 MHz                                                                                                                                          | 15 - 33 pF                                                                                                                                                          | 15 - 33 pF                                                                                                                                                                                           |  |  |

| Note: | of the oscill<br>start-up time<br>guidance on<br>mode, as we<br>driving crysta<br>cation. Sinc<br>characteristic<br>crystal ma<br>values of ext | ator, but also<br>. These values<br>ly. Rs may be<br>ell as XT mode<br>als with low driv<br>e each crysta<br>cs, the user sho<br>nufacturer for<br>ternal component | ses the stability<br>increases the<br>s are for design<br>required in HS<br>, to avoid over-<br>ve level specifi-<br>il has its own<br>buld consult the<br>r appropriate<br>ents.<br>30 pF is recom- |  |  |

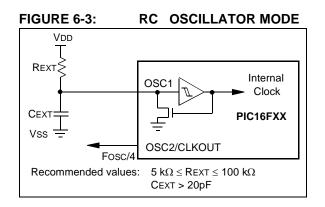

#### 6.2.3 RC OSCILLATOR

For timing insensitive applications, the RC device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) values, capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types also affects the oscillation frequency, especially for low CEXT values. The user needs to take into account variation, due to tolerance of the external R and C components. Figure 6-3 shows how an R/C combination is connected to the PIC16F84A.

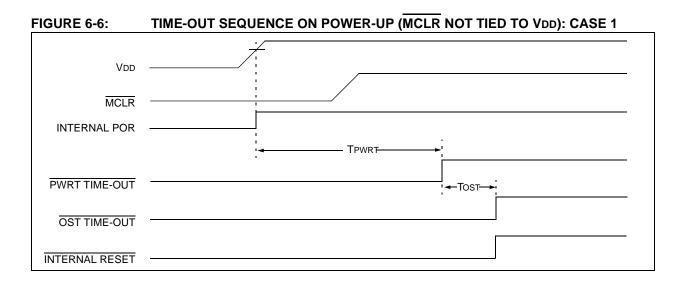

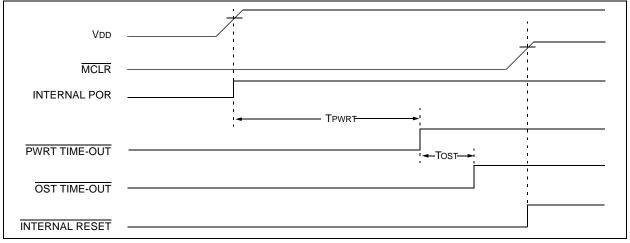

FIGURE 6-7: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

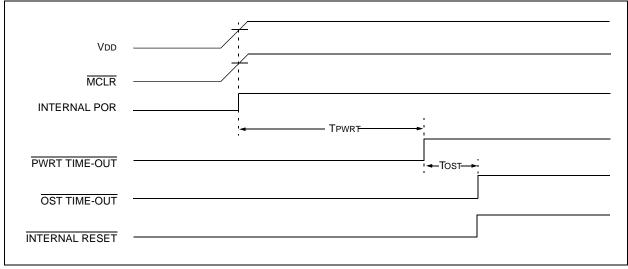

FIGURE 6-8: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD): FAST VDD RISE TIME

#### 6.9 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users wish to save key register values during an interrupt (e.g., W register and STATUS register). This is implemented in software.

The code in Example 6-1 stores and restores the STATUS and W register's values. The user defined registers, W\_TEMP and STATUS\_TEMP are the temporary storage locations for the W and STATUS registers values.

Example 6-1 does the following:

- a) Stores the W register.

- b) Stores the STATUS register in STATUS\_TEMP.

- c) Executes the Interrupt Service Routine code.

- d) Restores the STATUS (and bank select bit) register.

- e) Restores the W register.

| PUSH | MOVWF | W_TEMP        | ; Copy W to TEMP register,                          |

|------|-------|---------------|-----------------------------------------------------|

|      | SWAPF | STATUS, W     | ; Swap status to be saved into W                    |

|      | MOVWF | STATUS_TEMP   | ; Save status to STATUS_TEMP register               |

| ISR  | :     |               | :                                                   |

|      | :     |               | ; Interrupt Service Routine                         |

|      | :     |               | ; should configure Bank as required                 |

|      | :     |               | ;                                                   |

| POP  | SWAPF | STATUS_TEMP,W | ; Swap nibbles in STATUS_TEMP register              |

|      |       |               | ; and place result into W                           |

|      | MOVWF | STATUS        | ; Move W into STATUS register                       |

|      |       |               | ; (sets bank to original state)                     |

|      | SWAPF | W_TEMP, F     | ; Swap nibbles in W_TEMP and place result in W_TEMP |

|      | SWAPF | W_TEMP, W     | ; Swap nibbles in W_TEMP and place result into W    |

|      |       |               |                                                     |

#### 6.10 Watchdog Timer (WDT)

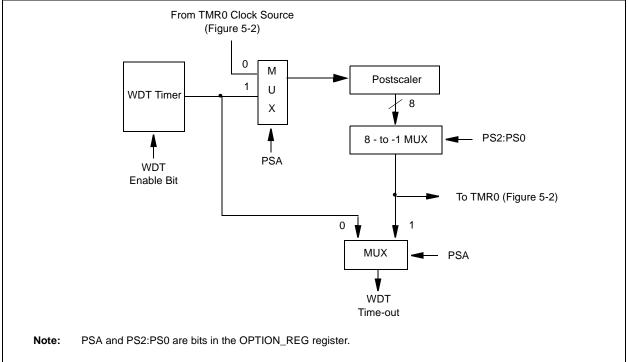

The Watchdog Timer is a free running On-Chip RC Oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run even if the clock on the OSC1/CLKIN and OSC2/CLKOUT pins of the device has been stopped, for example, by execution of a SLEEP instruction. During normal operation, a WDT time-out generates a device RESET. If the device is in SLEEP mode, a WDT wake-up causes the device to wake-up and continue with normal operation. The WDT can be permanently disabled by programming configuration bit WDTE as a '0' (Section 6.1).

#### 6.10.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms, (with no prescaler). The time-out periods vary with temperature, VDD and process variations from part to part (see DC specs). If longer time-out periods are desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT under software control by writing to the OPTION\_REG register. Thus, time-out periods up to 2.3 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the postscaler (if assigned to the WDT) and prevent it from timing out and generating a device RESET condition.

The  $\overline{\text{TO}}$  bit in the STATUS register will be cleared upon a WDT time-out.

#### 6.10.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken into account that under worst case conditions (VDD = Min., Temperature = Max., Max. WDT Prescaler), it may take several seconds before a WDT time-out occurs.

TABLE 6-7: SUMMARY OF REGISTERS ASSOCIATED WITH THE WATCHDOG TIMER

| Addr  | Name         | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on all<br>other<br>RESETS |

|-------|--------------|-------|--------|-------|-------|----------------------|-------|-------|-------|-------------------------------|---------------------------------|

| 2007h | Config. bits | (2)   | (2)    | (2)   | (2)   | PWRTE <sup>(1)</sup> | WDTE  | FOSC1 | FOSC0 | (2)                           |                                 |

| 81h   | OPTION_REG   | RBPU  | INTEDG | TOCS  | TOSE  | PSA                  | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                       |

Legend: x = unknown. Shaded cells are not used by the WDT.

**Note 1:** See Register 6-1 for operation of the PWRTE bit.

2: See Register 6-1 and Section 6.12 for operation of the code and data protection bits.

## 6.11.3 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs **during or after** the execution of a SLEEP instruction, the device will immediately wake-up from SLEEP. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

#### 6.12 Program Verification/Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

## 6.13 ID Locations

Four memory locations (2000h - 2004h) are designated as ID locations to store checksum or other code identification numbers. These locations are not accessible during normal execution but are readable and writable only during program/verify. Only the four Least Significant bits of ID location are usable.

## 6.14 In-Circuit Serial Programming

PIC16F84A microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground, and the programming voltage. Customers can manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product, allowing the most recent firmware or custom firmware to be programmed.

For complete details of Serial Programming, please refer to the In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) Guide, (DS30277).

#### TABLE 7-2: PIC16CXXX INSTRUCTION SET

| Operands         Description         Cycles         MSb         LSb         Affected         Note           BYTE-ORIENTED FILE REGISTER OPERATIONS           ADDWF         f, d         Add W and f         1         00         0111         dfff         ffff         Z         1,2           ANDWF         f, d         AND W with f         1         00         00101         dfff         ffff         Z         1,2           CLRF         f         Clear f         1         00         00101         dfff         fff         Z         1,2           CDECF         f, d         Decrement f, Skip if 0         1 (2)         00         1010         dfff         fff         Z         1,2           DECF         f, d         Increment f, Skip if 0         1 (2)         00         1010         dfff         fff         1,2           INCFSZ         f, d         Increment f, Skip if 0         1 (2)         00         1111         dfff         1,2         1,2           INCFSZ         f, d         Increment f, Skip if 0         1 (2)         00         1100         0000         dff ffff         1,2           INCFSZ         f, d         Notate Left (through Carry                                                                                                                                            | Mnemonic, Description |                                        |                             | 14-Bit C |      | Opcode |      | Status |          |       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------------------------|-----------------------------|----------|------|--------|------|--------|----------|-------|

| ADDWF         f, d         Add W and f         1         00         0111         dff ffff         C,DC,Z         1.2           ANDWF         f, d         AND W with f         1         00         0101         dfff ffff         Z         2           CLRF         f         Clear f         1         00         0001         dfff ffff         Z         2           COMF         f, d         Complement f         1         00         0001         dfff ffff         Z         1.2           DECFSZ         f, d         Decrement f, Skip if 0         1 (2)         00         1011         dfff ffff         Z         1.2           INCFS         f, d         Increment f, Skip if 0         1 (2)         00         1111         dfff ffff         Z         1.2           INCFSZ         f, d         Increment f, Skip if 0         1 (2)         00         1111         dfff fffff         Z         1.2           INCFSZ         f, d         Move f         1         00         0000         dfff ffff         Z         1.2           MOVF         f, d         Rotate Left fthrough Carry         1         00         0000         dfff ffff         C         1.2                                                                                                                                                   |                       |                                        | Description                 | Cycles   | MSb  |        |      | LSb    | Affected | Notes |

| ANDWF         f, d         AND With f         1         00         0101         dff ffff         Z         12           CLRF         f         Clear f         1         00         0001         lfff ffff         Z         12           CLRW         -         Clear W         1         00         0001         lfff ffff         Z         12           COMF         f, d         Decrement f         1         00         0011         dfff ffff         Z         12           DECFSZ         f, d         Decrement f, Skip if 0         1 (2)         00         111         dfff ffff         Z         1,2           INCFSZ         f, d         Increment f, Skip if 0         1 (2)         00         1111         dfff ffff         Z         1,2           IORVF         f, d         Increment f, Skip if 0         1 (2)         00         1111         dfff ffff         Z         1,2           MOVF         f, d         Move f         1         00         0000         0xx0         0000           REF         f, d         Rotate Right fft mough Carry         1         00         110         dff ffff         C         1,2           SUBWF         f, d                                                                                                                                                         |                       | BYTE-ORIENTED FILE REGISTER OPERATIONS |                             |          |      |        |      |        |          |       |

| CLRF         f         Clear f         Clear f         1         00         0001         lfff         fff         Z         2           COMF         f, d         Complement f         1         00         0001         0xxx <xxxx< td="">         Z         2           DECF         f, d         Decrement f, Skip if 0         1 (2)         00         1011         dfff ffff         Z         1,2           DECFSZ         f, d         Decrement f, Skip if 0         1 (2)         00         1111         dfff ffff         Z         1,2           INCF         f, d         Increment f, Skip if 0         1 (2)         00         1111         dfff ffff         Z         1,2           INCFVF         f, d         Move f         1         00         1001         dfff ffff         Z         1,2           INCFVF         f         Move f         1         00         100         dfff ffff         Z         1,2           MOVF         f         Move f         1         00         100         100         100         100         100         100         110         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2</xxxx<>                                                                                                                                               | ADDWF                 | f, d                                   | Add W and f                 | 1        | 00   | 0111   | dfff | ffff   | C,DC,Z   | 1,2   |

| CLRW         -         Clear W         1         00         0001         0xxx         xxxx         Z           COMF         f, d         Complement f         1         00         0011         dfff         ffff         Z         1,2           DECF         f, d         Decrement f, Skip if 0         1 (2)         00         1011         dfff         ffff         Z         1,2           INCF         f, d         Increment f         1         00         1010         dfff         ffff         Z         1,2           INCFSZ         f, d         Increment f, Skip if 0         1 (2)         00         1111         dfff         ffff         Z         1,2           MOVF         f, d         Increment f, Skip if 0         1 (2)         00         1111         dfff         T         1,2           MOVF         f, d         Move f         1         00         0000         1ff         T         1,2           MOVF         f, d         Rotate Left fthrough Carry         1         00         1010         dfff         C,DC,Z         1,2           SUBWF         f, d         Subtract W from f         1         00         0100         dffff                                                                                                                                                              | ANDWF                 | f, d                                   | AND W with f                | 1        | 00   | 0101   | dfff | ffff   | Z        | 1,2   |

| COMF         f, d         Complement f         1         00         1001         dfff         ffff         Z         1,2           DECF         f, d         Decrement f, Skip if 0         1 (2)         00         1011         dfff         ffff         Z         1,2           INCF         f, d         Increment f, Skip if 0         1 (2)         00         1010         dfff         ffff         Z         1,2           INCF         f, d         Increment f, Skip if 0         1 (2)         00         1010         dfff         ffff         Z         1,2           INCFSZ         f, d         Increment f         1         00         1000         dfff         ffff         Z         1,2           INCFV         f, d         Move W with f         1         00         1000         dfff         ffff         Z         1,2           MOVF         f, d         Rotate Left fthrough Carry         1         00         1000         0000         0xco 0000         RC         1,2           SUBWF         f, d         Subtract W from f         1         00         1010         dfff         ffff         Z         1,2           SUBWF         f, d         Sub                                                                                                                                                 | CLRF                  | f                                      | Clear f                     | 1        | 00   | 0001   | lfff | ffff   | Z        | 2     |

| DECF         f, d         Decrement f, Skip if 0         1         0         0011         dfff         fff         Z         1/2           DECFSZ         f, d         Increment f, Skip if 0         1 (2)         00         1011         dfff         fff         1/2           INCFSZ         f, d         Increment f, Skip if 0         1 (2)         00         1010         dfff         fff         Z         1/2           INCFSZ         f, d         Increment f, Skip if 0         1 (2)         00         1111         dfff         ffff         Z         1/2           INCFSZ         f, d         Increment f, Skip if 0         1         00         0100         dfff         ffff         Z         1/2           MOVF         f, d         Move f         1         00         0100         dfff         ffff         Z         1/2           MOVF         f, d         Rotate Left fhrough Carry         1         00         1010         dfff         ffff         Z         1/2           SUBWF         f, d         Subtract W from f         1         00         1010         dfff         ffff         1/2         1/2         1/2         1/2         1/2         1/2                                                                                                                                          | CLRW                  | -                                      | Clear W                     | 1        | 00   | 0001   | 0xxx | xxxx   | Z        |       |

| DECF         f, d         Decrement f, Skip if 0         1         00         0011         dfff         fff         Z         1, 2           DECFSZ         f, d         Decrement f, Skip if 0         1         1         00         1010         dfff         ffff         Z         1, 2           INCF         f, d         Increment f, Skip if 0         1         1         00         1010         dfff         ffff         Z         1, 2           INCFSZ         f, d         Increment f, Skip if 0         1         1         00         0100         dfff         ffff         Z         1, 2           INCFSZ         f, d         Inclusive OR W with f         1         00         0100         dfff         ffff         Z         1, 2           MOVF         f         Move f         No operation         1         00         0000         0000         0000         R         RF         f, d         Subtract W from f         1         00         1010         dfff         ffff         C         1, 2           SUBWF         f, d         Subtract W from f         1         00         1010         dfff         ffff         1, 2         1, 2           SWAPF <td>COMF</td> <td>f, d</td> <td>Complement f</td> <td>1</td> <td>00</td> <td>1001</td> <td>dfff</td> <td>ffff</td> <td>Z</td> <td>1,2</td> | COMF                  | f, d                                   | Complement f                | 1        | 00   | 1001   | dfff | ffff   | Z        | 1,2   |

| INCF         f, d         Increment f, Skip if 0         1         0         1010         dfff         ffff         Z         1,2           INCFSZ         f, d         Increment f, Skip if 0         1 (2)         00         1111         dfff         ffff         Z         1,2           IORWF         f, d         Inclusive OR W with f         1         00         0100         dfff         ffff         Z         1,2           MOVF         f, d         Move W to f         1         00         1000         dfff         ffff         Z         1,2           MOVF         f         Move W to f         1         00         1000         dfff         ffff         Z         1,2           MOVF         f, d         Rotate Left fthrough Carry         1         00         1100         dfff         ffff         C         1,2           SUBWF         f, d         Subtract W from f         1         00         1100         dfff         ffff         Z         1,2           XORWF         f, d         Subtract W from f         1         00         01010         dfff         ffff         Z         1,2           XORWF         f, d         Bit Set f                                                                                                                                                         | DECF                  | f, d                                   |                             | 1        | 00   | 0011   | dfff | ffff   | Z        | 1,2   |

| INCF         f, d         Increment f, Skip if 0         1         0         1010         dfff         ffff         Z         1,2           INCFSZ         f, d         Increment f, Skip if 0         1 (2)         00         1111         dfff         ffff         Z         1,2           IORWF         f, d         Inclusive OR W with f         1         00         0100         dfff         ffff         Z         1,2           MOVF         f, d         Move W to f         1         00         1000         dfff         ffff         Z         1,2           MOVF         f         Move W to f         1         00         1000         dfff         ffff         Z         1,2           MOVF         f, d         Rotate Left fthrough Carry         1         00         1100         dfff         ffff         C         1,2           SUBWF         f, d         Subtract W from f         1         00         1100         dfff         ffff         Z         1,2           XORWF         f, d         Subtract W from f         1         00         01010         dfff         ffff         Z         1,2           XORWF         f, d         Bit Set f                                                                                                                                                         | DECFSZ                | f, d                                   | Decrement f, Skip if 0      | 1 (2)    | 00   | 1011   | dfff | ffff   |          | 1,2,3 |

| INCFSZ         f, d         Increment f, Skip if 0         1 (2)         00         1111         dfff         ffff         1,2,           IORWF         f, d         Inclusive OR W with f         1         00         0100         dfff         ffff         Z         1,2,           MOVF         f, d         Move f         1         00         0100         dfff         ffff         Z         1,2,           MOVF         f, d         Move f         1         00         0100         dfff         ffff         Z         1,2,           MOVF         f         Move f         1         00         0000         0x00                                                                                                                                            | INCF                  | f. d                                   | Increment f                 | . ,      | 00   | 1010   | dfff | ffff   | Z        | 1,2   |

| IORWF         f, d         Inclusive OR W with f         1         00         0100         dfff         ffff         Z         1, 2           MOVF         f, d         Move f         1         00         1000         dfff         ffff         Z         1, 2           MOVWF         f         Move W to f         1         00         1000         dfff         ffff         Z         1, 2           MOVF         f         Move W to f         1         00         1000         dfff         ffff         Z         1, 2           RF         f, d         Rotate Left fthrough Carry         1         00         1100         dfff         ffff         C         1, 2           SUBWF         f, d         Swap nibbles in f         1         00         101         dfff         ffff         1, 2           XORWF         f, d         Exclusive OR W with f         1         0         0100         dfff         ffff         1, 2           XORWF         f, d         Exclusive OR W with f         1         1         00         101         01bb         bfff         ffff         2         1, 2           XORWF         f, d         Bit Test f, Skip if Clear                                                                                                                                                       | INCFSZ                | f. d                                   | Increment f. Skip if 0      | 1 (2)    | 00   | 1111   | dfff | ffff   |          | 1,2,3 |

| MOVF         f, d         Move f         1         00         1000         dfff         ffff         Z         1, 2           MOVF         f         Move W to f         1         00         0000         10ff         ffff         Z         1, 2           NOP         -         No Operation         1         00         0000         0xx0         0000         Cxx0         Cx1, 2         Cxx0         Cxx0         Cxx0         Cx1, 2         Cxx0         Cx1, 2         Cxx0         Cxx0         Cx0, Cx         Cx1, 2         Cxx0         Cxx0         Cx1, 2         C                                                                                                 | IORWF                 | ,                                      |                             |          |      |        |      |        | Z        | 1,2   |

| MOWWF         f         Move W to f         1         00         0000         1ff ffff         fff           NOP         -         No Operation         1         00         0000         0xx0         0xx0         0x00         0x00         0xx0         0x00         0xx0         0x00                                                                                                                    | -                     | ,                                      |                             |          |      |        |      |        |          |       |

| NOP         -         No Operation         1         00         0000         0xx0         0000           RLF         f, d         Rotate Left fthrough Carry         1         00         1101         dfff         ffff         C         1,2           RRF         f, d         Subtract W from f         1         00         1000         dfff         ffff         C         1,2           SWAPF         f, d         Swap nibbles in f         1         00         0110         dfff         ffff         Z         1,2           XORWF         f, d         Exclusive OR W with f         1         00         0110         dfff         ffff         Z         1,2           BIT-ORIENTED FILE REGISTER OPERATIONS           BCF         f, b         Bit Clear f         1         01         00bb         bfff         ffff         1,2           BSF         f, b         Bit Set f         1         01         01bb         bfff         ffff         3           BTFSS         f, b         Bit Test f, Skip if Clear         1 (2)         01         11bb         bfff         ffff         3           CALL         k         Call subroutine         2                                                                                                                                                                     |                       | , -                                    |                             | -        |      |        |      |        | _        | .,_   |

| RLF         f, d         Rotate Left fthrough Carry         1         00         1101         dfff         ffff         C         1,2           RRF         f, d         Rotate Right fthrough Carry         1         00         1100         dfff         ffff         C         1,2           SUBWF         f, d         Subtract W from f         1         00         0100         dfff         ffff         C,DC,Z         1,2           SWAPF         f, d         Swap nibbles in f         1         00         1110         dfff         ffff         Z,DC,Z         1,2           XORWF         f, d         Exclusive OR W with f         1         00         1100         dfff         ffff         Z         1,2           XORWF         f, d         Bit Clear f         1         01         00bb         bfff         ffff         1,2           BCF         f, b         Bit Test f, Skip if Clear         1         1         01         00bb         bfff         ffff         1,2           BTFSC         f, b         Bit Test f, Skip if Set         1         1         11         1111         111x         kkkk kkkk         Z           ADDLW         k         Add litera                                                                                                                                        |                       |                                        |                             |          |      |        |      |        |          |       |

| RRF         f, d         Rotate Right f through Carry         1         00         1100         dfff         fff         C         1,2           SUBWF         f, d         Subtract W from f         1         00         0010         dfff         ffff         C,DC,Z         1,2           SWAPF         f, d         Swap nibbles in f         1         00         0110         dfff         ffff         Z,DC,Z         1,2           XORWF         f, d         Exclusive OR W with f         1         00         0110         dfff         ffff         Z         1,2           BIT-ORIENTED FILE REGISTER OPERATIONS           BCF         f, b         Bit Clear f         1         01         00bb         bfff         ffff         1,2           BTFSC         f, b         Bit Test f, Skip if Clear         1 (2)         01         10bb         bfff         ffff         3           CLITERAL AND CONTROL OPERATIONS         LITERAL AND CONTROL OPERATIONS         Z         Z         Add literal and W         1         11         11101         kkkk kkkk         Z         Z           ADDLW         k         Add literal and W         1         1         11         1000         kkkk kkkk                                                                                                                     | -                     | f. d                                   |                             | -        |      |        |      |        | С        | 1,2   |

| SUBWF         f, d         Subtract W from f         1         00         0010         dfff         ffff         C,DC,Z         1,2           SWAPF         f, d         Swap nibbles in f         1         00         0110         dfff         ffff         Z         1,2           XORWF         f, d         Exclusive OR W with f         1         00         0110         dfff         ffff         Z         1,2           BIT-ORIENTED FILE REGISTER OPERATIONS           BCF         f, b         Bit Clear f         1         01         00bb         bfff         ffff         1,2           BSF         f, b         Bit Test f, Skip if Clear         1         01         01bb         bfff         ffff         1,2           BTFSS         f, b         Bit Test f, Skip if Set         1 (2)         01         10bb         bfff         ffff         3           LITERAL AND CONTROL OPERATIONS         Interal and W         1         11         111x         kkkk kkkk         Z         Z           ADDLW         k         Add literal and W         1         1         11         111x         kkkk kkkk         Z           CALL         k         Call subroutine                                                                                                                                              |                       | , -                                    |                             | -        |      |        |      |        | -        | 1,2   |

| SWAPF<br>XORWF         f, d         Swap nibbles in f<br>Exclusive OR W with f         1         00         1110         dfff         ffff         1,2           BIT-ORIENTED FILE REGISTER OPERATIONS           BIT-ORIENTED FILE REGISTER OPERATIONS           BCF         f, b         Bit Clear f         1         01         00bb         bfff         ffff         1,2           BSF         f, b         Bit Set f         1         01         00bb         bfff         ffff         1,2           BTFSC         f, b         Bit Test f, Skip if Clear         1         01         01bb         bfff         ffff         1,2           LITERAL AND CONTROL OPERATIONS           ADDLW         k         Add literal and W         1         11         111.001         kkkk         kkkk         Z           ANDLW         k         Add literal and W         1         11         11001         kkkk         kkkk         Z           CALL         k         Call subroutine         2         10         0kkk         kkkkk         Z           GOTO         k         Go to address         2         10         111.0000         kkkkkkkk         Z </td <td></td> <td>,</td> <td></td> <td>-</td> <td></td> <td></td> <td></td> <td></td> <td>-</td> <td>,</td>                                                            |                       | ,                                      |                             | -        |      |        |      |        | -        | ,     |

| XORWF         f, d         Exclusive OR W with f         1         00         0110         dfff         ffff         Z         1,2           BIT-ORIENTED FILE REGISTER OPERATIONS           BCF         f, b         Bit Clear f         1         01         00bb         bfff         ffff         1,2           BSF         f, b         Bit Clear f         1         1         01         01bb         bfff         ffff         1,2           BTFSC         f, b         Bit Test f, Skip if Clear         1         1         01         01bb         bfff         ffff         1,2           ADDLW         k         Add literal and W         1         1         111         111x         kkkk         kkkk         Z         Z           ADDLW         k         Add literal and W         1         1         11         111x         kkkk         kkkk         Z           ADDLW         k         Call subroutine         2         10         0kkk         kkkk         Z         Z           GOTO         k         Go to address         2         10         0kkk         kkkk         Z           OCOTO         K                                                                                                                                                                                                         |                       | ,                                      |                             |          |      |        |      |        | 0,20,2   |       |

| BIT-ORIENTED FILE REGISTER OPERATIONS         BCF       f, b       Bit Clear f       1       01       00bb       bfff       ffff       1,2         BSF       f, b       Bit Set f       1       01       01bb       bfff       ffff       1,2         BTFSC       f, b       Bit Test f, Skip if Clear       1 (2)       01       10bb       bfff       ffff       3         BTFSS       f, b       Bit Test f, Skip if Set       1 (2)       01       11bb       bfff       ffff       3         LITERAL AND CONTROL OPERATIONS         ADDLW       k       Add literal and W       1       11       111       111x       kkkk       kkkk       Z         ADDLW       k       Add literal with W       1       1       11       1001       kkkk       kkkk       Z         CALL       k       Call subroutine       2       10       0kkk       kkkk       Z       TO,PD         GOTO       k       Go to address       2       10       11kkk       kkkk       Z       MOVLW       TO,PD         MOVLW       k       Inclusive OR literal with W       1       11       00000       0001                                                                                                                                                                                                                                                    |                       | ,                                      |                             | -        |      |        |      |        | 7        |       |

| BCFf, bBit Clear f10100bbbfffffff1,2BSFf, bBit Set f10101bbbfffffff1,2BTFSCf, bBit Test f, Skip if Clear1 (2)0110bbbfffffff3BTFSSf, bBit Test f, Skip if Set1 (2)0111bbbfffffff3LITERAL AND CONTROL OPERATIONSADDLWkAdd literal and W111111kkkkkkkZADDLWkAND literal with W1111001kkkkkkkkZCALLkCall subroutine2100kkkkkkkZCLRWDT-Clear Watchdog Timer11000000100TO,PDGOTOkGo to address2101kkkkkkkZIORLWkInclusive OR literal with W111000xkkkkZMOVLWkMove literal to W111000xkkkkZRETFIE-Return from interrupt20000001001RETLWRETURN-Return with literal in W21101xxkkkkKkkkRETURN-Return from Subroutine20000001000SLEEP-Go into standby mode100000010011TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                       | ., a                                   |                             |          |      |        | 4111 |        | _        | •,=   |

| BSFf, bBit Set f10101bbbfffffff1,2BTFSCf, bBit Test f, Skip if Clear11110bbbfffffff3BTFSSf, bBit Test f, Skip if Set1(2)0111bbbfffffff3LITERAL AND CONTROL OPERATIONSADDLWkAdd literal and W111111111xkkkkkkkkZANDLWkAdd literal with W1111001kkkkkkkkZCALLkCall subroutine2100kkkkkkkKkkkZGOTOkGo to address2101kkkkkkkZIORLWkInclusive OR literal with W1111000kkkkZMOVLWkReturn from interrupt200000000011001RETLWkReturn with literal in W21101xxkkkkkkkkRETURN-Return from Subroutine20000000001TO,PDSLEEP-Go into standby mode10000000101TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | DOF                   | 6.1                                    |                             | -        | -    | -      |      |        |          | 4.0   |

| BTFSC<br>BTFSSf, bBit Test f, Skip if Clear<br>Bit Test f, Skip if Set1 (2)0110bbbfffffff3LITERAL AND CONTROL OPERATIONSADDLW<br>ANDLWkAdd literal and W111111111xkkkkkkkkZANDLW<br>CALLkAdd literal with W1111111001kkkkkkkkZCALL<br>GOTOkCall subroutine2100kkkkkkkkkkkZCIRWDT<br>GOTOClear Watchdog Timer<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -                     | , -                                    |                             | -        | -    |        |      |        |          |       |

| BTFSSf, bBit Test f, Skip if Set1 (2)0111bbbfffffff3LITERAL AND CONTROL OPERATIONSADDLWkAdd literal and W111111111xkkkkkkkkC,DC,ZANDLWkAND literal with W1111001kkkkkkkkZCALLkCall subroutine2100kkkkkkkkkkkZCLRWDT-Clear Watchdog Timer100000001100100TO,PDGOTOkGo to address2101kkkkkkkZIORLWkInclusive OR literal with W1111000kkkkkkkkMOVLWkMove literal to W1110000000001001RETLWkReturn from interrupt200000000001001RETLWkReturn with literal in W21101xxkkkkkkkkRETURN-Return from Subroutine20000000001TO,PDSLEEP-Go into standby mode10000000110TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -                     | ,                                      |                             | -        | -    |        |      |        |          | ,     |

| LITERAL AND CONTROL OPERATIONSADDLWkAdd literal and W111111111xkkkkkkkkC,DC,ZANDLWkAND literal with W11111001kkkkkkkkZCALLkCall subroutine2100kkkkkkkkkkkZCLRWDT-Clear Watchdog Timer100000001100100TO,PDGOTOkGo to address2101kkkkkkkkkkkZIORLWkInclusive OR literal with W1111000kkkkkkkkZMOVLWkMove literal to W1110000000001001RETFIERETFIE-Return from interrupt200000000001001RETLWRETURN-Return from Subroutine200000000001000SLEEP-Go into standby mode10000000110TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                       | ,                                      |                             |          | -    |        |      |        |          |       |

| ADDLWkAdd literal and W111111 111xkkkkkkkkC,DC,ZANDLWkAND literal with W1111001kkkkkkkkZCALLkCall subroutine2100kkkkkkkkkkkZCLRWDT-Clear Watchdog Timer100000001100100TO,PDGOTOkGo to address2101kkkkkkkkkkkZIORLWkInclusive OR literal with W1111000kkkkkkkkZMOVLWkMove literal to W111000xxkkkkkkkkZRETFIE-Return from interrupt200000000011001RETLWkReturn with literal in W21101xxkkkkkkkkRETURN-Return from Subroutine20000000001TO,PDSLEEP-Go into standby mode10000000110TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | BIESS                 | f, b                                   |                             |          | -    | 11bb   | bfff | ffff   |          | 3     |

| ANDLWkAND literal with W1111001kkkkkkkkZCALLkCall subroutine2100kkkkkkkkkkkKkkkZCLRWDT-Clear Watchdog Timer100000001100100TO,PDGOTOkGo to address2101kkkkkkkkkkkKkkkZIORLWkInclusive OR literal with W1111000kkkkkkkkZMOVLWkMove literal to W111000000001001FRETFIE-Return from interrupt200000000001001RETLWkReturn with literal in W21101xxkkkkkkkkRETURN-Return from Subroutine200000000001000SLEEP-Go into standby mode10000000110TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                       |                                        | LITERAL AND CONTROL         | OPERAT   | IONS |        |      |        |          |       |

| CALLkCall subroutine2100kkkkkkkkkkkkkkkCLRWDT-Clear Watchdog Timer100000001100100TO,PDGOTOkGo to address2101kkkkkkkkkkkZIORLWkInclusive OR literal with W1111000kkkkkkkkZMOVLWkMove literal to W111000000001001FRETFIE-Return from interrupt200000000001001RETLWkReturn with literal in W21101xxkkkkkkkkRETURN-Return from Subroutine200000000001000SLEEP-Go into standby mode10000000110TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ADDLW                 | k                                      | Add literal and W           | 1        | 11   | 111x   | kkkk | kkkk   | C,DC,Z   |       |

| CLRWDT       -       Clear Watchdog Timer       1       00       0000       0110       0100         GOTO       k       Go to address       2       10       1kkk       kkkk       kkkk         IORLW       k       Inclusive OR literal with W       1       11       1000       kkkk       kkkk         IORLW       k       Inclusive OR literal with W       1       11       1000       kkkk       kkkk         MOVLW       k       Move literal to W       1       11       00000       0000       1001         RETFIE       -       Return from interrupt       2       00       0000       0000       1001         RETLW       k       Return with literal in W       2       11       01xx       kkkk       kkkk         RETURN       -       Return from Subroutine       2       00       0000       0001       1000         SLEEP       -       Go into standby mode       1       00       0000       0110       TO,PD                                                                                                                                                                                                                                                                                                                                                                                                             | ANDLW                 | k                                      | AND literal with W          | 1        | 11   | 1001   | kkkk | kkkk   | Z        |       |

| GOTO         k         Go to address         2         10         1kkk         kkkk         kkkk           IORLW         k         Inclusive OR literal with W         1         11         1000         kkkk         kkkk         Z           MOVLW         k         Move literal to W         1         11         1000         kkkk         kkkk         Z           RETFIE         -         Return from interrupt         2         00         0000         1001           RETLW         k         Return with literal in W         2         11         01xx         kkkk         kkkk           RETURN         -         Return from Subroutine         2         00         0000         1000           SLEEP         -         Go into standby mode         1         00         0000         011         TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CALL                  | k                                      | Call subroutine             | 2        | 10   | 0kkk   | kkkk | kkkk   |          |       |

| IORLW         k         Inclusive OR literal with W         1         11         1000         kkk         kkkk         Z           MOVLW         k         Move literal to W         1         11         1000         kkkk         kkkk         Z           RETFIE         -         Return from interrupt         2         00         0000         0000         1001           RETLW         k         Return with literal in W         2         11         01xx         kkkk         kkkk           RETURN         -         Return from Subroutine         2         00         0000         1000           SLEEP         -         Go into standby mode         1         00         0000         011         TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CLRWDT                | -                                      | Clear Watchdog Timer        | 1        | 00   | 0000   | 0110 | 0100   | TO,PD    |       |

| MOVLW         k         Move literal to W         1         11         00xx         kkkk         kkkk           RETFIE         -         Return from interrupt         2         00         0000         0001         1001           RETLW         k         Return with literal in W         2         11         01xx         kkkk         kkkk           RETURN         -         Return from Subroutine         2         00         0000         1000           SLEEP         -         Go into standby mode         1         00         0000         011         TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | GOTO                  | k                                      | Go to address               | 2        | 10   | 1kkk   | kkkk | kkkk   |          |       |

| RETFIE         -         Return from interrupt         2         00         0000         1001           RETLW         k         Return with literal in W         2         11         01xx         kkkk         kkkk           RETURN         -         Return from Subroutine         2         00         0000         1000           SLEEP         -         Go into standby mode         1         00         0000         011         TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | IORLW                 | k                                      | Inclusive OR literal with W | 1        | 11   | 1000   | kkkk | kkkk   | Z        |       |

| RETLW         k         Return with literal in W         2         11         01xx         kkkk         kkkk           RETURN         -         Return from Subroutine         2         00         0000         1000           SLEEP         -         Go into standby mode         1         00         0000         011         TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | MOVLW                 | k                                      | Move literal to W           | 1        | 11   | 00xx   | kkkk | kkkk   |          |       |

| RETURN         -         Return from Subroutine         2         00         0000         1000           SLEEP         -         Go into standby mode         1         00         0000         011         TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | RETFIE                | -                                      | Return from interrupt       | 2        | 00   | 0000   | 0000 | 1001   |          |       |

| SLEEP         -         Go into standby mode         1         00         0000         0110         0011         TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RETLW                 | k                                      | Return with literal in W    | 2        | 11   | 01xx   | kkkk | kkkk   |          |       |